#### **Features**

- Single supply voltage

5 ~ 26V for loudspeaker driver

- Input digital audio interface

- Sampling frequency: 32kHz, 44.1kHz and 48kHz

- Left-justified, MSB first, 1-bit delay with digital audio data 24-bits

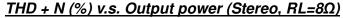

- Loudspeaker power @ 24V supply 15W / CH with 8Ω < 0.5% THD+N</li>

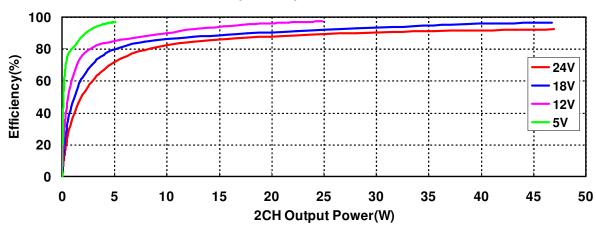

- Efficiency 87% (PVDD=24V, RL=8Ω, Po=10W)

- Distortion ration (THD+N) < 0.1% @ Po=7.5W

- PSNR ratio 99dB (PVDD=24V)

- Residual noise 130uVrms (A-weighted filter)

- Channel separation > 90 dB

- Power limit function

- Gain setting function

- Stereo/Mono switching function

- Output mute function (Quick mute / Quick start)

- Sleep function

- Pop noise reduction function

- Over current protection function (OCP)

- Over voltage protection function (OVP)

- Over temperature protection function (OTP)

- Under voltage lockout (UVLO)

- DC detection function (DCDET)

- Clock detection function (CKDET)

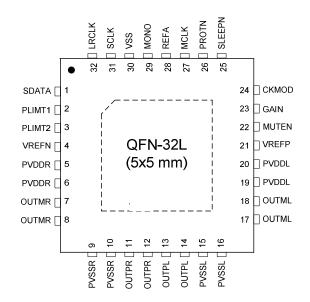

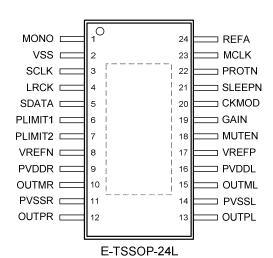

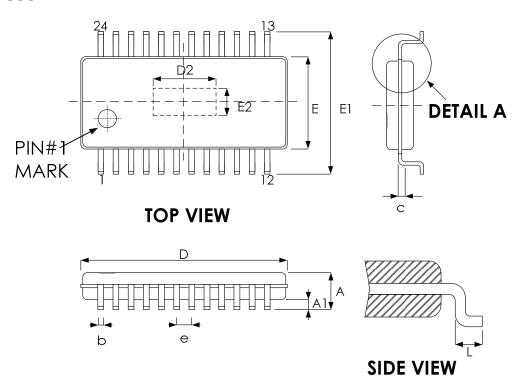

- Package available in both of QFN-32L and E-TSSOP-24L

### **Applications**

- TV audio

- Boom-Box

- Powered speaker

- Consumer Audio Equipment

### **Description**

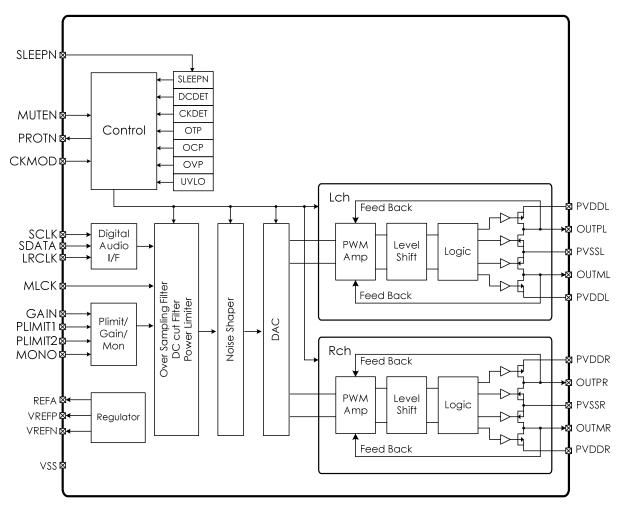

XA8123 is a high-performance digital audio amplifier IC that delivers up to 20W×2ch, which has a digital audio interface, and is capable of operating at a supply voltage ranging from 5V to 26V.

XA8123 allows a speaker to be directly connected to the output. In addition, this amplifier is insusceptible to supply voltage fluctuation because of a feedback-type digital amplifier, and have the feature with high power supply noise tolerance. As a result, power supply can be simplified and allowing a simple amplifier system with less external components to be configured.

XA8123 has the following functions: gain setting function, power limit function, pop noise reduction function, over current protection function for speaker output pins, internal over temperature protection function, under voltage lockout, and DC detection function.

### **Pin Assignments (TOP VIEW)**

### **Pin Description**

| NAME    | QFN-32L<br>Pin # | E-TSSOP-24L<br>Pin# | TYP<br>(Note1) | DESCRIPTION                                                                                                                                        |

|---------|------------------|---------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| SDATA   | 1                | 5                   | I              | Audio data input pin.                                                                                                                              |

| PLIMIT1 | 2                | 6                   | Α              | Power limit setting pin 1.                                                                                                                         |

| PLIMIT2 | 3                | 7                   | Α              | Power limit setting pin 2.                                                                                                                         |

| VREFN   | 4                | 8                   | 0              | Internal regulator output pin.                                                                                                                     |

| PVDDR   | 5, 6             | 9                   | Р              | Power pin for the digital amplifier output Rch.                                                                                                    |

| OUTMR   | 7, 8             | 10                  | 0              | Digital amplifier output pin Rch                                                                                                                   |

| PVSSR   | 9, 10            | 11                  | Р              | GND pin for digital amplifier output Rch.                                                                                                          |

| OUTPR   | 11, 12           | 12                  | 0              | Digital amplifier output pin Rch+.                                                                                                                 |

| OUTPL   | 13, 14           | 12                  | 0              | Digital amplifier output pin Lch+.                                                                                                                 |

| PVSSL   | 15, 16           | 14                  | Р              | GND pin for digital amplifier output Lch.                                                                                                          |

| OUTML   | 17, 18           | 15                  | 0              | Digital amplifier output pin Lch                                                                                                                   |

| PVDDL   | 19, 20           | 16                  | Р              | Power pin for the digital amplifier output Lch.                                                                                                    |

| VREFP   | 21               | 17                  | 0              | Internal regulator output pin.                                                                                                                     |

| MUTEN   | 22               | 18                  | I              | Mute pin.                                                                                                                                          |

| GAIN    | 23               | 19                  | Α              | Gain setting pin.                                                                                                                                  |

| CKMOD   | 24               | 20                  | I              | Clock mode setting pin.                                                                                                                            |

| SLEEPN  | 25               | 21                  | I              | Sleep reset, a voltage for supplying SLEEPN pin with "H" level should be applied from an external power supply. Do not apply from REFA pin output. |

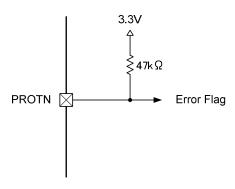

| PROTN   | 26               | 22                  | O/D            | Error flag output pin.                                                                                                                             |

| MCLK    | 27               | 23                  | I              | Master clock input pin.                                                                                                                            |

| REFA    | 28               | 24                  | 0              | Internal regulator output pin.                                                                                                                     |

| MONO    | 29               | 1                   | Α              | Stereo/Mono setting pin.                                                                                                                           |

| VSS     | 30               | 2                   | Р              | GND pin.                                                                                                                                           |

| SCLK    | 31               | 3                   | I              | Bit clock input pin.                                                                                                                               |

| LRCLK   | 32               | 4                   | I              | Word clock input pin.                                                                                                                              |

| Т       | hermal pad       |                     | Р              | Must be soldered to PCB's ground plane.                                                                                                            |

Note 1: "TYP" of description, I: Input pin, O: Output pin, A: Analog pin, O/D: Open-Drain output pin, P: Power pin.

## **Pin Internal Circuit**

| Name    | QFN 32L<br>Pin # | E-TSSOP-24L<br>Pin # | Equivalent Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDATA   | 1                | 5                    | <b>⋈</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PLIMIT1 | 2                | 6                    | Schmitt trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PLIMIT2 | 3                | 7                    | DVSS——                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VREFN   | 4                | 8                    | PVDDL |

| PVDDR   | 5,6              | 9                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| OUTMR   | 7,8              | 10                   | PVDDR — PVSSR — PVSSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PVSSR   | 9,10             | 11                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| OUTPR   | 11,12            | 12                   | PVDDR PVSSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| OUTPL   | 13,14            | 13                   | PVDDL PVSSL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PVSSL   | 15,16            | 14                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| OUTML   | 17,18 | 15 | PVDDL PVSSL                            |

|---------|-------|----|----------------------------------------|

| PVDDL   | 19,20 | 16 | _                                      |

| VREFP   | 21    | 17 | PVDD PVDD PVDD Analog VSS              |

| MUTEN   | 22    | 18 | Schmitt trigger    Use for Test    VSS |

| PLIMIT1 | 23    | 19 | Schmitt trigger                        |

| PLIMIT2 | 24    | 20 |                                        |

| GAIN    | 25    | 21 |                                        |

| PROTN   | 26    | 22 | DVSS                                   |

| MCLK    | 27    | 23 | Schmitt trigger                        |

| REFA  | 28 | 24 | VREFN VSS VSS           |

|-------|----|----|-------------------------|

| MONO  | 29 | 1  | Schmitt trigger         |

| VSS   | 30 | 2  | -                       |

| SCLK  | 31 | 3  | N N N                   |

| LRCLK | 32 | 4  | Schmitt trigger  DVSS—— |

### **Ordering Information**

| Product ID | Package              | Packing                                  | Comments |

|------------|----------------------|------------------------------------------|----------|

| XA8123_QCB | QFN 32L<br>(5mmx5mm) | 490 Units / Tray<br>10 trays / Inner Box | Green    |

| XA8123_EX  | E-TSSOP 24L          | 62 Units / Tube<br>100 Tubes / Small Box | Green    |

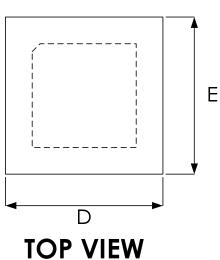

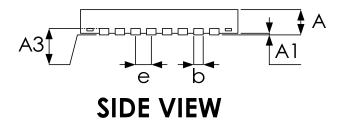

### **Available Package**

| Package Type | Device No. | θ <sub>ja</sub> (°C/ <b>W</b> ) | θ <sub>jt</sub> (°C/ <b>W</b> ) | Ψ <sub>jt</sub> (°C/ <b>W</b> ) | Exposed Thermal Pad |

|--------------|------------|---------------------------------|---------------------------------|---------------------------------|---------------------|

| QFN 32L      | XA8123     | 34                              | 14.4                            | 1.1                             | Yes (Note2)         |

| E-TSSOP 24L  | AA0123     | 26.8                            | 27.1                            | 1.83                            | res (Notez)         |

- Note 2.1: The thermal pad is located at the bottom of the package. To optimize thermal performance, soldering the thermal pad to the PCB's ground plane is suggested.

- Note 2.2:  $\theta_{ja}$  is measured on a room temperature ( $T_A$ =25 $\mathcal{C}$ ), natural convection environment test board, which is constructed with a thermally efficient, 4-layers PCB (2S2P). The measurement is tested using the JEDEC51-5 thermal measurement standard.

- Note 2.3:  $\theta_{jt}$  represents the heat resistance for the heat flow between the chip and the package's top surface (The junction-to-top thermal resistance is obtained by simulating a cold plate test on the top of the package).

- Note 2.4:  $\Psi_{jt}$  represents the heat resistance for the heat flow between the chip and the exposed pad's center (The junction-to-top characterization parameter is extracted from the simulation data to obtain  $\Theta_{ja}$ ).

### **Absolute Maximum Ratings**

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.

| SYMBOL             | PARAMETER                            | TEST CONDITIONS                                                                        | MIN  | MAX | UNIT |

|--------------------|--------------------------------------|----------------------------------------------------------------------------------------|------|-----|------|

| PVDD               | Supply for driver stage              | PVDDR, PVDDL                                                                           | -0.3 | 30  | V    |

| Vı                 | Interface pin voltage                | MUTEN, MCLK, SCLK, LRCLK,<br>SDATA, SLEEPN, CKMOD, GAIN,<br>MONO, PLIMIT1, and PLIMIT2 | -0.3 | 3.8 | V    |

| V <sub>PROTN</sub> | PROTN terminal voltage range         | PROTN                                                                                  | -0.3 | 3.8 | V    |

| T <sub>A</sub>     | Operating free-air temperature range |                                                                                        |      | 85  | °C   |

| TJ                 | Operating junction temperature range |                                                                                        | -40  | 150 | °C   |

| T <sub>stg</sub>   | Storage temperature range            | je                                                                                     |      | 150 | °C   |

| $R_L$              | Minimum Load Resistance              | Stereo (BTL)                                                                           | 3.6  |     | Ω    |

### **Recommended Operating Conditions**

| Parameter                             | Symbol          | Min. | Тур. | Max. | Unit        |

|---------------------------------------|-----------------|------|------|------|-------------|

| Power supply voltage for driver stage | PVDD            | 5    | =    | 26   | V           |

| Digital terminals input voltage       | V <sub>IN</sub> | 2.2  | 3.3  | 3.6  | V           |

| Operating Ambient Temperature         | Ta              | -40  | -    | 85   | $_{\infty}$ |

| Stereo Speaker Impedance (Note 3)     | $R_L$           | 4    | 8    | -    | Ω           |

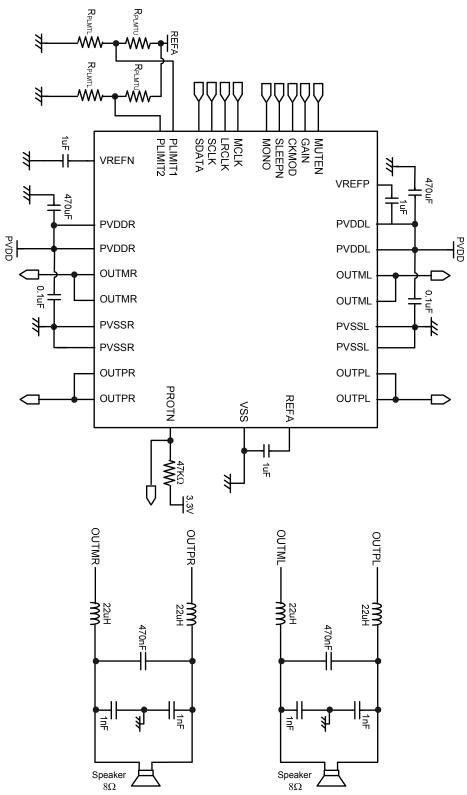

Note 3: Loudspeaker over-current protection is only effective when loudspeaker drivers are properly connected with external LC filters. Please refer to the application circuit example for recommended LC filter configuration.

### **General Electrical Characteristics**

● PVDD=5V to 24V, T<sub>A</sub>=25 °C, unless otherwise specified.

|                         | Item                                                 | Symbol            | Condition            | Min.      | Min. Typ. Max |     | Unit |

|-------------------------|------------------------------------------------------|-------------------|----------------------|-----------|---------------|-----|------|

| PVDD pin                | Startup Threshold Voltage                            | $V_{HUVLH}$       | -                    | _         | 4.1           | _   | V    |

| F VDD þill              | Shutdown Threshold Voltage                           | $V_{HUVLL}$       | _                    | _         | 4             | _   | ٧    |

| Digital pina            | Input Voltage H level                                | V <sub>IH</sub>   | _                    | 2.0       | -             | _   | ٧    |

| Digital pins<br>(note4) | Input Voltage L level                                | $V_{IL}$          | _                    | _         | -             | 8.0 | ٧    |

| (110164)                | Input Impedance                                      | R <sub>IN_D</sub> | ı                    | 3.3       | ı             | _   | МΩ   |

|                         | Input Voltage H level                                | $V_{IH}$          | _                    | 2.2       | -             | _   | V    |

| SLEEPN pin              | Input Voltage L level                                | $V_{IL}$          | _                    | _         | -             | 0.5 | V    |

|                         | Input Impedance                                      | R <sub>IN_D</sub> | _                    | 3.3       | -             | _   | МΩ   |

| PROTN pin C             | output Voltage                                       | V <sub>OL</sub>   | I <sub>OL</sub> =2mA | -   -   C |               | 0.4 | V    |

| REFA pin Out            | put Voltage                                          | $V_{REFA}$        | ı                    | ı         | 1.8           | _   | V    |

| VREFN pin O             | utput Voltage                                        | $V_{REFN}$        | PVDD =24V            | 5.5       |               |     | V    |

| VREFP pin O             | utput Voltage                                        | $V_{REFP}$        | PVDD =24V            | 18.5      |               |     | V    |

|                         | at idling state                                      | I <sub>DDPP</sub> | PVDD =24V,           | 1         | 34            | _   | mA   |

| Current                 | at raining state                                     | ·DDPP             | No load              |           | <u> </u>      |     | , \  |

| drawn from              | at power-down state                                  | I <sub>DDPS</sub> | PVDD =24V,           | _         | 20            | _   | μA   |

| PVDD                    | (SLEEPN="L")                                         | פאטטי             | No load              |           | 1             |     | μ/   |

| 1,400                   | at mute state                                        |                   | PVDD =24V,           |           | 26            |     | mA   |

|                         | (MUTEN="L")                                          | I <sub>DDPM</sub> | No load              |           | 20            |     | IIIA |

| Static drain to         | tatic drain to source on state resistor, PMOS Rds-on |                   |                      | 234       |               | mΩ  |      |

| Static drain to         | source on state resistor, NMOS                       | nus-ull           | Id=250mA             |           | 218           |     | mΩ   |

Note4: Digital Pins: MUTEN, MLCK, SCLK, LRCLK, SDATA, and CKMOD

### **Application Circuit Example**

Application circuit for Stereo mode

## **Electrical Characteristics and Specifications of Loudspeaker Driver**

• PVDD=24V,  $T_A=25$  °C,  $R_L=8\Omega$ ,unless otherwise specified.

| Item                        |                 | Symbol | Condition                                  | Min.     | Тур. | Max. | Unit     |

|-----------------------------|-----------------|--------|--------------------------------------------|----------|------|------|----------|

|                             |                 |        | PVDD=24V, $R_L=8\Omega$ ,<br>THD+N=2.9%    | 1        | 20   | -    | W        |

| Maximum Instantaneous       | Stereo          | Po     | PVDD=12V, R <sub>L</sub> =8Ω,<br>THD+N=10% | 1        | 10   | _    | W        |

| Output                      |                 | FU     | PVDD=12V, $R_L=4\Omega$<br>THD+N=10%       | ı        | 15   | -    | W        |

|                             | Mono            |        | PVDD=24V, $R_L$ =4 $\Omega$ , THD+N=10%    | 1        | 40   | _    | W        |

| Total Harmonic Distortion   | Stereo,<br>Mono | THD+N  | $R_L=8\Omega$ , Po=7.5W                    | _        | 0.1  | _    | %        |

| Residual Noise              | Stereo,<br>Mono | Vn     | $R_L$ =8 $\Omega$ , A-Weighted Filter      | 1        | 130  |      | μVrms    |

| S/N Ratio                   | Stereo,<br>Mono | SNR    | R <sub>L</sub> =8Ω,<br>A-Weighted Filter   | 1        | 99   | _    | dB       |

| Channel Separation (L vs R) |                 | CS     | $R_L=8\Omega$ , 1kHz                       | ı        | 93   | _    | dB       |

| PSRR                        | Stereo,<br>Mono | PSRR   | PVDD applied,<br>Vripple=200mVpp, f=1kHz   | -        | 70   | _    | dB       |

|                             | Stereo          |        | PVDD=24V, R <sub>L</sub> =8Ω,<br>Po=10W    |          | 87   | =-   | %        |

| Maximum Efficiency          | Stereo          | n      | PVDD=12V, $R_L$ =4 $\Omega$ , Po=10W       | ı        | 86   | _    | %        |

| Maximum Emolency            | Mono            | η      | PVDD=24V, R <sub>L</sub> =8Ω,<br>Po=10W    | _        | 87   | _    | %        |

|                             | IVIONO          |        | PVDD=12V, $R_L$ =4 $\Omega$ , Po=10W       | _        | 90   | _    | %        |

| Output Offset Voltage       | Stereo,<br>Mono | Vo     | _                                          | _        | 10   | 20   | mV       |

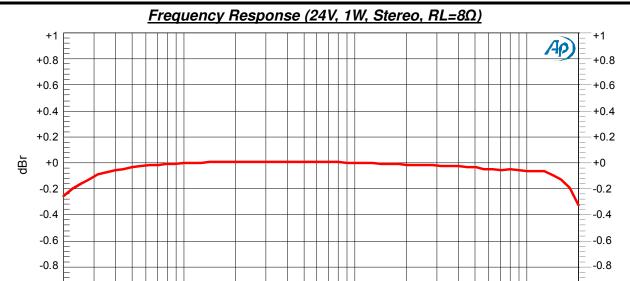

| Frequency Characteristics   | Stereo,<br>Mono | f      | 20Hz<br>20kHz                              | -1<br>-3 | 0    | 1    | dB<br>dB |

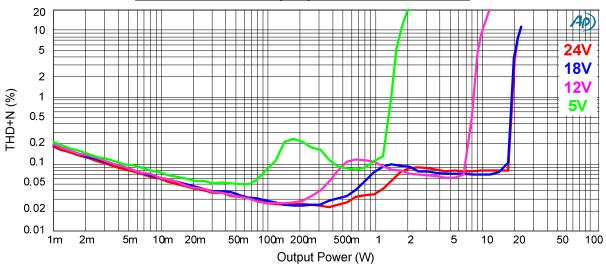

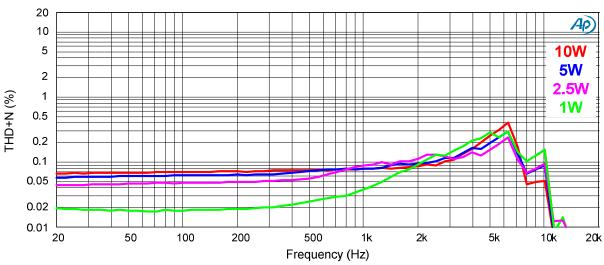

THD + N (%) v.s. Frequency (24V, Stereo, RL=8Ω)

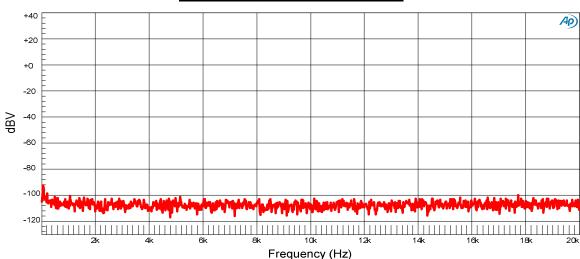

### Noise FFT (24V, Stereo, RL=8Ω)

-1 <del>-</del> 20

50

# 2x20W Stereo / 1x40W Mono Class-D Audio Amplifier With Power Limit Control

### Efficiency (Stereo, RL=8Ω)

Frequency (Hz)

500

2k

5k

10k

20k

200

100

### Efficiency vs. Output Power (Stereo)

### **Functional Block Diagram**

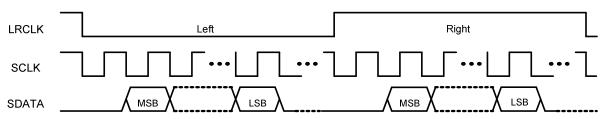

### **Interface Configuration**

I<sup>2</sup>S

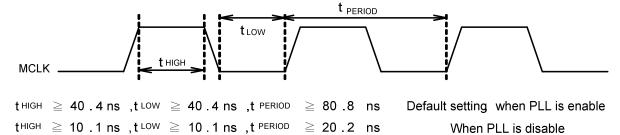

### System Clock Timing

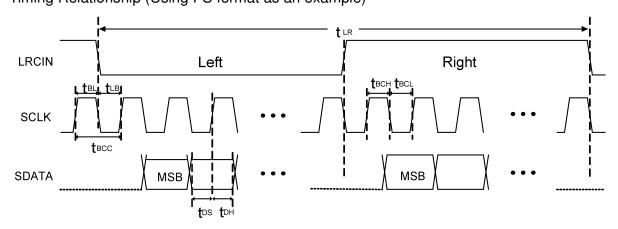

Timing Relationship (Using I<sup>2</sup>S format as an example)

| Symbol           | Parameter                         | Min    | Тур | Max   | Units |

|------------------|-----------------------------------|--------|-----|-------|-------|

| $t_{LR}$         | LRCLK Period (1/F <sub>S</sub> )  | 20.83  |     | 31.25 | μs    |

| t <sub>BL</sub>  | SCLK Rising Edge to LRCLK Edge    | 100    |     |       | ns    |

| t <sub>LB</sub>  | LRCLK Edge to SCLK Rising Edge    | 100    |     |       | ns    |

| t <sub>BCC</sub> | SCLK Period (1/64F <sub>S</sub> ) | 325.52 |     | 488.3 | ns    |

| t <sub>BCH</sub> | SCLK Pulse Width High             | 162.76 |     | 244   | ns    |

| t <sub>BCL</sub> | SCLK Pulse Width Low              | 162.76 |     | 244   | ns    |

| t <sub>DS</sub>  | SDATA Set-Up Time                 | 100    |     |       | ns    |

| t <sub>DH</sub>  | SDATA Hold Time                   | 100    |     |       | ns    |

### **Operation Descriptions**

The description below shows XA8123 functions and operations

### Digital Amplifier Modulation Method

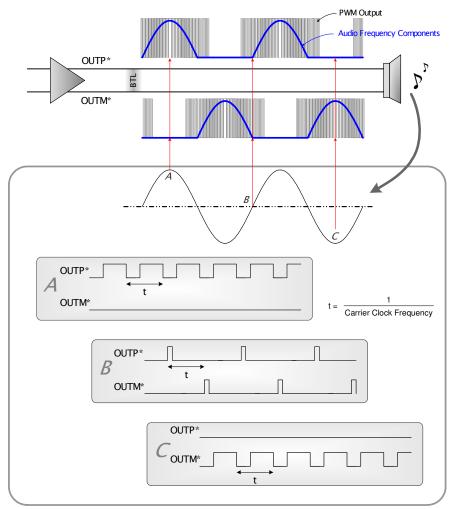

XA8123 has a 20W (Max.)×2ch digital amplifier with digital input and PWM pulse output. The pulse frequency that appears between OUTP\* and OUTM\* pins is called "Carrier Clock Frequency." The figure 1 below shows the output waveform for when a sine wave is input about the characteristics of modulation method. As shown in B of the figure, the frequency that appears between GND and OUTP\* pins and between GND and OUTM\* pins at no-signal input becomes the half of a carrier clock frequency. As shown in A, C of the figure, when the output power increases, one side stops its switching and the other serves as a carrier clock frequency.

Figure 1, Modulation Method with XA6123

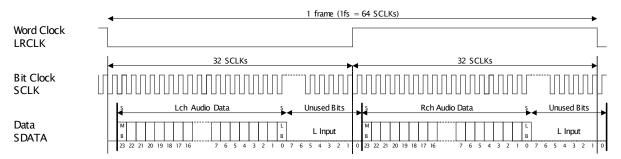

### • Digital Audio Interface

XA8123 receives digital audio data using SCLK, LRCLK, and SDATA pins. The following sampling frequencies are supported: 32kHz, 44.1kHz, and 48kHz

- Audio signal format: Left-justified format, MSB first, 1-bit delay, 24 bits.

- LRCLK and SDATA are loaded at the rising edge of SCLK.

- The number of valid SDATA bits is up to 24 bits.

- 24bit×2ch audio data are input through SDATA pin during one sample period. Fill the unused bits after 24th bit with "L" data.

Figure 2, Digital Audio Interface Timing

### • Carrier Clock Frequency Control Function

This is the function to set a carrier frequency with the following control pins. The way to control the frequency is as follows:

· LRCLK, SCLK and MCL pins

According to condition used, input clock to LRCLK, SCLK, and MCLK pins as shown in Table.

CKMOD pin

CKMOD pin is the clock mode setting pin. It should be set as shown in the table 1 according to MCLK frequency to input. Frequencies and pin settings other than the listed values are not available. MCLK frequency must be just an integral multiple of SCLK frequency. And, the frequencies must be derived from the same oscillator. There is no restriction about the phase relationship of MCLK and SCLK. To change SCLK and LRCLK frequencies, MUTEN pin must be set to "L". To change MCLK frequencies and CKMOD pin setting, SLEEPN pin must be set to "L" or power must be down.

| Table 1, Carrier Clock Frequency | Table 1, | Carrier | Clock | Fred | uency |

|----------------------------------|----------|---------|-------|------|-------|

|----------------------------------|----------|---------|-------|------|-------|

| Fs    | LRCLK(1fs) | SCLK(64fs) | MCLK  | MCLK | CKMOD   | Carrier Clock   |

|-------|------------|------------|-------|------|---------|-----------------|

| [kHz] | [kHz]      | [kHz]      | [kHz] | [Fs] | CKINIOD | Frequency [kHz] |

| 32    | 32         | 2048       | 24576 | 768  | L       | 768             |

| 32    | 32         | 2048       | 16384 | 512  | Ι       | 1024            |

| 32    | 32         | 2048       | 12288 | 384  | Н       | 768             |

| 44.1  | 44.1       | 2822.4     | 22579 | 512  | L       | 705.6           |

| 44.1  | 44.1       | 2822.4     | 11290 | 256  | H       | 705.6           |

| 48    | 48         | 3072       | 24576 | 512  | L       | 768             |

| 48    | 48         | 3072       | 12288 | 256  | н       | 768             |

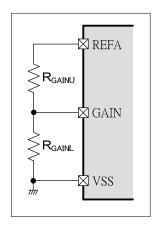

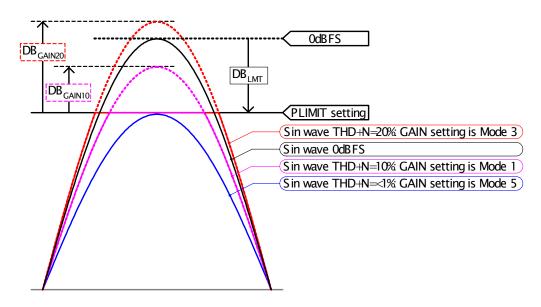

### Gain Setting function

Two discrete resistors on the GAIN pin select XA8123 amplifier gain from one of eight values. Gain setting circuit is shown below.

Figure 3, Gain Setting Circuit

The amplifier gain can be set to one of the three fixed levels ( $Mode\ 6$  through 8 in  $Table\ 2$ ), or a level that satisfies full scale output distortion figures of less than 1 %, or at 5 %, 10 %, 20 %, or 30 % ( $Mode\ 1$  through 5 in  $Table\ 2$ ). As an example, it becomes the following operations, when a GAIN pin is set as Mode 1 (THD+N=10%), PLIMIT2 pin is set as Mode 1, and PLIMIT1 pin is set as Mode H (Power limit setting is 10W, RL is 8  $\Omega$ ).

- If 0dBFS signal is inputted, output power is 10W (min) by THD+N 10%.

- If -20dBFS signal is inputted, output level is as follow.

4.81 + (DBLMT + DBGAIN10) = 4.81 - 6.86 + 2.473 = 0.423 [dBV]

To change GAIN pin setting, MUTEN pin must be set to "L" or power must be down. Table 2 shows digital amplifier gain setting.

Table 2 shows digital amplifier gain setting

| Mode |                    | Value Setting<br>% accuracy) | DB <sub>GAIN**</sub> [dB]    | Output level [dBV]<br>When –20dBFS input               | Power Limiter<br>bounded (at<br>the 0 dBFS<br>distortion |

|------|--------------------|------------------------------|------------------------------|--------------------------------------------------------|----------------------------------------------------------|

|      | R <sub>GAINU</sub> | R <sub>GAINL</sub>           |                              |                                                        | figure)                                                  |

| 1    | Short              | Open                         | DB <sub>GAIN10</sub> : 2.473 | 4.81 + (DB <sub>LMT</sub> + DB <sub>GAIN10</sub> ) *5) | 10%                                                      |

| 2    | 3.3kΩ              | 33kΩ                         | DB <sub>GAIN30</sub> : 9.159 | 4.81 + (DB <sub>LMT</sub> + DB <sub>GAIN30</sub> ) *5) | 30%                                                      |

| 3    | 10kΩ               | 27kΩ                         | DB <sub>GAIN20</sub> : 5.197 | 4.81 + (DB <sub>LMT</sub> + DB <sub>GAIN20</sub> ) *5) | 20%                                                      |

| 4    | 15kΩ               | 20kΩ                         | DB <sub>GAIN5</sub> : 1.376  | $4.81 + (DB_{LMT} + DB_{GAIN5})^{*5}$                  | 5%                                                       |

| 5    | 27kΩ               | 20kΩ                         | DB <sub>GAIN0</sub> : 0      | $4.81 + (DB_{LMT} + DB_{GAIN0})^{*5}$                  | <1%                                                      |

| 6    | 56kΩ               | 22kΩ                         | _                            | -1.19                                                  | _                                                        |

| 7    | 68kΩ               | 10kΩ                         | _                            | 10.81                                                  | _                                                        |

| 8    | Open               | Short                        | _                            | 4.81                                                   | _                                                        |

#### Note:

Gain setting resistors (RGAINU, RGAINL) draw current when not in sleep state (SLEEPN = "L").

The external resistance should use the above-mentioned value and the 1% accuracy.

\*5: DBLMT values are described in Table 4 Power Limiter Setting Example

Figure 4, Power Limiter bounded gain controls

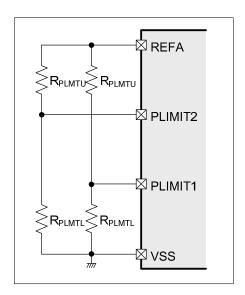

#### Power Limit function

This function, limiting the output peak voltage, protects an external speaker and controls the increase of internal temperature. *PLIMIT1* and *PLIMIT2* can be strapped to one of 8 *Modes* in *Table 3, A* through *H* and 1 through 8 respectively with two external resistors on each pin as shown in *Figure 5.* The combination of *PLIMIT1 Mode* and *PLIMIT2 Mode* configures 63 Power Limiter levels as shown in *Table 4.*

Figure 5, PLIMIT1 and PLIMIT2 pin setting circuit

Table 3, Power Limit Setting

| Mo          | ode         | Resistance Value Setting (E12 series 1% accuracy) |                    |  |

|-------------|-------------|---------------------------------------------------|--------------------|--|

| PLIMIT2 pin | PLIMIT1 pin | $R_{PLMTU}$                                       | R <sub>PLMTL</sub> |  |

| 1           | Α           | Short                                             | Open               |  |

| 2           | В           | 3.3kΩ                                             | 33kΩ               |  |

| 3           | С           | 10kΩ                                              | 27kΩ               |  |

| 4           | D           | 15kΩ                                              | 20kΩ               |  |

| 5           | E           | 27kΩ                                              | 20kΩ               |  |

| 6           | F           | 56kΩ                                              | 22kΩ               |  |

| 7           | G           | 68kΩ                                              | 10kΩ               |  |

| 8           | Н           | Open                                              | Short              |  |

Note: The external resistance should use the above-mentioned value and the 1% accuracy.

Table 4 shows sample Power Limiter levels using the Mode combinations. Power Limiter levels for 8  $\Omega$ , 6  $\Omega$ , or 4  $\Omega$  loads, and stereo or mono output configuration are shown. **Boldface** limits apply only for the operating PVDD = 12V.

Table 4, Power Limiter levels using the Mode combinations

|           |     |                    |             |                   | I Power I         |                   |                   | THD+N=           | 10%)               |                  |                   |

|-----------|-----|--------------------|-------------|-------------------|-------------------|-------------------|-------------------|------------------|--------------------|------------------|-------------------|

|           |     |                    | Load        | A                 | B                 | C                 | D                 | 18.              | P                  | G                | H                 |

|           |     |                    | 80          | 4.00W             | 0.30W             | 0.50W             | 0.7 OW            | 0.75W            | 1.00W              | 1.25W            | 10.00W            |

|           |     | Stereo             | 603         | 5.33W             | 0.40W             | 0.6FW             | 0.90W             | 1.00W            | 1.33W              | LSTW             | -                 |

|           |     |                    | 40          | 8.00W             | 0.60W             | 1.00W             | 1.40W             | 1.50W            | 2.00W              | 2.50W            | _                 |

|           | 1   |                    | 10          | 4.00W             | 0.30W             | 0.50W             | 0.70W             | 0.75W            | 1.00W              | 1.25W            | 10.00W            |

|           |     | Mono               | 60          | 3.33W             | 0.40W             | 0.GW              | USW               | 1.00W            | 1.33W              | 1.67W            | 13.33W            |

|           |     |                    | 40          | KINDW             | 0.60W             | LOW               | 1.40W             | 1.50W            | 2.00W              | 230W             | 20,00W            |

|           |     | DRIGHT             |             | -10.84dB          | -22.09dH          | -19.87dB          | -18.41dB          | -18.1149         | -16 B6dB           | -15.89dB         | -6.36dB           |

|           |     |                    | BO.         | 1.50W             | 0.23W             | 0.25W             | 0.35W             | 0.38W            | 0.53W              | DISDW            | 2.00W             |

|           |     | Stereo             | 60          | 2.00W             | 0.30W             | 0.33W             | 0.4TW             | 0.50W            | 0.70W              | 0.80W            | 2.6TW             |

|           | 2   |                    | 40          | 3.00W             | 0.45W             | 0.50W             | 0.70W             | 0.75W            | 1.05W<br>0.53W     | 1.20W            | 4.00W             |

|           | 2   | Mono               | NO.         | 1.50W<br>2.00W    | 0.23W<br>0.30W    | 0.25W<br>0.33W    | 0.35W<br>0.47W    | 0.38W<br>0.50W   | 0.70W              | 0.60W            | 2.00W<br>2.67W    |

|           |     | 1000000            | 40          | 3.00W             | 1.45W             | 15W               | 0.70W             | 0.75W            | L NW               | 1,20W            | 4.00W             |

|           |     | DB <sub>UM</sub> ) |             |                   |                   |                   |                   |                  |                    |                  |                   |

|           |     | ranifold.          | 80          | -15.10dB<br>2.25W | -23.34dH<br>0.65W | -22.88dB<br>0.83W | -21.42dB<br>0.90W | -21.12dh         | -19 66dB<br>1.7.5W | -19.08dB         | -13.85dB<br>2.50W |

| A         |     | Stereo             | 60          | 3.00W             | 0.87W             | 1.10W             | 1.20W             | 1.50W            | 2.33W              | 2.50W            | 3.33W             |

| 医         |     | 34230.0            | 40          | 4.50W             | 1.30W             | 1.63W             | 1.80W             | 2.25W            | 3.50W              | 3.75W            | 5,00W             |

| =         | 3   |                    | 80          | 2.25W             | 0.62W             | 0.EJW             | 0.90W             | 1.13W            | 1.7.5W             | LEEW             | 2.50W             |

| 廾         | 100 | Mono               | 60          | 3.00W             | 0.87W             | 1.10W             | 1.20W             | 1.50W            | 2.33W              | 2.50W            | 3.33W             |

| Ŧ         |     |                    | 40          | 4.50W             | 1.30W             | 1.65W             | 1.80W             | 2.25W            | 3.50W              | 3.75W            | 5.00W             |

| THD+N=10% |     | DRust              |             | -13.34dB          | -18.73dB          | -17.70dB          | -17.32dB          | -16.35dB         | -14.43dB           | -14.13dB         | -12.88dB          |

| E         |     |                    | 10          | 17.5W             | 2.63W             | 3.38W             | 4.13W             | 4.88W            | 5.50W              | 625W             | 3.00W             |

|           |     | Stere o            | 60          |                   |                   | 4.50W             | 3.50W             | 6.50W            | 7.37W              | 833W             | 4.00W             |

| .5        |     |                    | 40          | _                 | 3.50W<br>5.25W    | 675W              | 8.25W             | 9.75W            | _                  | _                | 6.0000            |

| (Min.,    | 4   |                    | 180         | 17.5W             | 2.63W             | 3.38W             | 4.13W             | 4009W            | 5.50W              | 625W             | 3.00W             |

| 625       |     | Mono               | 60          | 26.25W            | 3.50W             | 4.50W             | 5.50W             | 6.50W            | 7.33W              | 8.33W            | 4.00W             |

| E.        |     |                    | 40          | 35W               | 5.25W             | 6.75W             | 8.25W             | 9.75W            | 11.00W             | 12.50W           | 6.00W             |

| Setting   |     | Dilum)             | 201]<br>NO  | -4.43dB           | -12.67dH<br>6.38W | -11.5%db          | -10.71dB          | -9.98dB<br>7.13W | -9.46dB<br>8.25W   | -8 90dB<br>8.50W | -12.09dB<br>3.50W |

| 00        |     | Stere o            | 60          |                   | 8.50W             | B-GTW             | 9.33W             | 9.50W            |                    | 0.20             | 4.6TW             |

| Limit     |     |                    | 40          |                   |                   |                   |                   | _                |                    |                  | 7.00W             |

| 5         | 5   |                    | 100         | 18W               | 6.38W             | 6.53W             | 7.00W             | 7.13W            | K.25W              | 8.50W            | 3.50W             |

| 핕         |     | Mono               | 60          | 27W               | 8.50W             | LCW               | 9030W             | 930W             | 11.00W             | 11.33W           | 4.CTW             |

| 2         |     |                    | 40          | 36W               | 12.75W            | 13.00W            | 14.00W            | 14.25W           | 16.50W             | 17.00W           | 7.00W             |

| Power     |     | DB(um)             |             | -4.31dB           | - K K25B          | -8.73dB           | -8.41dB           | -8.33dB          | -7.70dB            | -7.57dB          | -11.4249          |

|           |     |                    | BΩ          | 4.25W             | 9.00W             | 9.50W             | 9.7.5W            | 10.50W           | 11.00W             | 11.25W           | 4.50W             |

| PLIMIT2   |     | Stereo             | 60          | 5.6TW             |                   |                   |                   |                  |                    |                  | 6.00W             |

| 묫         |     |                    | 49          | 8.50W             |                   |                   |                   |                  |                    |                  | 9.00W             |

|           | 6   | Marin              | 100         | 4.25W             | 9.00W             | 9.50W             | 9.75W             | 10.50W           | 11.00W             | 11.25W           | 4.50W             |

| 盂         |     | Mono               | 40          | 3.67W<br>8.50W    | 12,00W            | 12.67W            | 1300W             | 14 00W<br>21 00W | 14.67W             | 15.00W<br>22.50W | 6.00W<br>9.00W    |

|           |     | -                  |             |                   | 18.00W            | 19.00W            | 19.50W            |                  | 22.00W             |                  |                   |

|           |     | DRum               |             | -10.58dB          | -7.32MH           | -7.09dB           | -6.97dB           | -6.65dB          | -6.45dB            | -6.35dB          | -10.33dB          |

|           |     | Stereo             | ND<br>CD    | 20W               | 11.50W            | 13.00W            | 13.50W            | 14.00W           | 14.50W             |                  | 5.00W             |

|           |     | CARDIDO (I)        | 40<br>40    |                   |                   |                   |                   |                  |                    |                  | 6.67W             |

|           | 7   |                    | 30          | 20W               | 11.50W            | 13.00W            | 13.50W            | 14.00W           | 14.50W             | Reproved         | 5.00W             |

|           |     | Mono               | -85         | - 500             | 15.33W            | 17.33W            | 18,00W            | 18,0797          | 1933W              |                  | 6.67W             |

|           |     |                    | 40          | 40W               |                   | 26-00W            | 27.00W            | 28.00W           | 29 00W             |                  | 10,00W            |

|           |     | Distanti           | <b>5</b> 3] | -3.85dB           | -6.26dB           | -5.7268           | -5.5688           | -5.40dB          | -5.2588            |                  | -9.87dB           |

|           |     |                    | MO          | 3.75W             | 5.63W             | 6.00W             | 7.50W             | BLOOW            | 12.00W             | 12.50W           | 15.00W            |

|           |     | Stereo             | 60          | 5.00W             | 7.50W             | 8.00W             | 10.00W            | _                |                    | _                | -                 |

|           |     |                    | 40          | 7.50W             | 11,250            | 12.00%            | 15,000            |                  |                    |                  | _                 |

|           | 8   |                    | BO:         | 3.75W             | 5.63W             | 6.00W             | 7.50W             | KIDOW            | 12.00W             | 12.50W           | 15.00W            |

|           |     | Mono               | 60          | 5.00W             | 7.50W             | 8.00W             | 10.00W            | 10.67W           | 16.00W             | 16.6TW           | 20 00W            |

|           |     |                    | 40          | 7.50W             | 11.25W            | 12:00W            | 15.00W            | 16.00W           | 24.00W             | 25.00W           | 30.00W            |

|           |     | Dillam)            | in j        | -11.12dB          | -9.364B           | -9.08dB           | -8.11da           | -7.83dB          | -6.07dB            | -5.89dB          | -5.10dB           |

|           |     |                    |             |                   |                   |                   |                   |                  |                    |                  |                   |

Note: Power limit setting resistors ( $R_{PLMTD}$ ,  $R_{PLMTD}$ ) draw current when not in sleep state (SLEEPN = "L"). Parasitio DC resistances of signal traces and inductors are taken into account for each loading condition as follows. 8 $\Omega$  load: 0.10 $\Omega$ , 6 $\Omega$  load: 0.075 $\Omega$ , 4 $\Omega$  load: 0.05 $\Omega$ . Output power is the minimum value which taken into account for the above-mentioned parasitic DC resistance ingredient.

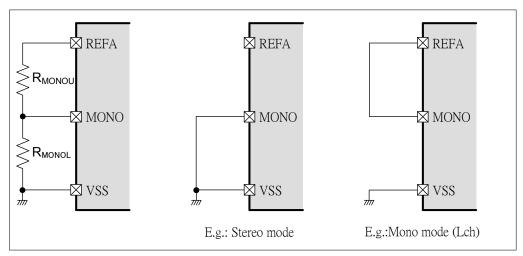

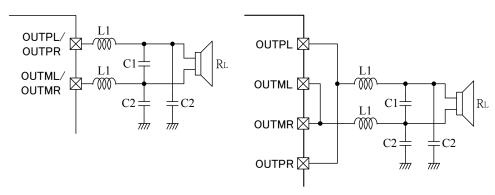

### Stereo / Mono mode Setting Function

XA8123 can be configured as stereo or mono amplifier by external resistors on MONO pin.

Figure 6, Mono pin setting circuit

XA81233 can be configured as stereo or mono amplifier by external resistors on *MONO* pin. For mono configuration, these resistors also determine which mono channel is used as the mono source. The source signal is amplified and put on both L- and R-channel outputs.

Table 5, Mono pin setting

| Mada                     | Resistance Value Setting (E12 series 1% accuracy) |                    |  |  |

|--------------------------|---------------------------------------------------|--------------------|--|--|

| Mode                     | R <sub>MONOU</sub>                                | R <sub>MONOL</sub> |  |  |

| Mono mode (Rch)          | 3.3kΩ                                             | 33kΩ               |  |  |

| Mono mode (Lch+Rch,-6dB) | 15kΩ                                              | 20kΩ               |  |  |

| Mono mode (Lch)          | Short                                             | Open               |  |  |

| Stereo mode              | Open                                              | Short              |  |  |

Note: Mono setting resistors ( $R_{MONOU}$ ,  $R_{MONOL}$ ) draw current when not in sleep state (SLEEPN = "L"). The external resistance should use the above-mentioned value and the 1% accuracy.

When using in stereo mode, this device should be connected as shown in "Stereo Mode" of application circuit. When using in monaural mode, OUTPL and OUTML should be connected to OUTPR and OUTMR respectively as shown in "Monaural Mode" of application circuit. Be sure to turn off the power before selecting stereo or monaural mode or making the appropriate connection.

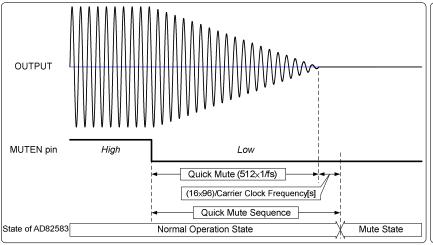

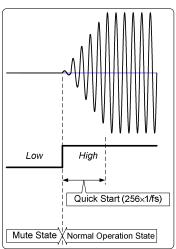

#### Quick Mute/Quick Start Function

Quick Mute/Quick Start function allows intermittent sound to be reduced significantly and uncomfortable feeling to be removed by varying the output envelope at a slow rate at the time of MUTE ON/OFF.

Table 6, MUTEN pin setting

| MUTEN pin | Mode                         |

|-----------|------------------------------|

| L         | Digital Amplifier Mute State |

| Н         | Normal Operation State       |

By setting MUTEN pin to "L", XA8123 performs Quick Mute operation (Decreasing the volume linearly by taking 512×1/fs), (16×96) / (carrier clock frequency)[s] later, it sets the digital amplifier output to WL (Weak Low: a state grounded through a high-value resistance), resulting in Mute state (Output Disabled).

By setting MUTEN pin to "H", XA8123 moves from the mute state to normal operation state while turned down volume. Afterwards, the quick start operation (where the volume is increased linearly over  $256 \times 1/fs$ ) is executed. Mute recovery time from Mute state is  $t_{mrcv}(Typ.)$ . If the mute state is cancelled during the Quick Mute Sequence, Quick Start Sequence will start after the quick mute sequence.

When the voltage at PVDD pin becomes lower than PVDD pin Shutdown Threshold Voltage (V<sub>HUVLL</sub>) in the mute state, for shutting down the system safely, the amplifier output is set to WL (Weak Low: a state grounded through a high-value resistance) after outputting a low signal for a given period of time.

Figure 7, Quick Mute and Quick Start

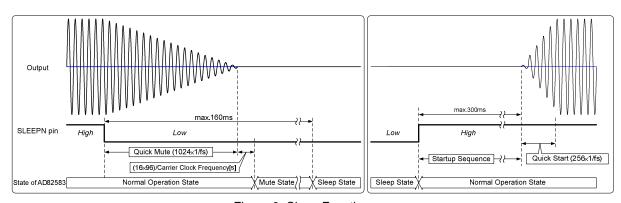

### Sleep Function

In Sleep state, all circuit functions are stopped and consumption current becomes the minimum (IDDPS). VREFA and VREFN pins outputs are pulled down, and VREFP pin is pulled high.

Table 7, SLEEPN pin setting

| SLEEPN pin | Mode                   |  |

|------------|------------------------|--|

| L          | Sleep State            |  |

| Н          | Normal Operation State |  |

By setting SLEEPN pin to "L", XA8123 performs Quick Mute operation (Decreasing the volume linearly by taking 1024×1/fs), (16×96) / (carrier clock frequency) [s] later, it sets the digital amplifier output to WL(Weak Low: a state grounded through a high-value resistance).

XA8123 goes to Sleep state when max.160ms has passed after setting SLEEPN pin to "L."

When going to sleep mode while some protection state is being activated, this protection mode is cancelled and PROTN pin output goes to Hi-Z state.

With PVDD pin output being higher than the threshold voltage to cancel the low-voltage malfunction preventing function, when changing the state of SLEEPN pin from "L" to "H," the digital amplifier terminates the sleep state, simultaneously starts the Startup Sequence and does the quick start (raises the volume level linearly by taking 256×1/fs) to activate the oscillation after max.300ms.

Figure 8, Sleep Function

#### DC-cut Function

XA8123 includes DC-cut filter (cut-off frequency=10Hz) for input digital audio data.

### Supply Voltage Regulation

XA8123 adopts a circuit method that feeds back the output signal. This method allows the deterioration in distortion characteristics to be minimized even when a supply voltage fluctuates (in case of a power supply not regulated). Whereas, with a non-feedback type digital amplifier, a power supply with high-regulation capability is required because this fluctuation is added to the output waveform.

### REFA Voltage Output Function

XA8123 includes series regulator. The voltage inputted from a PVDD power supply pin is supplied to a regulator. REFA pin outputs the voltage (VREFA) regulated from the voltage coming from PVDD pin. For its stabilization, connect a bypass capacitor of 1.0µF to 4.7µF between REFA and AVSS pins (0.8µF or more should be secured including its variation and temperature change.). REFA pin must not be connected to other devices.

### VREFN Voltage Output Function

The voltage inputted from a PVDD power supply pin is supplied to a regulator. VREFN pin outputs the voltage (VREFN) regulated from the voltage coming from PVDD pin. For its stabilization, connect a bypass capacitor of 1.0µF to 4.7µF between VREFN and VSS pins (0.8µF or more should be secured including its variation and temperature change.). VREFN pin must not be connected to other devices.

### VREFP Voltage Output Function

The voltage inputted from a PVDD power supply pin is supplied to a regulator. VREFP pin outputs the voltage (VREFN) regulated from the voltage coming from PVDD pin. For its stabilization, connect a bypass capacitor of  $1.0\mu\text{F}$  to  $4.7\mu\text{F}$  between VREFP and PVDDL(PVDDR) pins ( $0.8\mu\text{F}$  or more should be secured including its variation and temperature change.). VREFP pin must not be connected to other devices

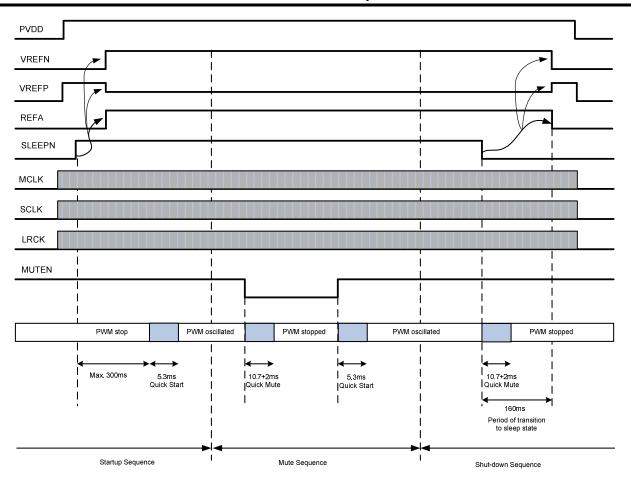

#### Digital Amplifier Startup/Shutdown Procedure

It is recommended to use the following sequences as digital amplifier start and shutdown procedure. With different sequence, unusual sound or pop noise may occur.

#### Recommended Digital Amplifier Startup Sequence

- 1. Supply the power to PVDD pin.

- 2. When the supply voltage reaches at the recommended voltage range, input clocks to MCLK, SCLK, and LRCLK pins.

- 3. Change the logical state of SLEEPN pin from "L" to "H".

#### Recommended Digital Amplifier Shutdown Sequence

- 1. Change the logical state of SLEEPN pin from "H" to "L".

- 2. After 160ms or more, stop input the signal to the input pins and shut down the power to PVDD pin.

- \* As long as SLEEPN pin was changed from "H" to "L" and Quick Mute {512×1/fs + (16×96) / (Carrier Clock Frequency) }[s]" has elapsed, unusual sound or pop noise is not generated even if the power is shut down.

### LC Filter

On the other hand, when using a LC filter, the output circuit as shown in Figure 10, 11 should be used with the constants listed in Table 8. The use of these constants enables the filter to be a low-pass filter with its cut-off frequency being 50kHz or so and Q being 0.6 or so. When disconnecting a speaker, turn off the power in advance. When operating the device without a speaker, consumption current may increase or over current detection circuit may work due to the resonance in LC filter. When removing a speaker during operation, SLEEPN or MUTEN pin should be set to "L" or PVDD should be shut down.

Figure 10, LC Filter Circuit (Stereo)

Figure 11, LC Filter Circuit (Mono)

| $R_{\rm L}$ | L1   | C1     | C2  | fc      | Q    |

|-------------|------|--------|-----|---------|------|

| $4\Omega$   | 10μΗ | 0.47μF | 1nF | 51.9kHz | 0.61 |

| 6Ω          | 15μΗ | 0.33µF | 1nF | 50.6kHz | 0.62 |

| 8Ω          | 22μΗ | 0.47μF | 1nF | 35kHz   | 0.82 |

| 16Ω         | 47μΗ | 0.1μF  | 1nF | 51.9kHz | 0.52 |

$$f_C = \frac{1}{2\pi\sqrt{L_1 \times (2 \times C_1 + C_2)}}$$

$$f_C(toGND) = \frac{1}{2\pi\sqrt{L_1C_2}}$$

$$Q = \frac{\sqrt{\frac{2 \times C_1 + C_2}{L_1}} \times R_L}{2}$$

When using XA8123 with a speaker connected directly without connecting LC filters, or when using it with EMI countermeasure components, such as ferrite beads etc., in addition to a speaker, a speaker with an inductance higher than 20µH should be used. Otherwise, loss of the speaker and XA8123 may increase.

### Protection Function

XA8123 has the following protection functions.

Table 9, Protection Function List

| Protection Function     | PROTN Pin<br>Output | Digital Amplifier<br>Output | Quick<br>Mute | Automatic Recovery              |

|-------------------------|---------------------|-----------------------------|---------------|---------------------------------|

| Over current Protection | L                   | WL (Note 7)                 | -             | Applicable (Note 5)             |

|                         |                     |                             |               | Not Applicable                  |

| Over Temperature        | L (Note 6)          | WL (Note 7)                 | _             | (However, it returns when       |

| Protection              | L (Note 0)          | VVL (INOIG 7)               | _             | the temperature                 |

|                         |                     |                             |               | decreases.)                     |

|                         |                     |                             |               | Not Applicable                  |

| Under Voltage Lock Out  | н                   | WL (Note 7)                 | _             | (However, it recovers from the  |

| (PVDD pin)              | ''                  |                             |               | lock out once the voltage level |

|                         |                     |                             |               | rise after startup sequence.)   |

|                         |                     |                             |               | Not Applicable                  |

| Over Voltage Lock Out   |                     | WL (Note 7)                 |               | (However, it recovers from the  |

| (PVDD pin)              | L (Note 6)          |                             |               | lock out once the voltage level |

| (I VDD piii)            |                     |                             |               | decrease after startup          |

|                         |                     |                             |               | sequence.)                      |

| DC Detection            | L                   | WL (Note 7)                 | -             | Applicable (Note 5)             |

| Clock Detection         |                     |                             |               | Not Applicable                  |

|                         | Н                   | WL (Note 7)                 | _             | (However, it returns when the   |