# XDP Hybrid-flyback Controller XDPS2201

# **Product Overview**

# **Product Highlights**

- Digital Hybrid-flyback controller with integrated half-bridge driver in DSO-14 (150mil) package

- 600V high voltage start-up cell for fast charging and low stand-by power

- Peak current mode control for robust and fast line and load control

- Burst mode entry/exit operation based on output current estimation

- Primary side output overvoltage protection

- Supports lowest no-load stand-by power < 75mW

- Wide range of configurable parameters via one pin UART interface

- Lowest necessary bill of material

# Features

- Configurable brown-in and brown-out protection

- Configurable built-in soft-start

- Configurable burst mode entry and exit current thresholds with small hysteresis

- Configurable overcurrent protection with two levels for peak and transient load

- Configurable output overvoltage protection

- Configurable frequency reduction with cycle skipping for improved low load efficiency

- Configurable jitter for switching frequency

- Configurable propagation delay compensation for accurate peak current control

- Pb-free lead plating; RoHS compliant

- Halogen-free according to IEC61249-2-21

# **Target Applications**

- AC/DC SMPS

- Ultra high power density adapter > 20W/inch<sup>3</sup>

- Ultra high efficiency SMPS > 93%

# **Product validation**

Qualified for industrial applications according to the relevant tests of JEDEC47/20/22.

# Description

The XDPS2201 contains a Hybrid-flyback controller that is based on an asymmetrical half-bridge control. The half-bridge is driving a conventional flyback transformer in conjunction with a serial capacitor. The main inductance of the flyback transformer and the serial capacitor are building a resonant tank, which is used for achieving zero voltage switching (ZVS) behavior of the half-bridge power switches and is providing in addition a resonant power transmission during the conventional demagnetization phase of the flyback transformer. During normal operation the charge period and associated power is controlled by direct peak current control, whereas the demagnetization phase is timing controlled to ensure proper negative premagnetization, which is required for ZVS condition at the half-bridge power switches. Beside the continuous resonant mode (CRM) operation the IC also provides an advanced zero voltage resonant valley switching (ZV-RVS) and burst mode to support highest efficiency over the whole load and wide output voltage range.

| Sales Code | Package   | SP-Ordering Code |

|------------|-----------|------------------|

| XDPS2201   | PG-DSO-14 | SP005417712      |

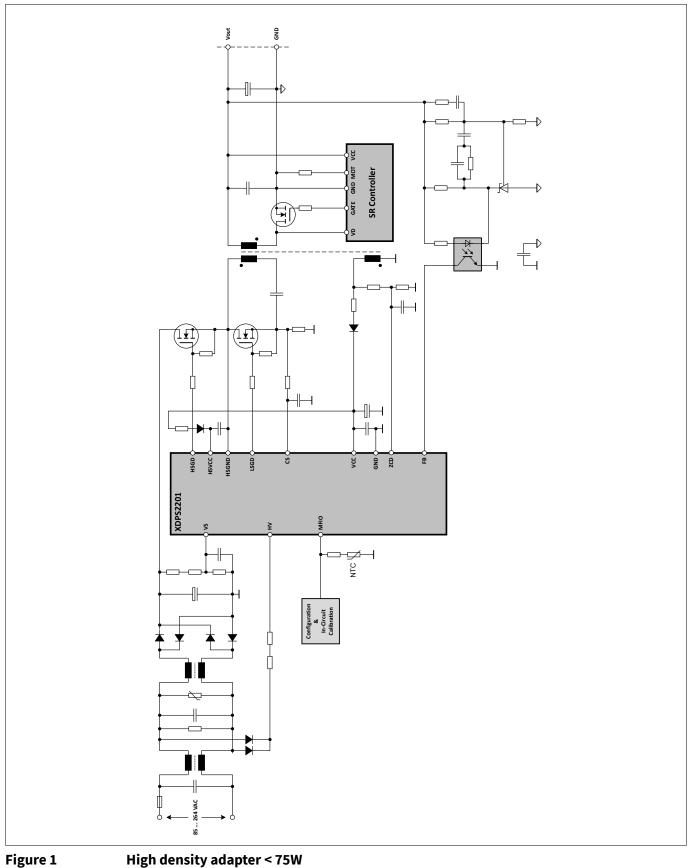

# **Typical Application**

# **Typical Application**

# Table of contents

# **Table of contents**

|           | Product Overview                                     |

|-----------|------------------------------------------------------|

|           | Product validation                                   |

|           | Description                                          |

|           | Typical Application                                  |

|           | Table of contents    3                               |

| 1         | Pin configuration                                    |

| 2         | Block diagram                                        |

| 3         | Functional description                               |

| 3.1       | Introduction                                         |

| 3.1.1     | Continuous resonant mode (CRM)10                     |

| 3.1.2     | Boundary conditions for ZVS operation13              |

| 3.1.3     | Zero voltage resonant valley switching mode (ZV-RVS) |

| 3.1.4     | Output control methods                               |

| 3.2       | Power supply management                              |

| 3.2.1     | VCC capacitor charge-up and start-up sequence        |

| 3.2.2     | Bang-bang mode operation during brown-in phase       |

| 3.2.3     | Bang-bang mode during protection mode operation      |

| 3.2.4     | VCC supply during burst mode (BM) operation          |

| 3.3       | Control features                                     |

| 3.3.1     | Output control                                       |

| 3.3.1.1   | Keeping ZVS operation for wide input voltage range   |

| 3.3.1.2   | Keeping ZVS operation for wide output voltage range  |

| 3.3.1.2.1 | Cycle by cyle ZVS operation during CRM operation     |

| 3.3.1.3   | Output current control law                           |

| 3.3.1.3.1 | Current control during CRM                           |

| 3.3.1.3.2 | Current control during ZV-RVS mode                   |

| 3.3.1.4   | Propagation delay compensation (PDC)                 |

| 3.3.2     | PWM control schemes                                  |

| 3.3.2.1   | CRM control scheme                                   |

| 3.3.2.2   | ZV-RVS control scheme                                |

| 3.3.2.2.1 | Valley skipping control                              |

| 3.3.2.3   | DCM control scheme                                   |

| 3.3.2.4   | Mode transition control                              |

| 3.3.2.5   | Overcurrent control                                  |

| 3.3.3     | Vout start-up control                                |

| 3.3.4     | Burst mode control                                   |

| 3.3.4.1   | Burst mode entry                                     |

# Table of contents

| 3.3.4.2   | Burst mode operation                                  |

|-----------|-------------------------------------------------------|

| 3.3.4.3   | Burst mode bootstrap precharge43                      |

| 3.3.4.4   | Burst mode exit control 44                            |

| 3.3.4.4.1 | Burst mode slow exit                                  |

| 3.3.4.4.2 | Burst mode fast exit                                  |

| 3.3.5     | Frequency jitter                                      |

| 3.3.6     | Half-bridge gate driver    47                         |

| 3.4       | Protection features                                   |

| 3.4.1     | Protection modes                                      |

| 3.4.2     | VCC undervoltage lockout (UVOFF) 50                   |

| 3.4.3     | HSVCC undervoltage lockout (HSUVOFF)50                |

| 3.4.4     | Input voltage Vin protection                          |

| 3.4.4.1   | Brown-in protection (BIP) 51                          |

| 3.4.4.2   | Fast brown-out protection (FBOP)51                    |

| 3.4.4.3   | Slow brown-out protection (SBOP)51                    |

| 3.4.4.4   | Vin overvoltage protection (VinOVP)51                 |

| 3.4.5     | Start-up timeout protection (STTOP) 52                |

| 3.4.6     | CS pin short circuit protection (CSSCP)52             |

| 3.4.7     | Overcurrent protection                                |

| 3.4.7.1   | Output overcurrent protection OCP1 level 1 (OCP1lev1) |

| 3.4.7.2   | Output overcurrent protection OCP1 level 2 (OCP1lev2) |

| 3.4.7.3   | Output maximum current protection (OCP1max)           |

| 3.4.7.4   | Primary peak overcurrent protection OCP2 (OCP2)       |

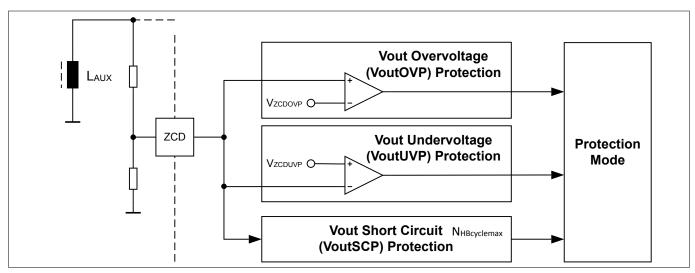

| 3.4.8     | Vout voltage protection                               |

| 3.4.8.1   | Vout undervoltage protection (VoutUVP)55              |

| 3.4.8.2   | Vout overvoltage protection (VoutOVP)56               |

| 3.4.8.3   | Vout short circuit protection (VoutSCP)56             |

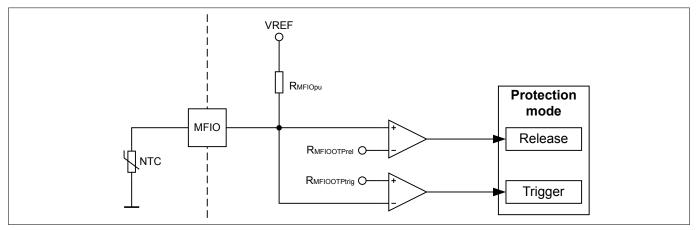

| 3.4.9     | External overtemperature protection (extOTP)56        |

| 3.4.10    | Watchdog timer                                        |

| 4         | <b>Configuration</b>                                  |

| 4.1       | Configurable parameters and functions57               |

| 4.1.1     | System settings                                       |

| 4.1.2     | Dimensioning                                          |

| 4.1.3     | Half-bridge                                           |

| 4.1.4     | ZV-RVS/DCM operation                                  |

| 4.1.5     | Burst                                                 |

| 4.1.6     | Start-up                                              |

| 4.1.7     | Protections                                           |

| 4.1.8     | Mode thresholds                                       |

| 4.1.9     | Jitter                                                |

| 4.1.10    | Others                                                |

# Table of contents

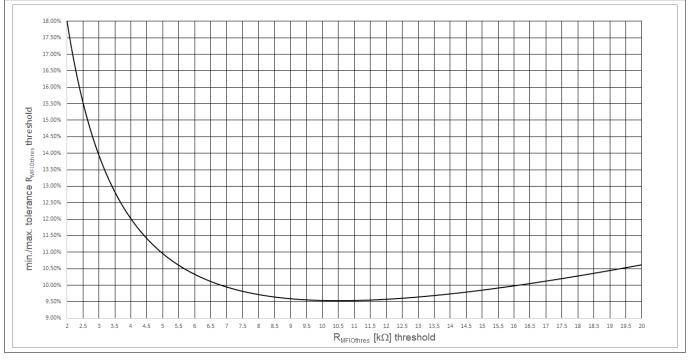

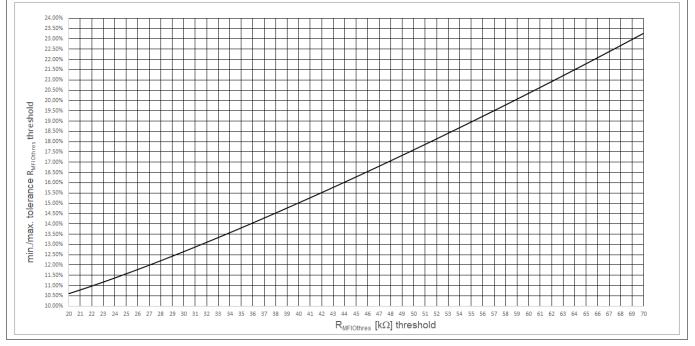

| 4.2 | Tolerance classes for configurable parameters    63 |

|-----|-----------------------------------------------------|

| 5   | Electrical characteristics                          |

| 5.1 | Definitions                                         |

| 5.2 | Absolute maximum ratings65                          |

| 5.3 | Package characteristics                             |

| 5.4 | Operating range                                     |

| 5.5 | DC electrical characteristics                       |

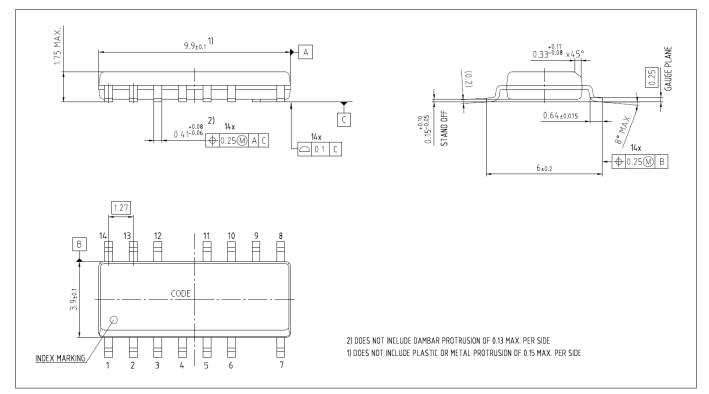

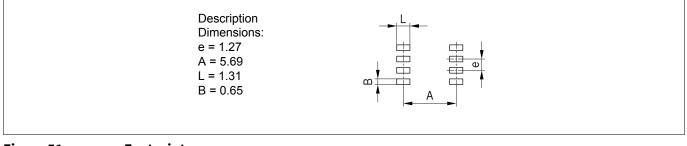

| 6   | Package dimensions    73                            |

|     | <b>Revision history</b>                             |

|     | <b>Disclaimer</b>                                   |

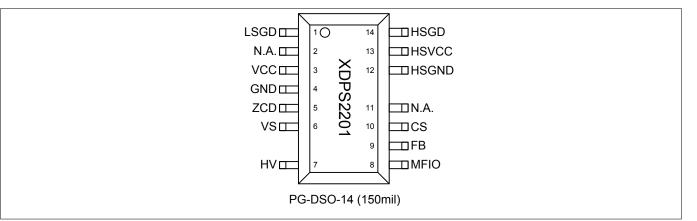

### **Pin configuration**

# 1 Pin configuration

The pin configuration is shown in *Figure 2* and *Table 1*. The pin functions are described in the sequel.

### Figure 2 Pin configuration

#### Table 1 Pin definitions and functions Pin Symbol Туре **Function** 1 0 LSGD Low-side gate driver Low-side gate driver of half-bridge driver stage N.A. 2 Not available This pin is internally connected but not used, and should be connected to GND VCC 3 I **Positive voltage supply** IC power supply GND 4 0 Ground Combined power and signal ground 5 I ZCD **Zero-crossing detection** ZCD pin provides zero-crossing detection after the low-side gate driver is turned off, during pause phase in skip cycle and burst mode. Furthermore, the reflected output voltage at auxiliary winding can be measured during the low-side gate driver turn-on phase VS 6 I **Voltage sensing** Low leakage input voltage sensing pin for controlling the negative magnetization and protections. VS pin is connected to a resistor divider for measuring the bulk voltage ΗV 7 I High-voltage input HV pin is connected to the AC line via external resistors and 2 diodes. An internally connected 600 V HV start-up cell is used for the initial VCC charge MFIO 8 10 Multi-functional input-output UART communication for parameter configuration and failure mode reporting is provided by this pin. In addition, a connected NTC can be measured FΒ 9 I Feedback Input pin receiving the feedback control signal from the optocoupler CS 10 I **Current sensing**

# Pin configuration

| Table 1Pin definitions and functions (continued) |     |      |                                                                                                          |  |

|--------------------------------------------------|-----|------|----------------------------------------------------------------------------------------------------------|--|

| Symbol                                           | Pin | Туре | Function                                                                                                 |  |

|                                                  |     |      | Input pin for current sensing during the high-side gate driver turn-on phase                             |  |

| N.A.                                             | 11  | _    | <b>Not available</b><br>This pin is internally connected but not used, and should be connected to<br>GND |  |

| HSGND                                            | 12  | 0    | High-side ground<br>Ground reference node for floating driver domain                                     |  |

| HSVCC                                            | 13  | I    | <b>High-side power supply</b><br>Power supply input for floating driver domain                           |  |

| HSGD                                             | 14  | 0    | <b>High-side gate driver</b><br>Floating high-side gate driver of half-bridge driver stage               |  |

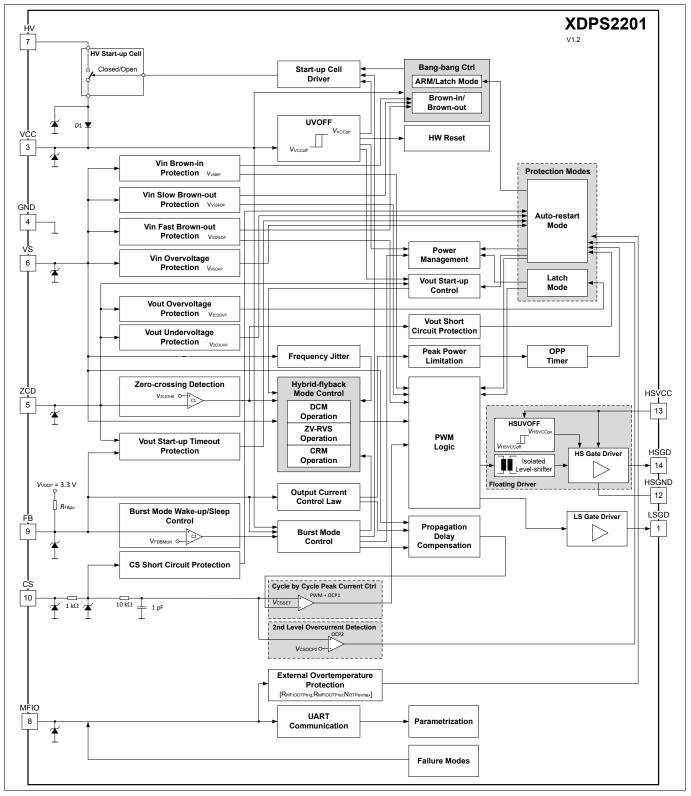

### **Block diagram**

# **3** Functional description

The functional description gives an overview about the integrated functions and features and their relationship. The mentioned parameters are based on either configurable parameters shown in *Chapter 4.1* or fixed parameters shown in *Chapter 5.5*.

This chapter contains following main descriptions:

- Introduction (*Chapter 3.1*)

- Power supply management (Chapter 3.2)

- Control features (Chapter 3.3)

- Protection features (Chapter 3.4)

# 3.1 Introduction

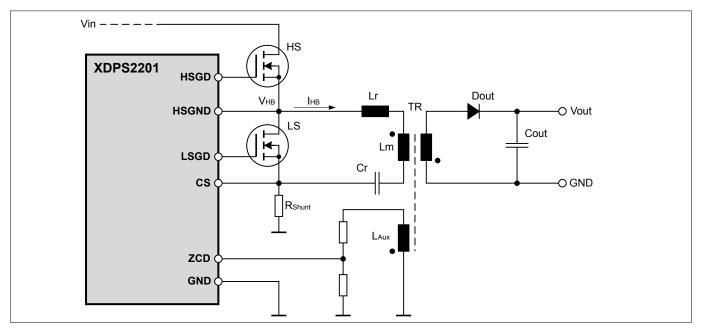

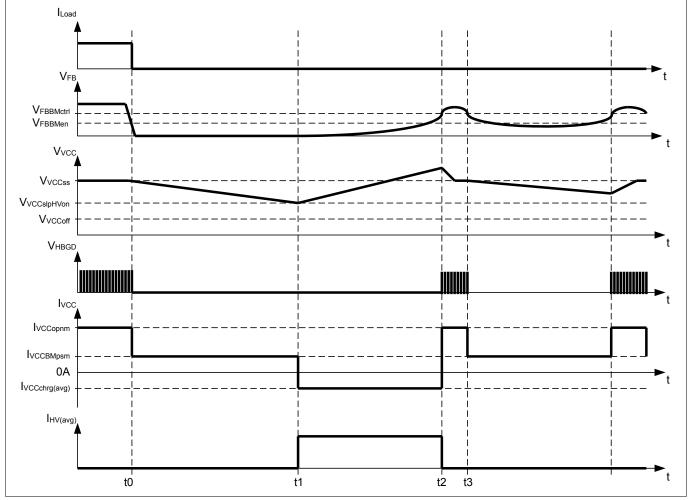

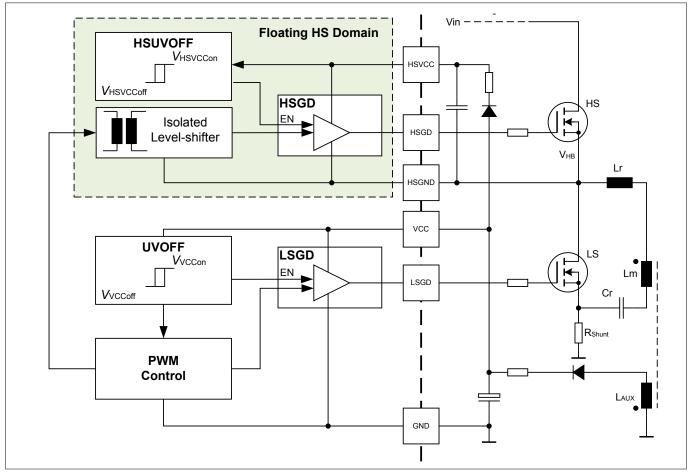

In the following a brief introduction is given for the hybrid-flyback converter, which is based on a resonant asymmetrical half-bridge flyback topology shown in *Figure 4*.

### Figure 4 Hybrid-flyback power stage

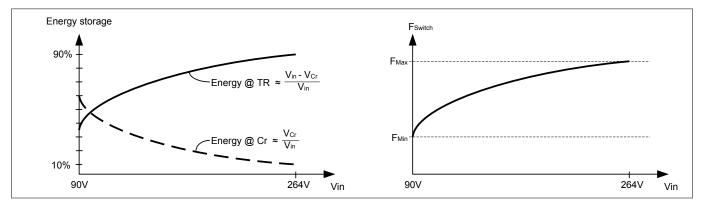

The main advantage of this hybrid-flyback topology is the extended energy storage approach, which enables the usage of a smaller transformer at the same switching frequency compared to the standard and active clamp flyback topologies. In hybrid-flyback the total energy is not only stored in the transformer. In addition an amount of energy is stored in an external capacitor *Cr*, which is connected in series with the transformer. The proportion of the amount of energy that is stored in transformer and capacitor is depending on the input voltage. For lower input voltage more energy is getting stored in the capacitor. The switching frequency is also depending on the input voltage similar to a critical conduction mode flyback operation (see *Figure 5*).

Hybrid-flyback energy storage sharing and switching frequency dependency

The resonant asymmetrical half-bridge flyback power stage can achieve zero voltage switching (ZVS) operation on primary side and zero current switching (ZCS) operation on secondary side under all conditions of input voltage *Vin* and output voltage *Vout*. The power circuit in the primary side is realized by an LC tank, built by the resonant inductor *Lr* and resonant capacitor *Cr*, which is driven by a half-bridge similar to an LLC converter. *Lr* represents the series inductance, being *Lr* either only the transformer leakage inductance or the leakage inductance plus an optional external inductor. With this configuration the transformer leakage energy is recycled avoiding the switching losses of traditional single switch flyback converter.

In order to achieve lowest switching losses by means of ZVS operation over the whole load range, two control methods are implemented to support maximum efficiency over wide *Vin*, wide *Vout* and whole output load ranges. The control methods are based on measured current signal  $V_{CS}$  at shunt resistor  $R_{Shunt}$ , voltage signal  $V_{ZCD}$  and valley detection  $N_{RVSval}$  at auxiliary winding  $L_{Aux}$  and input voltage *Vin*.

Following operating modes are supported by the two control methods for ensuring ZVS operation:

- Continuous resonant mode (CRM) operation (see Chapter 3.1.1)

- Zero voltage resonant valley switching (ZV-RVS) operation (see Chapter 3.1.3)

# 3.1.1 Continuous resonant mode (CRM)

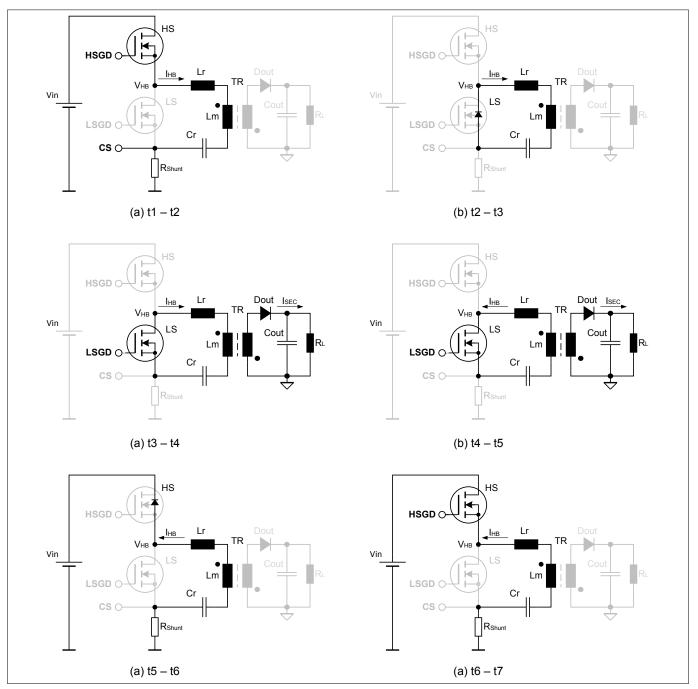

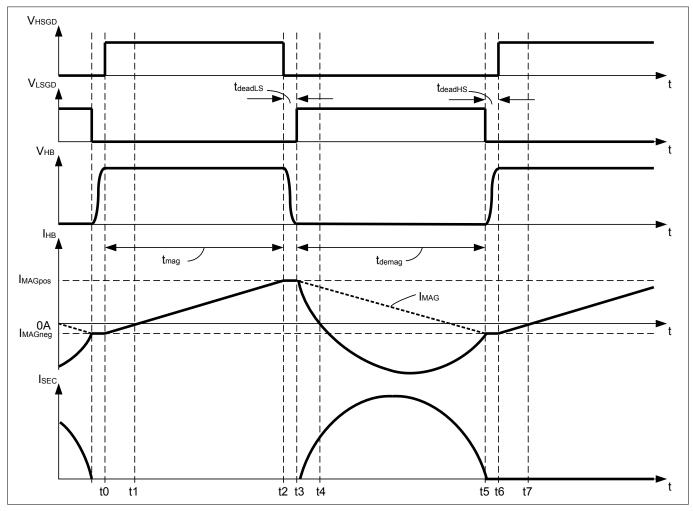

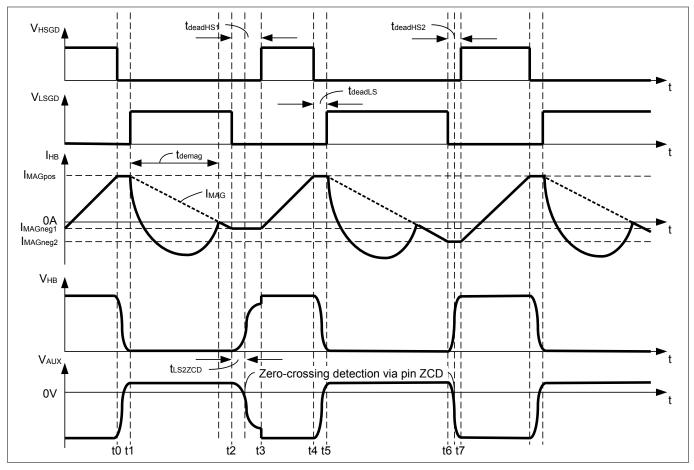

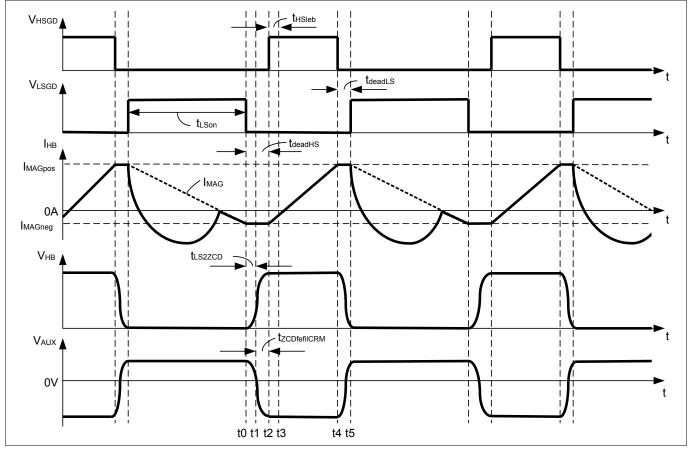

The operation phases of the resonant asymmetrical flyback duty cycle can be divided into 6 phases as shown in *Figure 6* and *Figure 7*. In continuous resonant mode (CRM) the switching of high-side switch *HS* and low-side switch *LS* is done in an alternating manner without blanking phases. Only short dead-times  $t_{deadHS}$  for the high-side switch turn-on and  $t_{deadLS}$  for the *LS* switch turn-on apply during the soft resonant switch-over of the half-bridge middle node.

Figure 6 Hybrid-flyback converter operation phases in CRM

### Phase 1, t1 to t2:

Phase 1 starts when the half-bridge current  $I_{HB}$  is changing in direction to a positive value. In this phase HS switch is turned on and LS switch is turned off since time t0. The increasing positive current  $I_{HB}$  is magnetizing the transformer TR and charging the resonant capacitor Cr. The output diode Dout is biased inversely blocking any energy transfer to the secondary side. The magnitude of  $I_{HB}$  is measured via the shunt resistor  $R_{Shunt}$ . Phase 1 is finished once  $I_{HB}$  exceeds an internal peak current set-point, which turns off the HS switch.

# Phase 2, t2 to t3:

At time t2 HS switch is also turned off, which disconnects the charging path from Vin. The magnetizing current  $I_{\text{HB}}$  in the transformer TR keeps flowing and forces the voltage at the half-bridge node  $V_{\text{HB}}$  to drop until the body diode of LS switch starts to conduct. At this time t3 the primary side of the transformer TR has the same voltage level as capacitor Cr.

# Phase 3, t3 to t4:

During phase 3 *HS* switch is kept turned off. At time *t*3 *LS* switch is turned on under zero voltage (ZVS) condition. The voltage at secondary winding of transformer *TR* is now equal to the voltage across the resonant capacitor *Cr*, divided by the transformer turns ratio. The secondary side current  $I_{SEC}$  starts flowing through output diode *Dout*. The resonant sine wave shape and period of  $I_{SEC}$  is determined by the resonant tank formed by the transformer *Lr* and *Cr*. The primary half-bridge current  $I_{HB}$  is the sum of the transformer *TR* magnetizing current  $I_{MAG}$  plus the reflected secondary side current  $I_{SEC}$ . The current in the resonant *LrCr* tank is still positive and mainly driven by the transformer magnetizing inductance *Lm*, which charges further the resonant capacitor *Cr*. In this manner the energy stored in the transformer and *Cr* is transferred to the output.

### Phase 4, t4 to t5:

Phase 4 starts when the primary side half-bridge current  $I_{\rm HB}$  inverts its direction, which is driven by the resonant *LrCr* tank. During this time period the energy is still being transferred to the secondary side. At the same time also bringing down the transformer magnetizing current  $I_{\rm MAG}$  to a negative level equivalent with  $I_{\rm MAGneg}$  is supported as long *LS* switch is kept turned on.

### Phase 5, t5 to t6:

At the beginning of phase 5 LS switch is also getting turned off. The negative current  $I_{MAGneg}$  in the transformer TR induced during the previous phase 4 is forcing the half-bridge bridge voltage  $V_{HB}$  to rise until clamping is taking place by the body diode of HS switch.

### Phase 6, t6 to t7:

Phase 6 starts with turning on HS switch at ZVS condition. As the transformer resonant tank LmCr current  $I_{MAG}$  is still negative the excess of energy in the tank is sent back to the input.

Figure 7 Hybrid-flyback converter signals

# 3.1.2 Boundary conditions for ZVS operation

Achieving a zero voltage switching (ZVS) turn-on condition for both *HS* and *LS* switches requires the right polarity of the resonant tank *LmCr* current  $I_{MAG}$ . Furthermore a sufficient energy level in the resonant tank *LmCr* is needed to switch-over the half-bridge voltage  $V_{HB}$  during the dead-times  $t_{deadLS}$  and  $t_{deadHS}$ . By ensuring ZVS operation, hard switching with undesired oscillations and, in worst case, body diode cross conduction can be properly avoided.

Switching over from *HS* switch to *LS* switch under ZVS condition is properly supported by the positive magnetization level (see *Figure 7*). Forcing ZVS condition for switch-over from *LS* switch to *HS* switch is covered by regulating the negative magnetization level depending on the input voltage *Vin*.

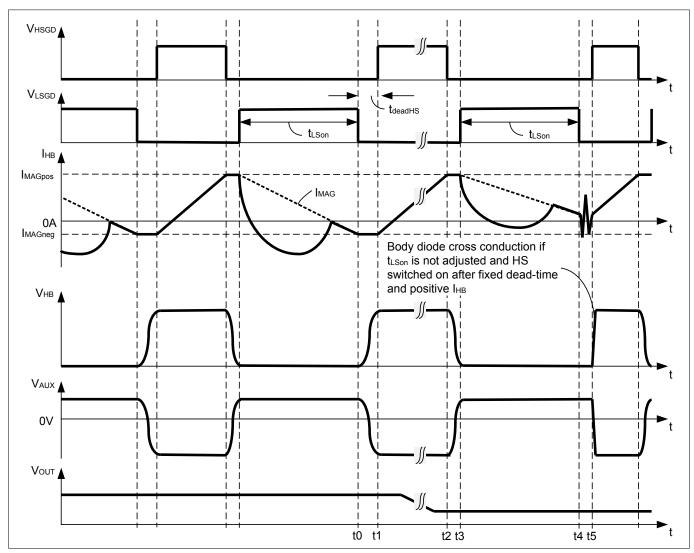

### Wide Vout voltage range operation

When operating with variable output voltage there is an application requirement for adapting the switching phase between HS switch turn-on phases to ensure ZVS condition. *Figure 8* shows an example for a potential body diode cross conduction when output voltage is reduced and the timings for *LS* switch turn-on phase  $t_{LSon}$  and start of *HS* turn-on are not adapted. At time t3 the slope of demagnetization current  $I_{MAG}$  is flatter compared to time period before t0 due to lower *Vout* level. This leads to a larger demagnetization period  $t_{demag}$  of the transformer (see *Equation 7*). Keeping the pulse pattern for  $t_{LSon}$  and dead-time  $t_{deadHS}$  for turning on the *HS* switch constant would result in a body diode cross conduction of *LS* switch at time t5 (see *Figure 8*). Here  $I_{MAG}$  is still positive and therefore not switching-over the half-bridge node and not finishing the conduction of the *LS* switch body diode. By adapting the pulse pattern depending on *Vout* ZVS condition is reached for all output voltage and load conditions (see *Chapter 3.3.1.2.1*).

Body diode cross condunction at low Vout and fixed LS switch on-time

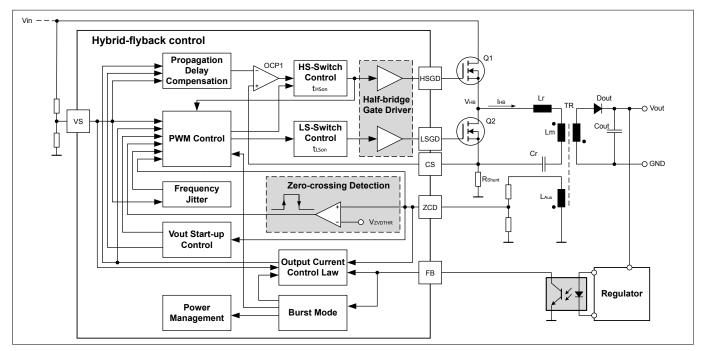

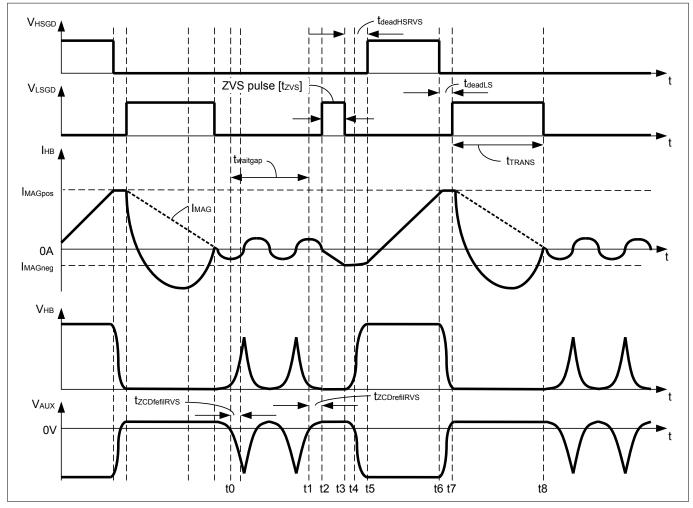

# 3.1.3 Zero voltage resonant valley switching mode (ZV-RVS)

When decreasing the load the amount of circulating magnetization energy is proportionally increasing compared to the transmitted energy in CRM operation. When decreasing *Vout* the demagnetization time is becoming longer than half of the resonant period of the *LrCr* tank, which can lead to further resonant half-bridge oscillations. Turning off the *LS* switch during an ongoing *I*<sub>HB</sub> oscillation can lead to oscillations on the secondary side due to the secondary side leakage inductance.

The higher circulation half-bridge current at low output load is limiting the achievable efficiency in CRM operation.

To overcome the mentioned issues the zero voltage resonant valley switching (ZV-RVS) mode is implemented to fix the peak to peak magnetization current and support a frequency foldback operation to reduce the average amount of circulating magnetization current.

ZV-RVS mode is based on valley detection of the signal at auxiliary winding  $L_{AUX}$  via ZCD pin zero-crossing detection. The free-wheeling oscillation, which is observed after demagnetization of transformer has finished, is the same as seen in the standard flyback topology. *Figure 4* shows the auxiliary winding  $L_{AUX}$  used for zero-crossing detection, the falling edge indicating a rising half-bridge voltage  $V_{HB}$  and vice versa.

For optimum operation a waiting time gap  $t_{waitgap}$  is introduced after a *HS* and *LS* switching cycle, which increases the associated half-bridge switching period. The time period  $t_{waitgap}$  is depending on the set number

for skipping valley detection before the next zero-crossing rising edge detection leads to a dedicated ZVS pulse. The number of skipped valleys is increasing with decreasing output load. After the ZVS pulse only one *HS* and *LS* half-bridge switching cycle with subsequent  $t_{waitgap}$  is performed. The ZVS pulse is generated by turning on *LS* switch under ZVS condition and forcing a negative half-bridge current level  $I_{MAGneg}$  to create a negative magnetization of the transformer. This leads to the same ZVS condition for turning on *HS* switch similar to CRM operation (see *Chapter 3.1.1*).

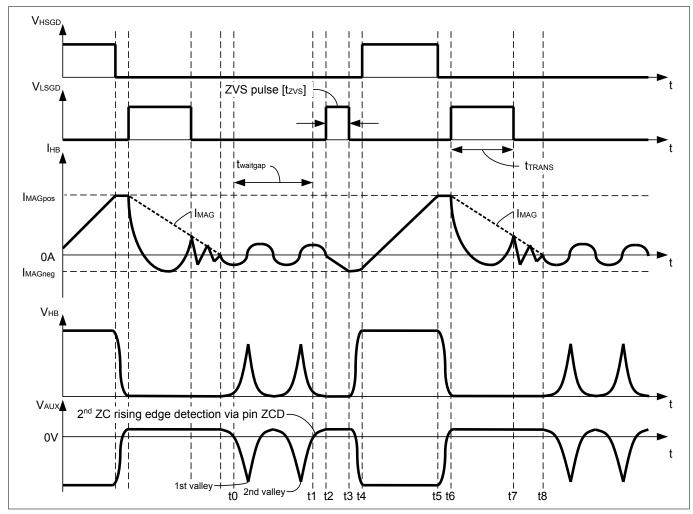

The operation can be divided into 8 phases as shown in Figure 9.

### Phase 1, t0 to t1:

Phase 1 starts with finishing the demagnetization of the transformer. In this phase both switches are kept turned off and the half-bridge current  $I_{HB}$  is only determined by the free-wheeling oscillation due to parasitic capacities and inductivities connected to the half-bridge node. Phase 1 ends with a zero-crossing rising edge detection, which is depending on the set valley skipping number. A zero-crossing rising edge detection via *ZCD* pin indicates that  $V_{HB}$  is dropping to 0V as base for reaching ZVS condition for turning on *LS* switch.

### Phase 2, t1 to t2:

Phase 2 is a predefined delay time for turning on *LS* switch after the zero-crossing rising edge detection at time t1. The predefined delay time is depending on the free-wheeling oscillation period and provides ZVS condition for  $V_{\rm HB}$ .

### Phase 3, t2 to t3:

At time t2 *LS* switch is turned on under ZVS condition. *HS* switch is still kept turned off. The voltage on the resonant capacitor *Cr* is applied to the primary winding of the transformer forcing a negative flowing half-bridge current level  $I_{\text{HBneg}}$ , which magnetizes the transformer in the negative direction. The injected current during ZVS pulse on-time  $t_{\text{ZVS}}$  needs to provide the right amount of energy for switching over the half-bridge node voltage  $V_{\text{HB}}$ .

Note: Depending on the voltage of the resonant capacitor Cr and the output capacitor Cout, a secondary side synchronous controller (SR) may get triggered at the same time when ZVS pulse is generated. To avoid a shoot-through with SR controller being turned on when subsequently turning on HS switch, the minimum on-time of the SR controller must be shorter than the minimum pulse width of ZVS pulse t<sub>ZVS</sub> (see **Figure 29**).

### Phase 4, t3 to t4:

At time t3 *LS* switch is turned off. The negative half-bridge current keeps flowing and pulls up the half-bridge node. Once the half-bridge voltage  $V_{\rm HB}$  is clamped by the body diode in *HS* switch ZVS condition is reached for turning on *HS* switch. Phase 4 is similar to the phase 5 in *Chapter 3.1.1*.

### Phase 5, t4 to t5:

At time t4 *HS* switch is turned on. Once the half-bridge current  $I_{HB}$  changes in polarity, energy is taken from the input capacitor and stored in the transformer and the resonant capacitor *Cr*.  $I_{HB}$  is rising and increasing the voltage at *Cr*. During this phase the secondary diode is inversely polarized and blocking a flowing current.

### Phase 6, t5 to t6:

At time t5 *HS* switch is turned off. The half-bridge current  $I_{HB}$  keeps flowing and decreases the half-bridge voltage  $V_{HB}$  down to 0V, leading to ZVS condition for *LS* switch.

### Phase 7, t6 to t7:

In phase 7 the main energy transmission to the secondary side is taking place. Once the half-bridge current *I*<sub>HB</sub> starts to decrease, the secondary side diode *Dout* is getting forward polarized and charging the output capacitor *Cout*. *I*<sub>MAG</sub> is then demagnetizing the transformer. In addition a resonant current is superimposed, which is generated by the transformer leakage inductance and the resonant capacitor acting as resonant tank *LrCr*. As *Lr* is significant smaller than *Lm* the resonant period of *LrCr* tank is much shorter and can be seen as an oscillation. The very large resonant period of *LmCr* tank can be seen as a linear decrease of magnetizing current in this relative short time phase.

# Phase 8, t7 to t8:

Phase 8 shows an example of the half-bridge current signal when the *LrCr* tank half resonant period is shorter than the demagnetization phase at *LS* switch turn-off. This shape of current is depending on the operation conditions determining the demagnetization period and low-side on-time. At time t8 the demagnetization of the transformer is finished. The secondary side diode *Dout* is again inversely polarized and the free-wheeling oscillation at the half-bridge node is starting.

# 3.1.4 Output control methods

### **Output current control in CRM**

The hybrid-flyback topology can be controlled either by duty cycle control or a combination of peak current control for *HS* switch and on-time control for *LS* switch. When looking on duty cycle control for *HS* switch a relationship between output voltage  $V_{out}$  and input voltage  $V_{in}$  is given as shown in the following equation. All equations in the sequel are based on considering ideal lossless components and neglecting any dead-times.

$$V_{\text{out}} = D \times \frac{V_{\text{in}}}{N} \times \frac{L_m}{L_m + L_r}$$

**Equation 1** The duty cycle *D* is determined by

$$D = \frac{t_{\rm HSon}}{t_{\rm HSon} + t_{\rm LSon}}$$

#### **Equation 2**

with  $t_{HSon}$  and  $t_{LSon}$  being the on-times for HS and LS switches. N represents the winding turns ratio between primary and secondary side of the transformer.

**Equation 1** shows that V<sub>out</sub> is independent of the output current I<sub>out</sub>.

Same as for standard flyback controllers primary peak current control is implemented to support a  $1^{st}$  order system for easier control loop compensation. The taken input power per half-bridge switching cycle is depending on the voltage at the resonant capacitor *Cr* that is charged by the half-bridge current *I*<sub>HB</sub> during the on-time *t*<sub>HSon</sub>. The input power can be calculated as shown in the following equation.

$$P_{\rm in} = \frac{1}{2} \times V_{\rm Cr_avg} \times (I_{\rm MAGpos} + I_{\rm MAGneg})$$

### **Equation 3**

$V_{Cr_{avg}}$  is the average voltage on the resonant capacitor Cr, which is the reflected output voltage  $V_{out}$  multiplied with the transformer turns ratio. The output voltage is reflected at winding  $L_{AUX}$  during the on-time period of LS switch.

$$V_{\rm Cr avg} = N \times V_{\rm out}$$

#### **Equation 4**

Assuming an ideal system with no losses, the taken output power  $P_{out}$  can be seen as the transferred input power  $P_{in} = P_{out}$ . Both leads to a direct correlation between input half-bridge current  $I_{HB}$  and average output current  $I_{out}$  as shown following.

$$I_{\text{out}} = \frac{P_{\text{out}}}{V_{\text{out}}} = \frac{1}{2} \times N \times (I_{\text{MAGpos}} + I_{\text{MAGneg}})$$

### **Equation 5**

**Equation 5** shows that  $I_{out}$  can be controlled only by controlling  $I_{MAG}$  and can then be independent of *Vin* and *Vout*. This is different compared to a standard flyback controller, where by means of peak current control the output power  $P_{out}$  is controlled independent on output voltage.

The hybrid-flyback is controlling the magnetization time  $t_{mag}$  and demagnetization time  $t_{demag}$  (see *Figure* 7) in 2 different ways.  $t_{mag}$  is mainly controlled by the positive half-bridge current level  $I_{MAGpos}$  by means of peak current control at shunt resistor  $R_{shunt}$  via *CS* pin. Whereas  $t_{demag}$  is controlled by adjusting the on-time  $t_{LSon}$ . Increasing  $t_{demag}$  increases the negative magnetizing current level  $I_{MAGneg}$  when keeping  $I_{MAGpos}$  level constant. During output overcurrent condition  $t_{demag}$  can be temporarily longer than  $t_{LSon}$  due to waiting for the zerocrossing detection before turning on the *HS* switch. The correlations between  $t_{mag}$ ,  $t_{demag}$  and  $I_{MAGpos}$ ,  $I_{MAGneg}$  are shown in following equations:

$$t_{\rm mag} = \frac{L_m \times \left(I_{\rm MAGpos} - I_{\rm MAGneg}\right)}{V_{\rm in} - V_{\rm Cr_avg}}$$

### **Equation 6**

$$t_{\rm demag} = \frac{L_m \times \left(I_{\rm MAGpos} - I_{\rm MAGneg}\right)}{N \times V_{\rm out}}$$

**Equation 7**

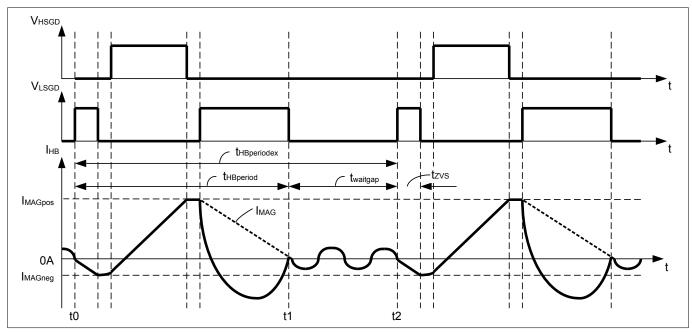

### Output current control in ZV-RVS mode

Compared to CRM operation the ZV-RVS mode is adding waiting time gaps  $t_{waitgap}$ , where no energy is either taken from the input nor energy is transferred to the output. This extends the minimum off-time, which is determined by the on-time of the *LS* switch. The average output current  $I_{out}$  is decreasing with increasing  $t_{waitgap}$  derived by following equation from *Figure 10*. This provides 2 degree of freedom to control the output current by means of half-bridge current  $I_{HB}$  and extended half-bridge switching period  $t_{HBperiodex}$  adjustment.

$$I_{\text{out}} = \frac{P_{\text{out}}}{V_{\text{out}}} = \frac{t_{\text{HBperiod}}}{t_{\text{HBperiodex}}} \times \frac{1}{2} \times N \times \left(I_{\text{MAGpos}} + I_{\text{MAGneg}}\right)$$

#### **Equation 8**

LrCr tank and I<sub>MAG</sub> currents during ZV-RVS mode operation

# 3.2 Power supply management

The power supply management ensures a reliable and robust IC operation. Depending on the operation mode of the control IC, the power supply management unit runs in different ways for VCC supply, which are described as in the sequel.

- VCC capacitor charge-up and start-up sequence (Chapter 3.2.1)

- Bang-bang mode operation during brown-in phase (*Chapter 3.2.1*)

- Bang-bang mode operation during protection mode (*Chapter 3.2.3*)

- VCC supply during burst mode (BM) operation (*Chapter 3.2.4*)

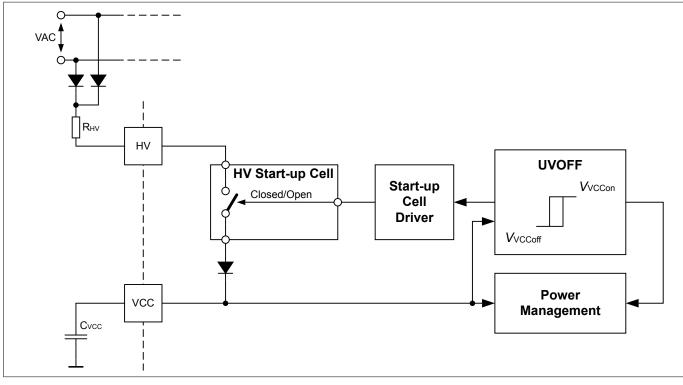

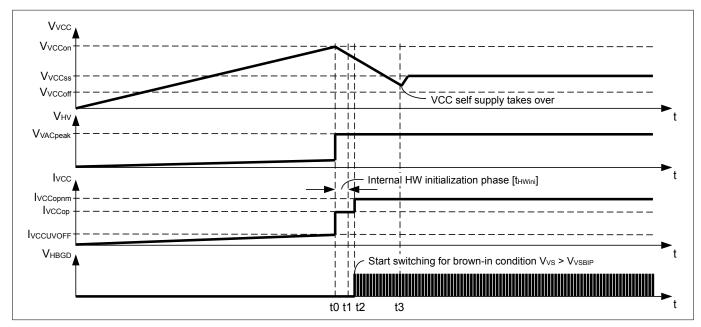

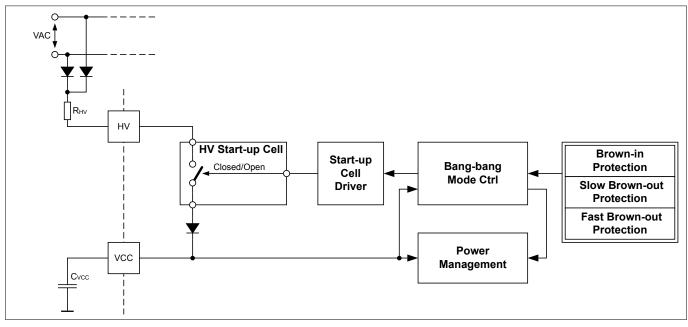

# 3.2.1 VCC capacitor charge-up and start-up sequence

At VCC start-up the capacitor  $C_{VCC}$  is being charged by the internal HV start-up cell via *HV* pin (see *Figure 11*). The high voltage *HV* pin is connected to an external resistor  $R_{HV}$ , which is in series with 2 diodes connected to *VAC*. The internal HV start-up cell is turned on for  $V_{VCC}$  lower than the IC deactivation voltage threshold  $V_{VCCoff}$  (see *Chapter 3.4.2*). Once the voltage at *VCC* pin exceeds the threshold  $V_{VCCon}$  at time *t0* the HV start-up cell is turned off and the IC is starting the internal hardware initialization procedure (see *Figure 12*). Subsequently the IC starts with half-bridge gate driver operation after brown-in condition is reached at time *t2* (see *Chapter*

**3.4.4.1**). During this period of time the VCC capacitor is discharging until the external VCC self-supply takes over at time *t3* and start regulating the voltage at VCC pin for V<sub>VCCss</sub>.

VCC capacitor charge-up control

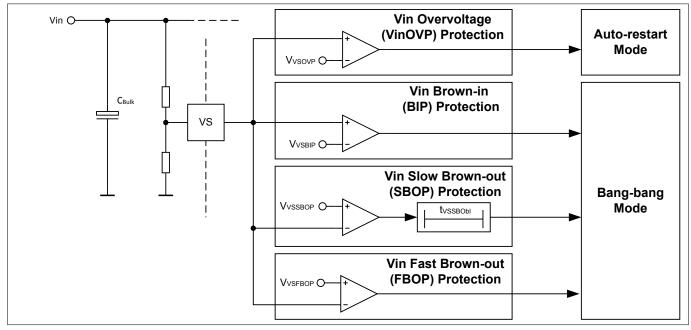

# 3.2.2 Bang-bang mode operation during brown-in phase

During brown-in phase the IC is observing the voltage at VS pin for reaching Vin brown-in condition. During this time VCC is not yet self-supplied via the transformer. To support a fast activation of switching operation when Vin brown-in condition is getting reached, the VCC voltage needs to be kept at a high level to support immediate operation with having enough time for take-over by VCC self-supply. A bang-bang mode operation

for *Vin* brown-in phase is ensuring a high VCC level, which can be either triggered by *Vin* brown-in protection or the fast and slow *Vin* brown-out protection (see *Figure 13* and *Chapter 3.4.4*).

#### Figure 13 Bang-bang mode triggered by brown-in and brown-out

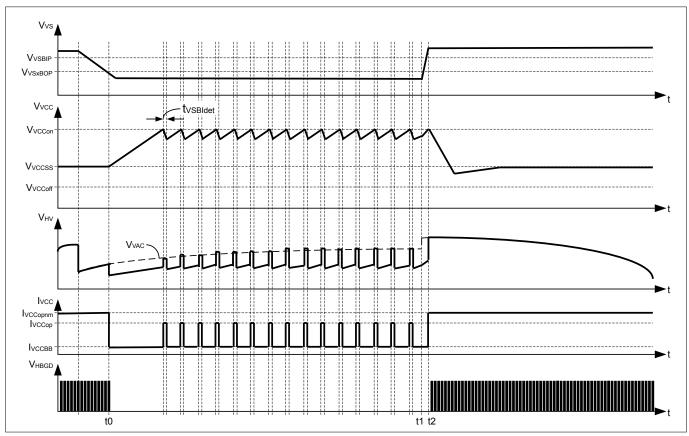

**Figure 14** shows the bang-bang mode operation after a brown-out detection event. Once brown-out is detected at time t0 the IC enters immediately a sleep mode with reduced current consumption  $I_{VCCBB}$ . The HV start-up cell turns on and charges up the VCC voltage until the threshold  $V_{VCCon}$ . Then the IC is activated for a time period  $t_{VSBIdet}$  in order to detect a *Vin* brown-in condition. Subsequently the IC is entering again the sleep mode. At time t1 *Vin* brown-in condition is reached but the IC is still inactive. The IC is detecting the *Vin* brown-in condition after being activated with VCC exceeding  $V_{VCCon}$  at time t2.

Figure 14 Bang-bang mode operation during brown-in phase

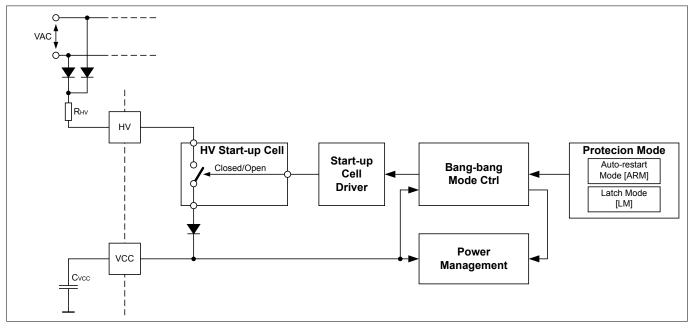

# 3.2.3 Bang-bang mode during protection mode operation

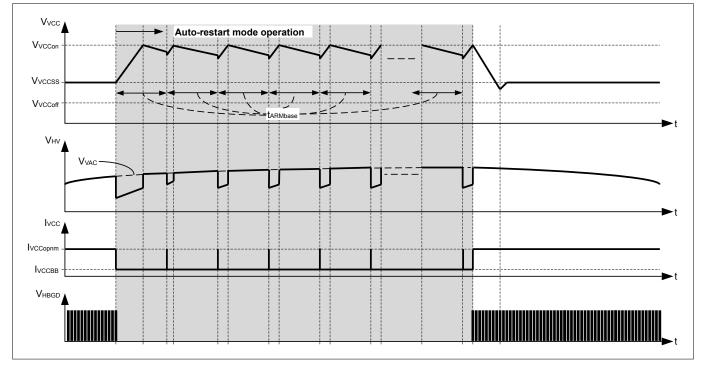

The bang-bang mode triggered by auto-restart mode or latch mode supports an IC operation without external VCC supply during the latched and auto-restart operation (see *Chapter 3.4.1*). It directly controls the HV start-up cell by turning off at *VCC* pin threshold  $V_{VCCon}$  and turning on after a time period  $t_{ARMbase}$  (see *Figure 15*). During this bang-bang mode operation the VCC is kept at a high voltage level in order to support a proper restart, once triggered. The VCC current consumption is reduced to  $I_{VCCBB}$ .

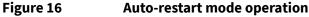

In auto-restart mode, there is also in addition a counter activated, which initiates a restart after a set number of  $N_{\text{ARMstep}}$  HV start-up cell charge cycles (see *Figure 16*).

In latched operation a mode reset can only be achieved by disconnecting the AC line. A HW reset is taking place once the VCC voltage drops below the threshold  $V_{VCCoff}$ .

Figure 15

Bang-bang mode during protection mode

# 3.2.4 VCC supply during burst mode (BM) operation

During burst mode operation the IC enters repeatedly a power saving mode, in which the IC current consumption is reduced to  $I_{VCCBMpsm}$ . Waking up from and entering this power saving mode is controlled by the feedback voltage at *FB* pin by comparing the voltage level with the wake-up and sleep control threshold  $V_{FBBMctrl}$  (see *Chapter 3.3.4.2*). In addition a wake-up threshold  $V_{VCCslpHVon}$  is enabled at *VCC* pin, which turns-on the HV start-up cell once  $V_{VCC}$  drops below  $V_{VCCslpHVon}$ . This shall support a higher voltage level at *HSVCC* pin than the threshold  $V_{HSVCCon}$ . The HV start-up cell is turned off when either the IC is waked up via *FB* pin or

$V_{VCC}$  is exceeding the threshold  $V_{VCCon}$ . In addition there is always only one HV start-up cell VCC charge up cycle initiated once entering the burst mode.

Note: The system dimensioning should ensure that during steady state burst mode operation V<sub>VCC</sub> stays always well above the VCC wake-up threshold V<sub>VCCslpHVon</sub> in order to avoid increasing bias losses due to charging the VCC capacitor from input high voltage.

**Figure 17** shows a typical burst mode operation signal for  $V_{VCC}$  and correlated current consumption  $I_{VCC}$  during steady state burst mode operation once feedback voltage has dropped below the burst mode entry threshold  $V_{FBBMen}$ . A large decrease of  $V_{VCC}$  can occur for a large output load drop at time *t0*, when optocoupler feedback network is entering saturation due to *Vout* overshoot. This can lead to a significant longer rising time period of feedback voltage  $V_{FB}$  until time *t2*. At time *t1* the VCC voltage is dropping below the threshold  $V_{VCCslpHVon}$  and turning on the HV start-up cell. The average current  $I_{HV(avg)}$  flowing into pin *HV* is depending on *VAC* and charging via *VCC* pin with  $I_{VCCchrg(avg)}$  the capacitor at VCC. At time *t2* the IC is waked up via *FB* pin and the HV start-up cell is turned off. When feedback voltage is dropping below  $V_{FBBMctrl}$  at time *t3* the IC is entering the power saving mode.

**Burst mode operation**

# 3.3 Control features

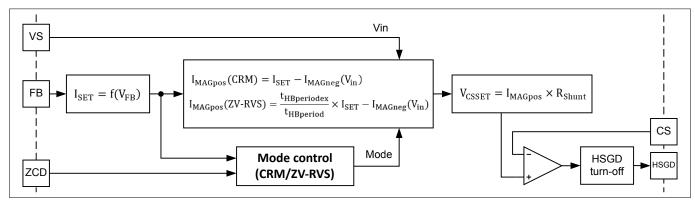

The control features chapter contains all functions for the hybrid-flyback PWM generation and the half-bridge gate driver listed in *Table 2*. The hybrid-flyback PWM generation consists mainly of the mode control and output current control. The output current control is determining that part of the PWM control, which is taking place during high-side switch on-time  $t_{HSon}$  by means of peak current control (see *Figure 18*) for the positive magnetization level  $I_{MAGpos}$ . Furthermore it provides the decision for changing the valley number in ZV-RVS operation. The PWM control ensures cycle by cycle ZVS switching operation. The mode control feature focus on controlling directly the timings of the half-bridge PWM scheme associated with the dead-times  $t_{deadLS}$ ,  $t_{deadHS}$  and the low-side switch on-time  $t_{LSon}$  to determine the negative magnetization level  $I_{MAGneg}$  for the different operation modes like CRM, ZV-RVS and DCM.

### Figure 18 Hybrid-flyback control structure

### Table 2Control features

| Chapter       |

|---------------|

| Chapter 3.3.1 |

| Chapter 3.3.2 |

| Chapter 3.3.4 |

| Chapter 3.3.3 |

| Chapter 3.3.5 |

| Chapter 3.3.6 |

|               |

# 3.3.1 Output control

During continuous switching operation the output current is only controlled by means of the positive and negative magnetization current levels  $I_{MAGpos}$  and  $I_{MAGneg}$  following *Equation 5*. During continuous operation the output current  $I_{out}$  is controlled by means of a linear relationship between the feedback voltage at *FB* pin and the associated internal current set-point  $I_{SET}$ , which is described in *Chapter 3.3.1.3*. The linear relationship is achieved by adjusting  $I_{MAGneg}$  cycle by cycle via the turn-on time of *LS* switch  $t_{LSon}$  depending on the input

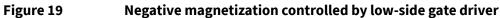

voltage *Vin* (see *Chapter 3.3.1.1*) and the output voltage *Vout* (see *Chapter 3.3.1.2*). The positive magnetization level  $I_{MAGpos}$  equals the positive half-bridge peak current that is controlled via *CS* pin at the shunt resistor  $R_{Shunt}$  (see *Figure 19*):

$V_{\text{CSpeak}} = I_{\text{HBpeak}} \times R_{\text{Shunt}} = I_{\text{MAGpos}} \times R_{\text{Shunt}}$

### **Equation 9**

The output voltage is measured via *ZCD* pin at the auxiliary winding and taken for protection features (see *Chapter 3.4.8*) and for compensating the peak to peak magnetizing current *I*<sub>MAGpp</sub> to ensure ZVS operation over wide output voltage range (see *Chapter 3.3.1.2*).

# 3.3.1.1 Keeping ZVS operation for wide input voltage range

ZVS operation for wide input voltage range is achieved by *Vin* feed-forward compensation of negative magnetization level *I*<sub>MAGneg</sub> during the different operation modes (see *Chapter 3.3.2*). This is supported by several configurable parameters introduced in the sequel.

The implemented output current control is based on the dimensioning for the nominal output current level *I*<sub>outnom</sub><sup>1</sup> following *Equation 5*:

$$I_{\text{outnom}} = \frac{N}{2} \times (I_{\text{MAGposnom}}(\text{Vin}; \text{Vout}; \text{Mode}) + I_{\text{MAGneg}}(\text{Vin}; \text{Mode}))$$

### **Equation 10**

The peak current control at CS pin for adjusting  $I_{MAGpos}$  is therefore depending on the input, output voltage and the mode operation that are directly impacting the negative magnetization level  $I_{MAGneg}$ .

```

<sup>1</sup> configurable, see Table 5

```

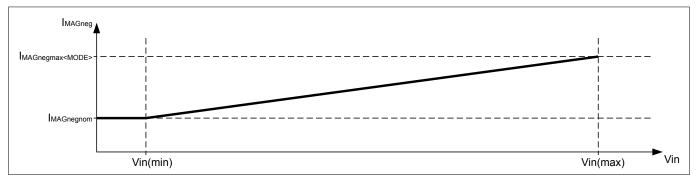

*I*<sub>MAGneg</sub> is compensated for a changing output voltage (see *Chapter 3.3.1.2*). Therefore the compensation for input voltage requires only set-points for minimum and maximum *Vin* (see *Figure 20*).

### Minimum Vin

For minimum *Vin* the natural freewheeling oscillation caused by  $I_{MAGnegnom}^{2}$  (see *Figure 19*) shall support the complete switch-over of the half-bridge node.

#### Maximum Vin

For maximum *Vin* the additional required negative magnetization is set for CRM with *I*<sub>MAGnegmaxCRM</sub><sup>2)</sup> and for ZV-RVS with *I*<sub>MAGnegmaxRVS</sub><sup>2)</sup>, which might be different.

# 3.3.1.2 Keeping ZVS operation for wide output voltage range

When output voltage *Vout* is decreasing the demagnetization time of the transformer  $t_{demag}$  is prolonging, which leads to a longer time period  $t_{TRANS}$ . ZVS operation is ensured by adjusting the turn-on time of the *LS* switch  $t_{LSon}$  to match with the changed time period for  $t_{TRANS}$  in order to keep the same negative magnetization level  $I_{MAGneg}$  for a constant output load (see *Figure 21*).  $t_{TRANSRVS0V}$  means the time period for *Vout* = 0V and is derived from  $t_{TRANSRVS0V}$ <sup>3</sup> by the following equation:

$t_{\text{TRANSRVS0V}} = t_{\text{TRANSRVS0V \%}} \times t_{\text{TRANSnom}}$

### **Equation 11**

### Figure 21 *Vout* compensation for t<sub>TRANS</sub>

# 3.3.1.2.1 Cycle by cyle ZVS operation during CRM operation

When fast decreasing the output voltage *Vout* (see *Figure 8*) or fast increasing the positive magnetization level  $I_{MAGpos}$  (see *Chapter 3.3.2.5*) the demagnetization time  $t_{demag}$  of the transformer can be too short when operating with fixed *LS* switch on-time period. This can cause hard switching or even body diode cross conduction if transformer is still positive magnetized.

<sup>&</sup>lt;sup>2</sup> configurable, see *Table 6*

<sup>&</sup>lt;sup>3</sup> configurable, see *Table 6*

To ensure a cycle by cycle ZVS switching condition, the controller only activates the *HS* switch when the voltage signal at *ZCD* pin (see *Figure 18*) indicates a changing half-bridge voltage  $V_{HB}$ . By this body diode cross conduction is properly avoided. This is achieved by regulating  $I_{MAGneg}$  for a target delay time  $t_{LS2ZCD}$  between falling edge of *LS* switch and subsequently occurring falling edge at *ZCD* pin (see *Figure 22*).

The polarity of the transformer auxiliary winding  $L_{AUX}$  has to be considered in such a way that a rising  $V_{HB}$  is leading to a falling  $V_{ZCD}$ . The time between turning off the *LS* switch until zero-crossing detection for turning on the high-side switch  $t_{LS2ZCD}$  is observed and determining a prolongation of next turn-on phase for *LS* switch if required to ensure reliable ZVS operation.

An example is shown with phase t2-t3 in comparison to phase t6-t7. The dead-time  $t_{deadHS1}$  is determined by the negative half-bridge current level  $I_{MAGneg1}$ . The small level of  $I_{MAGneg1}$  leads to a rather slow rising slope of  $V_{HB}$ . The detection of zero-crossing at *ZCD* pin is delayed and turn-on of *HS* switch is not taking place under full ZVS condition at time t3. The increased delay of zero-crossing after having turned off *LS* switch is taken as input for increasing indirectly the negative half-bridge current level to  $I_{MAGneg2}$  by extending the turn-on time of *LS* switch in phase t5-t6. ZVS condition for turning on the *LS* switch are reached by properly dimensioning the dead-time  $t_{deadLS}$  (see *Chapter 3.3.2.1*).

Only in DCM operation at very light-load partial hard switching can occur for the first *LS* switching cycle turn-on. This is only taking place after a long waiting period when demagnetization of the transformer is finished not causing a body diode conduction issue (see *Chapter 3.3.2.3*).

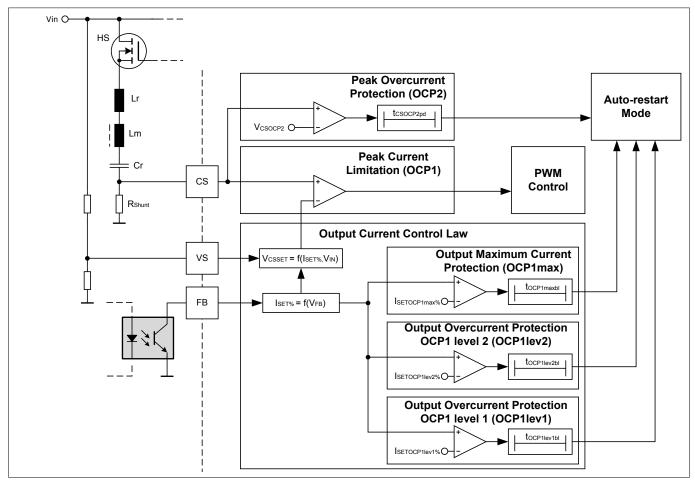

# 3.3.1.3 Output current control law

*Figure 23* shows the control path from feedback signal input at *FB* pin to peak current setting at *CS* pin. The requested output current equals to the internal *I*<sub>SET</sub> for the corresponding feedback signal. The required peak current setting is then calculated based on *Vin* measurement and mode operation.

### Figure 23 Control path from feedback input to peak current setting

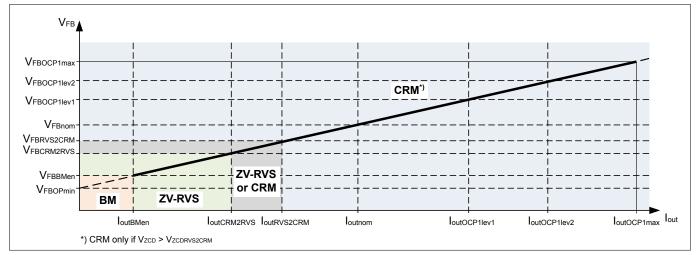

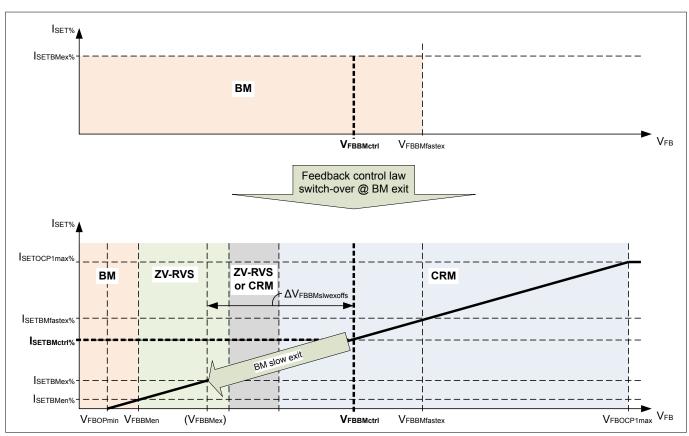

The feedback voltage  $V_{FB}$  has a linear correlation with the output current  $I_{out}$  between the boarders for maximum output current  $I_{outOCP1max}$  and burst mode entry current level  $I_{outBMen}$ . *Figure 24* is showing output current levels for various functions.

### Figure 24 Control law for feedback voltage at FB pin

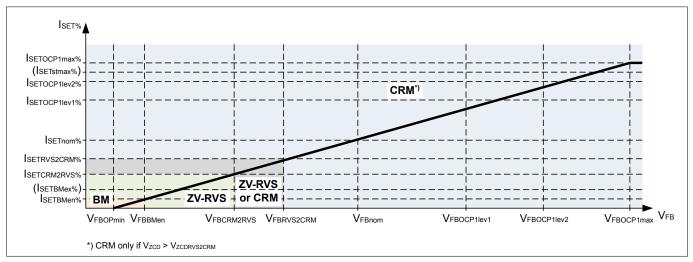

Controlling the output current  $I_{out}$  is determined by the equivalent internal current set-point  $I_{SET}$ , which is then taken for the peak current setting at CS pin to adjust the positive magnetization level  $I_{MAGpos}$ . The correlation between  $I_{SET}$  and  $I_{MAGpos}$  is different for CRM (see *Chapter 3.3.1.3.1*) and ZV-RVS mode (see *Chapter 3.3.1.3.2*) in order to ensure a smooth transition between the CRM and ZV-RVS mode. *Figure 25* shows the configurable current set-points for various functions and their correlation with the feedback voltage.

The configurable current set-points  $I_{SETxxx\%}$  are defined in percentage with respect to the nominal current set-point  $I_{SETnom\%}$  that determines in percentage of the *FB* pin operating voltage range  $V_{FBOPmax}$  the associated voltage level  $V_{FBnom}$ . Here  $I_{SETnom\%}$  is set to 50% used as a factor without unit.

$V_{\text{FBnom}} = (I_{\text{SETnom \%}} \times V_{\text{FBOPmax}}) + V_{\text{FBOPmin}}$

### **Equation 12**

Note: The current set-point for burst mode exit threshold I<sub>SETBMex%</sub> is only active during burst mode operation and only used as an internal parameter for comparison, which is not associated with a feedback voltage level (see **Chapter 3.3.4.4.1**). The same applies for I<sub>SETstmax%</sub> that is only active during Vout start-up control (see **Chapter 3.3.3**) to provide additional output charge current.

### Figure 25 Configurable internal current set-points *I*<sub>SETxxx%</sub> and correlation with *V*<sub>FB</sub>

For all other current set-points *I*<sub>SETxxx%</sub> the correlated feedback voltage *V*<sub>FBxxx</sub> can be calculated as following:

$V_{\rm FBxxx} = (I_{\rm SETxxx\%} \times I_{\rm SETnom\%} \times V_{\rm FBOPmax}) + V_{\rm FBOPmin}$

### **Equation 13**

The offset V<sub>FBOPmin</sub> considers the minimum operating voltage level of the opto-coupler output before entering saturation.

The peak current setting at CS pin is done by comparing the voltage at the shunt resistor  $R_{\text{Shunt}}$  with the internally derived threshold  $V_{\text{CSxxx}}$ :

$$I_{\text{MAGxxx}} = \frac{V_{\text{CSxxx}}}{R_{\text{Shunt}}}$$

### **Equation 14**

*V*<sub>CSxxx</sub> is beside *I*<sub>SET%</sub> also depending on *Vin* and the mode operation (see *Chapter 3.3.1.1*) shown by following relationship:

### **CRM operation**

```

V_{\text{CSxxx}} = (I_{\text{SETxxx\%}} \times I_{\text{SETnom\%}} \times V_{\text{CSOPmax}}) + (I_{\text{MAGneg}}(\text{Vin}) \times R_{\text{Shunt}})

```

### **Equation 15**

#### **ZV-RVS** operation

$$V_{\text{CSxxx}} = \frac{t_{\text{HBperiodex}}}{t_{\text{HBperiod}}} \times \left[ \left( I_{\text{SETxxx\%}} \times I_{\text{SETnom\%}} \times V_{\text{CSOPmax}} \right) + \left( I_{\text{MAGneg}}(\text{Vin}) \times R_{\text{Shunt}} \right) \right]$$

### **Equation 16**

Hereby  $V_{CSOPmax}$  is the maximum operating voltage range at CS pin.  $R_{Shunt}$  dimensioning is based on nominal output current  $I_{outnom}$  at nominal current set-point  $I_{SETnom\%}$ , where  $I_{SETnom\%}$  also determines in percentage of  $V_{CSOPmax}$  at CS pin the associated voltage level  $V_{CSOPnom}$ .

$R_{\text{Shunt}} = \frac{N}{2} \times \frac{I_{\text{SETnom \%}} \times V_{\text{CSOPmax}}}{I_{\text{Outnom}}}$

#### **Equation 17**

At the corners for *Vin(min)* and *Vin(max)* the expected peak current setting for nominal current set-point *I*<sub>SETnom%</sub> can be calculated with:

Minimum peak current setting  $V_{CSnom}(min)$  for nominal load at Vin(min) CRM operation

$$V_{\text{CSnom(min)}} = (I_{\text{SETnom \%}} \times V_{\text{CSOPmax}}) + \left( \left( I_{\text{MAGnegnom \%}} \times \frac{2 \times I_{\text{Outnom}}}{N} \right) \times R_{\text{Shunt}} \right)$$

### **Equation 18**

### **ZV-RVS** operation

$$V_{\text{CSnom(min)}} = \frac{t_{\text{HBperiodex}}}{t_{\text{HBperiod}}} \times \left( \left( I_{\text{SETnom \%}} \times V_{\text{CSOPmax}} \right) + \left( \left( I_{\text{MAGnegnom \%}} \times \frac{2 \times I_{\text{Outnom}}}{N} \right) \times R_{\text{Shunt}} \right) \right)$$

#### **Equation 19**

Maximum peak current setting  $V_{CSnom}(max)$  for nominal load at Vin(max) CRM operation

$$V_{\text{CSnom}(\text{max})} = (I_{\text{SETnom \%}} \times V_{\text{CSOPmax}}) + \left( \left( I_{\text{MAGnegmaxCRM \%}} \times \frac{2 \times I_{\text{Outnom}}}{N} \right) \times R_{\text{Shunt}} \right)$$

#### **Equation 20**

### **ZV-RVS** operation

$$V_{\text{CSnom}(\text{max})} = \frac{t_{\text{HBperiodex}}}{t_{\text{HBperiod}}} \times \left( \left( I_{\text{SETnom \%}} \times V_{\text{CSOPmax}} \right) + \left( \left( I_{\text{MAGnegmaxRVS \%}} \times \frac{2 \times I_{\text{Outnom}}}{N} \right) \times R_{\text{Shunt}} \right) \right)$$

#### **Equation 21**

# 3.3.1.3.1 Current control during CRM

During CRM operation the negative magnetization  $I_{MAGneg}$  is controlled for a target value only depending on input voltage *Vin* (see *Chapter 3.3.1.1*). Here the negative magnetization  $I_{MAGneg}$  is controlled by adjusting the on-time  $t_{LSon}$ , which leads to a linear correlation between  $I_{out}$  and the set positive magnetization level  $I_{MAGpos}$ :

$$I_{\text{out}} = \frac{N}{2} \times (I_{\text{MAGpos}}(\text{Vin}) + I_{\text{MAGneg}}(\text{Vin}))$$

### **Equation 22**

$I_{MAGpos}$  is then controlled by the peak current control at CS pin based on the correlation with the internal target current set-point  $I_{SET}$ , which is a proportional representation of the output current  $I_{out}$ :

$$I_{\text{SET}} = \frac{2}{N} \times I_{\text{out}}$$

### **Equation 23**

$$I_{\text{MAGpos}}(I_{\text{SET}}; \text{Vin}) = I_{\text{SET}} - I_{\text{MAGneg}}(\text{Vin})$$

### **Equation 24**

When reducing the load the on-time of *LS* switch is getting reduced until the minimum time period  $t_{\text{TRANSnom}}$ . For further reduction in load the on-time of *LS* is kept constant, which results in a constant peak to peak magnetization  $I_{\text{MAGpp}}$  (see *Figure 19*):

$I_{\rm MAGpp} = I_{\rm MAGpos} - I_{\rm MAGneg}$

#### **Equation 25**

# 3.3.1.3.2 Current control during ZV-RVS mode

As in ZV-RVS mode the peak current control for  $I_{MAGpos}$  shall be kept almost constant (see **Chapter 3.3.2.2.1**) to ensure that the demagnetization time is longer than half of the resonant period of the *LrCr* tank, a waiting time gap  $t_{waitgap}$  is introduced directly after the end of  $t_{TRANSnom}$  period (see **Figure 19**), which is extending the half-bridge period to  $t_{HBperiodex}$ . This results in a reduced output current  $I_{out}$  that can be expressed as:

$I_{\text{out}} = \frac{t_{\text{HBperiod}}}{t_{\text{HBperiodex}}} \times \frac{N}{2} \times \left(I_{\text{MAGpos}} + I_{\text{MAGneg}}\right)$

### **Equation 26**

The control for  $t_{\text{HBperiodex}}$  is performed by means of valley skipping control (see *Chapter 3.3.2.2.1*) depending on  $I_{\text{SET}}$  and *Vin*:

| $t_{\text{HBperiodex}}(I_{\text{SET}}; \text{Vin}) = t_{\text{HBperiod}} \times t_{\text{HBperiod}}$ | $(I_{MAGpos} + I_{MAGneg}(Vin))$ |

|------------------------------------------------------------------------------------------------------|----------------------------------|

| $\iota_{\text{HBperiodex}}(\Gamma_{\text{SET}}, \vee \Pi) - \iota_{\text{HBperiod}} \times$          | I <sub>SET</sub>                 |

#### **Equation 27**

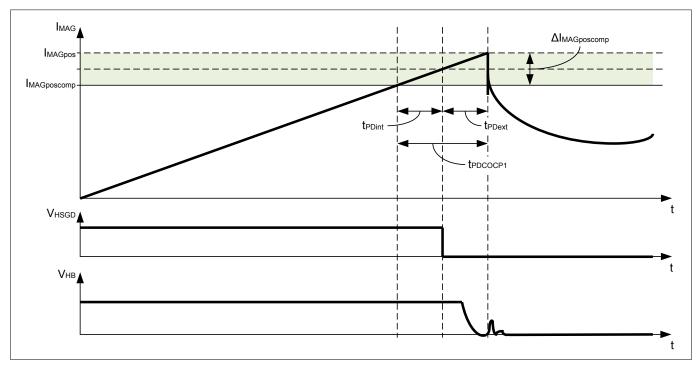

# 3.3.1.4 Propagation delay compensation (PDC)

During peak current control a propagation delay is impacting the resulting peak current limitation (see *Figure* **26**). The higher reached peak current is then compensated to a lower level by the closed application control loop via the feedback signal at *FB* pin. The magnitude of  $I_{MAG pos}$  overshoot is depending on the voltage at the transformer input winding *Lm*, which is depending on input voltage *Vin* and reflected output voltage at resonant capacitor  $V_{Cr}$ . A higher voltage amplitude at the transformer input winding leads to a steeper rising slope of  $I_{MAGpos}$  and vice versa. A total delay of  $t_{PDCOPC1}$  leads then to a delta overshoot of  $\Delta I_{MAGposcomp}$ :

$$\Delta I_{MAGposcomp} = \frac{(Vin - V_{Cr})}{Lm} \times t_{PDCOPC1}$$

#### **Equation 28**

$t_{\text{PDCOPC1}}$  consists of an internal delay  $t_{\text{PDint}}$  caused by the OCP1 comparator, gate driver and an external delay  $t_{\text{PDext}}$  caused by the power switch turn-off and parasitic capacitance connected to the half-bridge node.

$t_{\rm PDCOCP1} = t_{\rm PDint} + t_{\rm PDext}$

#### **Equation 29**

### Figure 26 Propagation delay compensation of peak current control for I<sub>MAGpos</sub>

This dependency on *Vin* and  $V_{Cr}$  impacts the current set-point threshold accuracy seen in the application and is therefore compensated to avoid errors on the feedback signal  $V_{FB}$ .

The propagation delay compensation uses **Equation 28** to calculate  $\Delta I_{MAGposcomp}$  based on the parameter  $t_{PDCOPC1}$ <sup>4</sup>, the measured input voltage at VS pin and measured reflected output voltage at ZCD pin. Lm is extracted from other configurable parameters as following:

$$Lm = \frac{V_{VSVCRnom} \times t_{TRANSnom}}{I_{MAGpp}}$$

### **Equation 30**

The peak current setting is then compensated by reducing the internal target peak current set-point  $I_{MAGpos}$  with  $\Delta I_{MAGposcomp}$ :

```

I_{\rm MAGposcomp} = I_{\rm MAGpos} - \Delta I_{\rm MAGposcomp}

```

## **Equation 31**

# 3.3.2 PWM control schemes

**Table 3** shows the list of features that describes the pulse width modulation (PWM) control methods for the different control modes and the associated mode transition. Depending on load, output voltage, and input voltage (see **Chapter 3.3.1**) the control scheme is adjusted to ensure ZVS operation for both low-side and high-side switches.

<sup>&</sup>lt;sup>4</sup> configurable, see *Table 21*

| Table 3 PWM control        |                 |  |

|----------------------------|-----------------|--|

| Feature                    | Chapter         |  |

| CRM control scheme         | Chapter 3.3.2.1 |  |

| ZV-RVS mode control scheme | Chapter 3.3.2.2 |  |

| DCM control scheme         | Chapter 3.3.2.3 |  |

| Mode transition control    | Chapter 3.3.2.4 |  |

| Overcurrent control        | Chapter 3.3.2.5 |  |

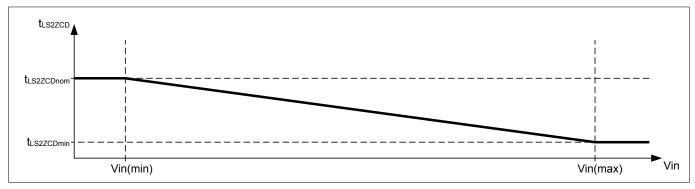

# 3.3.2.1 CRM control scheme

The PWM control targets a ZVS operation for every half-bridge switching cycle by cycle by tuning the negative current level  $I_{MAGneg}$  (see *Figure 27*). The dead-time  $t_{deadLS}^{5}$  between *HS* and *LS* switch is fixed as the peak current is high enough to provide proper ZVS operation for *LS* switch.

### Figure 27 Half-bridge timings for CRM operation

The dead-time  $t_{deadHS}$  is depending on input voltage and mode operation. In CRM operation it consists of 2 time periods:

<sup>&</sup>lt;sup>5</sup> configurable, see *Table 7*

# XDP Hybrid-flyback Controller XDPS2201

## Functional description

```

t_{\text{deadHS}}(\text{Vin}; \text{CRM}) = t_{\text{LS2ZCD}}(\text{Vin}) + t_{\text{ZCDfefilCRM}}

```

### **Equation 32**

The time period  $t_{LS2ZCD}$  is captured after turning off *LS* switch at time t0 until zero-crossing detection at time t1 and compared with a target value based on *Vin*. The shortest time period  $t_{LS2ZCDmin}^{5}$  occurs at maximum input voltage, whereas the longest time period  $t_{LS2ZCDnom}^{5}$  is correlated with minimum input voltage (see *Figure 28*).

### Figure 28 Adaptive target time period for t<sub>LS2ZCD</sub>

In the subsequent half-bridge switching cycle the LS switch on-time  $t_{LSon}$  is adjusted by  $\Delta t_{LSon}$

$$\Delta t_{\rm LSon} = t_{\rm LS2ZCD}(\rm Vin) - t_{\rm LS2ZCDcap}$$

### **Equation 33**

with  $t_{LS2ZCDcap}$  being the captured time period.

Extending  $t_{LSon}$  increases the negative magnetization level  $I_{MAGneg}$ , which then reduces the time for switchingover the half-bridge node. In this way the negative magnetization is being self-adjusted to the defined target value as shown in *Chapter 3.3.1.1* and supporting an internal accurate output current estimation for peak current setting at *CS* pin.

When reducing  $t_{LSon}$  the minimum is determined by  $t_{TRANSnom}$ <sup>5)</sup> at maximum output voltage level.

The 2<sup>nd</sup> part of  $t_{deadHS}$  is defined by the fixed time period  $t_{ZCDfefilCRM}^{5}$ , which is delaying the *HS* switch turn-on at time t2 after zero-crossing detection at time t1 (see *Figure 27*).

After *HS* switch is turned on the peak current limitation only takes place after a leading edge spike blanking period  $t_{\rm HSleb}^{5}$ , which determines also the minimum on-time of *HS* switch operation.

# 3.3.2.2 ZV-RVS control scheme

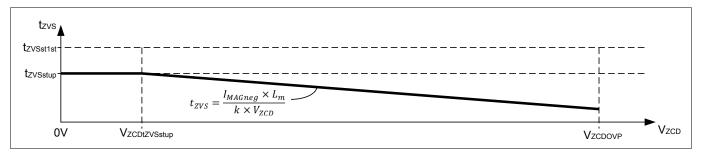

The relevant timings for ZV-RVS mode operation with ZVS pulse generation are shown in *Figure 29*). During ZV-RVS mode a waiting time gap  $t_{waitgap}$  is inserted at time t0 after a *HS* and *LS* switch half-bridge cycle to control the output current (see *Chapter 3.3.1.3.2*). The ZVS pulse  $t_{ZVS}$  is initiated by turning on the *LS* switch after the rising edge zero-crossing detection target number at time t1 and a delay time period  $t_{ZCDrefilRVS}^{6}$ . The dead-time for turning on the *HS* switch after the ZVS pulse is fixed with  $t_{deadHSRVS}^{6}$ . The subsequent dead-time  $t_{deadLS}$  is same as in CRM operation.

The required ZVS pulse length  $t_{ZVS}$  is determined by the target negative magnetization level  $I_{MAGneg}$ , the transformer magnetizing inductance *Lm* and depending on output voltage *Vout*:

<sup>&</sup>lt;sup>5</sup> configurable, see *Table 7*

<sup>&</sup>lt;sup>6</sup> configurable, see *Table 8*

# XDP Hybrid-flyback Controller XDPS2201

### **Functional description**

$$t_{\rm ZVS} = \frac{I_{\rm MAGneg} \times \rm Lm}{N \times V_{\rm OUT}}$$

### **Equation 34**

$I_{MAGneg}$  is adapted for changes in input voltage (see *Chapter 3.3.1.1*). The minimum ZVS pulse length occurs when both lowest input voltage and highest output voltage applies. Here the parameter  $t_{ZVSmin}^{7/}$  is limiting the minimum adjustable ZVS pulse length.

*Note:* The minimum t<sub>ZVSmin</sub> shall be equal or longer than the minimum on-time of the SR controller for proper operation.

# 3.3.2.2.1 Valley skipping control

When operating in ZV-RVS mode, valley detection is taking place to determine the time for turning on the ZVS pulse (see *Figure 29*). The waiting time after transformer demagnetization  $t_{waitgap}$  is controlled based on the target number of detected valleys. A valley is counted once a falling edge of the ZCD signal is detected after a filter  $t_{ZCD fefilRVS}^{8}$ . The target number for valley detection is adjusted every half-bridge switching cycle depending on exceeding the thresholds  $I_{MAGposRVS(+)}$  or  $I_{MAGposRVS(-)}$ . The target valley number is increased once

<sup>&</sup>lt;sup>7</sup> configurable, see *Table 8*

<sup>&</sup>lt;sup>8</sup> configurable, see *Table 8*

the internally derived peak current setting  $I_{MAGpos}$  is dropping below  $I_{MAGposRVS(+)}$  and decreased when exceeding  $I_{MAGposRVS(-)}$ . Hence a hysteresis is built in order to avoid value jumping during steady state operation. The hysteresis magnitude can be calculated with:

```

I_{\text{MAGposRVShys}} = \frac{1}{3} \times I_{\text{MAGposnom}}

```

#### **Equation 35**

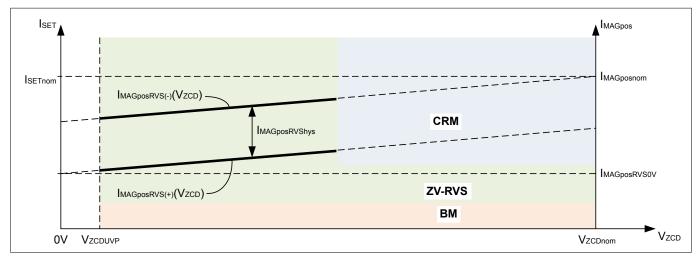

Both thresholds are depending on the output voltage measured via *ZCD* pin. The value is decreasing with decreasing output voltage as shown in *Figure 30*. As a result the peak current setting at *CS* pin is kept almost constant between the two thresholds  $I_{MAGposRVS(-)}$  and  $I_{MAGposRVS(+)}$  for a given output voltage. The threshold  $I_{MAGposRVS(+)}$  is determined by the two points for  $I_{MAGposnom}$  at nominal output voltage and  $I_{MAGposRVS0V}$  for *Vout* = 0V.  $I_{MAGposRVS0V}$  is defined by  $I_{MAGposRVS0V}$ <sup>9</sup> with following equation:

$I_{\rm MAGposRVS0V} = I_{\rm MAGposRVS0V\%} \times I_{\rm MAGposnom}$

### **Equation 36**

The maximum number of requested target valleys is limited and leads to a mode change to DCM (see *Chapter* **3.3.2.4**).

Figure 30

Valley skipping control for adjusting t<sub>waitgap</sub>

# 3.3.2.3 DCM control scheme

The DCM control is associated with triggering the ZVS pulse in ZV-RVS mode operation. ZV-RVS mode operation at light-load is limited by the maximum number of detectable zero-crossings at *ZCD* due to decreasing oscillation magnitude with prolongation of the inserted waiting time gap  $t_{waitgap}$  (see *Figure 10*). When further reducing the output current the waiting time gap  $t_{waitgap}$  is further increased until the ZVS pulse is initiated without zero-crossing detection. The subsequent half-bridge cycle is then again performed under ZVS condition (see *Chapter 3.3.2.2*).

Increasing  $t_{\text{waitgap}}$  takes only place until the extended half-bridge period  $t_{\text{HBperiodex}}$  (see **Chapter 3.3.2.2**) reaches the associated minimum half-bridge switching frequency  $F_{\text{DCMmin}}^{10}$ . When output current is further decreased, the feedback voltage  $V_{\text{FB}}$  drops until it exceeds the burst mode entry threshold (see **Chapter 3.3.4.1**).

The DCM operation can be disabled by means of  $EN_{DCM}^{10}$ .

<sup>&</sup>lt;sup>9</sup> configurable, see *Table 6*

<sup>&</sup>lt;sup>10</sup> configurable, see *Table 9*

## 3.3.2.4 Mode transition control

### Mode transition between CRM and ZV-RVS mode

The mode transition control observes the signal levels at *FB* and *ZCD* pins for exceeding thresholds that define the changeover from CRM to ZV-RVS mode and vice versa. The feedback signal  $V_{FB}$  is determining the internal current set-point  $I_{SET\%}$  and compared with the current set-point thresholds (see *Chapter 3.3.1.3*). During operating in CRM the thresholds  $I_{SETCRM2RVS\%}^{11}$  and  $V_{ZCDCRM2RVS}^{11}$  at *ZCD* pin are determining the switchover to ZV-RVS mode. Operating in ZV-RVS mode the thresholds  $I_{SETRVS2CRM\%}^{11}$  and  $V_{ZCDRVS2CRM\%}^{11}$  at *ZCD* pin are determining the switchover to CRM.

Figure 31 Mode transition between CRM and ZV-RVS mode

#### Mode transition between ZV-RVS mode and DCM

The DCM operation takes place once the control loop requests for operating beyond the maximum number of valley switching  $N_{\text{RVSvalmax}}^{12}$  (see *Chapter 3.3.2.2.1*). After entering DCM operation the peak current setting is slightly increased by adding an offset of 25% of the set  $I_{\text{MAGposRVS}(+)}$ . During DCM operation the number of occurring valleys is observed. When ZVS pulse is initiated within a time period with lower number of valleys than  $N_{\text{RVSvalmax}}$  a switch-over to valley synchronized ZV-RVS mode operation is taking place. After leaving the DCM operation the 25% offset is removed again. This ensures a hysteresis between entering and leaving DCM.

## 3.3.2.5 Overcurrent control

The hybrid-flyback topology supports high level overcurrent operation with high efficiency. In such case CRM operation is taking place based on the equations shown in *Chapter 3.3.1.3.1*. The additionally required circulating current is achieved by increasing the peak current setting for current set-points higher than  $I_{SETnom}$ , as requested by the feedback signal at *FB* pin. Hereby the energy transmission time  $t_{TRANS}$  is extended to provide increased negative magnetization level  $I_{MAGneg}$  to reach ZVS condition for turning on the *HS* switch (see *Chapter 3.3.1.2.1*). If the estimated overcurrent is exceeding overcurrent set-points for a defined time period, a protection mode is entered (see *Chapter 3.4.7*).

## 3.3.3 Vout start-up control

The IC contains a *Vout* start-up control by observing the output voltage via the reflected voltage at *ZCD* pin, which is shown in *Figure 34*.

<sup>&</sup>lt;sup>11</sup> configurable, see *Table 19*

<sup>&</sup>lt;sup>12</sup> configurable, see *Table 9*

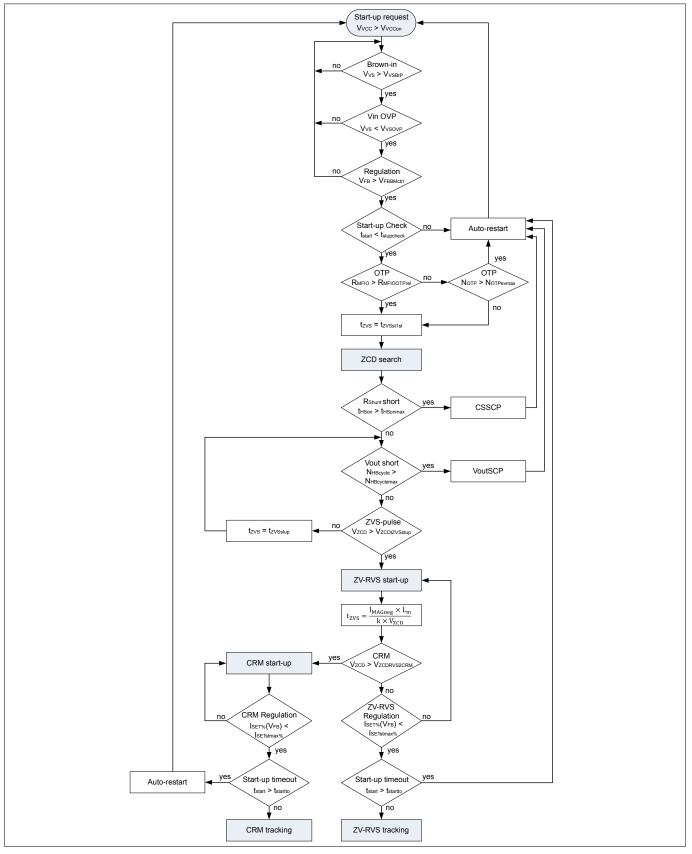

A start-up request takes place after an IC HW reset or entered auto-restart mode when VCC is charged up and exceeded the threshold  $V_{VCCon}$  (see *Chapter 3.2.1*). At that moment following 4 conditions are checked to be valid:

- **1.** Brown-in condition with  $V_{VS} > V_{VSBIP}$  (see **Chapter 3.4.4.1**)

- 2. No Input overvoltage with  $V_{VS} < V_{VSOVP}$  (see *Chapter 3.4.4.4*)

- **3.** Feedback signal out of regulation range  $V_{FB} > V_{FBBMctrl}$

- **4.** No overtemperature condition with  $R_{MFIO} > R_{MFIOOTPrel}$  (see *Chapter 3.4.9*)

The conditions 1-3 needs to be valid within the time period  $t_{stupcheck}$ . Once conditions 1-3 are valid condition 4 is checked.

In case one of those conditions is not met the IC enters bang-bang during brown-in phase (see *Chapter 3.2.2*).

After all 4 conditions are valid the IC prepares for the first *HS* switch pulse. Here a maximum on-time  $t_{HSonmax}$  is calculated based on *Vin* to check for a  $R_{Shunt}$  short circuit at *CS* pin (CSSCP, see *Chapter 3.4.6*), when turning on the *HS* switch. But before turning on the *HS* switch a first initial *LS* switch pulse is generated with  $t_{ZVSst1st}^{13}$  to precharge the bootstrap capacitor at *HSVCC* pin. Afterwards the length of ZVS pulse is fixed to the time period  $t_{ZVSstup}$  until the voltage at *ZCD* pin exceeds the threshold  $V_{ZCDtZVSstup}$ .

### **Equation 37**

Then  $t_{ZVS}$  is decreased depending on increasing  $V_{ZCD}$  (see *Figure 32*).

#### Figure 32 Adaptive t<sub>ZVS</sub> depending on V<sub>ZCD</sub>

During ZCD search phase the number of generated half-bridge switching cycles is counted. If no zero-crossing detection is taking place after the *HS* switch is turned off, a next ZVS pulse is generated after a time period  $t_{\text{startzcdto}}^{13}$ . When ZCD signal is missing, the counted number of half-bridge switching cycles is exceeding  $N_{\text{HBcyclemax}}^{13}$  a protection mode for *Vout* short circuit detection (VoutSCP, see *Chapter 3.4.8.3*) is entered.

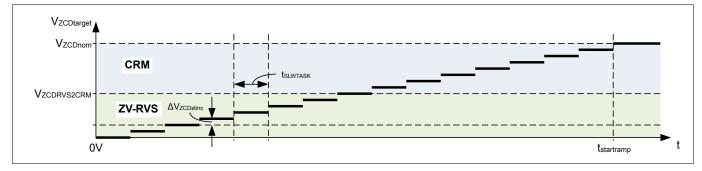

With entering the ZCD search phase the very first peak current setting at CS pin is starting based on overcurrent set-point  $I_{SETOCP1lev1\%}$ . The further peak current setting is kept constant until  $V_{ZCD}$  is exceeding the threshold  $V_{ZCDtZVSstup}$ . Then Vout start-up control is determining the peak current control setting based on comparing the measured voltage at *ZCD* pin with target voltage set-point  $V_{ZCDtarget}$ . The peak current control is cycle by cycle linearly increasing  $V_{CS}$  until target voltage level at *ZCD* pin is reached or linearly decreasing  $V_{CS}$  if  $V_{ZCD}$  is over the target voltage level for *ZCD* pin. Here the IC increases step by step after a time period  $t_{SLWTASK}$  the incremental target value  $V_{ZVDtarget}$  (see *Figure 33*). During start-up the current set-point maximum control range is limited by  $I_{SETStmax\%}$ <sup>13)</sup>.

The incremental voltage step  $\Delta V_{ZCDstinc}$  is determined by the ramp-up time period  $t_{startramp}^{13}$ :

<sup>&</sup>lt;sup>13</sup> configurable, see *Table 11*

## XDP Hybrid-flyback Controller XDPS2201

#### **Functional description**

$$\Delta V_{\text{ZCDstinc}} = \frac{V_{\text{ZCDnom}} \times t_{\text{SLWTASK}}}{t_{\text{startramp}}}$$

#### **Equation 38**

By this the IC ramps up the output voltage in a primary side controlled manner. When the voltage at *ZCD* pin exceeds the threshold *V*<sub>ZCDRVS2CRM</sub> the PWM operation is switched over to CRM scheme.

### Figure 33VZCDtarget control during start-up phase

The start-up phase is finished once the feedback loop at *FB* pin takes over the peak current control. This takes place when the peak current setting at *CS* pin determined by  $V_{FB}$  is dropping below the peak current setting determined by  $V_{ZCD}$  ramp-up control. The maximum time period for the start-up phase is limited by a timer when exceeding  $t_{startto}$ , which leads to a start-up timeout (STTOP, see *Chapter 3.4.5*).

Figure 34 Star

Start-up sequence

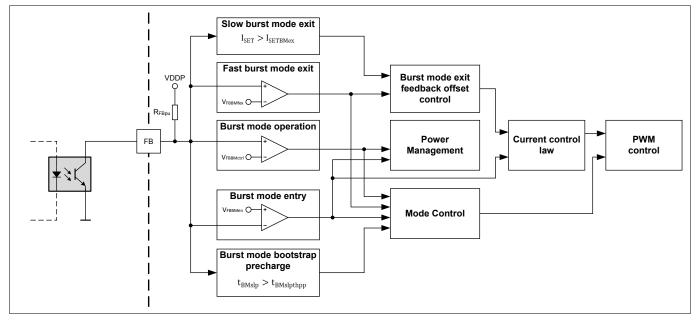

## 3.3.4 Burst mode control

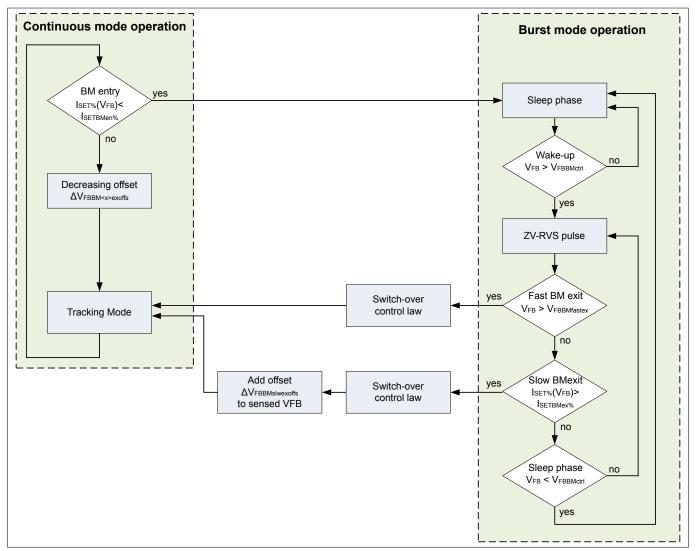

The IC contains a burst mode control block to enter a highly efficient operation mode at light-load. By introducing longer non-switching phases with IC entering a sleep mode the average switching and bias losses are reduced during burst mode operation. A slow and fast burst mode exit is supported in order to have a smooth take-over for feedback voltage regulation, when changing back from hysteretic burst frame on/off control to linear feedback loop control. *Figure 35* shows the main functions for the burst mode control as listed and described in the following:

- Burst mode entry (see *Chapter 3.3.4.1*)

- Burst mode operation (see *Chapter 3.3.4.2*)

- Burst mode bootstrap precharge (see Chapter 3.3.4.3)

- Burst mode exit control (see *Chapter 3.3.4.4*)

### Figure 35 Burst mode control block

## 3.3.4.1 Burst mode entry

The burst mode entry is based on comparing the voltage at *FB* pin with the threshold  $V_{\text{FBBMen}}$ . Once  $V_{\text{FB}}$  is dropping below  $V_{\text{FBBMen}}$  the generation of next switching pulse is stopped and burst mode is enabled by entering sleep mode with the reduced current consumption  $I_{\text{VCCBMpsm}}$ .  $V_{\text{FBBMen}}$  is correlated with the current set-point  $I_{\text{SETBMen}}^{14}$ , which is defined by the output current control law (see *Chapter 3.3.1.3*).

$V_{\text{FBBMen}} = (I_{\text{SETBMen \%}} \times I_{\text{SETnom \%}} \times V_{\text{FBOPmax}}) + V_{\text{FBOPmin}}$

#### **Equation 39**

Once entered burst mode the current control law is switched over to a minimum fixed peak current setting at CS pin, which is based on  $I_{MAGposRVS(+)} + I_{MAGneg}$  (see *Figure 30*).

At burst mode entry the HV start-up cell is used once to charge up the VCC and VCC current consumption is reduced during the sleep phases (see *Chapter 3.2.4*).

<sup>&</sup>lt;sup>14</sup> configurable, see *Table 10*

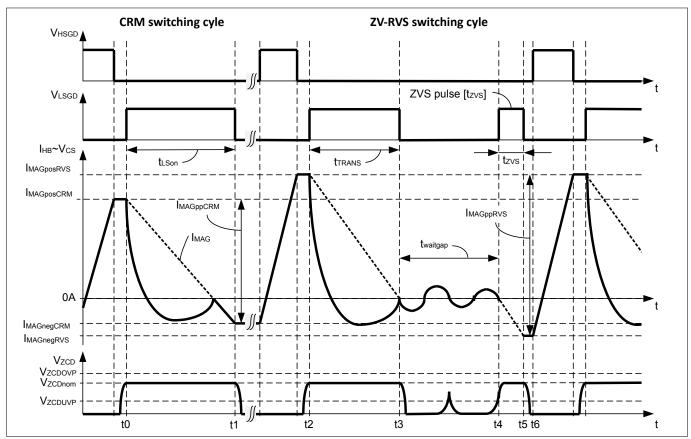

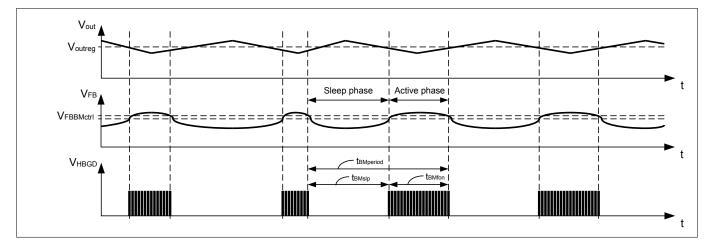

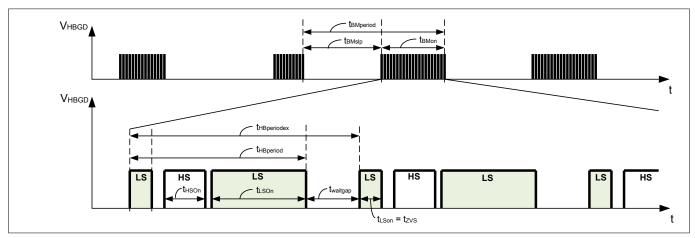

## 3.3.4.2 Burst mode operation

The steady state burst mode operation is based on a burst frame on/off control by means of comparing the voltage at *FB* pin with the feedback burst mode control threshold  $V_{FBBMctrl}$ . This threshold determines when the IC enters the sleep phase (falling edge) after having generated at least one switching pulse during the active phase. The same comparator is also used during the sleep phase for waking up (rising edge) by triggering a burst on-frame pattern  $t_{BMfon}$  (see *Figure 36*). During sleep phase  $V_{FBBMctrl}$  might be slightly lower than during the active phase. Here the burst frame duty cycle and burst mode frequency is fully controlled by means of  $V_{FB}$ .

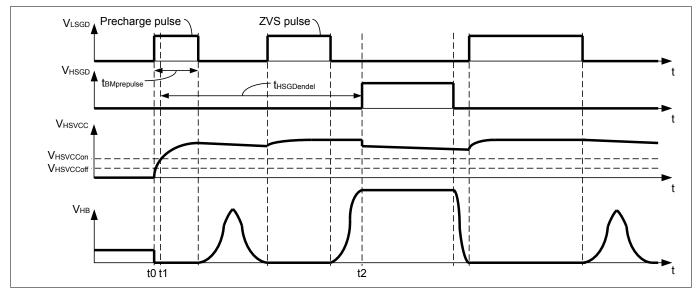

#### Figure 36 Pulse pattern during burst mode operation

During burst frame on-time t<sub>BMfon</sub> the transferred energy is based on ZV-RVS mode switching cycles (see **Chapter 3.3.1.3.2**) with a peak current setting at CS pin only dependent on *Vout* and taking the first valley as base for initiating the ZVS pulse.

In burst mode the peak current setting  $I_{MAGpos}$  is fixed to  $I_{MAGposRVS(+)} + I_{MAGneg}$  (see *Figure 30*). This results in a limited output current during the burst on-frame phase  $I_{outBM}$ :

$$I_{\text{outBM}} = \frac{t_{\text{HBperiod}}}{t_{\text{HBperiodex}}} \times \frac{1}{2} \times N \times \left( I_{\text{MAGposRVS(+)}} + I_{\text{MAGneg}} \right)$$

#### **Equation 40**

The average output current is now depending on the burst on-frame duty cycle (see *Figure 37*):

$$I_{\text{out}} = \frac{t_{\text{BMon}}}{t_{\text{BMperiod}}} \times I_{\text{outBM}}$$

#### **Equation 41**

## **3.3.4.3 Burst mode bootstrap precharge**

Operation in burst mode at very light-load leads to long IC sleep phases without switching activities. During this sleep-time period  $t_{BMSlp}$  (see *Figure 36*) the HSVCC voltage is dropping below the off-threshold  $V_{HSVCCoff}$  and deactivating the floating *HS* gate driver (HSUVOFF, see *Chapter 3.4.3*). When HSVCC is exceeding the on-threshold  $V_{HSVCCon}$  the *HS* gate driver is enabled for turning on the power switch after a delay  $t_{HSGDdelen}$  (see *Chapter 3.3.6*). To ensure that a proper HSVCC supply is in place for turning on the *HS* switch after a long IC sleep phase, a precharge pulse is introduced first before the ZV-RVS pattern is executed (see *Figure 38*). The precharge pulse shall only charge the HSVCC above  $V_{HSVCCon}$  in order to get the *HS* gate driver prematurely enabled. Dimensioning the length of this precharge pulse  $t_{BMprepulse}^{15}$  needs to consider the required delay time period  $t_{HSGDendel}$  for getting enabled the HS gate driver after the HSVCC voltage has exceeded the  $V_{HSVCCon}$  threshold. During this delay time period also one half-bridge oscillation and one ZVS pulse period are taking place. The precharge pulse is only introduced at the beginning of the burst mode on-frame for a subsequent ZV-RVS switching cycle when the captured burst mode sleep-time period is exceeding the threshold  $t_{BMSlothrop}^{15}$ .

Precharge pulse pattern

<sup>&</sup>lt;sup>15</sup> configurable, see *Table 10*

## 3.3.4.4 Burst mode exit control

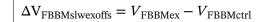

The burst mode exit control supports a smooth switch-over for the closed feedback control loop when leaving burst mode due to load jump or load is slowly increasing beyond a burst mode exit current set-point threshold. There are two burst mode exit paths supported. A strong load jump requires a fast burst mode exit (see *Chapter 3.3.4.4.2*) and immediate full power delivery whereas a slightly increasing load shall be controlled for a smooth switch-over (see *Chapter 3.3.4.4.1*) for the feedback voltage control in order to avoid oscillations at the output. A smaller load jump that leads to a fast burst mode exit shall also not lead to oscillations at the output. Both requirements are covered by introducing an offset  $\Delta V_{\text{FBBM}<x>exoffs}$  on the measured feedback voltage  $V_{\text{FB}}$ , when determining the correlated internal current set-point  $I_{\text{SET}\%}$  based on the output current control law (see *Chapter 3.3.1.3*). Once tracking mode is entered (CRM or continuous ZV-RVS mode operation)  $\Delta V_{\text{FBBM}<x>exoffs}$  is linearly reduced by every half-bridge switching cycle (see *Figure 39*).

### Figure 39 Burst mode exit flow diagram

During burst mode operation the feedback control law only contains two thresholds at *FB* pin and one for the internal current set-point  $I_{SET\%}$  (see *Figure 40*):

- *V*<sub>FBBMctrl</sub> for controlling the burst on-frame and the sleeping phase

- *V*<sub>FBBMfastex</sub> for immediately leaving the burst mode

- *I*<sub>SETBMex%</sub> based on output current estimation for slowly leaving the burst mode

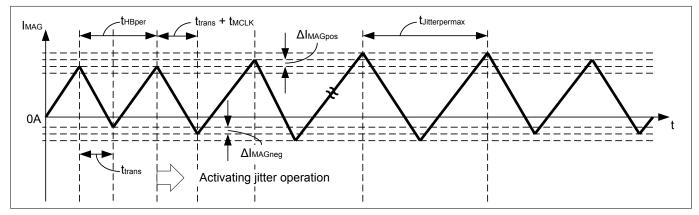

When a burst mode exit condition is met a switch-over of the output current control law is taking place. The feedback voltage level corresponds at that point of time to a different current set-point compared to steady state continuous operation. E.g. if a slow burst mode exit takes place with  $I_{SET\%}(V_{FB}) > I_{SETBMex\%}$ , the feedback