### 1 特性

- 支持 USB Type-C 协议

- 配置为 DFP(Source)

- 广播 3A/1.5A 电流

- 支持 USB Power Delivery (PD) 3.1 以及 PPS 协议

- 通过 PD3.1 和 PPS 认证 (TID: 8739)

- PDO 可配置: 5V, 9V, 12V, 15V, 20V

- 输出功率高至 100W

- APDO 可配置: 5V Prog, 9V Prog, 15V Prog, 20V Prog

- 支持 XPD-LINK™多芯片互联通信技术

- 支持 Quick Charge 3.0+/3.0/2.0+协议

- 支持小米 CHARGE TURBO 27W 协议

- 支持华为 FCP/SCP/HVSCP 协议

- 支持三星 AFC 协议

- 支持 VOOC 协议

- 支持 MTK PE 协议

- 支持 USB BC1.2 DCP

- 支持 Apple 2.4A 充电规范

- 集成 CC、CV 控制环路

- 集成对 E-Marker 线缆的识别和支持

- 支持在线升级功能

- 支持线损补偿功能

- 多重保护、高可靠性

- 输入过压、欠压保护

- 输出过压、过流保护

- 短路保护

- 过温保护

- NTC

- 全引脚 ESD ±4KV

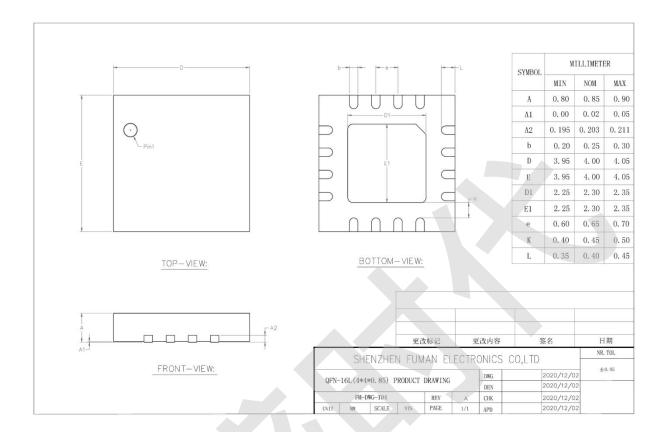

- QFN16 4\*4 封装

### 2 应用

- ACDC 适配器

- 智能排插

- USB 多口充电设备

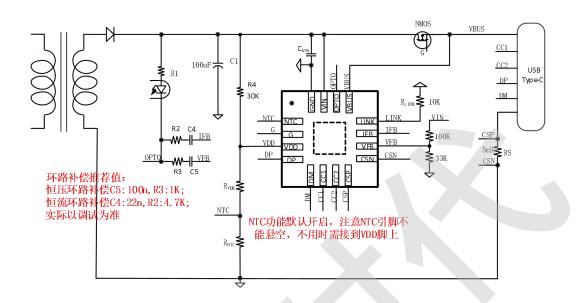

## 3 应用电路图

### 4 概述

XPD701 是一款集成 USB Type-C、USB Power Delivery(PD) 3.1 以及 PPS、QC3.0+/3.0/2.0 快充协议、华为 FCP/SCP/HVSCP 快充协议、三星 AFC 快充协议、VOOC 快充协议、MTK PE 快充协议、BC1.2 DCP 以及苹果设备 2.4A 充电规范的多功能 USB Type-C 单口控制器。

XPD701 特别的集成了 XPD-LINK™互联通信专利技术。通过 XPD-LINK™互联功能, XPD701 可以简单灵活的应用在多个 Type-C 端口的充电方案中。

XPD701 采用外置 NMOS 驱动,输出电压范围是 3.3V 到 21V,能提供最大 100W 的输出功率,能够根据识别到的快充协议自动调整输出电压和电流。

XPD701 的输出具有 CV/CC 特性,当输出电流小于设定值,输出 CV 模式,输出电压恒定;当输出电流大于设定值,输出 CC 模式,输出电压降低。通过一路可 Sink/Source 的电流源,连接到 AC-DC 或 DC-DC 的反馈引脚实现动态调节电压的功能,不管是启动还是调压过程,都具备软启动/调压功能,实现电压平顺过渡。

XPD701 具有线补功能,随着输出电流的增大会相应提高输出电压,用以补偿充电线缆内阻引起的电压下降。

XPD701 内置的 Type-C 协议可以支持 Type-C 设备插入自动唤醒,智能识别插头的正插与反插,并实现连接。XPD701 集成的 PD 协议支持双向标记编码(BMC),集成硬件的物理层协议和协议引擎,无需软件参与编解码

XPD701 具备非常高的可靠性。內建多种保护机制确保设备安全:输入过压、欠压保护,输出过流、过压、欠压、短路打嗝保护等。启动监测(VBUS输出前会监测端口电压是否处于安全状态); DP/DM 和 CC1/CC2 过压保护。

XPD701 支持二次烧录,可实现在线升级。

XPD701 采用 QFN16(4\*4)封装。

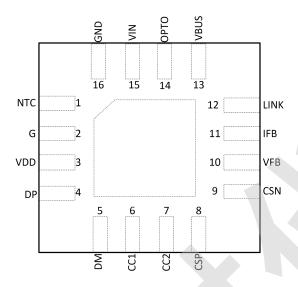

## 5 引脚定义

XPD701 引脚图 (顶视图)

| 编号 | 名称   | 功能描述                |

|----|------|---------------------|

| 1  | NTC  | 温度检测引脚。             |

| 2  | G    | TYPE-C 通路 MOS 控制引脚。 |

| 3  | VDD  | 内部电源供电脚             |

| 4  | DP   | TYPE-C 数据端口 DP。     |

| 5  | DM   | TYPE-C 数据端口 DM。     |

| 6  | CC1  | TYPE-C 数据端口 CC1。    |

| 7  | CC2  | TYPE-C 数据端口 CC2。    |

| 8  | CSP  | TYPE-C 电流检测正极端口。    |

| 9  | CSN  | TYPE-C 电流采样负极端口。    |

| 10 | VFB  | CV 环路补偿脚或者电压调节端口。   |

| 11 | IFB  | CC 环路补偿脚            |

| 12 | LINK | XPD-LINKтм互联功能端口    |

| 13 | VBUS | TYPE-C 端口电压检测引脚。    |

| 14 | ОРТО | 光耦驱动引脚。             |

| 15 | VIN  | 输入电源引脚。             |

| 16 | GND  | 电源地                 |

### 6 订购信息

| 料号            | PDO 和 QC 参数配置                                                                                                                                                                                                                                                  | 封装            |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| XPD701D3517A  | 高功率 PDO:<br>5V/3A,9V/3A,15V/2.33A,20V/1.75A<br>QC 高功率:<br>5V/3A,9V/3A,12V/2.25A,20V/1.35A<br>低功率 PDO:<br>5V/3A,9V/1.94A, 15V/1.16A,20V/0.87A<br>QC 低功率:<br>5V/3A,9V/1.65A,12V/1.25A                                                                            |               |

| XPD701DPS4525 | 高功率 PDO:5V/3A,9V/3A,15V/3A,20V/2.25A<br>高功率 APDO1:3.3-11V/5A<br>高功率 APDO2:3.3-21V/2.25A<br>QC 高功率:<br>5V/3A,9V/3A,12V/3A,20V/2.25A<br>低功率 PDO:5V/3A,9V/2.77A,12V/2.08A<br>低功率 APDO1:3.3-11V/2.25A<br>低功率 APDO2:3.3-21V/1.2A<br>QC 低功率:<br>5V/3A,9V/2A,12V/1.5A | QFN16<br>5K/盘 |

| XPD701DP10065 | 高功率 PDO: 5V/3A,9V/3A,12V/3A,15V/3A,20V/5A 高功率 APDO1:3.3-16V/5A 高功率 APDO2:3.3-21V/5A QC 高功率: 5V/3A,9V/3A,12V/3A,20V/2.25A 低功率 PDO: 5V/3A,9V/3A,12V/3A,15V/3A,20V/3.25A 低功率 APDO1:3.3-16V/3.25A 低功率 APDO2:3.3-21V/3A QC 低功率: 5V/3A,9V/3A,12V/3A,20V/2.25A        |               |

| 可定制           | 根据客户需求定制                                                                                                                                                                                                                                                       |               |

### 印字说明:

第一行, XPD701: 芯片型号;

第二行, XXXXX: Lot Number, X: 保留信息。

- 1、以上料号默认不开启 SCP, VOOC, 如需要支持, 定制时需提前说明

- 2、芯片调压方式默认为 VFB 调压,注意 ACDC 方案需要增加外部反馈电阻,如需采用内置,需要提前说明。

### 选型参考

|        | QC3.0 | FCP/<br>SCP | AFC      | vooc | PD3.0    | PD3.1    | PPS      | СС       | CV       | A+C | XPD-LINK | 在线<br>升级 |

|--------|-------|-------------|----------|------|----------|----------|----------|----------|----------|-----|----------|----------|

| XPD319 | √     | √           | √        |      | <b>√</b> |          | √        |          |          |     |          |          |

| XPD320 | √     | √           | <b>√</b> | √    | √        |          | √        |          |          |     |          |          |

| XPD720 | √     | √           | √        |      | √        |          | <b>√</b> |          | <b>√</b> |     |          |          |

| XPD738 | √     | √           | <b>√</b> |      | √        |          | √        |          | <b>√</b> | √   |          |          |

| XPD737 | √     | √           | √        |      | √        |          | <b>√</b> |          |          |     | √        |          |

| XPD767 | √     | √           | √        |      | √        |          | <b>√</b> |          |          | 1   | <b>√</b> |          |

| XPD920 | √     | √           | √        | √    | √        |          | √        |          | <b>V</b> |     |          | √        |

| XPD938 | √     | √           | √        | √    | <b>√</b> |          | √        | 1        | <b>√</b> | 1   |          | √        |

| XPD930 | √     | √           | √        | √    | √        |          | <b>√</b> | ~        | <b>√</b> |     | √        | √        |

| XPD977 | √     | <b>√</b>    | √        | √    | <b>√</b> |          | <b>√</b> | ~        | 1        | 1   | 1        | <b>√</b> |

| XPD701 | √     | <b>√</b>    | <b>√</b> | √    | <b>√</b> | <b>√</b> | <b>√</b> | <b>√</b> | <b>1</b> |     | √        | <b>√</b> |

| XPD702 | √     | √           | <b>√</b> | √    | <b>√</b> | √        | 1        | 1        | 1        | 1   | √        | √        |

### 7 规格参数

## 7.1 极限工作参数(1)

|      | 参数                               |      | 最大值 | 单位 |  |

|------|----------------------------------|------|-----|----|--|

|      | VIN/VBUS/OPTO                    | -0.3 | 28  | V  |  |

|      | G                                | -0.3 | 32  | V  |  |

| 耐压   | DM/DP/CC1/CC2                    | -0.3 | 7   | V  |  |

|      | NTC/CSP/CSN/IFB/VFB/LINK/<br>VDD | -0.3 | 7   | V  |  |

| 结温   |                                  | -40  | 135 | °C |  |

| 存储温度 |                                  | -55  | 150 | °C |  |

<sup>(1)</sup> 超出极限工作范围值可能会造成器件永久性损坏。长期工作在极限额定值下可能会影响器件的可靠性。

### 7.2 ESD 性能

| 符号                  | 参数         | 值     | 单位 |

|---------------------|------------|-------|----|

| V <sub>ESDHBM</sub> | 人体模型 (HBM) | ±4000 | V  |

ESD 测试基于人体放电模型(HBM)。

## 7.3 推荐工作条件

| 参数                |               | 最小值 | 典型值 | 最大值 | 单位 |

|-------------------|---------------|-----|-----|-----|----|

| VIN               | 输入电压          | 3.3 |     | 21  | V  |

| C <sub>VIN</sub>  | VIN 电容        | 1   |     | 10  | μF |

| R <sub>VFB</sub>  | 系统电压分压电阻      |     | 100 |     | kΩ |

| Rs                | USB-C 口电流检测电阻 |     | 5   |     | mΩ |

| R <sub>LINK</sub> | 互联总线电阻        |     | 10  |     | kΩ |

| TA                | 工作环境温度        | -40 |     | 85  | °C |

## 7.4 热阻值

| 符号    参数          |                  | 值  | 单位   |

|-------------------|------------------|----|------|

| $R_{\theta JA}$   | 结温和周围温度之间的热阻(1)  | 34 |      |

| $R_{	heta JCtop}$ | 结温和封装外壳表面温度之间的热阻 | 32 | °C/W |

| $R_{\theta JB}$   | 结温和板温度之间的热阻      | 10 |      |

### 7.5 电气特性

如无特殊说明,下述参数均在该条件下取得: T<sub>J</sub>= 25℃, 3.3V≤VIN≤21V

|                                  | 参数                              | 测试条件                                           | 最小   | 典型    | 最大   | 单位         |

|----------------------------------|---------------------------------|------------------------------------------------|------|-------|------|------------|

|                                  |                                 | 芯片供电相关(VIN, VBUS)                              |      |       |      |            |

|                                  |                                 | Rising edge                                    |      | 3.2   |      |            |

| $V_{VIN\_TH}$                    | VIN UVLO 门限                     | Falling edge                                   |      | 2.7   |      | V          |

|                                  |                                 | Hysteresis                                     |      | 0.5   |      |            |

| I <sub>SUPP</sub>                | 典型工作电流                          | VPWR=5V,VBUS=5V                                |      | 3     |      | mA         |

|                                  |                                 | Voltage Protection (VBUS)                      |      |       |      |            |

| $V_{FOVP}$                       | Fast OVP 门限,<br>always enabled  | Ref to target voltage                          |      | +20%  |      | V          |

| $V_{SOVP}$                       | Slow OVP 门限                     | Ref to target voltage                          |      | +15%  |      | V          |

| $V_{\text{SUVP}}$                | VBUS UVP 门限                     | Ref to target voltage                          |      | -22%  |      | V          |

| V <sub>PAD_</sub> SHORT          | CC1/CC2/DM1/DP1<br>过压保护门限       | Ref to target voltage                          |      | 5.5   |      | V          |

|                                  |                                 | Transmitter (CC1, CC2)                         |      |       |      |            |

| R <sub>TX</sub>                  | Output resistance               | During transmission                            | 33   | 48    | 75   | Ω          |

| V <sub>TXHI</sub>                | Transmit HIGH                   |                                                | 1.05 | 1.125 | 1.2  | V          |

| V <sub>TXLO</sub>                | Transmit LOW                    |                                                | -75  |       | 75   | mV         |

| tui                              | Bit unit interval               |                                                | 3.05 | 3.3   | 3.70 | us         |

| t <sub>BMC</sub>                 | Rise/fall time of BMC           | R <sub>load</sub> =5.1k,C <sub>load</sub> =1nF | 300  |       | 600  | ns         |

|                                  |                                 | Receiver (CC1, CC2)                            | 1    | 1     |      |            |

| V <sub>RXHI</sub>                | Receive HIGH                    |                                                | 800  | 840   | 885  |            |

| V <sub>RXLO</sub>                | Receive LOW                     |                                                | 485  | 525   | 570  | mV         |

|                                  | CC1/CC2Dreadcasti               | 3A DFP mode, $0 \le V_{CCX} \le 2.5V$          | 304  | 330   | 356  | uA         |

| I <sub>RP_SRC</sub>              | CC1/CC2Broadcasti<br>ng current | 1.5A DFP mode, $0 \le V_{CCX} \le$ 1.5V        | 166  | 180   | 194  | uA         |

|                                  |                                 | ОСР                                            | 1    | 1     |      | •          |

| V <sub>ITRIP</sub>               | Shunt voltage when OCP tripped  | Ref to Power Capability(pd)                    |      | 10    |      | Α          |

|                                  | Oor urpped                      | OTP (internal)                                 |      | 1     |      |            |

|                                  |                                 | Temperature rising edge                        | 125  | 135   | 145  | $^{\circ}$ |

| T <sub>J1</sub>                  | Die temperature                 | Hysteresis                                     |      | 20    |      | $^{\circ}$ |

|                                  |                                 | HVDCP interface (DP, DM)                       |      |       |      |            |

| V <sub>DAT(REF)</sub>            | 数据线检测电压                         |                                                | 0.25 | 0.325 | 0.4  | ٧          |

| V <sub>SEL(REF)</sub>            | 输出电压选择                          |                                                | 1.8  | 2     | 2.2  | V          |

| T <sub>GLITCH(DP)HIGH</sub>      | D+高电平扰动滤<br>波时间                 |                                                | 1    | 1.25  | 1.5  | S          |

| T <sub>GLITCH(DM)</sub> LOW      | D-低电平扰动滤<br>波时间                 |                                                |      | 1     |      | ms         |

| T <sub>GLITCH(V)CHANGE</sub>     | 输出电压扰动滤<br>波时间                  |                                                | 20   | 40    | 60   | ms         |

| T <sub>GLITCH</sub> (CONT)CHANGE | 连续模式的扰动<br>滤波时间                 |                                                | 100  | 150   | 200  | us         |

| R <sub>DAT(LKG)</sub>  | D+漏泄电阻                  |                          | 300   | 500   | 800  | ΚΩ |  |

|------------------------|-------------------------|--------------------------|-------|-------|------|----|--|

| R <sub>DM(DWN)</sub>   | D-下拉电阻                  |                          | 14.25 | 19.53 | 24.5 | ΚΩ |  |

| R <sub>ON(N1)</sub>    | 开关 <b>N1</b> 导通电<br>阻   |                          |       | 40    | 100  | Ω  |  |

| $V_{\text{TH(PD)}}$    | 受电设备连接检<br>测电压阈值        |                          | 0.25  | 0.325 | 0.4  | V  |  |

| $TD_PD$                | 受电设备连接检<br>测滤波时间        |                          | 120   | 160   | 200  | ms |  |

| $\Delta I_{T(UP)}$     | 电压升高时电流<br>源阶跃步长        | R <sub>IREF</sub> =100KΩ |       | 2     |      | uA |  |

| $\Delta I_{T(DO)}$     | 电压降低时电流<br>源阶跃步长        | R <sub>IREF</sub> =100KΩ |       | 2     |      | uA |  |

|                        |                         | Apple 2.4A 充电模式          |       |       |      |    |  |

| V <sub>DAT(2.7V)</sub> | D+/D-数据线电压              |                          | 2.57  | 2.7   | 2.84 | V  |  |

| R <sub>DAT(2.7V)</sub> | D+/D-数据线输出<br>阻抗        |                          |       | 11    |      | ΚΩ |  |

|                        |                         | FCP 充电模式                 |       |       |      |    |  |

| V <sub>TX-VOH</sub>    | D- FCP TX Valid<br>High |                          |       | 2.7   |      | V  |  |

| V <sub>TX-VOL</sub>    | D- FCP TX Valid Low     |                          |       |       | 0.3  | V  |  |

| V <sub>RX-VIH</sub>    | D- FCP RX Valid<br>High |                          |       | 1.2   |      | V  |  |

| V <sub>RX-VIL</sub>    | D- FCP RX Valid<br>High |                          |       | 0.9   |      | V  |  |

| Trise                  | FCP Pulse Rise Time     | 10% - 90%                |       |       | 2.5  | us |  |

| Tfall                  | FCP Pulse Fall Time     | 90% - 10%                |       |       | 2.5  | us |  |

|                        |                         |                          |       |       |      |    |  |

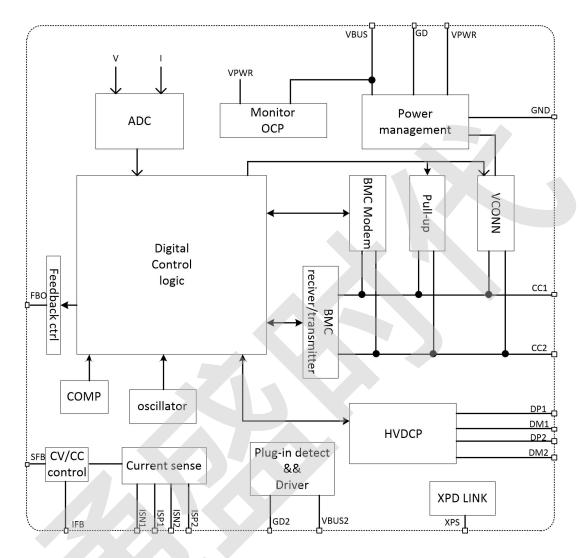

## 8功能描述

### 8.1、功能模块图

## 8.2 、NTC 功能

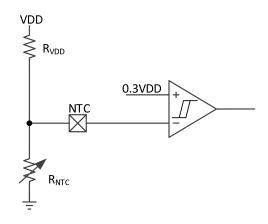

XPD701 集成 NTC 温敏电阻检测可检测 PCB 温度,如上图,NTC 引脚外部通过上拉电阻  $R_{VDD}$  上拉到 VDD 和 NTC 电阻下拉到地。芯片工作时,通过检测 PCB 温度来关闭快充,NTC 的触发点为 0.3VDD。以恭成的 NTC 电阻 QN0603X104F3950FB 为例, $R_{VDD}$  设置为 16K 此时过温点为 100°C 左右。 $R_{VDD}$  电阻的取值计算公式如下:

$$R_{VDD} = \frac{R_{NTC}}{0.3} - R_{NTC}$$

注意这里的 R<sub>NTC</sub> 阻值是需要查对应型号 NTC 电阻的 datasheet 设定温度下的标称值。

### 8.3 、恒压环路与 OPTO、VFB

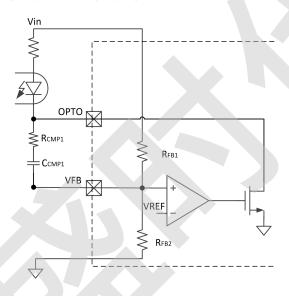

XPD701 内部集成恒压运算放大器,通过 OPTO 和 VFB 形成恒压环路(CV),如下图 所示。OPTO 端口直接驱动光耦,可以省掉传统的 TL431。OPTO 可以耐压至 21V 以上。

恒压环路(CV)需要在外部进行补偿,补偿电阻  $R_{CMP1}$  和补偿电容  $C_{CMP1}$  由具体应用决定。VFB 内部的基准电压为 1.24V,芯片内置 VFB 分压电阻,即 $R_{FB1}$ 和 $R_{FB2}$ ,ACDC 应用时外部可以省掉这两个电阻。如果要改变 VIN 初始电压可以通过下面公式进行换算:

$$R_{FB3} = \frac{1.24 * R_{FB1}}{V_{IN} - 1.24}$$

其中 $R_{FB1}$ 是芯片內置的 100K 电阻, $R_{FB3}$ 是內置的 33K 电阻 $R_{FB2}$ 和外置的 $R_{FB}$ 并联后的阻值,ACDC 应用中只需要通过调整 $R_{FB}$ 的值就可以改变初始输出电压  $V_{IN}$ 。

反馈电阻网络的分压电阻精度会影响 VBUS 电源精度,无论是 ACDC 还是 DCDC 应用都推荐使用 1%精度电阻。

### 8.4、CC 环路

XPD701 内部集成了恒流环路控制,通过 OPTO、IREF 以及 CSN 和 CSP 实现环路控制和电流采样,外部采样电阻为 5mΩ, 该采样电阻需采用开尔文连接,一端为 CSP,另

一端为芯片的 CSN; CC 值根据协议广播的电流来决定,5V 下的 CC 典型值为 3A,精度 在5%以内,而为保证恒流精度推荐采用 1%精度阻值。

### 8.5 、线损补偿

XPD701 具有线损补偿功能,可以根据输出电流按比例(即补偿系数)增加输出电压。补偿系数可以内部配置。例如补偿系数配置为 60mV/A,前端电源空载时输出电压为 5V,当输出电流为 3A 时,前端电源的输出电压会增加至 5.18V。

### 8.6、XPD-LINK™功能

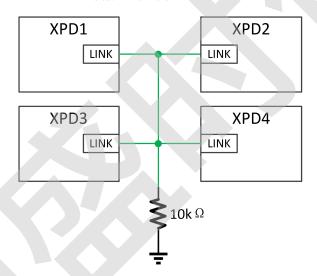

XPD-LINK™是已注册商标的受专利保护的多芯片互联通信技术。XPD701使用 XPD-LINK ™互联技术可以灵活实现多个 USB 端口自动分配前级电源固定额定功率的应用。应用中,将支持 XPD-LINK™互联技术的芯片的 LINK 引脚连接到总线,总线上连接一个阻值为 10K Ω 的电阻到地。每个芯片通过总线传输功率等信息。

### 9应用方案

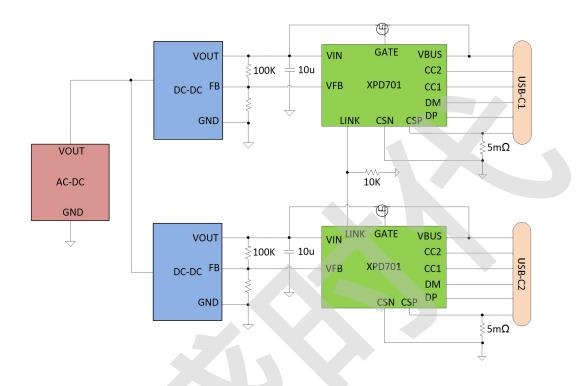

### 9.1、双C互联独立电源方案应用框架图

上面的应用框架图中,使用两颗 XPD701 分别控制 USB-C1 端口和 USB-C2 端口。两颗 XPD701 的 VFB 分别连接到两路 DCDC 电源的反馈网络,采用 VFB 调压。两颗 XPD701 通过 LINK 引脚连接到总线上进行通信。

在这个应用框架图中,任何一个口单独工作都支持快速充电,其中 USB-C1 或 USB-C2 以高档位功率工作。当 USB-C1 与 USB-C2 端口同时工作时,这两个端口依然支持快速充电,并且以低档位功率工作。理论上还可以支持三个及以上的 XPD701 进行多口级联。

以 100W 降 65W 的组合为例说明。控制端口分别为 USB-C1 和 USB-C2:

- 1. 当只有 C1 或 C2 端口工作时,都可以广播输出 100W 功率。

- 2. 当 C1 与 C2 同时工作时,两个端口独立工作,都广播输出 65W 功率。

### 9.2 、Layout 注意事项

- 1. 输入滤波电容,尤其是高频去耦小电容要尽可能的靠近输入引脚 VIN 放置,以提高滤波效果;

- 2. 输入电容和输出电容的地线连接要尽可能的在一点和系统的地线连接起来;

- 3. 采样电阻 RS 需采用开尔文连接, 且尽可能靠近芯片 GND;

- 4. TYPE-C 母座外壳禁止直接连接到 GND 网络,外壳建议连接 CSP 网络;

- 5. PCB 布局时尽量避免与主发热器件摆放在一起;

- 6. 尽量避免 VFB 连线受到干扰。

### 10、封装尺寸