# **Monolithic PCM Repeater**

# **GENERAL DESCRIPTION**

The XR-C240 is a monolithic repeater circuit for Pulse-Code Modulated (PCM) telephone systems. It is designed to operate as a regenerative repeater at 1.544 Megabits per second (Mbps) data rate on T1-type PCM lines.

The XR-C240 monolithic IC is packaged in a hermetic 16-Pin DIP package, and is designed to operate over a temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C. It contains all the basic functional blocks of a regenerative repeater system including Automatic Line Build-Out (ALBO) and equalization, and is insensitive to reflections caused by cable discontinuities.

Compared to conventional repeater designs using discrete components, the XR-C240 monolithic repeater IC offers greatly improved reliability and performance, along with significant savings in power consumption and system cost.

### FEATURES

Contains all Active Components of PCM Repeater On-Chip ALBO Port High-Current Output Drivers Low-Power Consumption Increased Reliability over Discrete Designs 2 Megabit Operation Capability

#### APPLICATIONS

PCM Repeater for T1 Systems PCM Repeater for 2 M Bit/s Systems

#### ABSOLUTE MAXIMUM RATINGS

| Storage Temperature                       | -65°C to +150°C |

|-------------------------------------------|-----------------|

| Operating Temperature                     | -40°C to +85°C  |

| Supply Voltage                            | -0.5 to 10 V    |

| Input Voltage (Except Pin 1,16)           | -0.5 to +7 V    |

| Input Voltage (Pin 7,16)                  | -0.5 to +0.5 V  |

| Data Output Voltage (Pin 8,9)             | +20 V           |

| Voltage Surge (Pin 2,3,8,9) (10 msec only | ) 50 V          |

#### **ORDERING INFORMATION**

| Part Number | Package | Operating Temperature |

|-------------|---------|-----------------------|

| XR-C240     | Ceramic | -40°C to +85°C        |

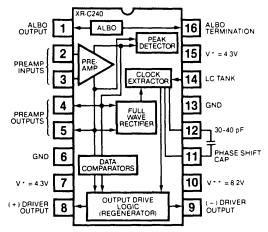

#### FUNCTIONAL BLOCK DIAGRAM

# SYSTEM DESCRIPTION

The XR-C240 contains all the active circuits required to build one side of a T1 or 2 M bit/s PCM repeater. T1 is the most widely used PCM transmission system, operating at 1.544 M bit/s. It can operate on either pulp or plastic insulated twisted pair cables. Although the cable gauge may vary, the total cable loss should not exceed 36 dB at 772 kHz. For a 22 gauge pulp insulated cable and a bit error rate (BER) of less than 10<sup>-6</sup>, the max allowable repeater to repeater spacing is about 6300 feet.

Bipolar PCM signal is attenuated and dispersed in time as it travels along a transmission cable. This signal, when received, is amplified and reconstructed by the preamplifier automatic line build out (ABLO), clock and data threshold detector circuits contained within the XR-C240. Amplitude equalization and frequency spectrum shaping is achieved through the variable impedance of the ALBO ports and its associated ALBO network.

Incoming pulse stream is full wave rectified and timing information is extracted by the clock threshold detector. Clock recovery is then achieved by driving an injection locked oscillator tuned to 1.544 MHz. The oscillator's sinusoidal waveform is amplified and phase shifted by 90 degrees with the help of a capacitor between Pins 11 and 12.

Data is sampled and stored in the output data latches by an internally generated sampling pulse. Buffer drivers are then enabled to produce precisely timed output pulses whose width and time of occurence are controlled by the regenerated clock signal.

# ELECTRICAL CHARACTERISTICS

(Measured at  $25^{\circ}$ C with V++ = 8.2V, V+ = 4.3V, unless specified otherwise.)

| PARAMETERS                             | LIMITS |           |             | CONDITIONS                                                                                        |

|----------------------------------------|--------|-----------|-------------|---------------------------------------------------------------------------------------------------|

| FARAMETERS                             | MIN.   | MAX.      | UNIT        | CONDITIONS                                                                                        |

| Supply Voltage:                        |        |           | <b>(</b> ,, |                                                                                                   |

| V++                                    | 7.79   | 8.61      | V           | Measured at Pin 10                                                                                |

| V+                                     | 4.085  | 4.515     | V           | Measured at Pins 7 and 15                                                                         |

| Supply Current:                        | ·      |           | •           |                                                                                                   |

| IA IA                                  | 1.1    | 2.5       | mA          |                                                                                                   |

| l IB                                   | 6      | 11        | mA          | Supply ≈ 8.2V                                                                                     |

| Total Current                          | 7.9    | 13.5      | mA          |                                                                                                   |

| Preamplifier                           |        |           |             |                                                                                                   |

| Input Offset Voltage, VOS              |        | 15        | mV          |                                                                                                   |

| Open Loop Differential Gain, AO        | 50     | 54        | dB          |                                                                                                   |

| Input Bias Current, IB                 |        | 4         | μΑ          |                                                                                                   |

| Input Offset Current, IOS              |        | 2         | μA          |                                                                                                   |

| Input Impedance, Rin                   | 50     |           | kΩ          |                                                                                                   |

| Comparator Thresholds                  |        |           |             |                                                                                                   |

| Peak Detector (ALBO) Threshold         | ±1.3   | ±1.6      | V           | Measured Differentially Across Pins 4 and 5                                                       |

| Full-Wave Rectifier Threshold          | ±0.9   | ±1.15     | V           |                                                                                                   |

| Data Threshold                         | ±0.28  | ±0.48     | V           |                                                                                                   |

| Clock Extractor Section                |        |           |             |                                                                                                   |

| Tank Drive Impedance                   | 50     |           | kΩ          | At Pin 14                                                                                         |

| Tank Drive Current                     |        | 1         |             |                                                                                                   |

| "Zero" Signal Current                  | 12     | 24        | μA          |                                                                                                   |

| "One" Signal Current                   | 80     | 220       | μA          |                                                                                                   |

| Recommended Tank Q                     | 100    | {         |             |                                                                                                   |

| Phase Shifter Offset Voltage           | -18    | +18       | mV          | Voltage applied to Pins 7 and 14 to reduce<br>differential voltage across Pins 11 and 12 to zero. |

| Output Drive Section                   |        |           | L           | L                                                                                                 |

|                                        |        |           |             | Voltage levels referenced to Pin 7                                                                |

| Output Voltage Swing                   | 3.0    | 0.05      |             | $R_{L} = 100 \Omega$                                                                              |

| Low Output Voltage                     | 0.65   | 0.95      | V           | Referenced to Pin 7, IL = 30 mA                                                                   |

| Output Leakage Current<br>Output Pulse |        | 50        | μΑ          |                                                                                                   |

| Maximum Pulse Width Error              |        | ±30       |             | • · · · · · · · · · · · · · · · · · · ·                                                           |

| Rise and Fall Times                    |        | ±30<br>80 | ns          |                                                                                                   |

|                                        |        | <u>ov</u> | ns          | 1                                                                                                 |