## **B8ZS/AMI** Line Transcoder

#### **GENERAL DESCRIPTION**

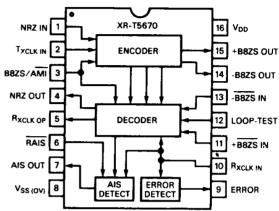

The XR-T5670 is an LSI CMOS integrated circuit which performs the B8ZS or AMI transmission coding and receiving decoding functions with error detection. It is intended for DS1 (1.544MBPS) PCM transmission applications, but can operate at clock frequencies up to 6MHz.

#### **FEATURES**

B8ZS Coding and Decoding for Data Rates up to 6MBPS to AT&T Technical Advisory 69

B8ZS/AMI Transmission Coding/Reception Decoding with Code Error Detection

All Transmitter and Receiver Inputs/Outputs are TTL Compatible

Internal Loop Test Capability

Single 5V ± 10% Supply Rail

#### **ABSOLUTE MAXIMUM RATINGS**

| DC Supply Voltage (V <sub>DD</sub> )   | -0.3 to 7.0V              |

|----------------------------------------|---------------------------|

| Input Voltage Range (V <sub>IN</sub> ) | $-0.3$ to $V_{DD} + 0.3V$ |

| Input Protection Current (ID)          | ±10mA                     |

| Storage Temperature Range              | -55°C to 150°C,           |

### PIN ASSIGNMENT

#### ORDERING INFORMATION

| Part Number | Package | Operating Temperature |  |  |

|-------------|---------|-----------------------|--|--|

| XR-T5670CP  | Plastic | 0°C to 70°C           |  |  |

| XR-T5670CN  | Ceramic | –40°C to +85°C        |  |  |

#### **APPLICATIONS**

AMI Encoding/Decoding B8ZS Encoding/Decoding

#### SYSTEM DESCRIPTION

#### Coder

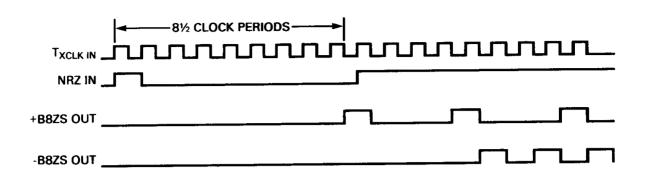

Binary data in "NRZIN" is clocked into the coder by a synchronous transmission clock "T<sub>XCLKIN</sub>" on the failing edge. The "+B8ZS" and "-B8ZS" output signals appear 8.5 clock cycles later to allow for the insertion of extra pulses due to sequences of eight consecutive zeros. These two signals are full width data and will be mixed with the "T<sub>XCLKIN</sub>" at the input of an external line driver to produce bipolar B8ZS signals for transmission.

#### Decoder

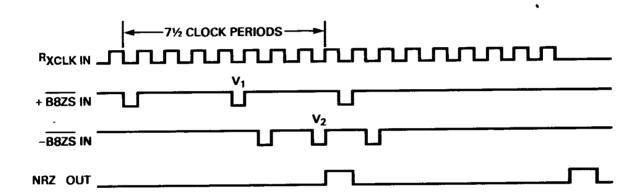

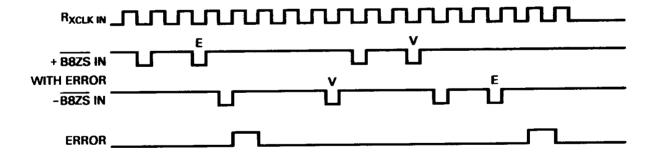

Received half width data on "+B8ZSIN" and "-B8ZSIN" are locked into the decoder on the rising edge of the received clock "R<sub>XCLKIN</sub>". The "NRZOUT" binary data output occurs on eight clock cycles later. Received signals not consistant with B8ZS coding rules are detected as

errors. The error output "ERROR" is active high during one "R<sub>XCLKIN</sub>" clock period. The error output is not an accurate measure of error count; it is intended for alarm indication only.

#### AIS (Alarm Indication Signal)

If the decoder inputs received a continuous of ones (all marks) over two consecutive periods of the external reset signal "RAIS", the "AISOUT" output will be set high and latched in that state until one or more zeros are received when the next reset signal "RAIS" occurs.

The number of received zeros required to reset "AISOUT" over two consectuive periods of "RAIS" can be mask programmed to two or three.

# XR-T5670

#### **ELECTRICAL CHARACTERISTICS**

**Test Conditions:**  $T_A = -40^{\circ}\text{C}$  to +85°C,  $V_{DD} = 4.5$  to 5.5V, unless specified otherwise.

| SYMBOL           | PARAMETERS                           | MIN. | TYP. | MAX | UNIT | CONDITIONS                                                                    |

|------------------|--------------------------------------|------|------|-----|------|-------------------------------------------------------------------------------|

| DYNAMIC CH       | IARACTERISTICS                       |      |      |     |      |                                                                               |

| TXCLKIN          | Clock Input Frequency                |      |      | 6   | MHz  |                                                                               |

| RXCLKIN          | Clock Input Frequency                |      |      | 6   | MHz  |                                                                               |

| t <sub>s1</sub>  | Data Set-Up Time                     | 55   |      |     | ns   | NRZIN to T <sub>XCLKIN</sub><br>See Figure 6                                  |

| t <sub>h1</sub>  | Data Hold Time                       | 25   |      |     | ns   | NRZIN to T <sub>XCLKIN</sub><br>See Figure 6                                  |

| <sup>t</sup> pd1 | Data Propagation Delay Time          |      |      | 65  | ns   | T <sub>XCLKIN</sub> to B8ZS OUT<br>See Figure, 3 and 6. Note 1                |

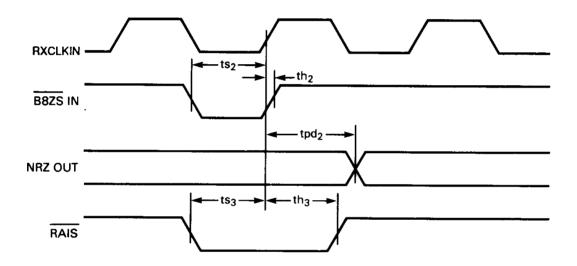

| t <sub>s2</sub>  | Data Set-Up Time                     | 55   |      |     | ns   | B8ZSIN to R <sub>XCLKIN</sub><br>See Figure 7, Loop Test = 0                  |

| t <sub>h2</sub>  | Data Hold Time                       | 0    |      |     | ns   | B8ZSIN to R <sub>XCLKIN</sub><br>See Figure 7, Loop Test = 0                  |

| t <sub>pd2</sub> | Data Propagation Delay Time          |      |      | 90  | ns   | R <sub>XCLKIN</sub> to NRZOUT<br>See Figures 4 and 7, Note 2<br>Loop Test = 0 |

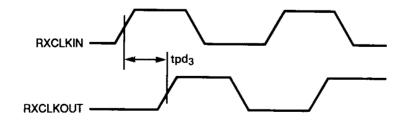

| <sup>t</sup> pd3 | Clock Delay Time                     |      |      | 50  | ns   | R <sub>XCLK</sub> IN to R <sub>XCLKOUT</sub><br>See Figure 8, Loop Test = 0   |

| t <sub>s3</sub>  | RAIS = 0 Set-Up Time                 | 30   |      |     | ns   | RAIS to R <sub>XCLKIN</sub><br>See Figure 7                                   |

| t <sub>h3</sub>  | RAIS= 0 Hold Time                    | 30   |      |     | ns   | RAIS to R <sub>XCLKIN</sub>                                                   |

| STATIC CHA       | RACTERISTICS, V <sub>DD</sub> = 5.0V |      |      |     |      |                                                                               |

| I <sub>DD</sub>  | Quiescent Device Current             |      |      | 100 | μΑ   |                                                                               |

|                  | Operating Current                    |      |      | 4   | mA   | Input Clock Frequency = 2.0MHz                                                |

| $V_{DD}$         | Supply Voltage                       | 4.5  | 5    | 5.5 | V    |                                                                               |

| V <sub>IN</sub>  | Input Voltage 0                      | 0    |      | 5.0 | l v  |                                                                               |

| $V_{IL}$         | Input Low Voltage                    |      |      | 0.8 | V    |                                                                               |

| V <sub>IH</sub>  | Input High Voltage                   | 2    |      |     | V    |                                                                               |

| V <sub>OL</sub>  | Output Low Voltage                   |      |      | 0.1 | v    | 1 <sub>OL</sub> = 0                                                           |

| V <sub>OH</sub>  | Output High Voltage                  | 4.9  |      |     | v    | I <sub>OH</sub> = 0                                                           |

| loL              | Output Lo, Current                   | 1.6  |      |     | mA   | V <sub>OL</sub> = 0.4V                                                        |

| Іон              | Output High Current                  | -1   |      |     | mA   | V <sub>OH</sub> = 4.6V                                                        |

| I <sub>IL</sub>  | Input Low Current                    |      |      | -10 | μА   | V <sub>IL</sub> = 0V                                                          |

| t <sub>iH</sub>  | Input High Current                   |      |      | 10  | μА   | V <sub>IH</sub> = 5V                                                          |

Note 1: The encoded B8ZS OUT are delayed by 8 1/2 clock periods from NRZIN.

Note 2: The decoded NRZOUT are delayed by 7 = clock periods from B8ZS IN.

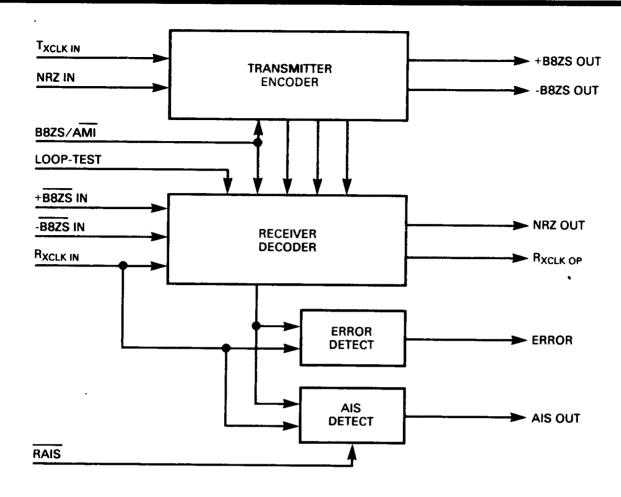

Figure 1. XR-T5670 Block Diagram

#### **Loop Test**

When the Loop Test control input is set high, a test mode is made in which the "+B8ZSOUT" and "-B8ZSOUT" are internally connected to the decoder inputs. The external B8ZS inputs and the "RXCLKIN" are disabled, and the "TXCLKIN" is used to control the decoder timing. The "NRZOUT" signals correspond to the "NRZIN" input, but delayed by 16 clock periods.

#### **B8ZS/AMI**

To operate the XR-T5670 in AMI mode, the B8ZS/AMI control input is driven low. In this mode, two consecutive pulses of the same polarity at the decoder inputs will be detected and flagged as an error at the "ERROR" output.

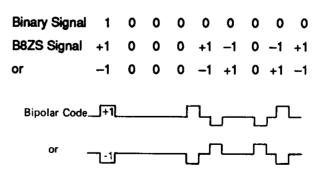

#### Definition of B8ZS Code Used in XR-T5670 Transcoder

With B8ZS coding, each block of eight consecutive zeros is removed and the B8ZS code is inserted. If the pulse

preceding the inserted code is transmitted as a positive pulse (+), the inserted code is 000+-0-+. Bipolar violations occur in the fourth and seventh bit position of the inserted code. If the pulse preceding the inserted code is a negative pulse (-), the inserted code is 000-+0+-. Bipolar violations again occur in the fourth and seventh bit positions as illustrated in Figure 2.

Figure 2. B8ZS Code

Figure 3. Encoder Waveforms

Figure 4. Decoder Waveforms

Figure 5. B8ZS Error Output Waveforms

Figure 6. Encoder Timing Relationship

Figure 7. Decoder Timing Relationship

Figure 8. RXCLKIN To R XCLKOUT Relationship