Receiver Rev. V1 30.0-46.0 GHz Mimix Broadband

#### **Features**

- Sub-harmonic Receiver

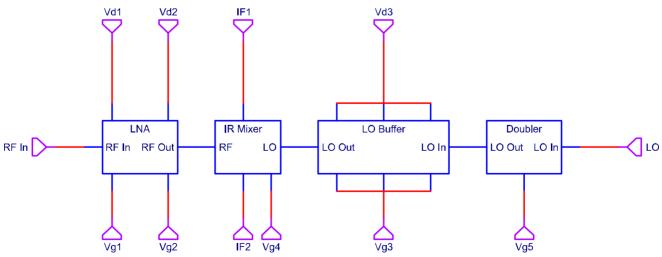

- Integrated LNA, LO Doubler/Buffer, Image Reject Mixer

- +4.0 dBm Input Third Order Intercept (IIP3)

- +2.0 dBm LO Drive Level

- 9.0 dB Conversion Gain

- 3.5 dB Noise Figure

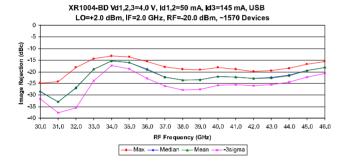

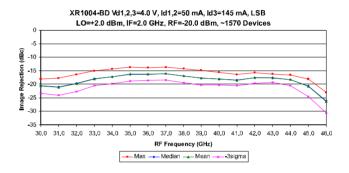

- 18.0 dB Image Rejection

- 100% On-Wafer RF, DC & Noise Figure Testing

- 100% Commercial-Level Visual Inspection Using Mil-Std-883 Method 2010

- RoHS\* Compliant and 260°C Reflow Compatible

#### **Description**

M/A-COM Tech's 30.0-46.0 GHz GaAs MMIC receiver has a noise figure of 3.5 dB and 18.0 dB image rejection across the band. This device is a three stage LNA followed by an image reject resistive pHEMT mixer and includes an integrated LO doubler and LO buffer amplifer. The image reject mixer eliminates the need for a bandpass filter after the LNA to remove thermal noise at the image frequency. The use of integrated LO doubler and LO buffer amplifier makes the provision of the LO easier than for fundamental mixers at these frequencies. I and Q mixer outputs are provided and an external 90 degree hybrid is required to select the desired sideband. This MMIC uses M/A-COM Tech's GaAs PHEMT device model technology, and is based upon electron beam lithography to ensure high repeatability and uniformity. The chip has surface passivation to protect and provide a rugged part with backside via holes and gold metallization to allow either a conductive epoxy or eutectic solder die attach process. This device is well suited for Radio, Millimeter-wave Point-to-Point SATCOM and VSAT applications.

### **Ordering Information**

Commitment to produce in volume is not guaranteed.

| Part Number    | Package                                                                    |  |  |  |

|----------------|----------------------------------------------------------------------------|--|--|--|

| XR1004-BD-000V | Where "V" is RoHS compli-<br>ant die packed in vacuum<br>released gel paks |  |  |  |

| XR1004-BD-EV1  | evaluation module                                                          |  |  |  |

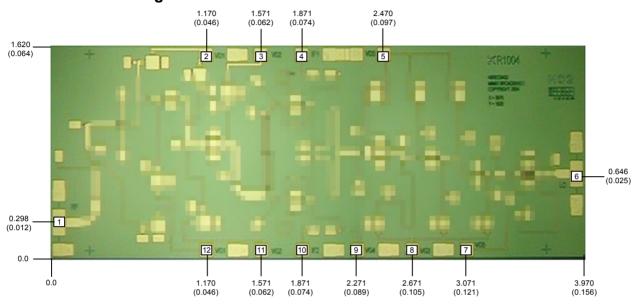

#### **Chip Device Layout**

### **Absolute Maximum Ratings**

| Parameter                     | Absolute Max.                |  |  |

|-------------------------------|------------------------------|--|--|

| Supply Voltage (Vd)           | +6.0 VDC                     |  |  |

| Supply Current (Id1,2), (Id3) | 110,180 mA                   |  |  |

| Gate Bias Voltage (Vg)        | +0.3 VDC                     |  |  |

| Input Power (RF Pin)          | +5 dBm                       |  |  |

| Storage Temperature (Tstg)    | -65 °C to +165 °C            |  |  |

| Operating Temperature (Ta)    | -55 °C to Table <sup>1</sup> |  |  |

| Channel Temperature (Tch)     | MTTF Table <sup>1</sup>      |  |  |

Channel temperature affects a device's MTTF. It is recommended to keep channel temperature as low as possible for maximum life.

Receiver Rev. V1 30.0-46.0 GHz Mimix Broadband

### Electrical Specifications: 35-46 GHz (RF/Upper Side Band) (Ambient Temperature T=25°C)

| Parameter                                               | Units | Min. | Тур.      | Max. |

|---------------------------------------------------------|-------|------|-----------|------|

| Frequency Range (RF) Lower Side Band                    | GHz   | 30.0 | -         | 46.0 |

| Frequency Range (LO)                                    | GHz   | 15.5 | -         | 25.0 |

| Frequency Range (IF)                                    | GHz   | DC   | -         | 4.0  |

| Input Return Loss RF (S11)                              | dB    | -    | 10.0      | -    |

| Small Signal Conversion Gain RF/IF (S21) <sup>2</sup>   | dB    | 9.0  | 9.0       | -    |

| LO Input Drive (P <sub>LO</sub> )                       | dBm   | -    | +2.0      | -    |

| Image Rejection <sup>2</sup>                            | dBc   | 15.0 | 18.0      | -    |

| Noise Figure (NF) <sup>2</sup>                          | dB    | -    | 3.5       | 4.0  |

| Isolation LO/RF @ LOx1/LOx2                             | dB    | -    | 40.0/40.0 | -    |

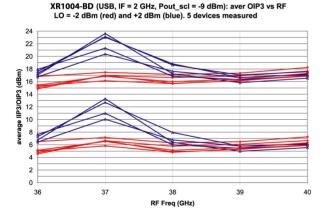

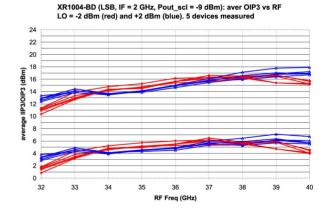

| Input Third Order Intercept (IIP3) <sup>1,2</sup>       | dBm   | -    | +4.0      | -    |

| Drain Bias Voltage (Vd1,2,3)                            | VDC   | -    | +4.0      | +5.5 |

| Gate Bias Voltage (Vg1,2,3)                             | VDC   | -1.2 | -0.3      | +0.1 |

| Gate Bias Voltage (Vg4,5) Mixer, Doubler                | VDC   | -1.2 | -0.5      | +0.1 |

| Supply Current (Id1,2) (Vd1,2=4.0 V, Vg=-0.3 V Typical) | mA    | -    | 50        | 100  |

| Supply Current (ld3) (Vd3=4.0 V, Vg=-0.3 V Typical)     | mA    | -    | 145       | 165  |

- (1) Measured using constant current.

- Measured using LO Input drive level of 0.0 and +2.0 dBm.

### **Block Diagram & Schematics**

typical. Mechanical outline has been fixed. Engineering samples and/or test data may be available.

Commitment to produce in volume is not guaranteed.

Receiver Rev. V1

30.0-46.0 GHz Mimi× Broadband

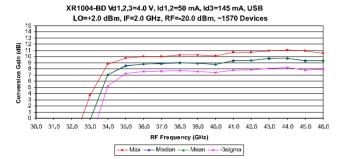

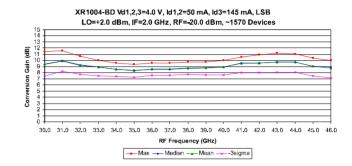

## **Typical Performance Curves**

• India Tel: +91.80.43537383

• China Tel: +86.21.2407.1588

Visit www.macomtech.com for additional data sheets and product information.

Receiver Rev. V1 30.0-46.0 GHz Mimix Broadband

#### **Mechanical Drawing**

(Note: Engineering designator is 40REC0452)

Units: millimeters (inches) Bond pad dimensions are shown to center of bond pad. Thickness: 0.110 +/- 0.010 (0.0043 +/- 0.0004), Backside is ground, Bond Pad/Backside Metallization: Gold All DC/IF Bond Pads are 0.100 x 0.100 (0.004 x 0.004). All RF Bond Pads are 0.100 x 0.200 (0.004 x 0.008) Bond pad centers are approximately 0.109 (0.004) from the edge of the chip. Dicing tolerance: +/- 0.005 (+/- 0.0002). Approximate weight: 3.987 mg.

Bond Pad #1 (RFIn) Bond Pad #3 (Vd2) Bond Pad #5 (Vd3) Bond Pad #7 (Vg5) Bond Pad #9 (Vg4) Bond Pad #11 (Vg2) Bond Pad #2 (Vd1) Bond Pad #4 (IF1) Bond Pad #6 (LO) Bond Pad #8 (Vg3) Bond Pad #10 (IF2) Bond Pad #12 (Vg1)

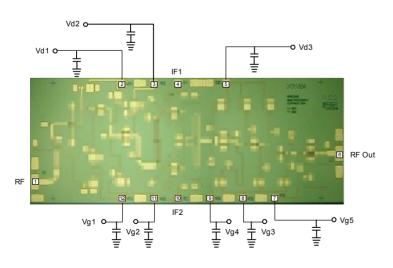

## **Bias Arrangement**

#### Bypass Capacitors - See App Note [2]

ADVANCED: Data Sheets contain information regarding a product M/A-COM Technology Solutions is considering for development. Performance is based on target specifications, simulated results, and/or prototype measurements. Commitment to develop is not guaranteed.

PRELIMINARY: Data Sheets contain information regarding a product M/A-COM Technology Solutions has under development. Performance is based on engineering tests. Specifications are typical. Mechanical outline has been fixed. Engineering samples and/or test data may be available. Commitment to produce in volume is not guaranteed.

• North America Tel: 800.366.2266 • Europe Tel: +353.21.244.6400

• India Tel: +91.80.43537383

• China Tel: +86.21.2407.1588

Visit www.macomtech.com for additional data sheets and product information.

Receiver Rev. V1

30.0-46.0 GHz Mimi× Broadband

### MTTF Table (TBD)

These numbers were calculated based on accelerated life test information and thermal model analysis received from the fabricating foundry.

| Backplate<br>Temperature | Channel<br>Temperature | Rth | MTTF Hours | FITs |

|--------------------------|------------------------|-----|------------|------|

| 55 deg Celsius           | deg Celsius            | C/W | E+         | E+   |

| 75 deg Celsius           | deg Celsius            | C/W | Et         | E+   |

| 95 deg Celsius           | deg Celsius            | C/W | Đ          | E+   |

Bias Conditions: Vd1=Vd2=Vd3=4.0V, Id1=Id2=25 mA, Id3=145 mA

Receiver Rev. V1

30.0-46.0 GHz Mimi× Broadband

App Note [1] Biasing - As shown in the bonding diagram, this device is operated by separately biasing Vd1, Vd2 and Vd3 with Vd(1,2,3)=4.0V, Id1=Id2=25mA and Id3=145mA. Additionally, a mixer and doubler bias are also required with Vg4=Vg5=-0.5V. Adjusting Vg4 and Vg5 above or below this value can adversely affect conversion gain, image rejection and intercept point performance. It is also recommended to use active biasing to keep the currents constant as the RF power and temperature vary; this gives the most reproducible results. Depending on the supply voltage available and the power dissipation constraints, the bias circuit may be a single transistor or a low power operational amplifier, with a low value resistor in series with the drain supply used to sense the current. The gate of the pHEMT is controlled to maintain correct drain current and thus drain voltage. The typical gate voltage needed to do this is -0.3V. Typically the gate is protected with Silicon diodes to limit the applied voltage. Also, make sure to sequence the applied voltage to ensure negative gate bias is available before applying the positive drain supply.

#### App Note [2] Bias Arrangement -

For Parallel Stage Bias (Recommended for general applications) -- The same as Individual Stage Bias but all the drain or gate pad DC bypass capacitors (~100-200 pF) can be combined. Additional DC bypass capacitance (~0.01 uF) is also recommended to all DC or combination (if gate or drains are tied together) of DC bias pads.

For Individual Stage Bias -- Each DC pad (Vd1,2,3 and Vg1,2,3,4,5) needs to have DC bypass capacitance (~100-200 pF) as close to the device as possible. Additional DC bypass capacitance (~0.01 uF) is also recommended.

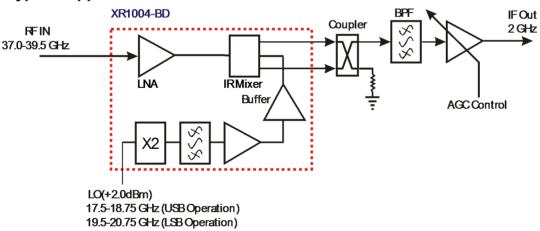

### **Typical Application**

## M/A-COM Tech MMIC-based 30.0-46.0 GHz Receiver Block Diagram (Changing LO and IF frequencies as required allows design to operate as high as 46 GHz)

M/A-COM Tech's 30.0-46.0 GHz XR1004-BD GaAs MMIC Receiver can be used in saturated radio applications and linear modulation schemes up to 128 QAM. The receiver can be used in upper and lower sideband applications from 30.0-46.0 GHz.

Commitment to produce in volume is not guaranteed.

India Tel: +91.80.43537383

China Tel: +86.21.2407.1588

Visit www.macomtech.com for additional data sheets and product information.

Receiver Rev. V1 30.0-46.0 GHz Mimix Broadband

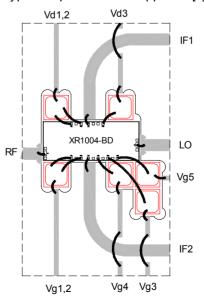

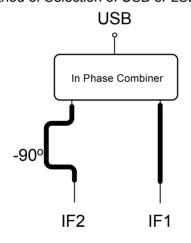

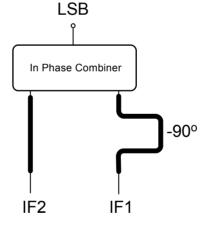

#### App Note [3] USB/LSB Selection -

#### An alternate method of Selection of USB or LSB:

#### For Upper Side Band operation (USB):

With IF1 and IF2 connected to the direct port (0°) and coupled port (90°) respectively as shown in the diagram, the USB signal will reside on the isolated port. The input port must be loaded with 50 ohms.

#### For Lower Side Band operation (LSB):

With IF1 and IF2 connected to the direct port (0°) and coupled port (90°) respectively as shown in the diagram, the LSB signal will reside on the input port. The isolated port must be loaded with 50 ohms.

Commitment to produce in volume is not guaranteed.

Receiver 30.0-46.0 GHz Mimix Broadband

### **Handling Procedures**

Please observe the following precautions to avoid damage:

### **Static Sensitivity**

Gallium Arsenide Integrated Circuits are sensitive to electrostatic discharge (ESD) and can be damaged by static electricity. Proper ESD control techniques should be used when handling these class 2 devices.

• India Tel: +91.80.43537383