# Two-Step LED Current Controller with Line Regulation Compensation

#### **Description**

The XR46073 is a two-step LED current controller with line regulation compensation for operating over a wide Alternative Current (AC) voltage source range. It can drive an external N-channel power MOSFET to regulate the current flowing through a High Voltage (HV) LED string.

The XR46073 works as a constant current sink with linear type Overvoltage Protection (OVP), linear type Over Temperature Protection (OTP) and line regulation compensation. It is suitable for applications with a rectified AC voltage source.

The PCB design can be very compact to meet various shape requirements. It is especially suitable for replacing incandescent light bulbs.

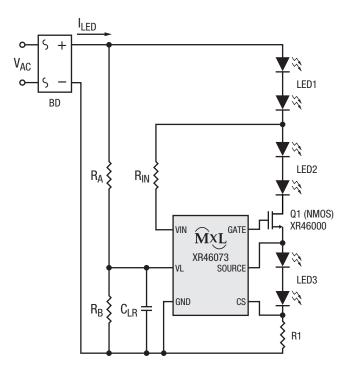

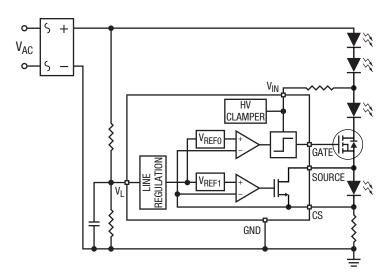

## **Typical Application**

Figure 1. Typical Application

#### **FEATURES**

#### **Device**

- Two-current step control from a single device

- Excellent system power regulation over AC input range

- 6V to 76V chip supply voltage range

- Over temperature protection

- Overvoltage protection

- TDFN-6 2mm x 2mm package

#### System

- Single board LED lighting solution available

- No electrolytic capacitor or MOV required

- Scalable architecture allows optimization of performance vs. cost

- Driver-on-board and chip-on-board design solution available which minimize process flow and assembly cost

- High PF and Low THD performance

- Flexible PCB layout options

- TRIAC dimmable

- All solid state components

#### **APPLICATIONS**

- LED Lighting Applications

- Downlight

- □ High bay

- □ Specialty

- Architectural

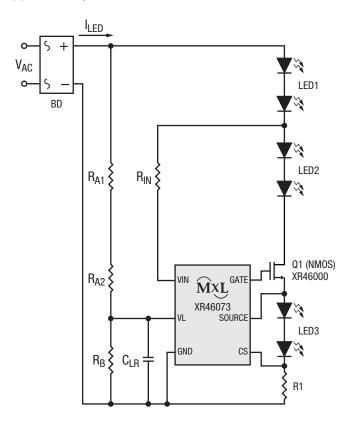

Figure 2. Two-Step 120V<sub>AC</sub>

### **Absolute Maximum Ratings**

Stresses beyond the limits listed below may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

| V <sub>IN</sub> , GATE, SOURCE to GND0.3V to 85V     |

|------------------------------------------------------|

| SOURCE to CS0.3V to 70V                              |

| GATE to SOURCE0.3V to 7V                             |

| VL to GND0.3V to 7V                                  |

| CS to GND0.3V to 1V                                  |

| V <sub>IN</sub> input current                        |

| SOURCE to CS current                                 |

| Maximum operating junction temperature, $T_J$ 150°C  |

| Operating temperature, T <sub>OPR</sub> 40°C to 85°C |

| Storage temperature range55°C to 150°C               |

| Lead temperature (soldering, 10 seconds) 260°C       |

| ESD Rating                                           |

| HBM (Human Body Model)±2kV                           |

| MM (Machine Model±200V                               |

# **Operating Conditions**

| V <sub>IN</sub>      | .6V | ′ to 76\ | / |

|----------------------|-----|----------|---|

| Peak level current20 | to  | 180mA    | ١ |

#### NOTES:

<sup>1.</sup> All voltages are with respect to ground. Currents are positive into negative out of the specified terminal.

<sup>2.</sup> All parameters having min/max specifications are guaranteed. Typical values are for reference purpose only.

<sup>3.</sup> Unless otherwise noted, all tests are pulsed tests at the specified temperature, therefore:  $T_J = T_C = T_A$ .

#### **Electrical Characteristics**

Unless otherwise noted, typical values are at  $T_A = 25$ °C.

| Symbol                               | Parameter                                                               | Conditions                                                                                                                              | Min | Тур   | Max | Units |  |

|--------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|-------|--|

| V <sub>IN,MIN</sub>                  | Minimum V <sub>IN</sub> supply voltage                                  |                                                                                                                                         | 6   |       |     | V     |  |

| I <sub>IN</sub>                      | V <sub>IN</sub> supply current                                          | V <sub>IN</sub> = 6V to 73V                                                                                                             |     | 0.3   |     | mA    |  |

| V <sub>IN,CLAMP</sub>                | V <sub>IN</sub> overvoltage clamp                                       | When V <sub>IN</sub> >V <sub>IN, CLAMP</sub> , I <sub>IN</sub> will increase to >1mA to clamp V <sub>IN</sub> at V <sub>IN, CLAMP</sub> | 74  | 76    | 80  | V     |  |

| V <sub>CS</sub>                      | CS voltage                                                              | $V_{IN} = 15V$ and 75V, $V_{VL} = 1.75V$                                                                                                | 244 | 250   | 256 | mV    |  |

| $\Delta V_{LR1}$                     |                                                                         | V <sub>VL</sub> = 1.57V to 1.75V                                                                                                        |     | -0.28 |     |       |  |

| $\Delta V_{LR2}$                     | CS voltage line regulation vs. V <sub>VL</sub> <sup>(1)</sup>           | V <sub>VL</sub> = 1.75V to 2.10V                                                                                                        |     | -0.24 |     | mV/mV |  |

| ΔV <sub>LR3</sub>                    |                                                                         | V <sub>VL</sub> = 2.10V to 2.28V                                                                                                        |     | -0.3  |     |       |  |

| V <sub>REF1</sub> /V <sub>REF0</sub> | Reference voltge ratio                                                  |                                                                                                                                         | 86  | 90    | 94  | %     |  |

| V <sub>CS,CLAMP</sub>                | Maximum V <sub>CS, CLAMP</sub>                                          | VL under voltage protection,<br>V <sub>VL</sub> < 1.45V                                                                                 | 310 | 323   | 336 | mV    |  |

| V <sub>GATE</sub>                    | Gate voltage                                                            | Gate to SOURCE                                                                                                                          |     | 5.4   |     | V     |  |

| I <sub>SOURCE</sub>                  | GATE source current <sup>(2)</sup>                                      | V <sub>GATE</sub> to V <sub>SOURCE</sub> = 3V                                                                                           |     | 30    |     | μΑ    |  |

| I <sub>SINK</sub>                    | GATE sink current <sup>(2)</sup>                                        | V <sub>GATE</sub> to V <sub>SOURCE</sub> = 3V                                                                                           |     | 500   |     | μΑ    |  |

| T <sub>TP</sub>                      | Thermal protection trip temperature <sup>(2)</sup>                      | When T <sub>J</sub> is higher than T <sub>TP</sub> , V <sub>CS</sub> decreases linearly                                                 | 135 | 145   |     | °C    |  |

| ΔV <sub>CS</sub> /ΔT <sub>J</sub>    | Thermal protection mode V <sub>CS</sub> decreasing slope <sup>(2)</sup> | $T_{J} > T_{TP}$                                                                                                                        |     | -1.1  |     | %/°C  |  |

#### NOTES:

1. The CS voltage line regulation is defined as:

$$\begin{split} \Delta V_{LR1} &= \frac{\Delta V_{CS}}{\Delta V_{VL}} = \frac{V_{CS(V_{VL} = 1.75V)} - V_{CS(V_{VL} = 1.57V)}}{1.75V - 1.57V} \\ \Delta V_{LR2} &= \frac{\Delta V_{CS}}{\Delta V_{VL}} = \frac{V_{CS(V_{VL} = 2.10V)} - V_{CS(V_{VL} = 1.75V)}}{2.10V - 1.75V} \\ \Delta V_{LR3} &= \frac{\Delta V_{CS}}{\Delta V_{VL}} = \frac{V_{CS(V_{VL} = 2.28V)} - V_{CS(V_{VL} = 2.10V)}}{2.28V - 1.10V} \end{split}$$

2. Guaranteed by design, not by production test.

3/11

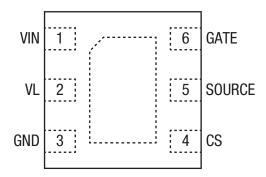

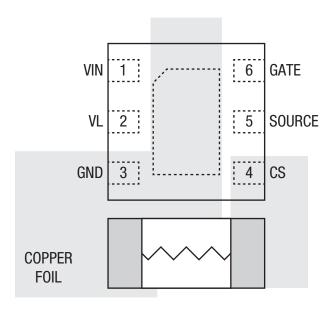

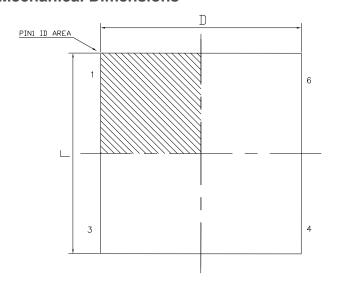

# Pin Configuration

TDFN-6 2mm x 2mm

# **Pin Functions**

| Pin Number Pin Name |      | Description                                                                                                                                                                                                                                                              |

|---------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 VIN               |      | Power supply pin.                                                                                                                                                                                                                                                        |

| 2 VL                |      | Line regulation sense pin. The reference voltage is adjusted according to V <sub>L</sub> to provide the line regulation compensation and to provide overvoltage protection.                                                                                              |

| 3                   | GND  | Ground pin.                                                                                                                                                                                                                                                              |

| 4 CS<br>5 SOURCE    |      | Current sense pin. Connect a sense resistor, $R_{CS}$ , between this pin and the GND pin. The peak current is set by: $I_{OUT} = \frac{V_{CS}}{R_{CS}}$                                                                                                                  |

|                     |      | External HV NMOS source pin. The VF of the LED segment connected between the SOURCE pin and the CS pin should not be higher than 70V.                                                                                                                                    |

| 6                   | GATE | External HV NMOS gate driving pin, limited to 5.5V maximum.                                                                                                                                                                                                              |

| EP                  |      | Exposed thermal pad (EP) of the chip. Use this pad to enhance the power dissipation capability. The thermal conductivity will be improved if a copper foil on PCB is soldered with the thermal pad. It is recommended to connect the exposed thermal pad to the GND pin. |

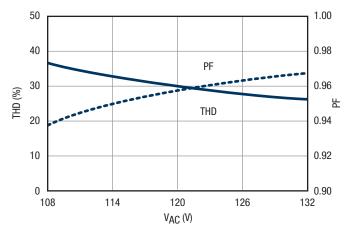

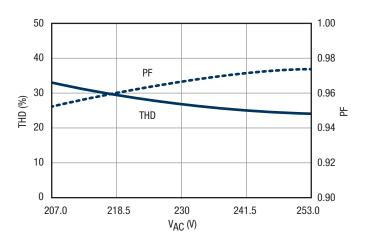

#### **Typical Performance Characteristics**

For a typical 2-step driving scheme using a single XR46073, the electrical performance is good enough to meet applications where the Power Factor (PF) is higher than 0.92 and the Total Harmonic Distortion (THD) is around 30%. If higher PF or lower THD is required, one more XR46083 or XR46084 can be added to the circuit to make a 3-step driving scheme, as shown below. The 3-step system can provide better electrical performance with PF greater than 0.96 and THD approximately 20%.

$I_{LED}$  $V_{AC}$ LED1 BDS S A LED2  $R_{A1}$ R<sub>IN</sub> } XR46083/ XR46084 R1 Q1 (NMOS)  $R_{A2} \\$  $\widehat{M}_{X}L^{\text{GATE}}$ XR46000 XR46073 SOURCE LED3 GND CS  $\mathsf{C}_{\mathsf{LR}}$  $R_B$ R2

Figure 3. Two-Step (PF > 0.92 and THD =  $\sim 30\%$ )

Figure 4. Three-Step (PF > 0.96 and THD =  $\sim 20\%$ )

#### **Functional Block Diagram**

Figure 5. Functional Block Diagram

# **Applications Information**

Figure 6. PF and THD, 120V<sub>AC</sub>

Figure 7. PF and THD,  $230V_{AC}$

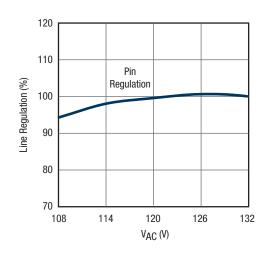

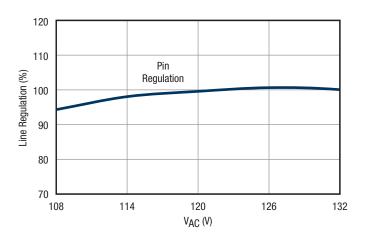

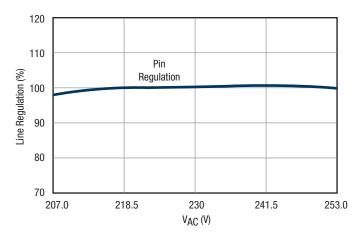

Figure 8. Line Regulation, 120V<sub>AC</sub>

Figure 9. Line Regulation, 230V<sub>AC</sub>

#### **Applications Information (Continued)**

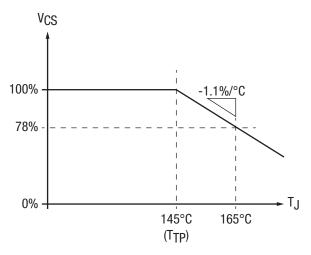

#### **Linear Type Thermal Protection**

When the junction temperature  $T_J$  rises to the Thermal Protection Trip Temperature  $T_{TP}$  (typically 145°C), the current sense voltage  $V_{CS}$  starts to decrease linearly at a slope of -1.1%/°C. The LED driving current decreases proportionally with the  $V_{CS}$  voltage. The system will function normally during the thermal protection mode with the lower driving current but the power dissipation of the XR46073 chip will decrease until thermal equilibrium is reached.

Figure 10. Linear Type Thermal Protection

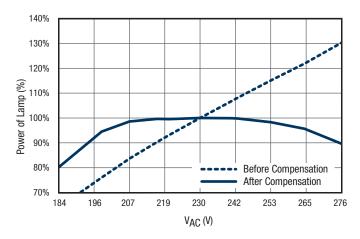

#### Line Regulation Compensation

When there is variation in line voltage ( $V_{AC}$ ), the power of the lamp will also change if the LED driving current is kept unchanged. In order to provide good line regulation when  $V_{AC}$  varies within a  $\pm 20\%$  range, the average of the rectified  $V_{AC}$  is sensed by the VL pin to provide compensation in order to attempt to keep the power of lamp at the same level.

The LED driving current is adjusted as the voltage level  $V_{VL}$  at VL pin is changed. Based on the design, the LED driving current will be lower when  $V_{AC}$  is higher than the nominal value, and the LED driving current will be higher when  $V_{AC}$  is lower than the nominal value. The system power can then be maintained at approximately the same level. During power on, the driving current may be slightly higher for a few cycles until steady state is reached.

With the compensation function, the XR46073 provides excellent power line regulation over a  $\pm 20\%$  V<sub>AC</sub> variation range, as shown below.

Figure 11. Power Line Regulation, 230V<sub>AC</sub> ±20%

#### **Applications Information (Continued)**

#### **Layout Suggestion**

The exposed thermal pad under the chip is used to enhance the power dissipation capability of the DFN package. The thermal conductivity will be improved if a copper foil on the PCB that is soldered to the thermal pad can be as large as possible. It is strongly recommended to connect the GND pin to the exposed thermal pad.

The external HV NMOS is also recommended to be placed close to the XR46073. The pull-high resistors for the VIN pin and the VL pin should be placed close to the chip. In addition, the current sense resistor connected between the CS pin and GND pin should be placed as close as possible to the CS pin and GND pin, as shown below.

Figure 12. Positioning Illustration

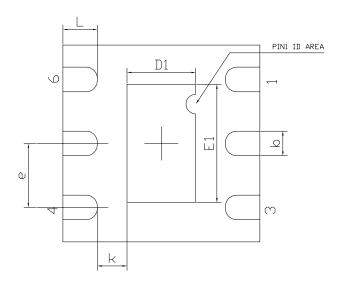

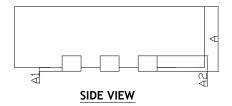

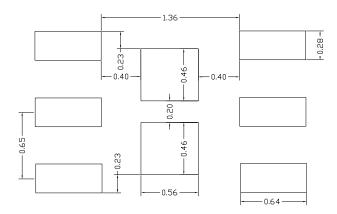

# **Mechanical Dimensions**

**TOP VIEW**

**BOTTOM VIEW**

| DIM | MIN       | NOM                  | MAX   |

|-----|-----------|----------------------|-------|

| Α   | 0.700     | 0.750                | 0.800 |

| A1  | 0.000     | ı                    | 0.050 |

| A2  | (         | 0.203Re <sup>-</sup> | f     |

| b   | 0.200     | 0.250                | 0.300 |

| D   | 2.00 BSC  |                      |       |

| Е   | 2.00 BSC  |                      |       |

| е   | 0.650 BSC |                      |       |

| D1  | 0.600     | 0.700                | 0.800 |

| E1  | 1.100     | 1.200                | 1.300 |

| L   | 0.274     | 0.350                | 0.426 |

| K   | 0.200     | _                    | _     |

| N   | 6         |                      |       |

# TERMINAL DETAILS

- ALL DIMENSIONS ARE IN MILLIMETERS, ANGLES ARE IN DEGREES.

- DIMENSIONS AND TOLERANCE PER JEDEC MO-229.

Drawing No.: POD-00000072

Revision: B

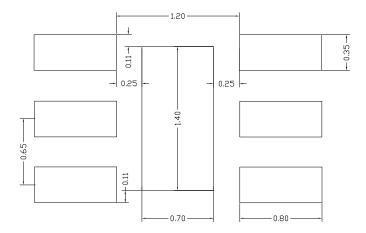

# **Recommended Land Pattern and Stencil**

#### TYPICAL RECOMMENDED LAND PATTERN

TYPICAL RECOMMENDED STENCIL

Drawing No.: POD-00000072

Revision: B

# Ordering Information(1)

| Part Number  | Operating Temperature Range | Lead-Free          | Package   | Packaging Method |

|--------------|-----------------------------|--------------------|-----------|------------------|

| XR46073IHBTR | -40°C to 85°C               | Yes <sup>(2)</sup> | TDFN6 2x2 | Tape and reel    |

#### NOTE:

- 1. Refer to <a href="www.exar.com/XR46073">www.exar.com/XR46073</a> for most up-to-date Ordering Information.

- 2. Visit www.exar.com for additional information on Environmental Rating.

#### **Revision History**

| Revision | Date      | Description                                                |

|----------|-----------|------------------------------------------------------------|

| 1A       | June 2015 | Initial release.                                           |

| 1B       | Nov 2016  | Update Package Description and Ordering Information table. |

| 1C       | Aug 2018  | Update to MaxLinear logo. Update format.                   |

Corporate Headquarters: 5966 La Place Court Suite 100 Carlsbad, CA 92008 Tel.:+1 (760) 692-0711 Fax: +1 (760) 444-8598 www.maxlinear.com

High Performance Analog: 1060 Rincon Circle San Jose, CA 95131 Tel.: +1 (669) 265-6100 Fax: +1 (669) 265-6101 www.exar.com

The content of this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by MaxLinear, Inc.. MaxLinear, Inc. assumes no responsibility or liability for any errors or inaccuracies that may appear in the informational content contained in this guide. Complying with all applicable copyright laws is the responsibility of the user. Without limiting the rights under copyright, no part of this document may be reproduced into, stored in, or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), or for any purpose, without the express written permission of MaxLinear, Inc.

Maxlinear, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless MaxLinear, Inc. receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of MaxLinear, Inc. is adequately protected under the circumstances.

MaxLinear, Inc. may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering subject matter in this document. Except as expressly provided in any written license agreement from MaxLinear, Inc., the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

Company and product names may be registered trademarks or trademarks of the respective owners with which they are associated.

© 2015 - 2018 MaxLinear, Inc. All rights reserved