# SYNCHRONOUS BOOST CONVERTER

# With 7A Switch, Can Output 5V 3.4A with Li-Battery Input

## **GENERAL DESCRIPTION**

XR6504/B is a high efficiency synchronous boost regulator that converts down to 2.5V input and up to 5.5V output voltage. It adopts NMOS for the main switch and PMOS for the synchronous switch. It can disconnect the output from input during the shutdown mode..

It integrates 6A power MOSFET and can output 5V 3.4A with Li-Battery input.

#### **FEATURES**

- 2.5V Minimum input voltage

- Adjustable output voltage from 3V to 5.

- 8A peak current limit

- Input under voltage lockout

- 600Khz fixed Switching Frequency

- Load disconnect during shutdown

- Integrated soft-start

- Output over voltage protection

- 20mohm Power MOSFET

- Thermal Shutdown

- QFN3\*3-15FC Package

## **APPLICATIONS**

Handheld Devices

Power Bank

All Single Cell Li or Dual Cell Battery Operated Products

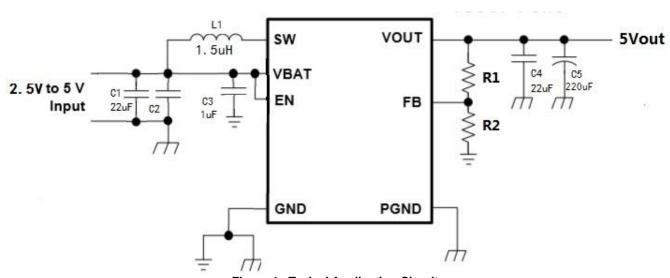

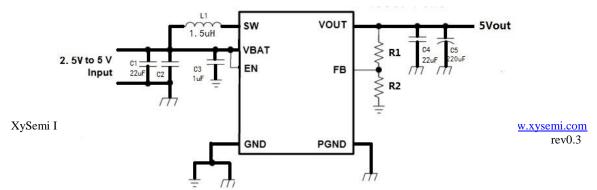

Figure 1. Typical Application Circuit

XySemi Inc - 1 - <u>www.xysemi.com</u> rev0.2

# **ORDERING INFORMATION**

| Ī | PART<br>NUMBER    | TEMP RANGE    | SWICHING<br>FREQUENCY | OUTPUT<br>VOLTAGE (V) | ILIM (A) | PACKAGE     | MARK     | PINS |

|---|-------------------|---------------|-----------------------|-----------------------|----------|-------------|----------|------|

|   | XR6504<br>XR6504B | -40°C to 85°C | 600KHZ                | ADJ                   | >8       | QFN3*3-15FC | XR6504YW | 15   |

Note: "YW" is manufacture date code, "Y" means the year, "W" means the week .

XR6504、XR6504B has the same top marks, but different in product name pasted on packages.

XR6504B has Short circuit protection and Non-Backflow function, and XR6504 hasn't .

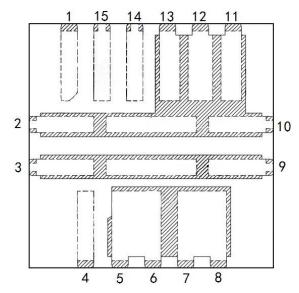

## **PIN CONFIGURATION**

Figure 2. PIN Configuration (TOP View)

# **PIN DESCRIPTION**

| PIN<br>NUMBER     | PIN<br>NAME | PIN DESCRIPTION                                                                    |

|-------------------|-------------|------------------------------------------------------------------------------------|

| 1                 | EN          | Shutdown control input., Connect this pin to logic high level to enable the device |

| 2,10,11,<br>12,13 | Vout        | DC-DC Boost output                                                                 |

| 3,9               | SW          | Switch pin , Connect an inductor between IN pin and LX pin.                        |

| 4                 | VBAT        | VDD Power Supply,need one 1uF MLCC close to VBAT pin and AGND                      |

| 5,6,7,8           | PGND        | Power ground                                                                       |

| 14                | FB          | Feedback pin                                                                       |

| 15                | AGND        | Analog ground                                                                      |

# **ABSOLUTE MAXIMUM RATINGS**

(Note: Do not exceed these limits to prevent damage to the device. Exposure to absolute maximum rating conditions for long periods may affect device reliability.)

| PARAMETER                            | VALUE      | UNIT |

|--------------------------------------|------------|------|

| EN Voltage                           | Vout+0.3V  | V    |

| Other Pins                           | 6V         | V    |

| Operating Ambient Temperature        | -40 to 85  | °C   |

| Maximum Junction Temperature         | 150        | °C   |

| Storage Temperature                  | -55 to 150 | °C   |

| Lead Temperature (Soldering, 10 sec) | 300        | °C   |

# **ELECTRICAL CHARACTERISTICS**

(V<sub>IN</sub> = 3.6V, T<sub>A</sub>= 25°C unless otherwise specified)

| PARAMETER                                            | SYMBOL              | TEST CONDITIONS                                    | MIN  | TYP | MAX  | UNIT |

|------------------------------------------------------|---------------------|----------------------------------------------------|------|-----|------|------|

| Input Voltage Range                                  | $V_{IN}$            |                                                    | 2.5  |     | 5.5  | V    |

| Boost output voltage range                           | Vout                |                                                    | 2.5  |     | 5.5  | V    |

| UVLO Threshold                                       | $V_{\text{UVLO}}$   | V <sub>HYSTERESIS</sub> =100mV                     |      | 2.2 |      | V    |

| Operating Supply Current                             |                     | $V_{FB}$ =1.3V , EN=Vin=3.6V, $I_{Load}$ =0        |      | 85  |      |      |

| Shutdown Supply Current                              | I <sub>SUPPLY</sub> | V <sub>EN</sub> =0V, V <sub>IN</sub> =3.6V         |      |     | 1    | μΑ   |

| Regulated Feedback<br>Voltage                        | $V_{FB}$            |                                                    | 1.18 | 1.2 | 1.22 | V    |

| Peak inductor Current limit (N-MOSFET current limit) | llim                |                                                    | 8    |     |      | А    |

| Oscillator Frequency                                 | Fosc                |                                                    |      | 0.6 |      | MHz  |

| Rds(ON) of N-channel FET                             |                     | I <sub>SW</sub> =-100mA                            |      | 20  |      | mOhm |

| *Enable Threshold                                    |                     | $V_{IN} = 2.3V \text{ to } 5.5V$                   | 0.3  | 1   | 1.5  | V    |

| Enable Leakage Current                               |                     |                                                    | -0.1 |     | 0.1  | μΑ   |

| SW Leakage Current                                   |                     | $V_{EN} = 0V$ , $V_{SW} = 0V$ or 5V, $V_{IN} = 5V$ |      |     | 1    | uA   |

| Output over voltage protection                       |                     |                                                    |      | 5.5 |      | V    |

| Minimum on time                                      |                     |                                                    |      | 100 |      | ns   |

| Minimum off time                                     |                     |                                                    |      | 100 |      | ns   |

# XR6504/B

| Soft Start Time Tss 1.5 ms | Soft Start Time | Tss |  |  | 1 5 |  | ms |

|----------------------------|-----------------|-----|--|--|-----|--|----|

|----------------------------|-----------------|-----|--|--|-----|--|----|

\*For XR6504 : Please set EN voltage \( \text{Vbat voltage, the best EN voltage from MCU is 2V} \) For XR6504B not such limit as above

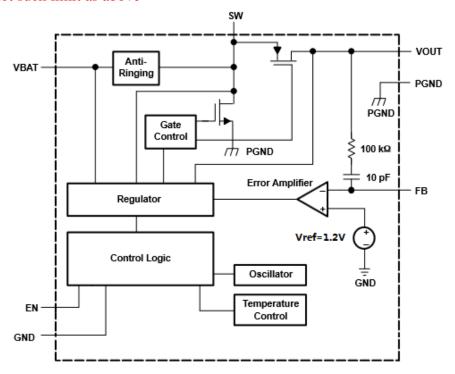

Figure 3. Functional Block Diagram

#### **CONTROLLER CIRCUIT**

The controller circuit of the device is based on a fixed frequency multiple feedforward controller topology. Input voltage, output voltage, and voltage drop on the NMOS switch are monitored and forwarded to the regulator. So changes in the operating conditions of the converter directly affect the duty cycle and must not take the indirect and slow way through the control loop and the error amplifier. The control loop, determined by the error amplifier, only has to handle small signal errors. The input for it is the feedback voltage on the FB pin, the voltage on the internal resistor divider. It is compared with the internal reference voltage to generate an accurate and stable output voltage.

The peak current of the NMOS switch is also sensed to limit the maximum current flowing through the switch and the inductor. The typical peak current limit is set to exceed 6A. An internal temperature sensor prevents the device from getting overheated in case of excessive power dissipation.

### SYNCHRONOUS RECTIFIER

The device integrates an N-channel and a P-channel MOSFET transistor to realize a synchronous rectifier. Because the commonly used discrete Schottky rectifier is replaced with a low RDS(ON) PMOS switch, the power conversion efficiency reaches 96%. To avoid ground shift due to the high currents in the NMOS switch, two separate ground pins are used. The reference for all control functions is the GND pin. The source of the NMOS switch is connected to PGND. Both grounds must be connected on the PCB at only one point close to the GND pin. A special circuit is applied to disconnect the load from the input during shutdown of the converter. In conventional synchronous rectifier circuits, the backgate diode of the high-side PMOS is forward biased in shutdown and allows current flowing from the battery to the output. This device however uses a special circuit which takes the cathode of the backgate diode of the high-side PMOS and disconnects it from the source when the regulator is not enabled (EN = low).

The benefit of this feature for the system design engineer is that the battery is not depleted during shutdown of the converter. No additional components have to be added to the design to make sure that the battery is disconnected from the output of the converter.

#### OUTPUT VOLTAGE PROGRAMMING

In the adjustable version, the output voltage is set by a resistive divider according to the following equation:

$$R_1 = R_2 \times \left(\frac{V_{OUT}}{1.2} - 1\right)$$

Typically choose R2=100K and determine R1 from the following equation.

#### INDUCTOR SELECTION

In normal operation, the inductor maintains continuous current to the output. The inductor current has a ripple that is dependent on the inductance value. The high inductance reduces the ripple current. For power bank application, 1uH~2.2uH is suitable.

#### SELECTED INDUCTOR BY ACTUAL APPLICATION:

| Manufact<br>urer | Part<br>Number | Inducta<br>nce(uH) | DRC<br>max<br>(Ohms<br>) | Dimensions<br>L*W*H(mm3) |

|------------------|----------------|--------------------|--------------------------|--------------------------|

| TDK              | SPM653<br>0T   | 1.0                | 0.007                    | 7. 1*6. 5*3              |

|                  | 01             | 1.5                | 0.01                     |                          |

|                  |                | 2.2                | 0.017                    |                          |

| Manufact<br>urer | Part<br>Number  | Inducta<br>nce(uH) | DRC<br>max<br>(Ohms<br>) | Dimensions<br>L*W*H(mm3) |

|------------------|-----------------|--------------------|--------------------------|--------------------------|

|                  |                 | 3.3                | 0.027                    |                          |

| WURTH            | 7443734<br>6010 | 1.0                | 0.008                    | 7.3*6.6*2.8              |

**Table 1. Recommend Surface Mount Inductors**

#### INPUT CAPACITOR

One or Two 22µF MLCC capacitor is recommended to improve transient behavior of the regulator and EMI behavior of the total power supply circuit. Two 22µF MLCC capacitor is recommended. One 1uF MLCC capacitor is needed close to Vbat<sub>o</sub>

#### **OUTPUT CAPACITOR**

For 5V 3A load, one 22uF MLCC+220uF E-cap is minim and low ESR tantalum capacitor is recommended

#### LAY OUT CONSIDERATIONS

- 1 : The input capacitor, output capacitor, and the inductor should be placed as close as possible to the IC.

- 2 : Use a common ground node for power ground and a different one for control ground to minimize the effects of ground noise.

- 3: The feedback divider should be placed as close as possible to the control ground pin of the IC. The components R1 and R2, and the trace connecting to the FB pin must NOT be adjacent to the SW net on the PCB layout to avoid the noise problem

- 4 : Please make sure that the big current circuits are board and short to reduce the circuit Rdson

- 5: The big current path must be broad line in PCB just as below . Ibat may be big current at startup so it also need broad and short line. It is desirable to maximize the PCB copper area connecting to GND/EPAD pin to achieve the best thermal and noise performance. If the board space allowed, a ground plane is highly desirable.

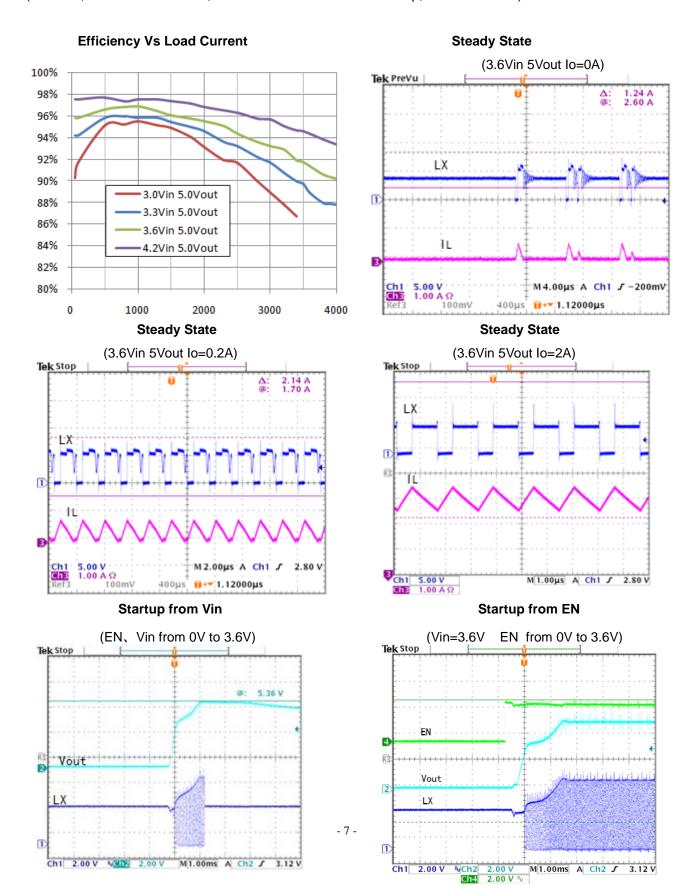

# **EFFICIENCY FIGURE**

(L=2.2uH, CIN=22uF MLCC\*2, COUT=22uF MLCC+220uF E-Cap,if not mentioned)

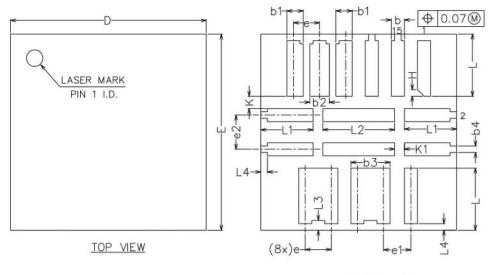

# PACKAGE OUTLINE

#### QFN3X3-15FC PACKAGE OUTLINE AND DIMENSIONS

BOTTOM VIEW

| SYMBOL | MIN   | NOM     | MAX   |

|--------|-------|---------|-------|

| A      | 0.50  | -       | 0.60  |

| A1     | 0.00  | 0.02    | 0.05  |

| A3     |       | 0.10REF |       |

| b      | 0.15  | 0.20    | 0.25  |

| b1     | 0.20  | 0.25    | 0.30  |

| b2     | 0.25  | 0.30    | 0.35  |

| b3     | 0.55  | 0.60    | 0.65  |

| b4     | 0.05  | 0.10    | 0.15  |

| D      | 2.90  | 3.00    | 3.10  |

| E      | 2.90  | 3.00    | 3.10  |

| e      | 0.30  | 0.40    | 0.50  |

| e1     | 0.32  | 0.42    | 0.52  |

| e2     | 0.423 | 0.523   | 0.623 |

| Н      |       | 0.10REF |       |

| K      | 0.089 | 0.189   | 0.289 |

| K1     | 0.05  | 0.15    | 0.25  |

| L      | 0.90  | 0.95    | 1.00  |

| L1     | 0.75  | 0.80    | 0.85  |

| L2     | 1.00  | 1.10    | 1.20  |

| L3     | 0.10  | 0.15    | 0.20  |

| L4     | 0.05  | 0.10    | 0.15  |

COMMON DIMENSIONS

# O.08 SIDE VIEW

NOTES:

ALL DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSION.

#### **RECOMMENDED LAND PATTERN**

In order to increase the driver current capability of XR6504/B and improve the temperature of package, Please ensure Vout / PGND pad enough copper metal to release energy.

XySemi Inc

a=0. 1mm f=0. 3mm j=0. 4mm p=1. 2mm b=0. 15mn g=0. 323m m=0. 6mm s=1. 3mm

b=0. 15mm c=0. 2mm g=0. 323mm h=0. 339mm m=0. 6mm n=0. 8mm

t=3mm

e=0. 25mm i=0. 338mm o=1. 15mm