XRT79L73

3 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC

#### REV. P1.0.0

#### JUNE 2004

### HARDWARE MANUAL

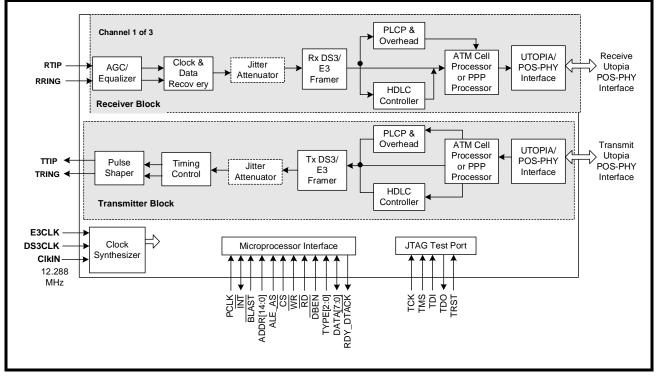

The XRT79L73 is a three channel, ATM UNI/PPP Physical Layer Processor with integrated DS3/E3 framing controllers and Line Interface Units with Jitter Attenuators that are designed to support ATM direct mapping and cell delineation as well as PPP mapping and Frame processing. For ATM UNI applications, this device provides the ATM Physical Layer (Physical Medium Dependent and Transmission Convergence sub-layers) interface for the public and private networks at DS3/E3 rates. For Clear-Channel Framer applications, this device supports the transmission and reception of "user data" via the DS3/E3 payload.

The XRT79L73 includes DS3/E3 Framing, Line Interface Unit with Jitter Attenuator that supports mapping of ATM or HDLC framed data. A flexible parallel microprocessor interface is provided for configuration and control. Industry standard UTOPIA II and POS-PHY interface are also provided.

#### **GENERAL FEATURES:**

- Integrated T3/E3 Line Interface Unit

- Integrated Jitter Attenuator that can be selected either in Receive or Transmit path

- Flexible integrated Clock Multiplier that takes single frequency clock and generates either DS3 or E3 frequency.

- 8/16 bit UTOPIA Level I and II and PPP Multi-PHY Interface operating at 25, 33 or 50 MHz.

- HDLC Controller that provides the mapping/ extraction of either bit or byte mapped encapsulated packet from DS3/E3 Frame.

- Contains on-chip 16 cell FIFO (configurable in depths of 4, 8, 12 or 16 cells), in both the Transmit (TxFIFO) and Receive Directions (RxFIFO)

- Contains on-chip 54 byte Transmit and Receive OAM Cell Buffer for transmission, reception and processing of OAM Cells

- Supports ATM cell or PPP Packet Mapping

- Supports M13 and C-Bit Parity Framing Formats

- Supports DS3/E3 Clear-Channel Framing.

- Includes PRBS Generator and Receiver

- Supports Line, Cell, and PLCP Loop-backs

- Interfaces to 8 Bit wide Intel, Motorola or PowerPC

- Low power 3.3V, 5V Input Tolerant, CMOS

- Available in 456 Lead PBGA Package

- JTAG Interface

#### LINE INTERFACE UNIT

- On chip Clock and Data Recovery circuit for high input jitter tolerance

- Meets E3/DS3 Jitter Tolerance Requirements

- Detects and Clears LOS as per G.775.

- Receiver Monitor mode handles up to 20 dB flat loss with 6 dB cable attenuation

- Compliant with jitter transfer template outlined in ITU G.751, G.752, G.755 and GR-499-CORE,1995 standards

- Meets ETSI TBR 24 and GR-499 Jitter Transfer Requirements

- On chip B3ZS/HDB3 encoder and decoder that can be either enabled or disabled

- On-chip clock synthesizer provides the appropriate rate clock from a single 12.288 MHz Clock

- On chip advanced crystal-less Jitter Attenuator

- Jitter Attenuator can be selected in Receive or Transmit paths

- 16 or 32 bits selectable FIFO size

- Meets the Jitter and Wander specifications described in T1.105.03b,ETSI TBR-24, Bellcore GR-253 and GR-499 standards

- Jitter Attenuator can be disabled

- Maximum power consumption 3.1W

#### DS3/E3 FRAMER

- DS3 framer supports both M13 and C-bit parity.

- DS3 framer meets ANSI T1.107 and T1.404 standards.

- Detects OOF,LOF,AIS,RDI/FERF alarms.

- Generation and Insertion of FEBE on received parity errors supported.

- Automatic insertion of RDI/FERF on alarm status.

- E3 framer meets G.832,G.751 standards.

- Framers can be bypassed.

#### ATM/PPP PROTOCOL PROCESSOR

#### TRANSMIT CELL PROCESSING

- Extracts ATM cells

- Supports ATM cell payload scrambling

- Maps ATM cells into E3 or DS3 frame

- PLCP frame and mapping of ATM cell streams

#### RECEIVE CELL PROCESSING

## PRELIMINARY

3 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC

- Extraction of ATM cells from PLCP frame or directly from E3 or DS3 frame

- Termination of PLCP frame

- Supports payload cell de-scrambling

### TRANSMIT PACKET PROCESSING

- Inserts PPP packets into data stream

- Maps HDLC data stream directly into DS3 or E3 frame

- Extracts in-band messaging packets

- Supports CRC-16/32, HDLC flag and Idle sequence generation

### **RECEIVE PACKET PROCESSING**

- Extracts HDLC data stream from DS3 or E3 frame

- Inserts in-band messaging packets

- Detects and removes HDLC flags

### UTOPIA/ SYSTEM INTERFACE

### FIGURE 1. BLOCK DIAGRAM OF THE XRT79L73

- 8/16 bit UTOPIA Level I and II and PPP Multi-PHY Interface operating at 25, 33 or 50 MHz.

- Compliant with ATM Forum UTOPIA II interface

- Programmable FIFO size for both Transmit and Receive direction

- Compliant to POS-PHY Level 2 interface

#### SERIAL INTERFACE

- Serial clock and data interface for accessing DS3/ E3 framer

- Serial clock and data interface for accessing cell/ packet processor

### APPLICATIONS

- Digital Access and Cross Connect Systems

- 3G Base Stations

- DSLAMs

- Digital, ATM, WAN and LAN Switches

### PRODUCT ORDERING INFORMATION

| PRODUCT NUMBER | PACKAGE TYPE  | OPERATING TEMPERATURE RANGE |

|----------------|---------------|-----------------------------|

| XRT79L73IB     | 456 Lead PBGA | -40°C to +85°C              |

3 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC

## TABLE OF CONTENTS

| HARDWARE MANUAL                                                                                                                 | 1        |

|---------------------------------------------------------------------------------------------------------------------------------|----------|

| GENERAL FEATURES:                                                                                                               | 1        |

| Line Interface Unit                                                                                                             |          |

| DS3/E3 Framer                                                                                                                   |          |

| ATM/PPP PROTOCOL PROCESSOR                                                                                                      |          |

| Transmit Cell Processing                                                                                                        |          |

| Receive Cell Processing                                                                                                         |          |

| Transmit Packet Processing                                                                                                      |          |

| Receive Packet Processing                                                                                                       | 2        |

| Utopia/ System Interface                                                                                                        | 2        |

| Serial Interface                                                                                                                | 2        |

| APPLICATIONS                                                                                                                    |          |

| FIGURE 1. BLOCK DIAGRAM OF THE XRT79L73                                                                                         | 2        |

| Product Ordering Information                                                                                                    | 2        |

| TABLE OF CONTENTS                                                                                                               | A        |

| Pin Descriptions                                                                                                                | 4        |

| MICROPROCESSOR INTERFACE                                                                                                        | 4        |

| Test and Diagnostic                                                                                                             |          |

| General Purpose Input and Output Pins                                                                                           |          |

| TRANSMIT SYSTEM SIDE INTERFACE PINS                                                                                             |          |

| RECEIVE SYSTEM SIDE INTERFACE PINS                                                                                              |          |

| TRANSMIT LINE SIDE SIGNALS                                                                                                      |          |

|                                                                                                                                 |          |

| RECEIVE LINE SIDE SIGNALS                                                                                                       |          |

| ELECTRICAL CHARACTERISTICS                                                                                                      |          |

| AC ELECTRICAL CHARACTERISTIC INFORMATION                                                                                        | 46       |

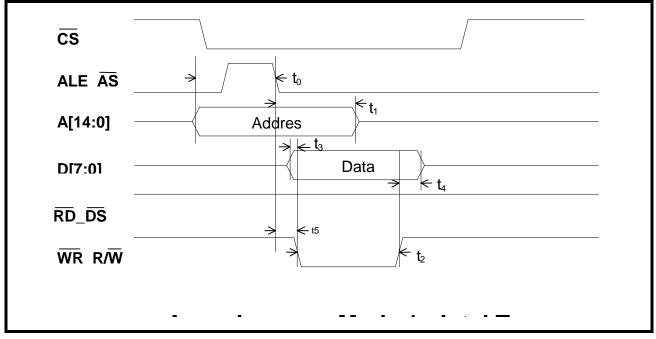

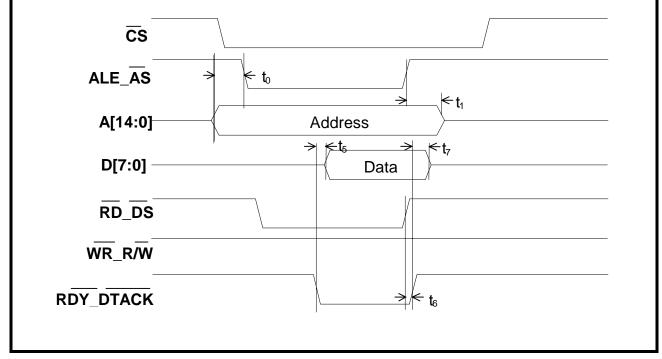

| MICROPROCESSOR INTERFACE TIMING FOR REVISION A SILICON                                                                          | 46       |

| MICROPROCESSOR INTERFACE TIMING - ASYNCHRONOUS INTEL MODE                                                                       |          |

| TABLE 1: DC ELECTRICAL CHARACTERISTICSS                                                                                         |          |

| Applies to all TTL-Level Input and CMOS Level Output pins - Ambient Temperature = 25°C                                          |          |

| Figure 2. Asynchronus Mode 1 - Intel type Programmed I/O Timing (Write Cycle)                                                   |          |

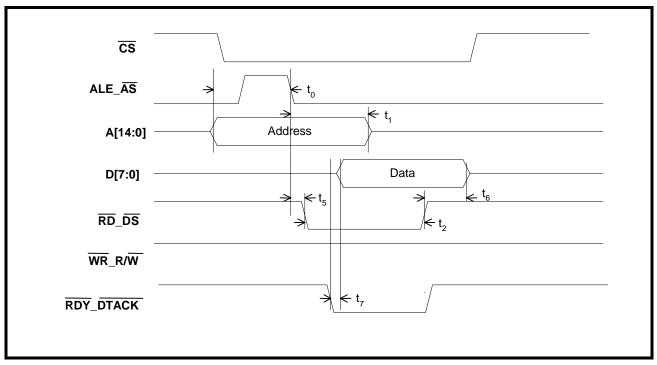

| FIGURE 3. ASYNCHRONUS MODE 1 - INTEL TYPE PROGRAMMED I/O TIMING (READ CYCLE)                                                    | 47       |

| TABLE 2: TIMING INFORMATION FOR THE MICROPROCESSOR INTERFACE, WHEN CONFIGURED TO OPERATE IN THE INTEL ASYNC         MODE        | CHRONOUS |

| MICROPROCESSOR INTERFACE TIMING - ASYNCHRONOUS MOTOROLA (68)                                                                    |          |

| •                                                                                                                               | -        |

| MODE                                                                                                                            | -        |

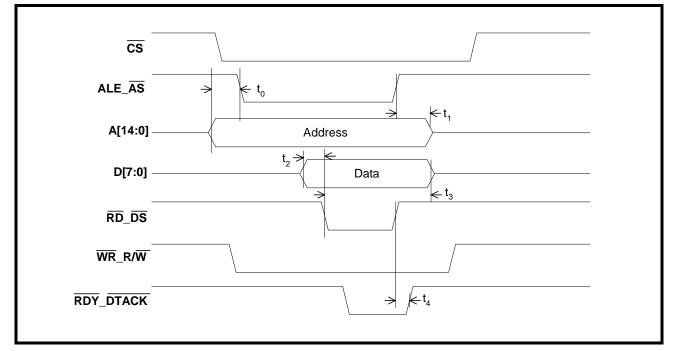

| FIGURE 4. ASYNCHRONUS MODE 2 - MOTOROLA 68K PROGRAMMED I/O TIMING (WRITE CYCLE)                                                 |          |

| Figure 5. Asynchronus Mode 2 - Motorola 68 Programmed I/O Timing (Read Cycle)                                                   |          |

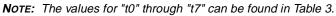

| MICROPROCESSOR INTERFACE TIMING - POWER PC 403 SYNCHRONOUS M                                                                    |          |

| TABLE 3: TIMING INFORMATION FOR THE MICROPROCESSOR INTERFACE WHEN CONFIGURED TO OPERATE IN THE MOTOROLA (         CHRONOUS MODE | ,        |

| Figure 6. Synchronous Mode 3 - IBM PowerPC 403 Interface timing (Write Cycle)                                                   | -        |

| FIGURE 7. SYNCHRONOUS MODE 3 - IBM POWERPC 403 INTERFACE TIMING (READ CYCLE)                                                    |          |

| TABLE 4: TIMING INFORMATION FOR THE MICROPROCESSOR INTERFACE, WHEN CONFIGURED TO OPERATE IN THE IBM POWER                       |          |

| Моде                                                                                                                            | 50       |

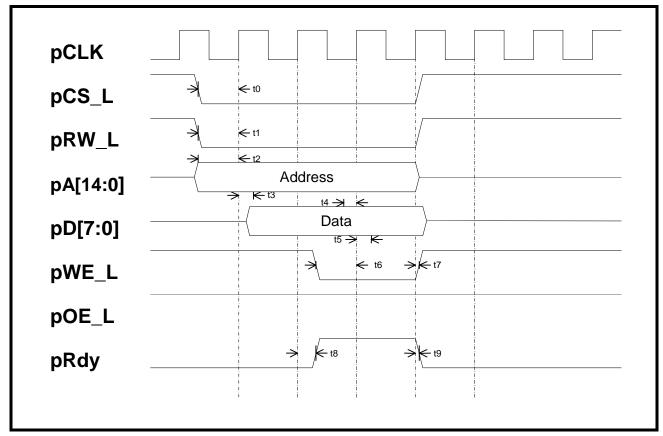

| DS3/E3 LIU INTERFACE - LINE SIDE ELECTRICAL CHARACTERISTIC INFORM                                                               | ATION    |

| 51                                                                                                                              |          |

| E3 LINE SIDE PARAMETERS                                                                                                         | 51       |

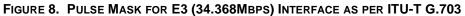

| Figure 8. Pulse Mask for E3 (34.368Mbps) Interface as per ITU-T G.703                                                           |          |

| TABLE 5: E3 TRANSMITTER LINE SIDE OUTPUT AND RECEIVER LINE SIDE INPUT SPECIFICATIONS                                            |          |

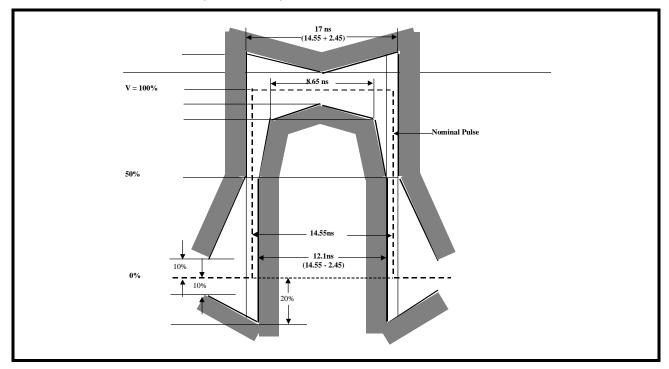

| DS3 Line Side Parameters.                                                                                                       |          |

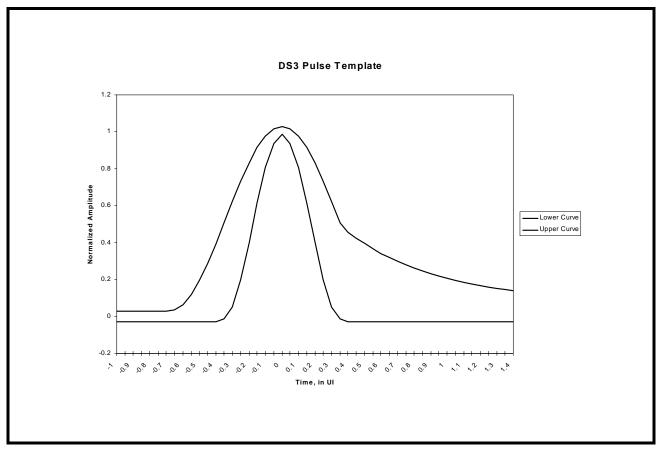

| FIGURE 0. BELL CODE CD 400 CODE DULLES TEMPLATE DECUMPENENTS FOR DS2 ADDUCATIONS                                                | 52       |

| FIGURE 9. BELLCORE GR-499-CORE PULSE TEMPLATE REQUIREMENTS FOR DS3 APPLICATIONS                |    |

|------------------------------------------------------------------------------------------------|----|

| TABLE 6: DS3 PULSE MASK EQUATIONS                                                              |    |

| TABLE 7: DS3 TRANSMITTER LINE SIDE OUTPUT AND RECEIVER LINE SIDE INPUT SPECIFICATIONS (GR-499) |    |

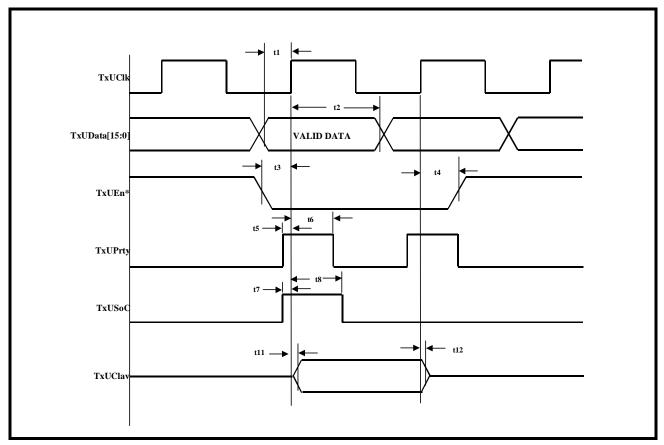

| TRANSMIT UTOPIA INTERFACE                                                                      | 54 |

| FIGURE 10. TIMING DIAGRAM FOR THE TRANSMIT UTOPIA INTERFACE BLOCK                              |    |

| TABLE 8: TIMING INFORMATION FOR THE TRANSMIT UTOPIA INTERFACE BLOCK                            | 54 |

**XPEXAR PRE** 3 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC

PRELIMINARY

XRT79L73 REV. P1.0.0

| TRANSMIT PAYLOAD DATA INPUT INTERFACE                                                                                                                    | 55        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| TRANSMIT PAYLOAD DATA INPUT INTERFACE - TIMING REQUIREMENTS                                                                                              |           |

| TABLE 9: TIMING INFORMATION FO RTHE TRNASMIT PAYLOAD DATA INPUT INTERFACE BLOCK                                                                          |           |

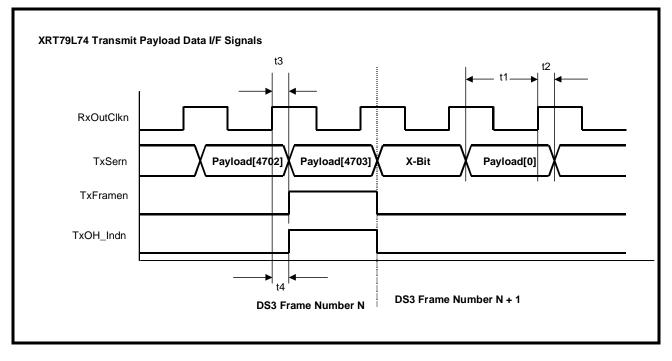

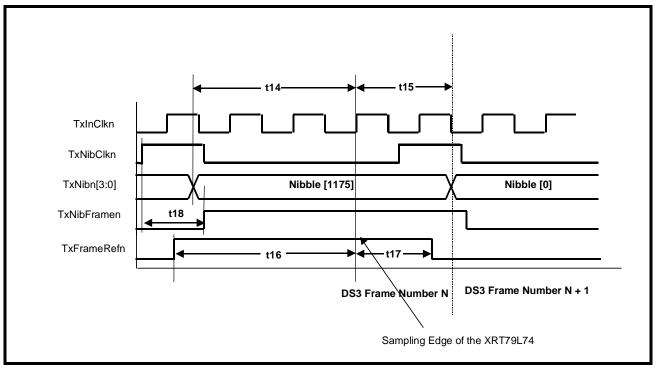

| Figure 11. Timing Diagram for the Transmit Payload Data Input Interface when the XRT79L73 is operating in both<br>and Loop-Timing Modes                  | н тне DS3 |

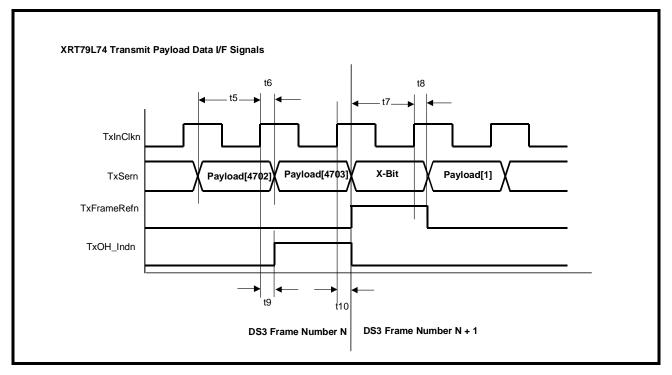

| Figure 12. Timing Diagram for the Transmit Payload Data Input Interface when the XRT79L73 is operating in both<br>And Local-Timing Modes                 |           |

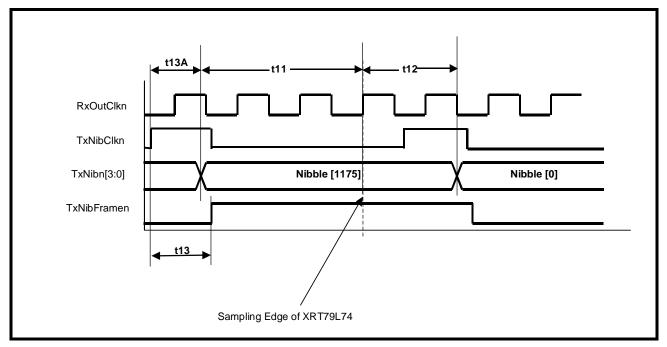

| Figure 13. Timing Diagram for the Transmit Payload Data Input Interface when the XRT79L73 is operating in both<br>Nibble-Parallel and Loop-Timing Modes  | 57        |

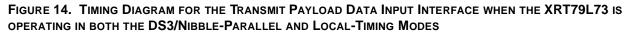

| Figure 14. Timing Diagram for the Transmit Payload Data Input Interface when the XRT79L73 is operating in both<br>Nibble-Parallel and Local-Timing Modes | 58        |

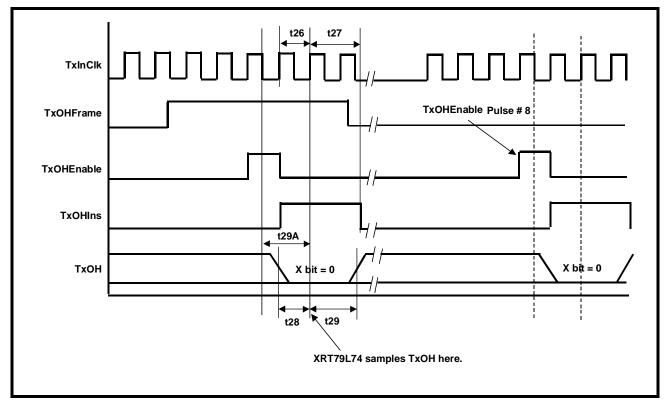

| TRANSMIT OVERHEAD DATA INPUT INTERFACE                                                                                                                   | 59        |

| TRANSMIT OVERHEAD DATA INPUT INTERFACE - TIMING REQUIREMENTS                                                                                             | 59        |

| TABLE 10: TIMING INFORMATION FOR THE TRANSMIT OVERHEAD DATA INPUT INTERFACE BLOCK                                                                        | 59        |

| Figure 15. Timing Diagram for the Transmit Overhead Data Input Interface (Method 1 Access)                                                               |           |

| FIGURE 16. TIMING DIAGRAM FOR THE TRANSMIT OVERHEAD DATA INPUT INTERFACE (METHOD 2 ACCESS)                                                               |           |

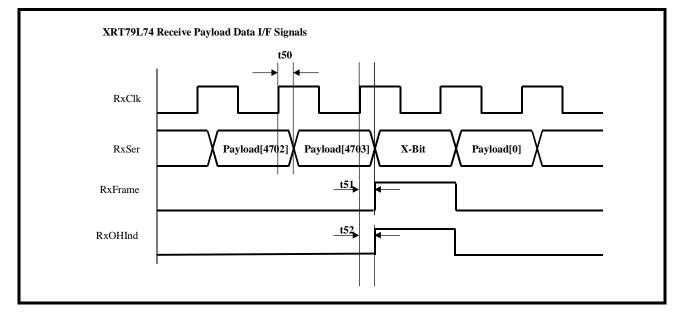

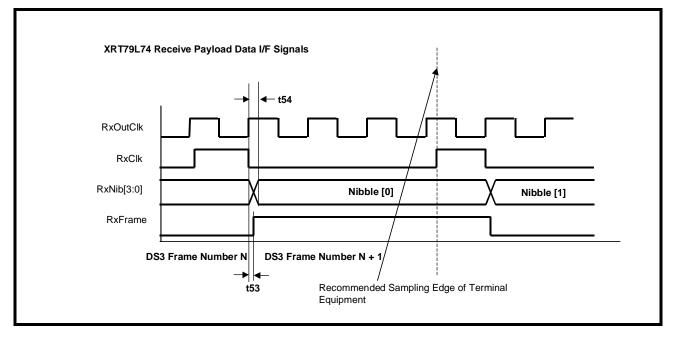

| RECEIVE PAYLOAD DATA OUTPUT INTERFACE                                                                                                                    | 62        |

| RECEIVE PAYLOAD DATA OUTPUT INTERFACE - TIMING REQUIREMENTS                                                                                              | 62        |

| TABLE 11: TIMING INFORMATION FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE BLOCK                                                                         | 62        |

| FIGURE 17. TIMING DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE (SERIAL MODE)                                                                    |           |

| FIGURE 18. TIMING DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE (NIBBLE-PARALLEL MODE)                                                           |           |

| RECEIVE OVERHEAD DATA OUTPUT INTERFACE                                                                                                                   | 64        |

| RECEIVE OVERHEAD DATA OUTPUT INTERFACE - TIMING REQUIREMENTS                                                                                             | 64        |

| AC ELECTRICAL CHARACTERISTICS (CONT.)                                                                                                                    | 64        |

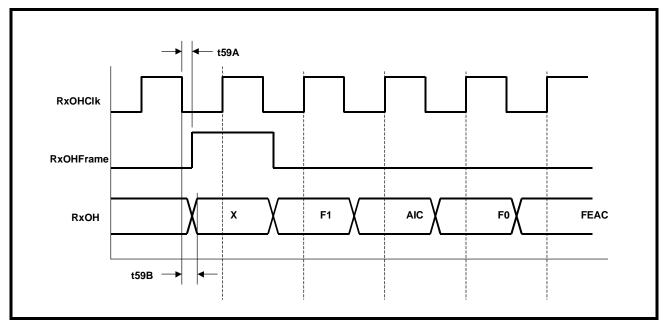

| FIGURE 19. TIMING DIAGRAM FOR THE RECEIVE OVERHEAD DATA OUTPUT INTERFACE (METHOD 1 - USING RXOHCLK)                                                      |           |

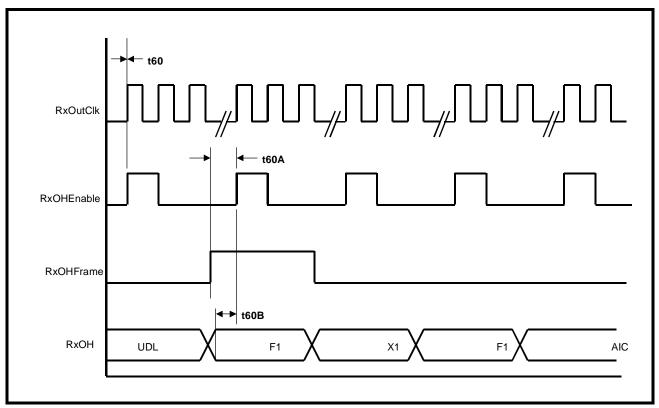

| FIGURE 20. TIMING DIAGRAM FOR THE RECEIVE OVERHEAD DATA OUTPUT INTERFACE (METHOD 2 - USING RXOHENABLE)                                                   | 65        |

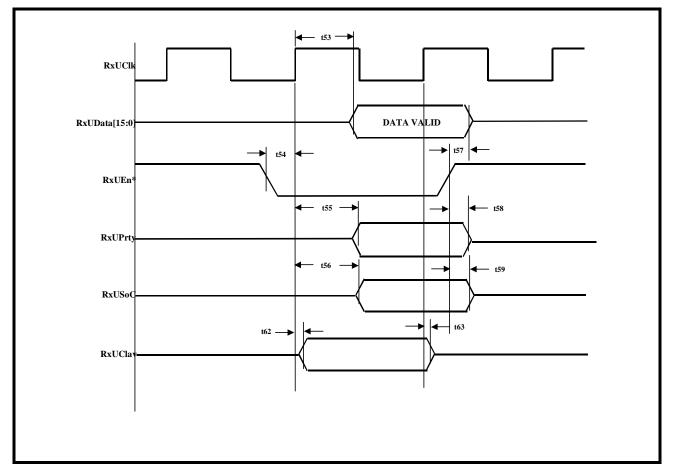

| RECEIVE UTOPIA INTERFACE                                                                                                                                 | 66        |

| RECEIVE UTOPIA INTERFACE                                                                                                                                 |           |

| Figure 21. Timing Diagram for the Receive UTOPIA Interface Block                                                                                         |           |

| TABLE 12: TIMING INFORMATION FOR THE RECEIVE UTOPIA INTERFACE BLOCK                                                                                      | 66        |

| ORDERING INFORMATION                                                                                                                                     | 68        |

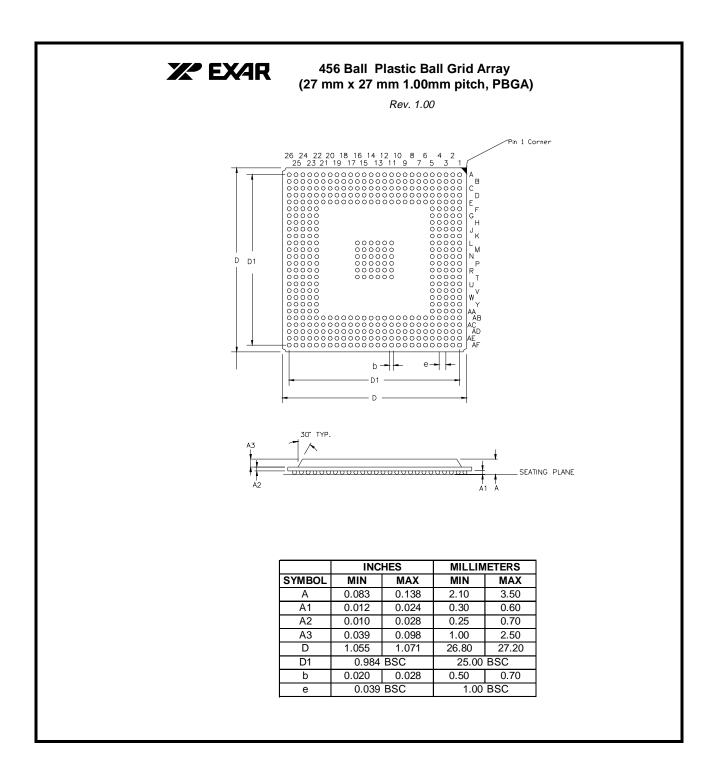

| PACKAGE DIMENSIONS                                                                                                                                       |           |

| Revision History                                                                                                                                         |           |

В

### **PIN DESCRIPTIONS**

| Pin #   | NAME         | TYPE | DESCRIPTION                                                                                                                                                                 |

|---------|--------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MICROPF | ROCESSOR INT | ERFA | CE                                                                                                                                                                          |

| AB26    | A0           | I    | Address Bus Input pins Microprocessor Interface:                                                                                                                            |

| AC26    | A1           |      | These direct address pins are used to select the on-chip Framer/UNI registers and                                                                                           |

| AD26    | A2           |      | RAM space for READ and WRITE Operations with the Microprocessor.                                                                                                            |

| AB25    | A3           |      |                                                                                                                                                                             |

| AA24    | A4           |      |                                                                                                                                                                             |

| AD25    | A5           |      |                                                                                                                                                                             |

| AC25    | A6           |      |                                                                                                                                                                             |

| AB24    | A7           |      |                                                                                                                                                                             |

| AF25    | A8           |      |                                                                                                                                                                             |

| AE25    | A9           |      |                                                                                                                                                                             |

| AF24    | A10          |      |                                                                                                                                                                             |

| AE24    | A11          |      |                                                                                                                                                                             |

| AD24    | A12          |      |                                                                                                                                                                             |

| AC24    | A13          |      |                                                                                                                                                                             |

| AF23    | A14          |      |                                                                                                                                                                             |

| AI 23   | 714          |      |                                                                                                                                                                             |

| R22     | D0           | I/O  | Bi-Directional Data Bus pins Microprocessor Interface:                                                                                                                      |

| T24     | D1           |      | These pins are used to drive and receive data over the bi-directional data bus.                                                                                             |

| T25     | D2           |      |                                                                                                                                                                             |

| T26     | D3           |      |                                                                                                                                                                             |

| U22     | D4           |      |                                                                                                                                                                             |

| U23     | D5           |      |                                                                                                                                                                             |

| U24     | D6           |      |                                                                                                                                                                             |

| U25     | D7           |      |                                                                                                                                                                             |

| AB23    | ALE/AS       | 1    | Address Latch Enable/Address Strobe:                                                                                                                                        |

| , 1020  |              |      | This input pin is used to latch the address present at the Microprocessor Interface                                                                                         |

|         |              |      | Address Bus pins A[14:0] into the Framer/UNI Microprocessor Interface block and to indicate the start of a READ or WRITE cycle. This input pin is active high, in the Intel |

|         |              |      | Mode and active low in the Motorola Mode.                                                                                                                                   |

| AE23    | CS           | I    | Chip Select Input:                                                                                                                                                          |

|         |              |      | The user must assert this active low signal in order to select the Microprocessor                                                                                           |

|         |              |      | Interface for READ and WRITE operations between the Microprocessor and the UNI/                                                                                             |

|         |              |      | Framer on-chip registers and RAM locations.                                                                                                                                 |

| R23     | INT          | 0    | Interrupt Request Output:                                                                                                                                                   |

|         |              |      | This open-drain, active-low output signal will be asserted when the Framer/UNI                                                                                              |

|         |              |      | device is requesting interrupt service from the Microprocessor. This output pin                                                                                             |

|         |              |      | should typically be connected to the Interrupt Request input of the Microprocessor.                                                                                         |

| AD23    | RD/DS        | I    | READ Strobe Intel Mode:                                                                                                                                                     |

|         |              |      | If the Microprocessor Interface is operating in the Intel Mode, then this input pin will                                                                                    |

|         |              |      | function as the $\overline{\text{RD}}$ (READ Strobe) input signal from the Microprocessor. Once this                                                                        |

|         |              |      | active-low signal is asserted, then the Framer/UNI will place the contents of the                                                                                           |

|         |              |      | addressed register within the Framer/UNI IC on the Microprocessor Bi-directional                                                                                            |

|         |              |      | Data Bus D[7:0]. When this signal is negated, the Data Bus will be tri-stated.                                                                                              |

|         |              |      | Data Strobe Motorola Mode:                                                                                                                                                  |

|         |              |      | If the Microprocessor Interface is operating in the Motorola Mode, then this input will function as the $\overline{\text{DS}}$ (Data Strobe) signal.                        |

|         |              |      | initiation as the Do (Data Ottobe) signal.                                                                                                                                  |

XRT79L73 *REV. P1.0.0*

### 3 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC

### PIN DESCRIPTIONS

| PIN #                | NAME                          | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|-------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U26                  | RDY/DTACK                     | 0    | <ul> <li>READY or DTACK:</li> <li>This active-low output pin will function as the READY output when the Microprocessor Interface is configured to operate in the Intel Mode; and will function as the DTACK output when the Microprocessor Interface is running in the Motorola Mode.</li> <li>Intel Mode - READY output:</li> <li>When the Framer/UNI negates this output pin (e.g., toggles it "Low") it indicates to the Microprocessor that the current READ or WRITE operation is to be extended until this signal is asserted (e.g., toggled "High").</li> <li>Motorola Mode - DTACK Data Transfer Acknowledge Output:</li> <li>The Framer/UNI will assert this pin in order to inform the Microprocessor that the present READ or WRITE cycle is nearly complete. If the Framer/UNI requires that the current READ or WRITE cycle be extended, then the Framer/UNI will delay its assertion of this signal. The 68000 family of Microprocessors requires this signal from its peripheral devices, in order to quickly and properly complete a READ or WRITE cycle.</li> </ul> |

| AF4                  | RESET                         | I    | <b>Reset Input:</b><br>When this active-low signal is asserted, the Framer/UNI device will be asynchro-<br>nously reset. When this occurs, all outputs will be tri-stated and all on-chip registers<br>will be reset to their default values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AA26                 | μPCLK                         | I    | Microprocessor Interface Clock Input:<br>This clock input signal is used for synchronous/burst/DMA data transfer operations.<br>This clock can be running up to 33MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| AC23                 | WR/R/W                        | Ι    | <ul> <li>Write Strobe Intel Mode:</li> <li>If the Microprocessor Interface is configured to operate in the Intel Mode, then this active-low input pin functions as the WR (WRITE Strobe) input signal from the Microprocessor. Once this active-low signal is asserted, the Framer/UNI will latch the contents of the bi-directional data D[7:0] into the addressed registers or Buffer location within the Framer/UNI IC.</li> <li>R/W Input Pin Motorola Mode:</li> <li>When the Microprocessor Interface Section is operating in the Motorola Mode, then this pin is functionally equivalent to the R/W pin. In the Motorola Mode, a READ operation occurs if this pin is at a logic "1". Similarly a WRITE operation occurs if this pin is at a logic "0".</li> </ul>                                                                                                                                                                                                                                                                                                            |

| AB22<br>AC22<br>AD22 | PTYPE_0<br>PTYPE_1<br>PTYPE_2 | Ι    | Microprocessor Type Select input:<br>These three input pins are used to configure the Microprocessor Interface block to<br>readily support a wide variety of Microprocessor Interfaces. The relationship<br>between the settings of these input pins and the corresponding Microprocessor Inter-<br>face configuration is presented below.<br>"000" = Intel Asynchronous Mode<br>"001" = Motorola Asynchronous Mode<br>"111" = Power PC Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AF22                 | DBEN                          | I    | <b>Bi-directional Data Bus Enable Input pin:</b><br>If the Microprocessor Interface is operating in the Intel-I960 Mode, then this input pin<br>is used to enable the Bi-directional Data Bus.<br>Setting this input pin "Low" enables the Bi-directional Data bus. Setting this input<br>"High" tri-states the Bi-directional Data Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

PRELIMINARY

| PIN #               | NAME                       | TYPE | DESCRIPTION                                                                                                                                    |

|---------------------|----------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST AN             | D DIAGNOSTIC               |      |                                                                                                                                                |

| AD5                 | ТСК                        | Ι    | <b>Test Clock input, Boundary Scan Clock input:</b><br><b>Note:</b> This input pin should be pulled "Low" for normal operation.                |

| AC5                 | TDI                        | I    | <b>Test Data input, Boundary Scan Test Data Input:</b><br><b>Note:</b> This input pin should be pulled "Low" for normal operation.             |

| AB5                 | TDO                        | 0    | <b>Test Data output:</b><br>Boundary Scan Test Data Output:                                                                                    |

| AE5                 | TMS                        | I    | <b>Test Mode Select, Boundary Scan Test Mode Select input pin:</b><br><b>Note:</b> This input pin should be pulled "Low" for normal operation. |

| AF5                 | TRST                       | I    | <b>Test Mode Reset, Boundary Scan Mode Reset Input pin:</b><br><b>Note:</b> This input pin should be pulled "Low" for normal operation.        |

| AD4                 | TESTMODE                   | ***  | Factory Test Mode Pin:<br>Tie this pin to Ground.                                                                                              |

| AC9<br>AC17<br>AC13 | Anaio2<br>Anaio1<br>Anaio0 | I/O  | Analog Input/Output Test Pin:<br>These pins should be pulled "Low" for normal operation.                                                       |

| PIN #  | NAME         | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                      |

|--------|--------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GENERA | L PURPOSE IN | PUT AN | D OUTPUT PINS                                                                                                                                                                                                                                                                                                                                                                    |

| U3     | DMO1         | 0      | Drive Monitor Output Pins:                                                                                                                                                                                                                                                                                                                                                       |

| N26    | DMO2         | 0      | For each channel, if the DMO output signal is "High", then it means that the drive                                                                                                                                                                                                                                                                                               |

| W5     | DMO3         | 0      | monitor circuitry within the XRT79L73 has not detected any bipolar signals at the MTIP and MRING inputs (or via the Internal Drive Monitor circuit) within the last 128 $\pm$ 32 bit periods. If this output signal is "Low", then it means that bipolar signals are being detected at the MTIP and MRING input pins of the XRT79L73.                                            |

| W1     | GPIO_0       | I/O    | General Purpose Input/Output Pins:                                                                                                                                                                                                                                                                                                                                               |

| W2     | GPIO_1       |        | Each of these pins can be configured to function as either a general-purpose input                                                                                                                                                                                                                                                                                               |

| W3     | GPIO_2       |        | or output pin. If a given pin (GPIO_X) is configured to function as an input pin,                                                                                                                                                                                                                                                                                                |

| W4     | GPIO_3       |        | then the state of this input pin can be monitored by reading Bit X within the "Oper-<br>ation General Purpose Pin Data" Register (Address Location = 0x0147).                                                                                                                                                                                                                    |

|        |              |        | If a given pin is configured to function as an output pin, then the state of this out-<br>put pin (GPIO_X) can be controlled by writing the appropriate value into Bit X<br>within the "Operation General Purpose Pin Data" Register.                                                                                                                                            |

|        |              |        | Finally, the user can configure a given GPIO_X pin to be an input pin by setting Bit X, within the "Operation General Purpose Pin Direction Control Register (Address = 0x014B) to "0". Conversely, the user can configure the GPIO_X pin to be an output pin by setting Bit X, within the "Operation General Purpose Pin Direction Control" Register (Address = 0x014B) to "1". |

| Pin #   | NAME          | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|---------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRANSMI | T SYSTEM SIDE | INTERF | ACE PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AC4     | NibbleIntf    | I      | Nibble Interface Select Input pin:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |               |        | This input pin permits the user to configure the Transmit Payload Data<br>Input Interface and the Receive Payload Data Output Interface blocks to<br>operate in either the "Serial" or the "Nibble-Parallel" Mode.                                                                                                                                                                                                                                                                                                      |

|         |               |        | Setting this input pin "high" configures each of these blocks to operate in the Nibble-Parallel Mode. In this mode, the "Transmit Payload Data Input Interface" block will accept the "outbound" payload data (from the System-Side terminal equipment) in a "nibble-parallel" manner via the "TxNib[3:0]" input pins. Further, the Receive Payload Data Output Interface block will output "inbound" payload data (to the System-Side terminal equipment) in a "nibble-parallel" with "System-Side terminal equipment. |

|         |               |        | Setting this input pin "low" configures each of these blocks to operate in<br>the Serial Mode. In this mode, the Transmit Payload Data Input Interface<br>block will accept the "outbound" payload data (from the System-Side<br>terminal equipment) in a "serial" manner via the "TxSer" input pin.<br>Further, the Receive Payload Data Output Interface block will output the<br>"inbound" payload data (to the System-Side terminal equipment) in a<br>serial manner, via the "RxSer" output pin.NOTE:              |

|         |               |        | <b>Note:</b> This input pin is only active if the XRT79L73 device has been configured to operate in the Clear-Channel Framer Mode. The user is advised to tie this input pin to GND if the user intends to configure the XRT79L73 device to operate in the ATM UNI or PPP Modes.                                                                                                                                                                                                                                        |

PRELIMINARY

**XP EXAR**

| Pin #             | NAME                                      | TYPE      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------|-------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U5<br>N24<br>V2   | TxFrame1<br>TxFrame2<br>TxFrame3          | 0<br>0    | <ul> <li>Transmit End of DS3/E3 Frame Indicator:</li> <li>These output pins will pulse "High" for one DS3 or E3 clock period, when the Transmit Section of the XRT79L73 is processing the last bit of a given DS3 or E3 frame. The implications of these output pins, for each mode of operation, are described below.</li> <li>ATM UNI/PPP/High-Speed HDLC Controller Mode:</li> <li>These output pins serve as an end-of-frame indication to the local terminal equipment.</li> <li>Clear-Channel Framer Mode:</li> <li>If the XRT79L73 is configured to operate in the Clear-Channel Framer mode, then these output pins serve to alert the Local Terminal Equipment that it needs to begin transmission of a new DS3 or E3 frame. Hence, the Local Terminal Equipment uses these output signals to maintain Framing Alignment with the XRT79L73.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                           |

| AF1<br>W25<br>AF2 | TxFrameRef1<br>TxFrameRef2<br>TxFrameRef3 | <br> <br> | <ul> <li>Transmit DS3/E3 Framer - Framing Alignment Input pin:</li> <li>If the the Transmit Section of the XRT79L73 is configured to operate in the Local-Timing/Frame-Slave Mode, then the Transmit DS3/E3 Framer block will use these input signals as the Framing Reference.</li> <li>When the XRT79L73 is configured to operate in this mode any rising edge at these input pins will cause the Transmit DS3/E3 Framer block to begin its creation of a new DS3 or E3 frame. Consequently, the user must supply a clock signal that is equivalent to the DS3 or E3 frame rates to these input pins. Further, it is imperative that this clock signal be synchronized with the 44.736MHz or 34.368MHz clock signal applied to the TxInClk input pins.</li> <li>Note: These input pins should be tied to GND if they are not to be used as the Transmit DS3/E3 Framer - Framing Reference input signals.</li> </ul>                                                                                                                                                                                                                                                                                                                                                     |

| U4<br>N25<br>V1   | TxInClk1<br>TxInClk2<br>TxInClk3          |           | <ul> <li>Transmit DS3/E3 Framer Block - Timing Reference Signal:</li> <li>If the Transmit Section of the XRT79L73 is configured to operate in the Local-<br/>Timing Mode, then it will use this signal as the Timing Reference. If the<br/>XRT79L73 is being operating in the DS3 Mode, then the user is expected to<br/>apply a high-quality 44.736MHz clock signal to these input pins. Likewise, if the<br/>XRT79L73 is being operated in the E3 Mode, then the user is expected to apply<br/>a high-quality 34.368MHz clock signal to these input pins.</li> <li>A Note for Clear-Channel Framer Operation:</li> <li>If the user is operating the XRT79L73 device in both the Clear-Channel<br/>Framer and Local-Timing modes, then the user should design or<br/>configure the System-Side terminal equipment circuitry, such that<br/>"outbound" DS3 or E3 data will be output, upon the falling edge of<br/>TxInClk. The Transmit Payload Data Input Interface (within the Transmit<br/>Section of the XRT79L73 device) will sample the data, applied to the<br/>"TxSer" input pin, upon the rising edge of TxInClk.</li> <li>Note: This input pin should be tied to GND if the XRT79L73 device is configured<br/>to operate in the "Loop-Timing" Mode.</li> </ul> |

XRT79L73 REV. P1.0.0

### **XPEXAR PRE** 3 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC

| Pin #             | NAME                                                                                | TYPE        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|-------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD2<br>Y22<br>AB4 | TxOH1/<br>TxHDLCDat1_5<br>TxOH2/<br>TxHDLCDat2_5<br>TxOH3/<br>TxHDLCDat3_5          | 1           | <ul> <li>Transmit Overhead Data Input/Transmit HDLC Controller Data Bit 5 input pins:</li> <li>The function of these input pins depend upon whether or not the XRT79L73 has been configured to operate in the High-Speed HDLC Controller Mode.</li> <li>Non-High Speed HDLC Controller Mode - TxOH:</li> <li>The Transmit Overhead Data Input Interface accepts overhead via these input pins, and insert this data into the overhead bit positions within the outbound DS3 or E3 frames. If the TxOHIns input pins are pulled "High", then the Transmit Overhead Data Input Interface will sample the overhead data, via these input pins, upon the falling edge of the TxOHClk output signals.</li> <li>Conversely, if the TxOHIns input pins are NOT pulled "High", then the Transmit Overhead Data Input Interface block will be inactive and will not accept any overhead data via the TxOH input pins.</li> <li>High Speed HDLC Controller Mode - TxHDLCDat_5:</li> <li>If the XRT79L73 is configured to operate in the High-Speed HDLC Controller mode, then the local terminal equipment will be provided with a byte-wide Transmit HDLC Controller byte-wide input interface. These input pins will function as Bit 5 within this byte wide interface.</li> </ul>                                                                                                                                                  |

| AC2<br>W26<br>AB3 | TxOHIns1/<br>TxHDLCDat1_4<br>TxOHIns2/<br>TxHDLCDat2_4<br>TxOHIns3/<br>TxHDLCDat3_4 | 1           | <ul> <li>Transmit Overhead Data Insert Input/Transmit HDLC Controller Data Bit 4 input pins:</li> <li>The function of these input pins depend upon whether or not the XRT79L73 has been configured to operate in the High-Speed HDLC Controller Mode.</li> <li>Non-High Speed HDLC Controller Mode - TxOHIns:</li> <li>This input pins are used to either enable or disable the Transmit Overhead Data Input Interface block. If the Transmit Overhead Data Input Interface block. If the Transmit Overhead Data Input Interface block. If the Transmit Overhead Data Input Interface block is enabled, then it will accept overhead data from the local terminal equipment via the TxOH input pins; and insert this data into the overhead bit positions within the outbound DS3 or E3 data stream.</li> <li>Conversely, if the Transmit Overhead Data Input Interface block is disabled, then it will NOT accept overhead data from the local terminal equipment. Pulling these input pins "High" enables the Transmit Overhead Data Input Interface block.</li> <li>High-Speed HDLC Controller Mode - TxHDLCDat_4:</li> <li>If the XRT79L73 is configured to operate in the High-Speed HDLC Controller mode, then the local terminal equipment will be provided with a byte-wide Transmit HDLC Controller byte-wide input interface. These input pins will function as Bit 4 within this byte wide interface.</li> </ul> |

| G3<br>A26<br>J1   | TxOHClk1<br>TxOHClk2<br>TxOHClk3                                                    | 0<br>0<br>0 | <ul> <li>Transmit Overhead Clock Output:</li> <li>These output pins functions as the Transmit Overhead Data Input Interface clock signals. If the user enables the Transmit Overhead Data Input Interface block by asserting the TxOHIns input pins, then the Transmit Overhead Data Input Interface block will sample and latch the data residing on the TxOH input pins upon the falling edge of these signals.</li> <li>Note: The Transmit Overhead Data Input Interface block is disabled if the user has configured the XRT79L73 to operate in the High-Speed HDLC Controller Mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

PRELIMINARY

| Pin # | NAME                         | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G2    | TxOHFrame1/<br>TxHDLCClk1    | 0    | Transmit Overhead Framing Pulse/Transmit HDLC Controller Clock Output pin:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| D23   | TxOHFrame2/<br>TxHDLCClk2    | 0    | The function of these output pins depend upon whether or not the XRT79L73 has been configured to operate in the High-Speed HDLC Controller Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| H5    | TxOHFrame3/                  | 0    | Non-High-Speed HDLC Controller Mode - TxOHFrame:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | TxHDLCClk3                   |      | These output pins pulse high for one TxOHClk period coincident with the instant the Transmit Overhead Data Input Interface would be accepting the first overhead bit within an outbound DS3 or E3 frame.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |                              |      | High Speed HDLC Controller Mode - TxHDLCClk:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       |                              |      | This output pin functions as the "demand" clock output signal for the "Transmit<br>HDLC Controller" byte-wide input interface. This clock signal is ultimately<br>derived from either the TxInClk clock signal (for Local-Timing Applications) or the<br>RxOutClk clock signal (for Loop-Timing Applications). Hence, the frequency of<br>this clock signal is nominally one-eight of that of the TxInClk or the RxOutClk sig-<br>nals.<br>The Transmit HDLC Controller block will sample the contents of the Transmit<br>HDLC Controller byte-wide input interface, upon the rising edge of these clock<br>output signals. Therefore, the local terminal equipment should be designed to<br>output data onto the TxHDLCDatn_[7:0] bus upon the falling edge of these clock<br>output signals. |

| R2    | TxOHEnable1/<br>TxHDLCDat1_7 | I/O  | Transmit Overhead Enable Output indicator/Transmit HDLC Controller Data<br>Bit 7 Input:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| M24   | TxOHEnable2/<br>TxHDLCDat1_2 | I/O  | The function of these input pins depend upon whether or not the XRT79L73 is configured to operate in the High Speed HDLC Controller Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| U2    |                              | I/O  | Non-High Speed HDLC Controller Mode - TxOHEnable:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 02    | TxHDLCDat1_3                 | 1/0  | The XRT79L73 will assert these output pins, for one TxInClk period, just prior to the instant that the Transmit Overhead Data Input Interface will be sampling and processing an overhead bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                              |      | If the local terminal equipment intends to insert its own value for an overhead bit, into the outbound DS3 or E3 data stream, then it is expected to sample the state of these signals, upon the falling edge of TxInClk. Upon sampling the TxOHEnable signal "High", the local terminal equipment should;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       |                              |      | <ul><li>(1) place the desired value of the overhead bit onto the TxOH input pin and</li><li>(2) assert the TxOHIns input pin.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       |                              |      | The Transmit Overhead Data Input Interface block will sample and latch the data on the TxOH signal, upon the rising edge of the very next TxInClk input signal.<br><b>High-Speed HDLC Controller Mode - TxHDLCDat_7:</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |                              |      | If the XRT79L73 is configured to operate in the High-Speed HDLC Controller mode, then the local terminal equipment will be provided with a byte-wide Transmit HDLC Controller byte-wide input interface. These input pins will function as Bit 7 (the MSB) within this byte wide interface.<br>Data, residing on the Transmit HDLC Controller byte wide input interface, will be                                                                                                                                                                                                                                                                                                                                                                                                               |

|       |                              |      | sampled upon the rising edge of the TxHDLCClk output signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

PRELIMINARY

XRT79L73 *REV. P1.0.0*

| Pin #     | Nаме                       | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|----------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|