www.DataShapril 2009 REV.1.0.0

#### **GENERAL DESCRIPTION**

The XRT83VL38 is a fully integrated Octal (eight channel) long-haul and short-haul line interface unit for T1 (1.544Mbps)  $100\Omega$ , E1 (2.048Mbps)  $75\Omega$  or  $120\Omega$ , or J1  $110\Omega$  applications.

In long-haul applications the XRT83VL38 accepts signals that have been attenuated from 0 to 36dB at 772kHz in T1 mode (equivalent of 0 to 6000 feet of cable loss) or 0 to 43dB at 1024kHz in E1 mode.

In T1 applications, the XRT83VL38 can generate five transmit pulse shapes to meet the short-haul Digital Cross-Connect (DSX-1) template requirements as well as for Channel Service Units (CSU) Line Build Out (LBO) filters of 0dB, -7.5dB -15dB and -22.5dB as required by FCC rules. It also provides programmable transmit pulse generators for each channel that can be used for output pulse shaping allowing performance improvement over a wide variety of conditions (The arbitrary pulse generators are available in both T1 and E1 modes).

The XRT83VL38 provides both a parallel/serial **Host** microprocessor interface as well as a **Hardware** mode for programming and control.

Both the B8ZS and HDB3 encoding and decoding functions are selectable as well as AMI. Two on-chip

crystal-less jitter attenuators with a 32 or 64 bit FIFO can be placed in the receive and the transmit paths with loop bandwidths of less than 3Hz. The XRT83VL38 provides a variety of loop-back and diagnostic features as well as transmit driver short circuit detection and receive loss of signal monitoring. It supports internal impedance matching for  $75\Omega,\,100\Omega,\,110\Omega$  and  $120\Omega$  for both transmitter and receiver. In the absence of the power supply, the transmit outputs and receive inputs are tri-stated allowing for redundancy applications. The chip includes an integrated programmable clock multiplier that can synthesize T1 or E1 master.

## **APPLICATIONS**

- T1 Digital Cross-Connects (DSX-1)

- ISDN Primary Rate Interface

- CSU/DSU E1/T1/J1 Interface

- T1/E1/J1 LAN/WAN Routers

- Public switching Systems and PBX Interfaces

- T1/E1/J1 Multiplexer and Channel Banks

### Features (See Page 2)

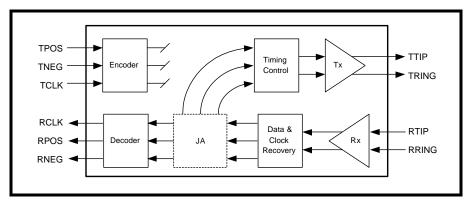

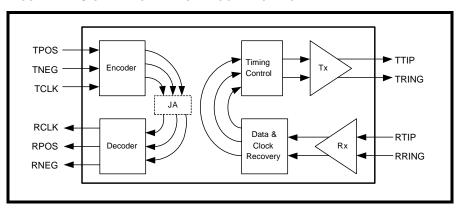

FIGURE 2. BLOCK DIAGRAM OF THE XRT83VL38 T1/E1/J1 LIU (HARDWARE MODE)

#### **FEATURES**

- Fully integrated eight channel long-haul or short-haul transceivers for E1,T1 or J1 applications

- Adaptive Receive Equalizer for up to 36dB cable attenuation

- Programable Transmit Pulse Shaper for E1,T1 or J1 short-haul interfaces

- Five fixed transmit pulse settings for T1 short-haul applications plus a fully programmable waveform generator for transmit output pulse shaping available for both T1 and E1 modes

- Transmit Line Build-Outs (LBO) for T1 long-haul application from 0dB to -22.5dB in three 7.5dB steps

- Selectable receiver sensitivity from 0 to 36dB cable loss for T1 @772kHz and 0 to 43dB for E1 @1024kHz

- Receive monitor mode handles 0 to 29dB resistive attenuation along with 0 to 6dB of cable attenuation for E1 and 0 to 3dB of cable attenuation for T1 modes

- Supports  $75\Omega$  and  $120\Omega$  (E1),  $100\Omega$  (T1) and  $110\Omega$  (J1) applications

- Internal and/or external impedance matching for 75 $\Omega$ , 100 $\Omega$ , 110 $\Omega$  and 120 $\Omega$

- Tri-State transmit output and receive input capability for redundancy applications

- Provides High Impedance for Tx and Rx during power off

- Transmit return loss meets or exceeds ETSI 300-166 standard

- On-chip digital clock recovery circuit for high input jitter tolerance

- Crystal-less digital jitter attenuator with 32-bit or 64-bit FIFO selectable in transmit or receive paths

- On-chip frequency multiplier generates T1 or E1 Master clocks

- High receiver interference immunity

- On-chip transmit short-circuit protection and limiting, and driver fail monitor output (DMO)

- Receive loss of signal (RLOS) output

- www.DataSi**REV.1.0.0**n

- On-chip HDB3/B8ZS/AMI encoder/decoder functions

- QRSS pattern generator and detection for testing and monitoring

- Error and Bipolar Violation Insertion and Detection

- Receiver Line Attenuation Indication Output in 1dB steps

- Network Loop-Code Detection for automatic Loop-Back Activation/Deactivation

- Transmit All Ones (TAOS) and In-Band Network Loop Up and Down code generators

- Supports Local Analog, Remote, Digital and Dual Loop-Back Modes

- Meets or exceeds T1 and E1 short-haul and long-haul network access specifications in ITU G.703, G.775, G.736 and G.823; TR-TSY-000499; ANSI T1.403 and T1.408; ETSI 300-166 and AT&T Pub 62411

- Supports both Hardware and Host (parallel or serial) Microprocessor interface for programming

- Programmable Interrupt

- Low power dissipation

- Logic inputs accept either 3.3V or 5V levels

- Dual 3.3V and 1.8V Supply Operation

- 225 ball BGA package

- -40°C to +85°C Temperature Range

### ORDERING INFORMATION

| PART NUMBER | PACKAGE      | OPERATING TEMPERATURE RANGE |

|-------------|--------------|-----------------------------|

| XRT83VL38IB | 225 Ball BGA | -40°C to +85°C              |

REV. 1.0.0

# FIGURE 3. PACKAGE PIN OUT

|                  |         | 1        |               |         |         |         |         | ,                 |                  |              |         |         |         |                              |                             |                 | ,        | -  |

|------------------|---------|----------|---------------|---------|---------|---------|---------|-------------------|------------------|--------------|---------|---------|---------|------------------------------|-----------------------------|-----------------|----------|----|

| DVDD_DR          | NC12    | RTIP_3   | RRING_3       | NC11    | RRING_2 | RTIP_2  | RNEG_2  | GAUGE             | о∨ооо_µР         | RTIP_6       | RRING_6 | SENSE   | SER_PAR | RRING_7                      | RTIP_7                      | RVDD_7          | DGND_DR  | 18 |

| RCLK_3           | RPOS_3  | TGND_3   | RGND_3        | TVDD_3  | TTIP_2  | RGND_2  | DGND_µP | AGND_BIAS         | AVDD_BIAS        | RPOS_6       | RGND_6  | RVDD_6  | TRING_7 | RGND_7                       | RPOS_7                      | DMO_6           | RNEG_7   | 17 |

| RLOS_3           | RNEG_3  | TTIP_3   | RVDDD_3       | TRING_3 | TVDD_2  | RVDD_2  | RCLK_2  | PTS1              | RXON             | <u> </u> E   | RNEG_6  | TIP_6   | TIP_7   | TGND_7                       | TGND_6                      | RCLK_7          | TCLK_6   | 16 |

| TCLK_2           | TNEG_3  | DMO_2    | RPOS_2        | TGND_2  | TRING_2 | DGND_DR | RLOS_2  | RLOS_6            | DVDD_DR          | PTS2         | RCLK_6  | TVDD_6  | TVDD_7  | TRING_6                      | RLOS_7                      | TCLK_7          | TPOS_6   | 15 |

| JASELO           | TPOS_2  | TCLK_3   | TPOS_3        |         |         |         |         |                   |                  |              |         |         |         | TNEG_7                       | TPOS_7                      | TNEG_6          | DMO_7    | 41 |

| TXON_0 JASEL0    | JASEL1  | DMO_3    | TNEG_2 TPOS_3 |         |         |         |         |                   |                  |              |         |         |         | TXON_7                       | µPCLK                       | TXON_5 TNEG_6   | TXON_4   | 13 |

| A[7]             | TX0N_3  | TXON_2   | TXON_1        |         |         |         |         |                   |                  |              |         |         |         | TERSELO TXON_6 TXON_7 TNEG_7 | TERSEL1 RXMUTE µPCLK TPOS_7 | TEST            | ICT      | 12 |

| A[3]             | A[6]    | A[5]     | A[4]          |         |         |         |         |                   |                  |              |         |         |         | TERSELO                      | TERSEL1                     | RXTSEL          | TXTSEL   | 7  |

| A[1]             | A[2]    | A[0]     | DVDD_PDR      |         |         |         |         | L38               | (w.              | 3GA          |         |         |         | RXRES1                       | HW_HOST                     | DVDD_PDR RXTSEL | RXRESO   | 10 |

| DVDD             | DGND    | DGND_PDR | DVDD_DR       |         |         |         |         | XRT83VL38         | (Top View)       | 225 Ball BGA |         |         |         | DVDD_DR                      | DGND_DR                     | D[1]            | D[3]     | 6  |

| CLKSEL0          | CLKSEL1 | CLKSEL2  | DGND_DR       |         |         |         |         | ×                 |                  | 8            |         |         |         | DGND_PDR                     | RESET                       | D[2]            | D[4]     | 8  |

| ALE_AS           | SS      | RD_DS    | WR_R/W        | -       |         |         |         |                   |                  |              |         |         |         | [0]                          | [ <u>7</u> ]0               | [9]0            | D[5]     | 7  |

| TAOS_2 RDY_DTACK | TAOS_1  | TAOS_3   | TAOS_0        |         |         |         |         |                   |                  |              |         |         |         | TAOS_7                       | TAOS_4                      | TAOS_5          | TAOS_6   | 9  |

| TAOS_2 F         | TNEG_1  | TPOS_0   | DMO_0         | RVDD_1  |         |         |         |                   |                  |              |         |         |         | DMO_4                        | TCLK_5                      | TPOS_5          | TNEG_5   | 5  |

| TPOS_1           | TCLK_0  | TNEG_0   | DMO_1         | TVDD_0  | TVDD_1  | TTIP_1  | RLOS_1  | DVDD_DR           | SR_DR            | GNDPLL_2     | RNEG_5  | TRING_5 | DMO_5   | TVDD_4                       | RNEG_4                      | TNEG_4          | TPOS_4   | 4  |

| TCLK_1           | RCLK_0  | RLOS_0   | TGND_0        | TTIP_0  | TRING_1 | RGND_1  | RCLK_1  |                   | GNDPLL_1         | RCLK_5       | RPOS_5  | RVDD_5  | TGND_5  | TGND_4                       | TCLK_4                      | RCLK_4          | RLOS_4   | က  |

| RNEG_0           | RPOS_0  | RVDD_0   | RGND_0        | TRING_O | TGND_1  | RPOS_1  | RNEG_1  | VDDPLL_2 VDDPLL_1 | DGND_DR GNDPLL_1 | RLOS_5       | RGND_5  | TTIP_5  | TRING_4 | TTIP_4                       | RGND_4                      | RPOS_4          | RVDD_4   | 2  |

| DGND_PDR         | ОДТ     | RTIP_0   | RRING_0       | SMT     | RRING_1 | RTIP_1  | MCLKOUT | MCLKE1 \          | MCLKT1 [         | RTIP_5       | RRING_5 | TCLK    | TVDD_5  | Ē                            | RRING_4                     | RTIP_4          | DVDD_PDR | -  |

| 4                | В       | O        | Ω             | Ш       | ш       | Ō       | I       | 7                 | Y                |              | Σ       | Z       | Ф       | 22                           | -                           | ⊃               | >        | 4  |

# **GENERAL DESCRIPTION 1**

Applications 1

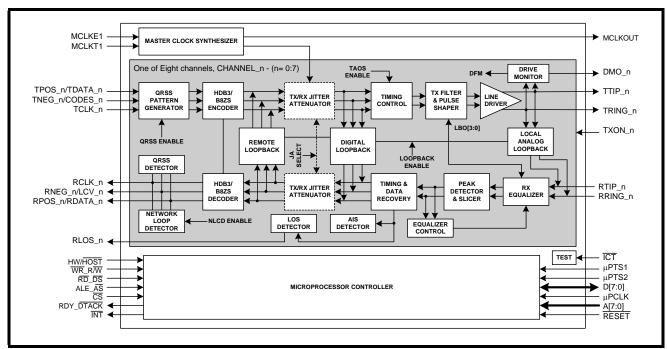

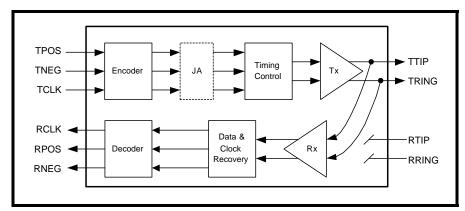

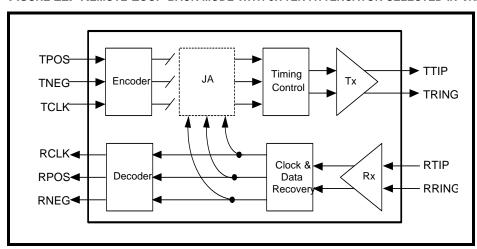

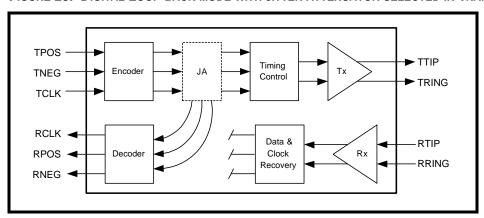

Block Diagram of the XRT83VL38 T1/E1/J1 LIU (Host Mode) 1

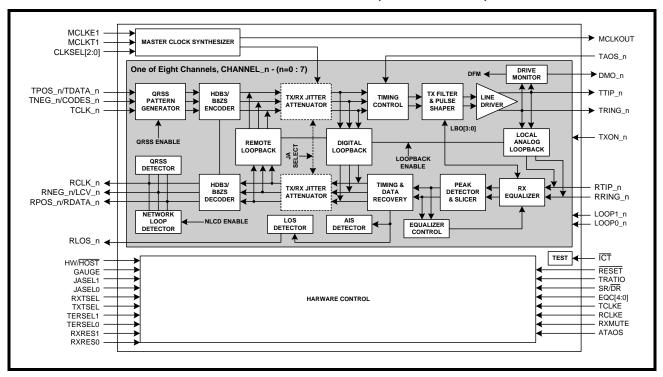

Block Diagram of the XRT83VL38 T1/E1/J1 LIU (Hardware Mode) 2

Features 2

Ordering Information 3

Package Pin Out 4

PIN DESCRIPTION BY FUNCTION 5

Receive Sections 5

**Transmitter Sections 7**

Microprocessor Interface 11

jitter Attenuator 14

Clock Synthesizer 14

Alarm Functions/Redundancy Support 16

Power and Ground 19

**FUNCTIONAL DESCRIPTION 22**

Master Clock Generator 22

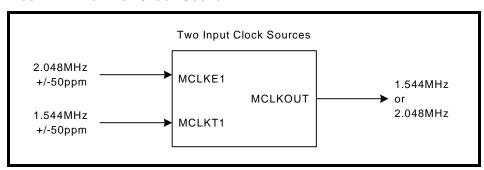

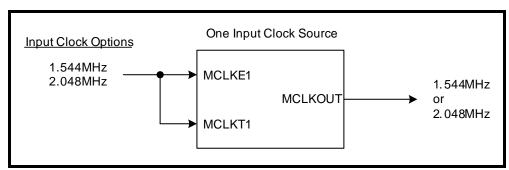

Two Input Clock Source 22

One Input Clock Source 22

Master Clock Generator 23

23

**RECEIVER 23**

Receiver Input 23

Receive Monitor Mode 24

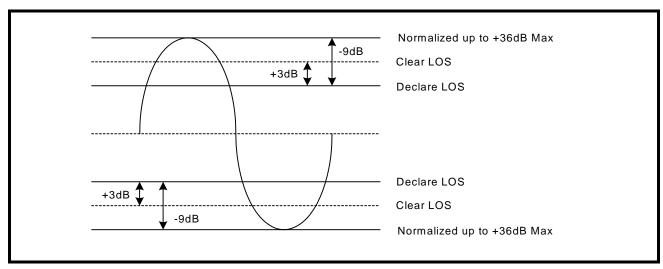

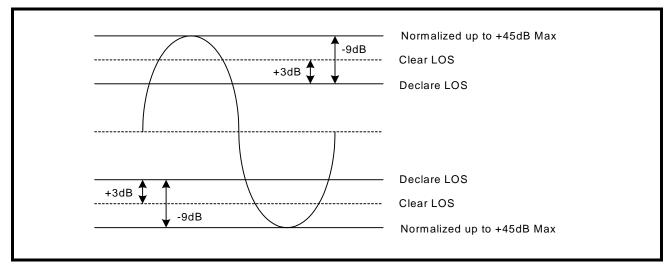

Receiver Loss of Signal (RLOS) 24

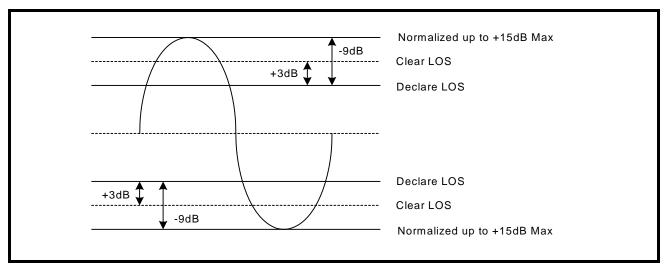

Simplified Diagram of -15dB T1/E1 Short Haul Mode and RLOS Condition 24

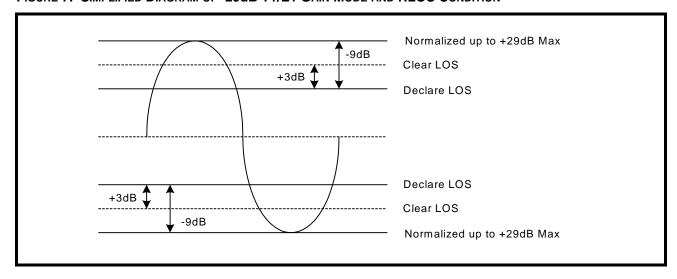

Simplified Diagram of -29dB T1/E1 Gain Mode and RLOS Condition 25

Simplified Diagram of -36dB T1/E1 Long Haul Mode and RLOS Condition 25

Simplified Diagram of Extended RLOS mode (E1 Only) 26

Receive HDB3/B8ZS Decoder 26

Recovered Clock (RCLK) Sampling Edge 26

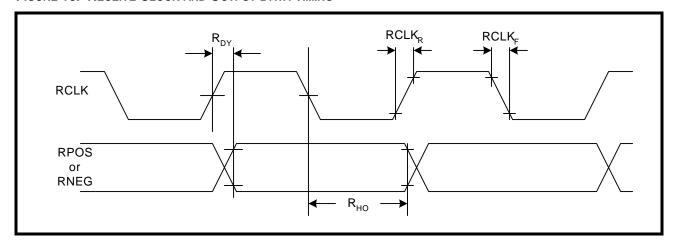

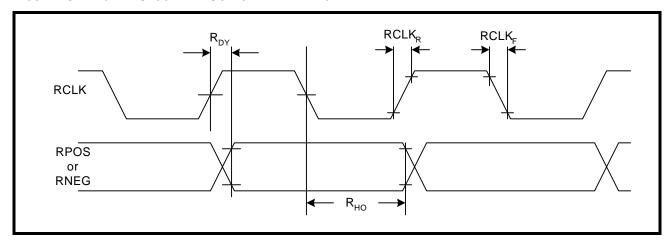

Receive Clock and Output Data Timing 27

Jitter Attenuator 27

Gapped Clock (JA Must be Enabled in the Transmit Path) 27

Maximum Gap Width for Multiplexer/Mapper Applications 27

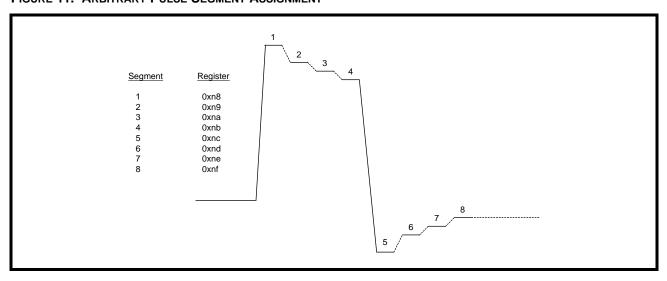

Arbitrary Pulse Generator for T1 and e1 28

Arbitrary Pulse Segment Assignment 28

TRANSMITTER 28

Digital Data Format 28

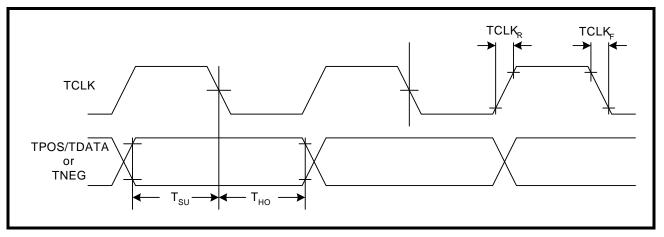

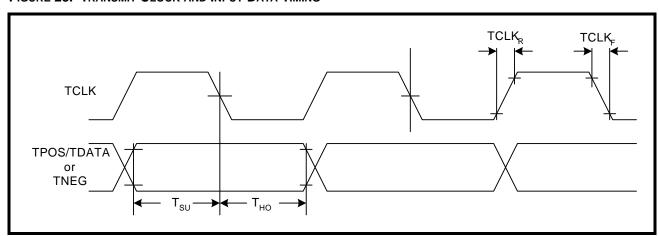

Transmit Clock (TCLK) Sampling Edge 28

Transmit Clock and Input Data Timing 29

Transmit HDB3/B8ZS Encoder 29

Examples of HDB3 Encoding 29

Examples of B8ZS Encoding 29

29

Driver Failure Monitor (DMO) 30

Transmit Pulse Shaper & Line Build Out (LBO) circuit 30

## XRT83VL38

# WWW.DOCTAL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

REV. 1.0.0

Receive Equalizer Control and Transmit Line Build-Out Settings 30

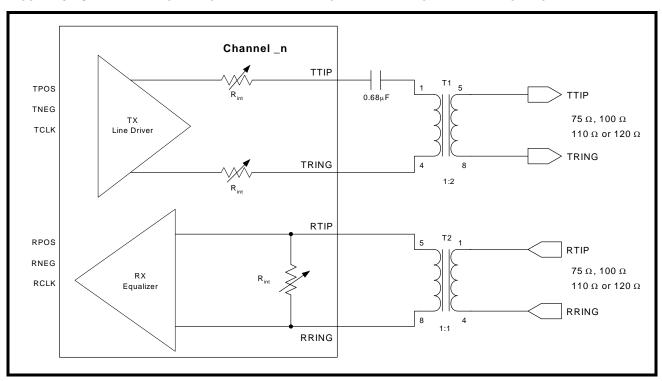

Transmit and Receive Terminations 32

RECEIVER (Channels 0 - 7) 32

**Internal Receive Termination Mode 32**

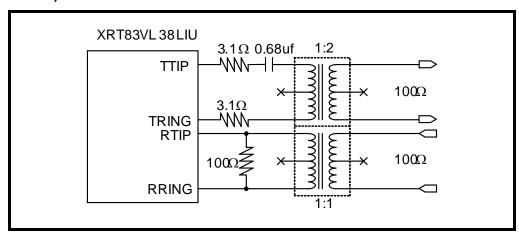

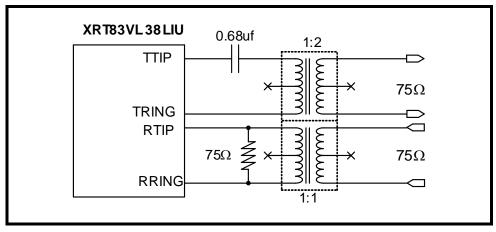

**Receive Termination Control 32**

Simplified Diagram for the Internal Receive and Transmit Termination Mode 32

Receive Terminations 33

Simplified Diagram for T1 in the External Termination Mode (RXTSEL= 0 & TXTSEL= 0) 33

Simplified Diagram for E1 in External Receive Termination Mode (RXTSEL= 0) and Internal Trans-

mit Termination Mode (TXTEL= 1) 34

TRANSMITTER (Channels 0 - 7) 34

**Transmit Termination Mode 34**

Termination Select Control 34

External Transmit Termination Mode 34

**Transmit Terminations 35**

35

35

**REDUNDANCY APPLICATIONS 35**

TYPICAL REDUNDANCY SCHEMES 36

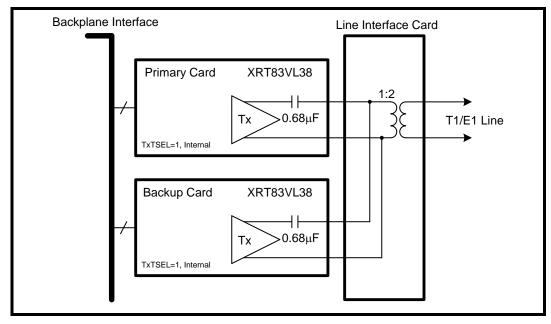

Simplified Block Diagram of the Transmit Section for 1:1 & 1+1 Redundancy 37

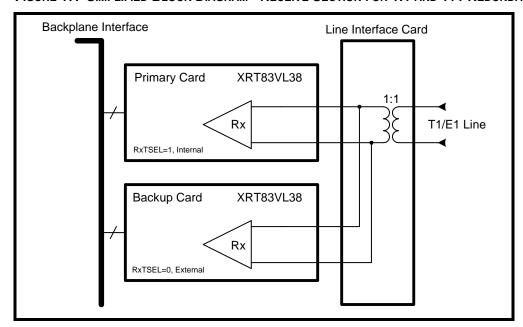

Simplified Block Diagram - Receive Section for 1:1 and 1+1 Redundancy 37

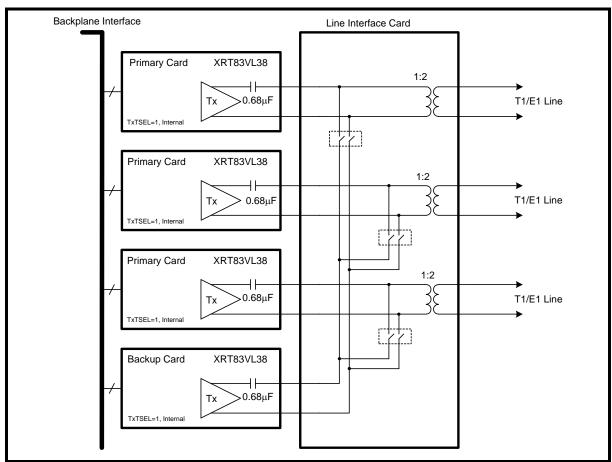

Simplified Block Diagram - Transmit Section for N+1 Redundancy 38

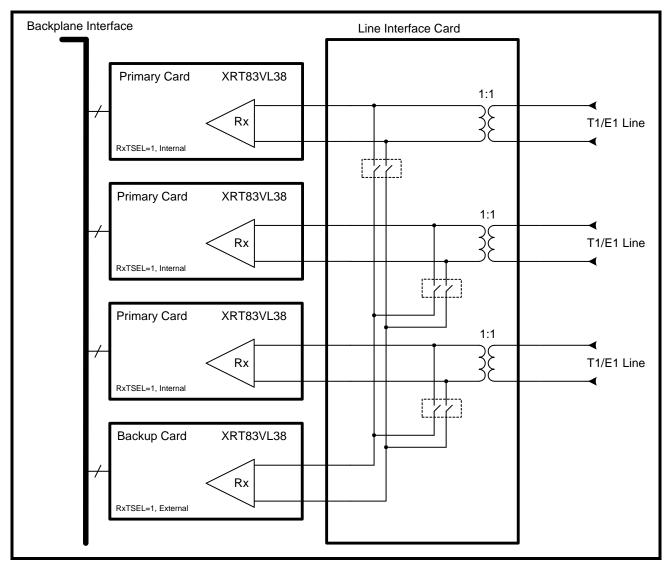

Simplified Block Diagram - Receive Section for N+1 Redundancy 39

Pattern Transmit and Detect Function 40

Pattern transmission control 40

Transmit All Ones (TAOS) 40

Network Loop Code Detection and Transmission 40

Loop-Code Detection Control 40

Transmit and Detect Quasi-Random Signal Source (TDORSS) 41

Loop-Back Modes 42

Loop-back control in Hardware mode 42

Loop-back control in Host mode 42

Local Analog Loop-Back (ALOOP) 42

Local Analog Loop-back signal flow 42

Remote Loop-Back (RLOOP) 43

Remote Loop-back mode with jitter attenuator selected in receive path 43

Remote Loop-back mode with jitter attenuator selected in Transmit path 43

Digital Loop-Back (DLOOP) 44

Digital Loop-back mode with jitter attenuator selected in Transmit path 44

Dual Loop-Back 44

Signal flow in Dual loop-back mode 44

MICROPROCESSOR Parallel INTERFACE 45

Microprocessor interface signal description 45

Microprocessor Register Tables 46

Microprocessor Register Address 46

Microprocessor Register Bit Description 46

Microprocessor Register Descriptions 50

Microprocessor Register #0, Bit Description 50

Microprocessor Register #1, Bit Description 51

Microprocessor Register #2, Bit Description 53

Microprocessor Register #3, Bit Description 55

Microprocessor Register #4, Bit Description 56

Microprocessor Register #5, Bit Description 58

Microprocessor Register #6, Bit Description 60

Microprocessor Register #7, Bit Description 61

Microprocessor Register #8, Bit Description 62

Microprocessor Register #9, Bit Description 62

Microprocessor Register #10, Bit Description 63

Microprocessor Register #11, Bit Description 63

Microprocessor Register #12, Bit Description 64

Microprocessor Register #13, Bit Description 64

Microprocessor Register #14, Bit Description 65

Microprocessor Register #15, Bit Description 65

Microprocessor Register #128, Bit Description 66

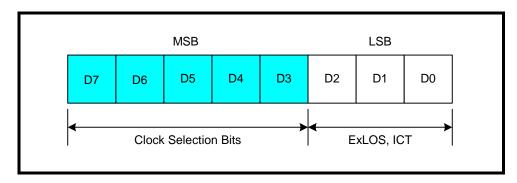

clock select register 67

Register 0x81h Sub Registers 67

Microprocessor Register #129, Bit Description 67

Microprocessor Register #130, Bit Description 68

Microprocessor Register #131, Bit Description 69

Microprocessor Register #192, Bit Description 70

**ELECTRICAL CHARACTERISTICS 71**

Absolute Maximum Ratings 71

DC Digital Input and Output Electrical Characteristics 71

XRT83VL38 Power Consumption 71

E1 Receiver Electrical Characteristics 72

T1 Receiver Electrical Characteristics 73

E1 Transmit Return Loss Requirement 73

E1 Transmitter Electrical Characteristics 74

T1 Transmitter Electrical Characteristics 74

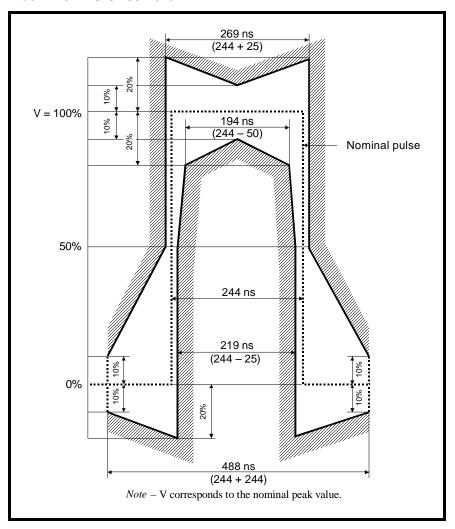

ITU G.703 Pulse Template 75

Transmit Pulse Mask Specification 75

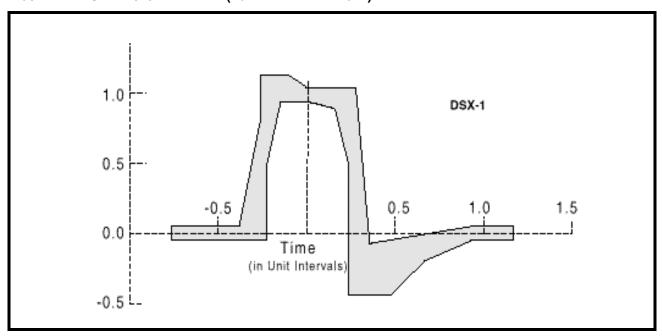

DSX-1 Pulse Template (normalized amplitude) 76

DSX1 Interface Isolated pulse mask and corner points 76

AC Electrical Characteristics 77

Transmit Clock and Input Data Timing 77

Receive Clock and Output Data Timing 78

Microprocessor interface 78

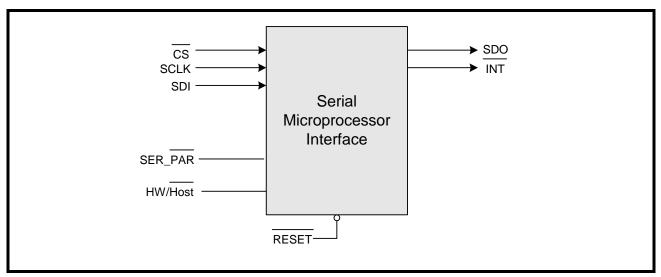

Serial Microprocessor Interface Block 78

Simplified Block Diagram of the Serial Microprocessor Interface 78

Serial Timing Information 78

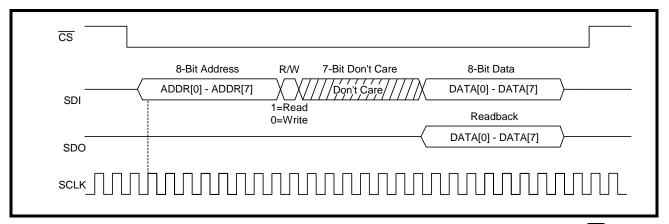

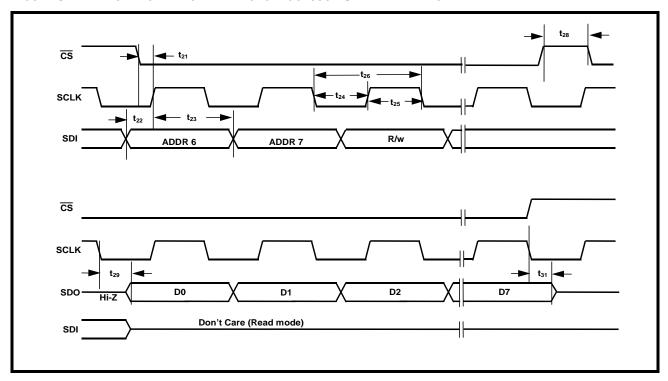

Timing Diagram for the Serial Microprocessor Interface 79

24-Bit Serial Data Input Descritption 79

ADDR[7:0] (SCLK1 - SCLK8) 79

R/W (SCLK9) 79

## XRT83VL38

# WWW.DOCTAL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

REV. 1.0.0

Dummy Bits (SCLK10 - SCLK16) 79

DATA[7:0] (SCLK17 - SCLK24) 79

8-Bit Serial Data Output Description 79

Timing Diagram for the Microprocessor Serial Interface 80

Microprocessor Serial Interface Timings ( TA = 250C,  $VDD=3.3V\pm5\%$  and load = 10pF) 80

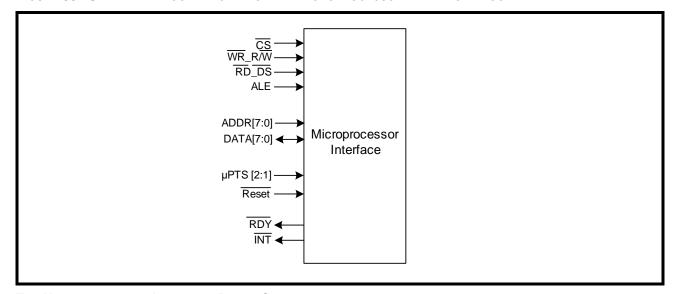

Parallel Microprocessor Interface Block 80

Selecting the Microprocessor Interface Mode 81

Simplified Block Diagram of the Microprocessor Interface Block 81

The Microprocessor Interface Block Signals 81

XRT83VSH38 Microprocessor Interface Signals that exhibit constant roles in both Intel and Motorola

Modes 82

Intel mode: Microprocessor Interface Signals 82

Motorola Mode: Microprocessor Interface Signals 82

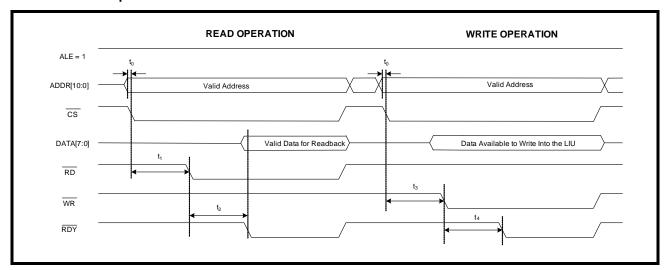

Intel Mode Programmed I/O Access (Asynchronous) 83

Intel µP Interface Signals During Programmed I/O Read and Write Operations 84

Intel Microprocessor Interface Timing Specifications 84

Motorola Mode Programmed I/O Access (Asynchronous) 84

Motorola 68K µP Interface Signals During Programmed I/O Read and Write Operations 85

Motorola 68K Microprocessor Interface Timing Specifications 86

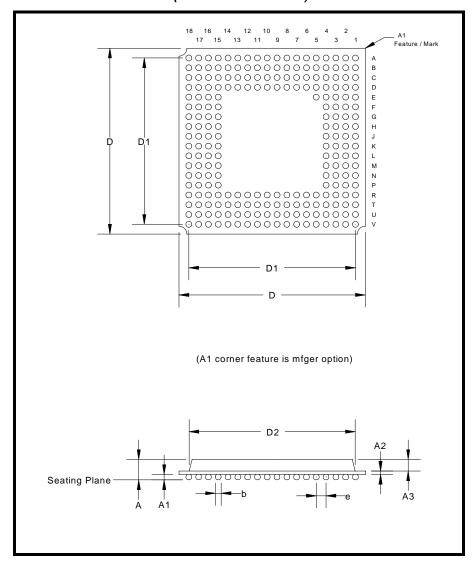

Package dimensions 87

225 Ball Plastic Ball Grid Array (Bottom View) 87

(19.0 x 19.0 x 1.0mm) 87

**ORDERING INFORMATION 88**

**REVISIONS 88**

# PIN DESCRIPTION BY FUNCTION

# **RECEIVE SECTIONS**

| SIGNAL NAME | LEAD# | Түре | DESCRIPTION                                                                                                                                                                                                           |

|-------------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RxON        | K16   | I    | Receiver On - Harware Mode                                                                                                                                                                                            |

|             |       |      | Writing a "1" to this pin in <b>Hardware</b> mode turns on the Receive Sections of all channels. Writing a "0" shuts off the Receiver Sections of all channels.                                                       |

| RLOS_0      | C3    | 0    | Receiver Loss of Signal for Channel_ 0:                                                                                                                                                                               |

|             |       |      | This output signal goes "High" for at least one RCLK_0 cycle to indicate loss of signal at the receive 0 input. RLOS will remain "High" for the entire duration of the Loss of Signal detected by the receiver logic. |

|             |       |      | SEE"RECEIVER LOSS OF SIGNAL (RLOS)" ON PAGE 24.                                                                                                                                                                       |

| RLOS_1      | H4    |      | Receiver Loss of Signal for Channel _1                                                                                                                                                                                |

| RLOS_2      | H15   |      | Receiver Loss of Signal for Channel _2                                                                                                                                                                                |

| RLOS_3      | A16   |      | Receiver Loss of Signal for Channel _3                                                                                                                                                                                |

| RLOS_4      | V3    |      | Receiver Loss of Signal for Channel _4                                                                                                                                                                                |

| RLOS_5      | L2    |      | Receiver Loss of Signal for Channel_ 5                                                                                                                                                                                |

| RLOS_6      | J15   |      | Receiver Loss of Signal for Channel _6                                                                                                                                                                                |

| RLOS_7      | T15   |      | Receiver Loss of Signal for Channel _7                                                                                                                                                                                |

| RCLK_0      | В3    | 0    | Receiver Clock Output for Channel _0                                                                                                                                                                                  |

| RCLK_1      | Н3    |      | Receiver Clock Output for Channel _1                                                                                                                                                                                  |

| RCLK_2      | H16   |      | Receiver Clock Output for Channel _2                                                                                                                                                                                  |

| RCLK_3      | A17   |      | Receiver Clock Output for Channel _3                                                                                                                                                                                  |

| RCLK_4      | U3    |      | Receiver Clock Output for Channel _4                                                                                                                                                                                  |

| RCLK_5      | L3    |      | Receiver Clock Output for Channel _5                                                                                                                                                                                  |

| RCLK_6      | M15   |      | Receiver Clock Output for Channel _6                                                                                                                                                                                  |

| RCLK_7      | U16   |      | Receiver Clock Output for Channel _7                                                                                                                                                                                  |

| RNEG_0      | A2    | 0    | Receiver Negative Data Output for Channel_0 - Dual-Rail mode                                                                                                                                                          |

|             |       |      | This signal is the receive negative-rail output data.                                                                                                                                                                 |

| LCV_0       | A2    |      | Line Code Violation Output for Channel_0 - Single-Rail mode                                                                                                                                                           |

|             |       |      | This signal goes "High" for one RCLK_0 cycle to indicate a code violation is detected in the received data of Channel _0. If AMI coding is selected, every bipolar violation                                          |

|             |       |      | received will cause this pin to go "High".                                                                                                                                                                            |

| RNEG_1      | H2    |      | Receiver Negative Data Output for Channel _1                                                                                                                                                                          |

| LCV_1       |       |      | Line Code Violation Output for Channel _1                                                                                                                                                                             |

| RNEG_2      | H18   |      | Receiver Negative Data Output for Channel _2                                                                                                                                                                          |

| LCV_2       |       |      | Line Code Violation Output for Channel _2                                                                                                                                                                             |

| RNEG_3      | B16   |      | Receiver Negative Data Output for Channel _3                                                                                                                                                                          |

| LCV_3       |       |      | Line Code Violation Output for Channel _3                                                                                                                                                                             |

| RNEG_4      | T4    |      | Receiver Negative Data Output for Channel _4                                                                                                                                                                          |

| LCV_4       |       |      | Line Code Violation Output for Channel _4                                                                                                                                                                             |

| RNEG_5      | M4    |      | Receiver Negative Data Output for Channel _5                                                                                                                                                                          |

| LCV_5       |       |      | Line Code Violation Output for Channel _5                                                                                                                                                                             |

| RNEG_6      | M16   |      | Receiver Negative Data Output for Channel _6                                                                                                                                                                          |

| LCV_6       | -     |      | Line Code Violation Output for Channel _6                                                                                                                                                                             |

| RNEG_7      | V17   |      | Receiver Negative Data Output for Channel _7                                                                                                                                                                          |

| LCV_7       |       |      | Line Code Violation Output for Channel _7                                                                                                                                                                             |

| SIGNAL NAME | LEAD# | Түре | DESCRIPTION                                                                      |

|-------------|-------|------|----------------------------------------------------------------------------------|

| RPOS_0      | B2    | 0    | Receiver Positive Data Output for Channel _0 - Dual-Rail mode                    |

|             |       |      | This signal is the receive positive-rail output data sent to the Framer.         |

|             |       |      | Receiver NRZ Data Output for Channel _0 - Single-Rail mode                       |

| RDATA_0     | B2    |      | This signal is the receive output data.                                          |

|             |       |      | Receiver Positive Data Output for Channel _1                                     |

| RPOS_1      | G2    |      | Receiver NRZ Data Output for Channel _1                                          |

| RDATA_1     |       |      | Receiver Positive Data Output for Channel _2                                     |

| RPOS_2      | D15   |      | Receiver NRZ Data Output for Channel _2                                          |

| RDATA_2     |       |      | Receiver Positive Data Output for Channel _3                                     |

| RPOS_3      | B17   |      | Receiver NRZ Data Output for Channel _3                                          |

| RDATA_3     |       |      | Receiver Positive Data Output for Channel _4                                     |

| RPOS_4      | U2    |      | Receiver NRZ Data Output for Channel _4                                          |

| RDATA_4     |       |      | Receiver Positive Data Output for Channel _5                                     |

| RPOS_5      | М3    |      | Receiver NRZ Data Output for Channel _5                                          |

| RDATA_5     |       |      | Receiver Positive Data Output for Channel _6                                     |

| RPOS_6      | L17   |      | Receiver NRZ Data Output for Channel 6                                           |

| RDATA_6     |       |      | Receiver Positive Data Output for Channel _7                                     |

| RPOS_7      | T17   |      | Receiver NRZ Data Output for Channel _7                                          |

| RDATA_7     |       |      |                                                                                  |

| RTIP_0      | C1    | _    | Receiver Differential Tip Input for Channel _0                                   |

|             |       |      | Positive differential receive input from the line                                |

| RTIP_1      | G1    |      | Receiver Differential Tip Input for Channel _1                                   |

| RTIP_2      | G18   |      | Receiver Differential Tip Input for Channel _2                                   |

| RTIP_3      | C18   |      | Receiver Differential Tip Input for Channel _3                                   |

| RTIP_4      | U1    |      | Receiver Differential Tip Input for Channel _4                                   |

| RTIP_5      | L1    |      | Receiver Differential Tip Input for Channel _5                                   |

| RTIP_6      | L18   |      | Receiver Differential Tip Input for Channel _6                                   |

| RTIP_7      | T18   |      | Receiver Differential Tip Input for Channel _7                                   |

| RRING_0     | D1    | I    | Receiver Differential Ring Input for Channel _0                                  |

|             |       |      | Negative differential receive input from the line                                |

| RRING_1     | F1    |      | Receiver Differential Ring Input for Channel _1                                  |

| RRING_2     | F18   |      | Receiver Differential Ring Input for Channel _2                                  |

| RRING_3     | D18   |      | Receiver Differential Ring Input for Channel _3                                  |

| RRING_4     | T1    |      | Receiver Differential Ring Input for Channel _4                                  |

| RRING_5     | M1    |      | Receiver Differential Ring Input for Channel _5                                  |

| RRING_6     | M18   |      | Receiver Differential Ring Input for Channel _6                                  |

| RRING_7     | R18   |      | Receiver Differential Ring Input for Channel _7                                  |

| RXMUTE      | T12   | I    | Receive Data Muting                                                              |

|             |       |      | When a LOS condition occurs, the outputs RPOS_n/RNEG_n will be muted, (forced to |

|             |       |      | ground) to prevent data chattering.                                              |

|             |       |      | Tie this pin "Low" to disable the muting function.  Notes:                       |

|             |       |      | 1. This pin is internally pulled "High" with a $50k\Omega$ resistor.             |

|             |       |      | In <b>Hardware mode</b> , all receive channels share the same RXMUTE control     |

|             |       |      | function.                                                                        |

# www.DataSI**REV.1.0.0**n

# OCTAL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

| SIGNAL NAME      | LEAD#      | Түре |                                                    | DESCRIPTION                                                                                                                                                                                                                                      |                  |                                        |  |  |  |

|------------------|------------|------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------|--|--|--|

| RXRES1<br>RXRES0 | R10<br>V10 | ı    | Receive Extern                                     | Receive External Resistor Control Pins - Hardware mode Receive External Resistor Control Pin 1: Receive External Resistor Control Pin 0: These pins determine the value of the external Receive fixed resistor according to the billowing table: |                  |                                        |  |  |  |

|                  |            |      | ı                                                  | RXRES1                                                                                                                                                                                                                                           | RXRES0           | Required Fixed External<br>RX Resistor |  |  |  |

|                  |            |      |                                                    | 0                                                                                                                                                                                                                                                | 0                | No External Fixed Resistor             |  |  |  |

|                  |            |      |                                                    | 0                                                                                                                                                                                                                                                | 1                | 240Ω                                   |  |  |  |

|                  |            |      |                                                    | 1                                                                                                                                                                                                                                                | 0                | 210Ω                                   |  |  |  |

|                  |            |      |                                                    | 1                                                                                                                                                                                                                                                | 1                | 150Ω                                   |  |  |  |

|                  |            |      | Note: These p                                      | ins are inte                                                                                                                                                                                                                                     | rnally pulled "L | ow" with a 50k $\Omega$ resistor.      |  |  |  |

| RCLKE            | J16        | I    | Receive Clock                                      | Edge - Ha                                                                                                                                                                                                                                        | rdware mode      |                                        |  |  |  |

|                  |            |      |                                                    | Set this pin "High" to sample RPOS_N/RNEG_n on the falling edge of RCLK_n. With this pin tied "Low", output data are updated on the rising edge of RCLK_n.                                                                                       |                  |                                        |  |  |  |

|                  |            |      | Microprocessor Type Select Input pin 1 - Host mode |                                                                                                                                                                                                                                                  |                  |                                        |  |  |  |

| μPTS1            | J16        |      |                                                    | his pin along with µPTS2 (pin 128) is used to select the microprocessor type.  SEE"MICROPROCESSOR TYPE SELECT INPUT PINS - HOST MODE:"  DN PAGE 12.                                                                                              |                  |                                        |  |  |  |

|                  |            |      | <b>Note:</b> This pin                              | is internall                                                                                                                                                                                                                                     | y pulled "Low" v | vith a 50k $\Omega$ resistor.          |  |  |  |

# TRANSMITTER SECTIONS

| SIGNAL NAME | LEAD# | Түре | DESCRIPTION                                                                                                                                                     |

|-------------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCLKE       | L15   | I    | Transmit Clock Edge - Hardware mode                                                                                                                             |

|             |       |      | Set this pin "High" to sample transmit input data on the rising edge of TCLK_n. With this pin tied "Low", input data are sampled on the falling edge of TCLK_n. |

|             |       |      | Microprocessor Type Select Input pin 2 - Host mode                                                                                                              |

| μPTS2       | L15   |      | This pin along with µPTS1 (pin 133) selects the microprocessor type. SEE"MICRO-PROCESSOR TYPE SELECT INPUT PINS - HOST MODE:" ON PAGE 12.                       |

|             |       |      | <b>Note:</b> This pin is internally pulled "Low" with a $50k\Omega$ resistor.                                                                                   |

| TTIP_0      | E3    | 0    | Transmitter Tip Output for Channel _0                                                                                                                           |

|             |       |      | Positive differential transmit output to the line.                                                                                                              |

| TTIP_1      | G4    |      | Transmitter Tip Output for Channel _1                                                                                                                           |

| TTIP_2      | F17   |      | Transmitter Tip Output for Channel _2                                                                                                                           |

| TTIP_3      | C16   |      | Transmitter Tip Output for Channel _3                                                                                                                           |

| TTIP_4      | R2    |      | Transmitter Tip Output for Channel _4                                                                                                                           |

| TTIP_5      | N2    |      | Transmitter Tip Output for Channel _5                                                                                                                           |

| TTIP_6      | N16   |      | Transmitter Tip Output for Channel _6                                                                                                                           |

| TTIP_7      | P16   |      | Transmitter Tip Output for Channel _7                                                                                                                           |

REV. 1.0.0

| SIGNAL NAME | LEAD# | Түре | DESCRIPTION                                                                        |

|-------------|-------|------|------------------------------------------------------------------------------------|

| TRING_0     | E2    | 0    | Transmitter Ring Output for Channel _0                                             |

|             |       |      | Negative differential transmit output to the line.                                 |

| TRING_1     | F3    |      | Transmitter Ring Output for Channel _1                                             |

| TRING_2     | F15   |      | Transmitter Ring Output for Channel _2                                             |

| TRING_3     | E16   |      | Transmitter Ring Output for Channel _3                                             |

| TRING_4     | P2    |      | Transmitter Ring Output for Channel _4                                             |

| TRING_5     | N4    |      | Transmitter Ring Output for Channel _5                                             |

| TRING_6     | R15   |      | Transmitter Ring Output for Channel _6                                             |

| TRING_7     | P17   |      | Transmitter Ring Output for Channel _7                                             |

| TPOS_0      | C5    | I    | Transmitter Positive Data Input for Channel _0 - Dual-Rail mode                    |

|             |       |      | This signal is the positive-rail input data for transmitter 0.                     |

| TDATA_0     |       |      | Transmitter 0 Data Input - Single-Rail mode                                        |

|             |       |      | This pin is used as the NRZ input data for transmitter 0.                          |

| TPOS_1      | A4    |      | Transmitter Positive Data Input for Channel _1                                     |

| TDATA_1     |       |      | Transmitter 1 Data Input                                                           |

| TPOS_2      | B14   |      | Transmitter Positive Data Input for Channel _2                                     |

| TDATA_2     |       |      | Transmitter 2 Data Input                                                           |

| TPOS_3      | D14   |      | Transmitter Positive Data Input for Channel _3                                     |

| TDATA_3     |       |      | Transmitter 3 Data Input                                                           |

| TPOS_4      | V4    |      | Transmitter Positive Data Input for Channel _4                                     |

| TDATA_4     |       |      | Transmitter 4 Data Input                                                           |

| TPOS_5      | U5    |      | Transmitter Positive Data Input for Channel _5                                     |

| TDATA_5     |       |      | Transmitter 5 Data Input                                                           |

| TPOS_6      | V15   |      | Transmitter Positive Data Input for Channel _6                                     |

| TDATA_6     |       |      | Transmitter 6 Data Input                                                           |

| TPOS_7      | T14   |      | Transmitter Positive Data Input for Channel _7                                     |

| TDATA_7     |       |      | Transmitter 7 Data Input                                                           |

|             |       |      | <b>Note:</b> Internally pulled "Low" with a $50k\Omega$ resistor for each channel. |

www.DataSt**REV.1.0.0**

OCTAL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

| SIGNAL NAME | LEAD# | Түре | DESCRIPTION                                                                                                                                          |

|-------------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| TNEG_0      | C4    | I    | Transmitter Negative NRZ Data Input for Channel _0                                                                                                   |

|             |       |      | Dual-Rail mode                                                                                                                                       |

|             |       |      | This signal is the negative-rail input data for transmitter 0.                                                                                       |

|             |       |      | Single-Rail mode                                                                                                                                     |

|             |       |      | This pin can be left unconnected.                                                                                                                    |

| CODES_0     | C4    |      | Coding Select for Channel _0 - Hardware mode and Single-Rail mode                                                                                    |

|             |       |      | Connecting this pin "Low" enables HDB3 in E1 or B8ZS in T1 encoding and decoding for Channel _0. Connecting this pin "High" selects AMI data format. |

| TNEG_1      | B5    |      | Transmitter Negative NRZ Data Input for Channel _1                                                                                                   |

| CODES_1     |       |      | Coding Select for Channel _1                                                                                                                         |

| TNEG_2      | D13   |      | Transmitter Negative NRZ Data Input for Channel _2                                                                                                   |

| CODES_2     |       |      | Coding Select for Channel _2                                                                                                                         |

| TNEG_3      | B15   |      | Transmitter Negative NRZ Data Input for Channel _3                                                                                                   |

| CODES_3     |       |      | Coding Select for Channel _3                                                                                                                         |

| TNEG_4      | U4    |      | Transmitter Negative NRZ Data Input for Channel _4                                                                                                   |

| CODES_4     |       |      | Coding Select for Channel _4                                                                                                                         |

| TNEG_5      | V5    |      | Transmitter Negative NRZ Data Input for Channel _5                                                                                                   |

| CODES_5     |       |      | Coding Select for Channel _5                                                                                                                         |

| TNEG_6      | U14   |      | Transmitter Negative NRZ Data Input for Channel _6                                                                                                   |

| CODES_6     |       |      | Coding Select for Channel _6                                                                                                                         |

| TNEG_7      | R14   |      | Transmitter Negative NRZ Data Input for Channel _7                                                                                                   |

| CODES_7     |       |      | Coding Select for Channel _7                                                                                                                         |

|             |       |      | <b>Note:</b> Internally pulled "Low" with a $50k\Omega$ resistor for each channel.                                                                   |

| TCLK_0      | B4    | I    | Transmitter Clock Input for Channel _0 - Host mode and Hardware mode                                                                                 |

|             |       |      | E1 rate at 2.048MHz ± 50ppm. T1 rate at 1.544MHz ± 32ppm.                                                                                            |

|             |       |      | During normal operation TCLK_0 is used for sampling input data at TPOS_0/                                                                            |

|             |       |      | TDATA_0 and TNEG_0/CODES_0 while MCLK is used as the timing reference for the                                                                        |

|             |       |      | transmit pulse shaping circuit.                                                                                                                      |

|             |       |      | Transmitter Clock Input for Channel _1                                                                                                               |

| TCLK_1      | A3    |      | Transmitter Clock Input for Channel _2                                                                                                               |

| TCLK_2      | A15   |      | Transmitter Clock Input for Channel _3                                                                                                               |

| TCLK_3      | C14   |      | Transmitter Clock Input for Channel _4                                                                                                               |

| TCLK_4      | T3    |      | Transmitter Clock Input for Channel _5                                                                                                               |

| TCLK_5      | T5    |      | Transmitter Clock Input for Channel _6 Transmitter Clock Input for Channel _7                                                                        |

| TCLK_6      | V16   |      | -                                                                                                                                                    |

| TCLK_7      | U15   |      | <b>Note:</b> Internally pulled "Low" with a $50k\Omega$ resistor for all channels.                                                                   |

REV. 1.0.0

| SIGNAL NAME      | LEAD#      | Түре | DESCRIPTION                                                                                                                                                                                                                                                                       |

|------------------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TAOS_0           | D6         | I    | Transmit All Ones for Channel _0 - Hardware mode                                                                                                                                                                                                                                  |

|                  |            |      | Setting this pin "High" enables the transmission of an "All Ones" Pattern from Channel _0. A "Low" level stops the transmission of the "All Ones" Pattern.                                                                                                                        |

|                  |            |      | Transmit All Ones for Channel 1                                                                                                                                                                                                                                                   |

| TAOS_1           | B6         |      | Transmit All Ones for Channel 2                                                                                                                                                                                                                                                   |

| TAOS_1           | A5         |      | Transmit All Ones for Channel _3                                                                                                                                                                                                                                                  |

| TAOS_3           | C6         |      | Transmit All Ones for Channel _4                                                                                                                                                                                                                                                  |

| TAOS 4           | T6         |      | Transmit All Ones for Channel _5                                                                                                                                                                                                                                                  |

| TAOS_5           | U6         |      | Transmit All Ones for Channel _6                                                                                                                                                                                                                                                  |

| TAOS_6           | V6         |      | Transmit All Ones for Channel _7                                                                                                                                                                                                                                                  |

| TAOS_7           | R6         |      | <b>Note:</b> Internally pulled "Low" with a $50k\Omega$ resistor for all channels.                                                                                                                                                                                                |

| TXON_0           | A13        | I    | Transmitter Turn On for Channel _0                                                                                                                                                                                                                                                |

|                  |            |      | Hardware mode                                                                                                                                                                                                                                                                     |

|                  |            |      | Setting this pin "High" turns on the Transmit and Receive Sections of Channel _0. When TXON_0 = "0" then TTIP_0 and TRING_0 driver outputs will be tri-stated.                                                                                                                    |

|                  |            |      | In Host mode                                                                                                                                                                                                                                                                      |

|                  |            |      | The TXON_n bits in the channel control registers turn each channel Transmit and Receive section ON or OFF. However, control of the on/off function can be transferred to the <b>Hardware</b> pins by setting the TXONCNTL bit (bit 7) to "1" in the register at address hex 0x82. |

|                  |            |      | Transmitter Turn On for Channel _1                                                                                                                                                                                                                                                |

|                  |            |      | Transmitter Turn On for Channel _2                                                                                                                                                                                                                                                |

|                  |            |      | Transmitter Turn On for Channel _3                                                                                                                                                                                                                                                |

|                  |            |      | Transmitter Turn On for Channel _4                                                                                                                                                                                                                                                |

|                  | D.10       |      | Transmitter Turn On for Channel _5                                                                                                                                                                                                                                                |

| TXON_1           | D12        |      | Transmitter Turn On for Channel _6                                                                                                                                                                                                                                                |

| TXON_2           | C12<br>B12 |      | Transmitter Turn On for Channel _7                                                                                                                                                                                                                                                |

| TXON_3<br>TXON_4 | V13        |      | <b>Note:</b> Internally pulled "Low" with a $50k\Omega$ resistor for all channels.                                                                                                                                                                                                |

| TXON_4 TXON_5    | U13        |      |                                                                                                                                                                                                                                                                                   |

| TXON_5           | R12        |      |                                                                                                                                                                                                                                                                                   |

| TXON_7           | R13        |      |                                                                                                                                                                                                                                                                                   |

# www.DataSi**REV.11.0.0**n

# **MICROPROCESSOR INTERFACE**

| SIGNAL NAME | LEAD#    | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                      |

|-------------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HW_HOST     | T10      | I    | Mode Control Input This pin selects Hardware or Host mode. Leave this pin unconnected or tie "High" to select Hardware mode. For Host mode, this pin must be tied "Low".  Note: Internally pulled "High" with a 50kΩ resistor.                                                                                                   |

| WR_R/W      | D7       | ı    | Write Input (Read/Write) - Host mode: Intel bus timing: A "Low" pulse on WR selects a write operation when CS pin is "Low".  Motorola bus timing: A "High" pulse on R/W selects a read operation and a "Low" pulse on R/W selects a write operation when CS is "Low".                                                            |

| EQC0        | D7       |      | Equalizer Control Input pin 0 - Hardware mode  Pins EQC0, EQC1, EQC2, EQC3 and EQC4 select the Receive Equalizer and  Transmitter Line Build Out. SEE"RECEIVE EQUALIZER CONTROL AND  TRANSMIT LINE BUILD-OUT SETTINGS" ON PAGE 30.  Note: Internally pulled "Low" with a 50kΩ resistor.                                          |

| RD_DS       | C7       | I    | Read Input (Data Strobe) - Host mode Intel bus timing: A "Low" pulse on RD selects a read operation when the CS pin is "Low".  Motorola bus timing: A "Low" pulse on DS indicates a read or write operation when the CS pin is "Low".                                                                                            |

| EQC1        | C7       |      | Equalizer Control Input pin 1 - Hardware mode  Pins EQC0, EQC1, EQC2, EQC3 and EQC4 select the Receive Equalizer and  Transmitter Line Build Out. SEE"RECEIVE EQUALIZER CONTROL AND  TRANSMIT LINE BUILD-OUT SETTINGS" ON PAGE 30.  Note: Internally pulled "Low" with a 50kΩ resistor.                                          |

| ALE_AS      | A7       | I    | Address Latch Input (Address Strobe) - Host mode Intel bus timing: The address inputs are latched into the internal register on the falling edge of ALE.  Motorola bus timing: The address inputs are latched into the internal register on the falling edge of AS.                                                              |

| EQC2        | A7       |      | Equalizer Control Input pin 2 - Hardware mode Pins EQC0, EQC1, EQC2, EQC3 and EQC4 select the Receive Equalizer and Transmitter Line Build Out. SEE"RECEIVE EQUALIZER CONTROL AND TRANSMIT LINE BUILD-OUT SETTINGS" ON PAGE 30.  Note: Internally pulled "Low" with a 50kΩ resistor.                                             |

| CS<br>EQC3  | B7<br>B7 | I    | Chip Select Input - Host mode: This signal must be "Low" in order to access the parallel port.  Equalizer Control Input pin 3 - Hardware mode: Pins EQC0, EQC1, EQC2, EQC3 and EQC4 select the Receive Equalizer and Transmitter Line Build Out. SEE"RECEIVE EQUALIZER CONTROL AND TRANSMIT LINE BUILD-OUT SETTINGS" ON PAGE 30. |

|             |          |      | <b>NOTE:</b> Internally pulled "Low" with a $50k\Omega$ resistor.                                                                                                                                                                                                                                                                |

OCTAL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

| SIGNAL NAME                                                    | LEAD#                                  | Түре |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                  | DESCRIPTION                                                                                                                                                       |  |  |

|----------------------------------------------------------------|----------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RDY_DTACK                                                      | A6<br>A6                               | I    | Ready Output (Data Transfer Acknowledge Output) - Host mode Intel bus timing: RDY is asserted "High" to indicate the device has completed a read or write operation.  Motorola bus timing: DTACK is asserted "Low" to indicate the device has completed a read or write cycle.  Equalizer Control Input pin 4 - Hardware mode  Pins EQC0, EQC1, EQC2, EQC3 and EQC4 select the Receive Equalizer and Transmitter Line Build Out. SEE"RECEIVE EQUALIZER CONTROL AND TRANSMIT LINE BUILD-OUT SETTINGS" ON PAGE 30.  Note: Internally pulled "Low" with a 50kΩ resistor. |                                                                  |                                                                                                                                                                   |  |  |

| μPTS1<br>μPTS2                                                 | J16<br>L15                             | I    | Microprocesso<br>Microprocesso                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | r Type Select<br>r Type Select                                   | Input Bit 2                                                                                                                                                       |  |  |

|                                                                |                                        |      | μPTS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | μPTS1                                                            | μP Type                                                                                                                                                           |  |  |

|                                                                |                                        |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                | Intel 8051 Asynchronous                                                                                                                                           |  |  |

|                                                                |                                        |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                | Motorola Asynchronous                                                                                                                                             |  |  |

|                                                                |                                        |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                | Power PC Synchronous                                                                                                                                              |  |  |

|                                                                |                                        |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                | MPC8xx Motorola Synchronous                                                                                                                                       |  |  |

| RCLKE<br>TCLKE                                                 | J16<br>L15                             |      | Transmit Clock SEE"TRANSM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | E CLOCK E Edge - Hard                                            | DGE - HARDWARE MODE" ON PAGE 7.                                                                                                                                   |  |  |

| D[7] D[6] D[5] D[4] D[3] D[2] D[1] D[0]/SDO                    | T7<br>U7<br>V8<br>V9<br>U8<br>U9<br>R7 | I/O  | Data Bus[7] Data Bus[6] Data Bus[5] Data Bus[4] Data Bus[3] Data Bus[2] Data Bus[1] Data Bus[0] if Sor Serial Data I  Loop-back Cor                                                                                                                                                                                                                                                                                                                                                                                                                                   | SER_PAR = 0<br>nput if SER_F<br>ntrol Pins, Bit<br>173-180 contr | Data Bus Pins - Host mode  PAR = 1  s [1:0] Channel_[7:4] - Hardware Mode ol which Loop-Back mode is selected per channel. ROL PINS, BITS [1:0] CHANNEL_[7:0]" ON |  |  |

| LOOP0_4<br>LOOP1_5<br>LOOP1_6<br>LOOP0_6<br>LOOP1_7<br>LOOP0_7 | V7<br>V8<br>V9<br>U8<br>U9<br>R7       |      | PAGE 17.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                  | with a 50k $\Omega$ resistor for all channels.                                                                                                                    |  |  |

www.DataSt**REV**.1.0.0

# OCTAL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

| SIGNAL NAME | LEAD# | Түре | DESCRIPTION                                                                                                                                                                                                                                             |

|-------------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|