## STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER

JANUARY 2006 REV. P1.0.8

## GENERAL DESCRIPTION

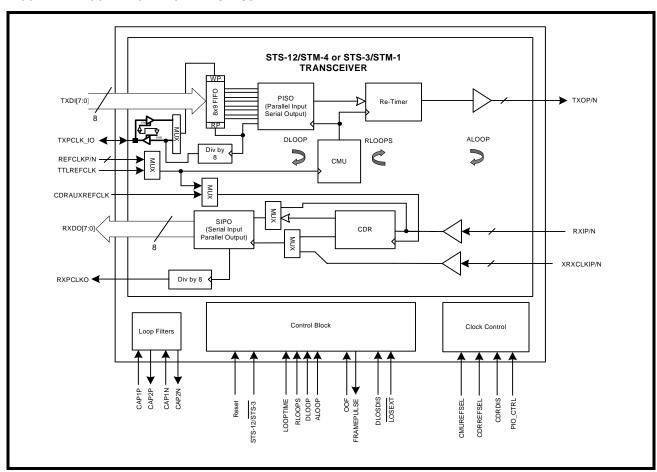

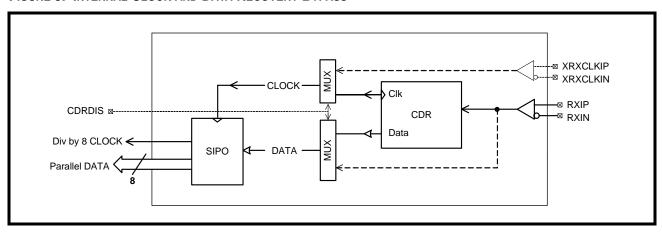

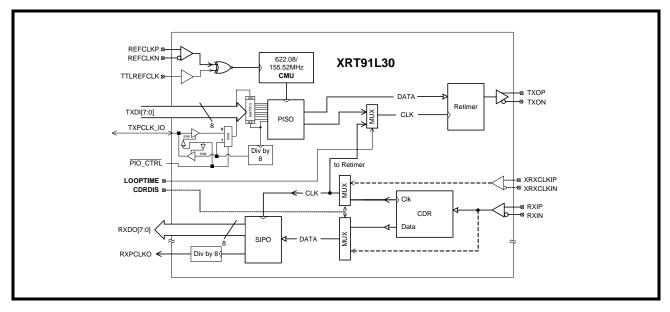

The XRT91L30 is a fully integrated SONET/SDH transceiver for SONET/SDH 622.08 Mbps STS-12/ STM-4 or 155.52 Mbps STS-3/STM-1 applications. The transceiver includes an on-chip Clock Multiplier Unit (CMU), which uses a high frequency Phase-Locked Loop (PLL) to generate the high-speed transmit serial clock from a slower external clock reference. It also provides Clock and Data Recovery (CDR) function by synchronizing its on-chip Voltage Controlled Oscillator (VCO) to the incoming serial data stream. The internal CDR unit can be disabled and bypassed in lieu of an externally recovered received clock from the optical module. Either the internally recovered clock or the externally recovered clock can be used for loop timing applications. The chip provides serial-to-parallel and parallel-to-serial converters using an 8-bit wide LVTTL system interface in both receive and transmit directions. The transmit section includes an option to accept a parallel clock signal from the framer/mapper to synchronize the transmit section timing. The device can internally monitor Loss of Signal (LOS) condition and automatically mute received data upon LOS. An on-chip SONET/SDH frame byte and boundary detector and frame pulse generator offers the ability recover SONET/SDH framing and to byte align the receive serial data stream into the 8-bit parallel bus.

## **APPLICATIONS**

- SONET/SDH-based Transmission Systems

- Add/Drop Multiplexers

- Cross Connect Equipment

- ATM and Multi-Service Switches, Routers and Switch/Routers

- DSLAMS

- SONET/SDH Test Equipment

- DWDM Termination Equipment

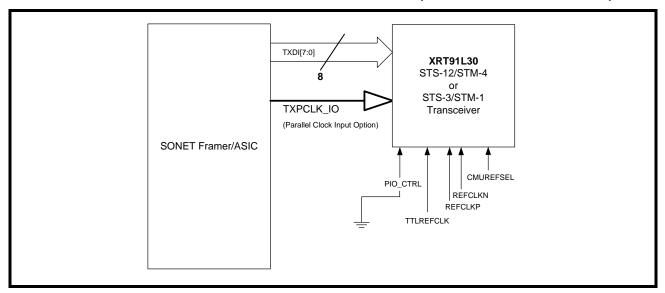

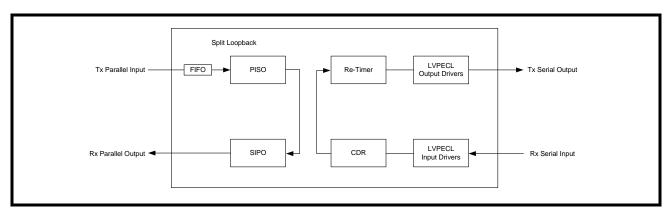

FIGURE 1. BLOCK DIAGRAM OF XRT91L30

#### **FEATURES**

- Targeted for SONET STS-12/STS-3 and SDH STM-4/STM-1 Applications

- Selectable full duplex operation between STS-12/STM-4 standard rate of 622.08 Mbps or STS-3/STM-1 155.52 Mbps

- Single-chip fully integrated solution containing parallel-to-serial converter, clock multiplier unit (CMU), serialto-parallel converter, clock data recovery (CDR) functions, and a SONET/SDH frame and byte boundary detection circuit

- Ability to disable and bypass onchip CDR for external based received reference clock recovery thru Differential LVPECL input pins XRXCLKIP/N

- 8-bit LVTTL parallel data bus paths running at 77.76 Mbps in STS-12/STM-4 or 19.44 Mbps in STS-3/STM-1 mode of operation

- Uses Differential LVPECL or Single-Ended LVTTL CMU reference clock frequencies of either 19.44 MHz or 77.76 MHz for both STS-12/STM-1 or STS-3/STM-1 operations

- Optional use of 77.76 MHz Single-Ended LVTTL input for independent CDR reference clock operation

- Able to Detect and Recover SONET/SDH frame boundary and byte align received data on the parallel bus

- Diagnostics features include LOS monitoring and automatic received data mute upon LOS

- Provides Local, Remote and Split Loop-Back modes as well as Loop Timing mode

- Optional flexibility to re-configure the transmit parallel bus clock output to a clock input and accept timing signal from the framer/mapper device to permit the framer/mapper device time domain to be synchronized with the transceiver transmit timing.

- Meets Telcordia, ANSI and ITU-T G.783 and G.825 SDH jitter requirements including T1.105.03 2002 SONET Jitter Tolerance specification, Bellcore TR-NWT-000253 and GR-253-CORE, GR-253 ILR SONET Jitter specifications.

- Complies with ANSI/TIA/EIA-644 and IEEE P1596.3 3.3V LVDS standard, 3.3V LVPECL, and JESD 8-B LVTTL and LVCMOS standard.

- Operates at 3.3V Core with 3.3V I/O

- Less than 660mW in STS-3/STM-1 mode or 800mW in STS-12/STM-4 mode Typical Power Dissipation

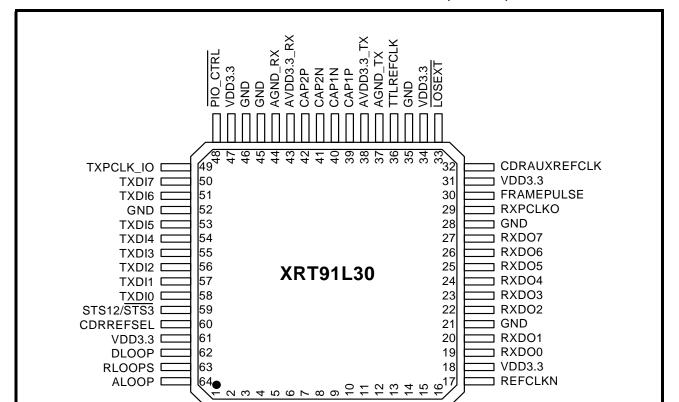

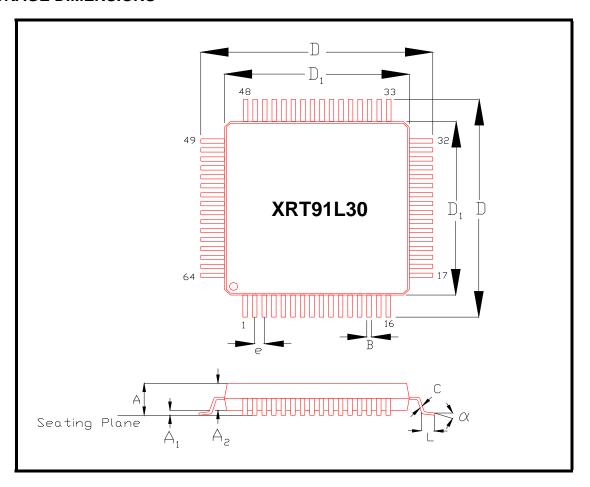

- Package: 10 x 10 x 2.0 mm 64-pin QFP

FIGURE 2. 64 QFP PIN OUT OF THE XRT91L30 (TOP VIEW)

## **ORDERING INFORMATION**

DLOSDIS E XRXCLKIP E XRXCLKIN E VDD\_PECL

RXIP I RXIN I VDD3.3 [

REFCLKP

OOF CORDIS

LOOPTIME C CMUFREQSEL C VDD\_PECL C TXOP C

| PART NUMBER | PACKAGE         | OPERATING TEMPERATURE RANGE |

|-------------|-----------------|-----------------------------|

| XRT91L30IQ  | 64 Pin Lead QFP | -40°C to +85°C              |

## **TABLE OF CONTENTS**

| GENERAL DESCRIPTION                                                              | 1  |

|----------------------------------------------------------------------------------|----|

| APPLICATIONS                                                                     |    |

| FIGURE 1. BLOCK DIAGRAM OF XRT91L30                                              |    |

| FEATURES                                                                         |    |

| FIGURE 2. 64 QFP PIN OUT OF THE XRT91L30 (TOP VIEW)                              | 3  |

| ORDERING INFORMATION                                                             | 3  |

| TABLE OF CONTENTS                                                                |    |

| PIN DESCRIPTIONS                                                                 |    |

|                                                                                  |    |

| HARDWARE CONTROL                                                                 |    |

| TRANSMITTER SECTION                                                              |    |

| RECEIVER SECTION                                                                 |    |

| Power and Ground                                                                 |    |

| 1.0 FUNCTIONAL DESCRIPTION                                                       |    |

| 1.1 STS-12/STM-4 AND STS-3/STM-1 MODE OF OPERATION                               |    |

| 1.1 S15-12/S1M-4 AND S15-3/S1M-1 MODE OF OPERATION                               |    |

| TABLE 1: CMU REFERENCE FOR CLOCK MULTIPLIER (SYNTHESIZER) UNIT                   |    |

| 1.3 DATA LATENCY                                                                 |    |

| TABLE 2: DATA INGRESS TO DATA EGRESS LATENCY                                     |    |

| 2.0 RECEIVE SECTION                                                              |    |

| 2.1 RECEIVE SERIAL INPUT                                                         |    |

| FIGURE 3. RECEIVE SERIAL INPUT INTERFACE BLOCK                                   |    |

| 2.2 RECIEVE SERIAL DATA INPUT TIMING                                             |    |

| FIGURE 4. RECEIVE HIGH-SPEED SERIAL DATA INPUT TIMING DIAGRAM                    |    |

| TABLE 3: RECEIVE HIGH-SPEED SERIAL DATA INPUT TIMING (STS-12/STM-4 OPERATION)    |    |

| 2.3 RECEIVE CLOCK AND DATA RECOVERY                                              |    |

| TABLE 5: CLOCK DATA RECOVERY UNIT REFERENCE CLOCK SETTINGS                       |    |

| TABLE 6: CLOCK AND DATA RECOVERY UNIT PERFORMANCE                                |    |

| 2.3.1 INTERNAL CLOCK AND DATA RECOVERY BYPASS                                    |    |

| FIGURE 5. INTERNAL CLOCK AND DATA RECOVERY BYPASS                                | 16 |

| 2.4 EXTERNAL RECEIVE LOOP FILTER CAPACITORS                                      |    |

| FIGURE 6. EXTERNAL LOOP FILTERS                                                  |    |

| 2.5 LOSS OF SIGNAL                                                               |    |

| 2.6 SONET FRAME BOUNDARY DETECTION AND BYTE ALIGNMENT RECOVERY                   | 18 |

| 2.7 RECEIVE SERIAL INPUT TO PARALLEL OUTPUT (SIPO)                               |    |

| Figure 8. Simplified Block Diagram of SIPO                                       |    |

| 2.8 RECEIVE PARALLEL OUTPUT INTERFACE                                            | 19 |

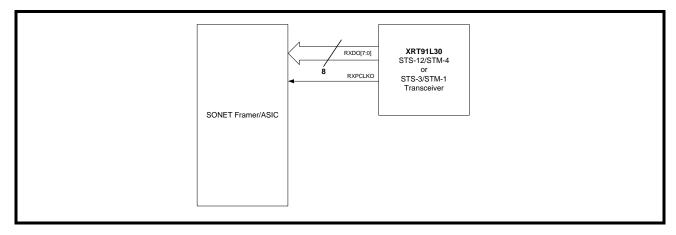

| FIGURE 9. RECEIVE PARALLEL OUTPUT INTERFACE BLOCK                                |    |

| 2.9 DISABLE PARALLEL RECEIVE DATA OUTPUT UPON LOS                                |    |

| 2.10 RECEIVE PARALLEL DATA OUTPUT TIMING                                         |    |

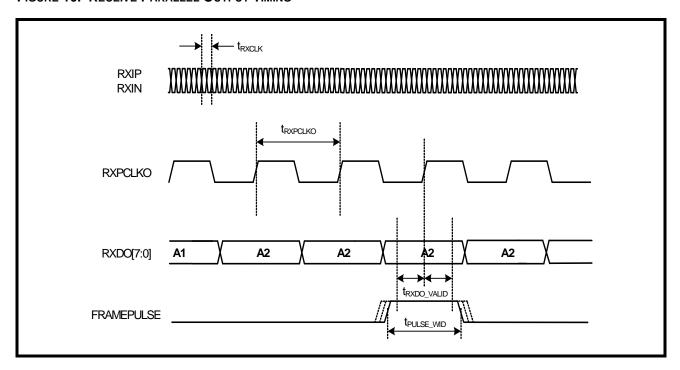

| FIGURE 10. RECEIVE PARALLEL OUTPUT TIMING                                        |    |

| TABLE 7: RECEIVE PARALLEL DATA OUTPUT TIMING (STS-12/STM-4 OPERATION)            |    |

| TABLE 9: PECL AND TTL RECEIVE OUTPUTS TIMING SPECIFICATION                       |    |

| 3.0 TRANSMIT SECTION                                                             |    |

| 3.1 TRANSMIT PARALLEL INPUT INTERFACE                                            |    |

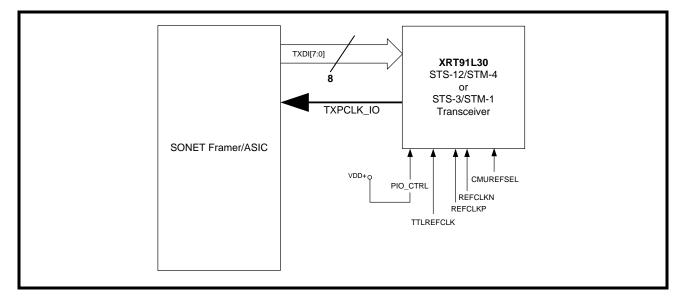

| FIGURE 11. TRANSMIT PARALLEL INPUT INTERFACE BLOCK                               |    |

| 3.2 TRANSMIT PARALLEL DATA INPUT TIMING                                          | -  |

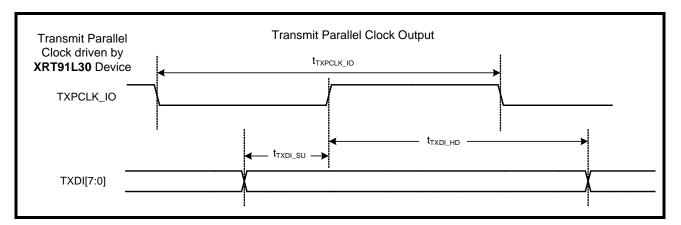

| FIGURE 12. TRANSMIT PARALLEL INPUT TIMING                                        |    |

| TABLE 10: TRANSMIT PARALLEL DATA INPUT TIMING (STS-12/STM-4 OPERATION)           |    |

| TABLE 11: TRANSMIT PARALLEL DATA INPUT TIMING (STS-3/STM-1 OPERATION)            |    |

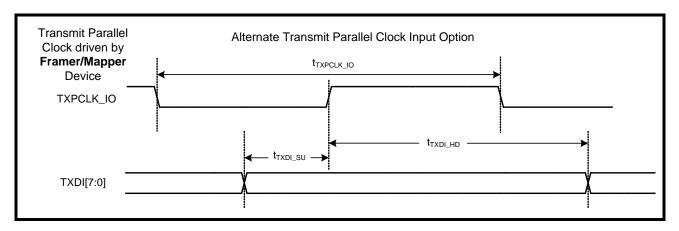

| FIGURE 13. ALTERNATE TRANSMIT PARALLEL BUS CLOCK INPUT OPTION                    |    |

| 3.4 ALTERNATE TRANSMIT PARALLEL DATA INPUT TIMING                                |    |

| FIGURE 14. ALTERNATE TRANSMIT PARALLEL INPUT TIMING                              |    |

| Table 12: Alternate Transmit Parallel Data Input Timing (STS-12/STM-4 Operation) |    |

| TABLE 13: ALTERNATE TRANSMIT PARALLEL DATA INPUT TIMING (STS-3/STM-1 OPERATION). | 25 |

# **EXAR**STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER

|     | 3.5 TRANSMIT PARALLEL INPUT TO SERIAL OUTPUT (PISO)                                                         | . 25     |

|-----|-------------------------------------------------------------------------------------------------------------|----------|

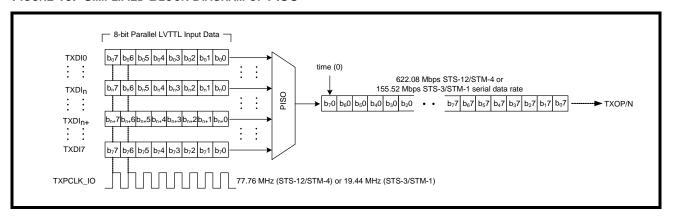

|     | FIGURE 15. SIMPLIFIED BLOCK DIAGRAM OF PISO                                                                 | 25       |

|     | 3.6 CLOCK MULTIPLIER UNIT (CMU) AND RE-TIMER                                                                | . 26     |

|     | Table 14: Clock Multiplier Unit Performance                                                                 | 26       |

|     | 3.7 LOOP TIMING AND CLOCK CONTROL                                                                           |          |

|     | TABLE 15: LOOP TIMING AND CLOCK RECOVERY CONFIGURATIONS                                                     |          |

|     | Figure 16. Loop Timing Mode Using Internal CDR or an External Recovered Clock                               | 28       |

|     | 3.8 TRANSMIT SERIAL OUTPUT CONTROL                                                                          |          |

|     | FIGURE 17. TRANSMIT SERIAL OUTPUT INTERFACE BLOCK                                                           |          |

| 1.0 | DIAGNOSTIC FEATURES                                                                                         |          |

|     | 4.1 SERIAL REMOTE LOOPBACK                                                                                  | . 29     |

|     | FIGURE 18. SERIAL REMOTE LOOPBACK                                                                           |          |

|     | 4.2 DIGITAL LOCAL LOOPBACK                                                                                  |          |

|     | Figure 19. Digital Local Loopback                                                                           |          |

|     | 4.3 ANALOG LOCAL LOOPBACK                                                                                   |          |

|     | FIGURE 20. ANALOG LOCAL LOOPBACK                                                                            |          |

|     | 4.4 SPLIT LOOPBACK                                                                                          |          |

|     | FIGURE 21. SPLIT LOOPBACK                                                                                   |          |

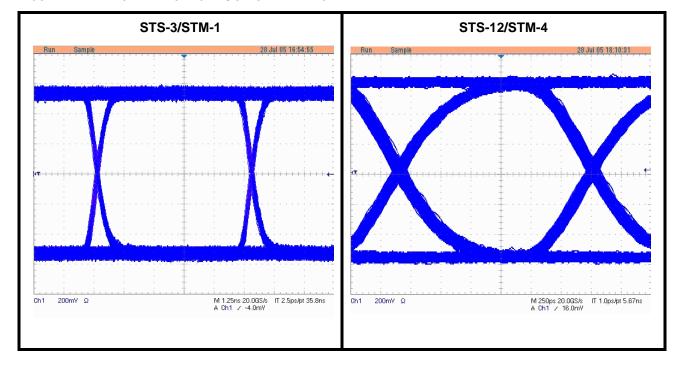

|     | 4.5 EYE DIAGRAM                                                                                             |          |

|     | FIGURE 22. TRANSMIT ELECTRICAL OUTPUT EYE DIAGRAM                                                           |          |

|     | 4.6 SONET JITTER REQUIREMENTS                                                                               |          |

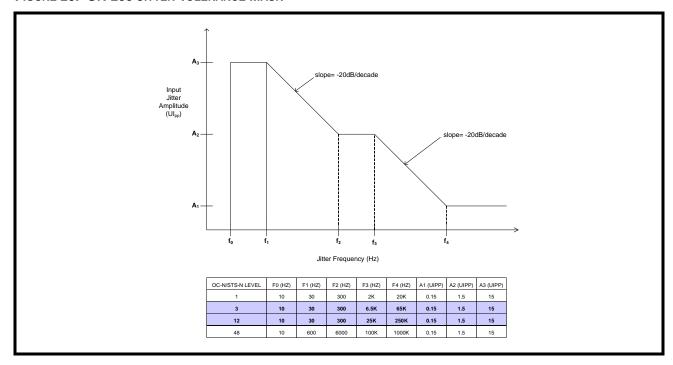

|     | 4.6.1 JITTER TOLERANCE:                                                                                     |          |

|     | FIGURE 23. GR-253 JITTER TOLERANCE MASK                                                                     |          |

|     | FIGURE 24. XRT91L30 MEASURED JITTER TOLERANCE                                                               |          |

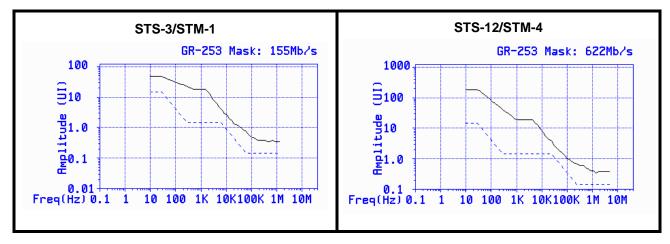

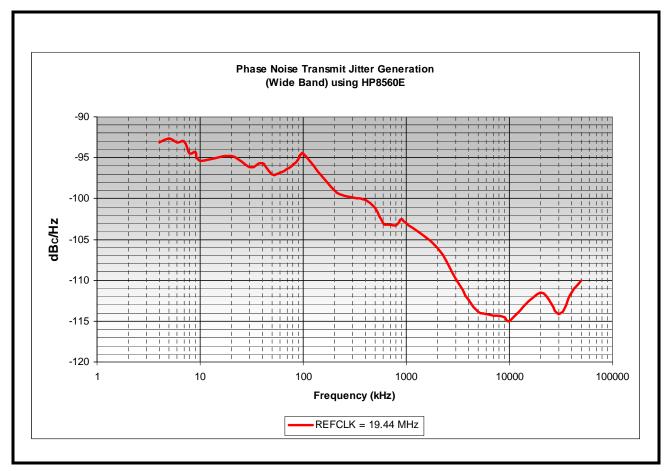

|     | 4.6.2 JITTER GENERATION                                                                                     |          |

|     | FIGURE 25. XRT91L30 MEASURED ELECTRICAL PHASE NOISE TRANSMIT JITTER GENERATION AT 622.08 MBPS STS-12/STM4 U |          |

| - ^ | '1010' OUTPUT PATTERN                                                                                       | 33<br>24 |

|     |                                                                                                             |          |

|     | ABSOLUTE MAXIMUM RATINGS                                                                                    |          |

|     | ABSOLUTE MAXIMUM POWER AND INPUT/OUTPUT RATINGS                                                             | _        |

| I   | POWER AND CURRENT DC ELECTRICAL CHARACTERISTICS                                                             | . 34     |

|     |                                                                                                             | . 34     |

| I   | LVPECL AND LVTTL LOGIC SIGNAL DC ELECTRICAL CHARACTERISTICS                                                 |          |

| -   | ORDERING INFORMATION                                                                                        |          |

| D / | ACKAGE DIMENSIONS                                                                                           |          |

|     |                                                                                                             |          |

| - 1 | REVISION HISTORY                                                                                            | .37      |

## **PIN DESCRIPTIONS**

## HARDWARE CONTROL

| NAME       | LEVEL | Түре | Pin |                                                                     |                                           | DESCRIPTION                                         |                                                                                      |

|------------|-------|------|-----|---------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------|

| RESET      | LVTTL | ı    | 1   | Master Reset Active "High." machines are "Low" = Norm "High" = Mast | When this set to their al Operatio        | default state.<br>n                                 | " , the internal state                                                               |

| STS12/STS3 | LVTTL | I    | 59  | Data Rate Se<br>Selects SONE<br>"Low" = STS-3<br>"High" = STS-      | ET/SDH trai<br>3/STM-1 15                 | •                                                   | eption speed rate                                                                    |

| CMUFREQSEL | LVTTL | I    | 3   | _                                                                   | ed to select<br>input to the<br>MHz refer | ence clock                                          | _                                                                                    |

|            |       |      |     | CMU-<br>FREQSEL                                                     | STS12/<br>STS3                            | REFCLKP/N OR<br>TTLREFCLK<br>REFERENCE<br>FREQUENCY | DATA RATE                                                                            |

|            |       |      |     | 0                                                                   | 0                                         | 77.76 MHz                                           | STS-3/STM-1<br>155.52 Mbps                                                           |

|            |       |      |     | 0                                                                   | 1                                         | 77.76 MHz                                           | STS-12/STM-4<br>622.08 Mbps                                                          |

|            |       |      |     | 1                                                                   | 0                                         | 19.44 MHz                                           | STS-3/STM-1<br>155.52 Mbps                                                           |

|            |       |      |     | 1                                                                   | 1                                         | 19.44 MHz                                           | STS-12/STM-4<br>622.08 Mbps                                                          |

|            |       |      |     | from freque<br>transi                                               | an LVPECI<br>ency accur<br>mitted data    | L/LVTTL crystal os<br>acy better than 20µ           | should be generated cillator which has a opm in order for the have the necessary ems |

## STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER

| Name      | LEVEL | Түре | Pin |                                                                                                                                                                                                                                                                             | l                                                                                                                                                                                                                      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                     |

|-----------|-------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CDRREFSEL | LVTTL | I    | 60  | Selects the Clobased on the ta                                                                                                                                                                                                                                              | ck and Datable below.<br>ses CMU's                                                                                                                                                                                     | Unit Reference From Recovery Unit reference clock lock from CDRAUX                                                                                                                                                                                                                                                                                                   | erence frequency                                                                                                                                                                                    |

|           |       |      |     | CDRREFSEL                                                                                                                                                                                                                                                                   | STS12/<br>STS3                                                                                                                                                                                                         | CDRAUXREFCLK<br>FREQUENCY                                                                                                                                                                                                                                                                                                                                            | DATA RATE                                                                                                                                                                                           |

|           |       |      |     | 0                                                                                                                                                                                                                                                                           | С                                                                                                                                                                                                                      | DR uses CMU's refere<br>(see CMUFREQSE                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                     |

|           |       |      |     | 1                                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                      | 77.76 MHz                                                                                                                                                                                                                                                                                                                                                            | STS-3/STM-1<br>155.52 Mbps                                                                                                                                                                          |

|           |       |      |     | 1                                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                                                      | 77.76 MHz                                                                                                                                                                                                                                                                                                                                                            | STS-12/STM-4<br>622.08 Mbps                                                                                                                                                                         |

|           |       |      |     | NOTE: CDRA<br>+/- 500                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                        | K requires accura                                                                                                                                                                                                                                                                                                                                                    | cy of 77.76 MHz                                                                                                                                                                                     |

| LOOPTIME  | LVTTL | I    | 2   |                                                                                                                                                                                                                                                                             | timing mod<br>ut of the Re<br>ive clock fr<br>ed                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                     |

| CDRDIS    | LVTTL | I    | 12  | Received serial RXINP/N is the recovered different call module.  "Low" = Internal                                                                                                                                                                                           | Disables in<br>al data by<br>ien sample<br>rential cloc<br>al CDR unit                                                                                                                                                 | ternal Clock and Day<br>passes the integred on the rising each control of the rising each XRXCLKIP/N cor                                                                                                                                                                                                                                                             | ated CDR block.  dge of externally ning from the opti-                                                                                                                                              |

| PIO_CTRL  | LVTTL |      | 48  | Transmit Paral If this pin is ass output. Data or prior to the sam TXPCLK_IO clo Alternate Tran Asserting this c ures TXPCLK_ than a parallel t accept the exte sampled at the driven by the fra "Low" = TXPCL "High" = TXPCI "High" = TXPCI "Note: Paralle permitt synchro | llel Clock berted "High in the TXDI in the TXDI in pling by thock output smit Para control pin" IO to serve bus clock of the trising edge amer/mapp. LK_IO is a LK_IO is a bel Clock Inting the fing the foonized with | Directional Control Output Operation n", TXPCLK_IO is a [7:0] must be synch ne PISO at the rising driven by the XRT9 Illel Clock Input Op Low" or if left uncor as a parallel bus co output and permits to input. Data on the To e of the TXPCLK_IO oper device. Parallel Clock Input put operation has ramer/mapper device the transceiver tra th an internal pull- | parallel bus clock ronously applied g edge of 1L30.  peration nected, it configlock input rather he XRT91L30 to XDI[7:0] is then 0 clock input  the advantage of ice timing to be insmitter timing. |

## STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER

| NAME   | LEVEL | Түре | Pin | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|-------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

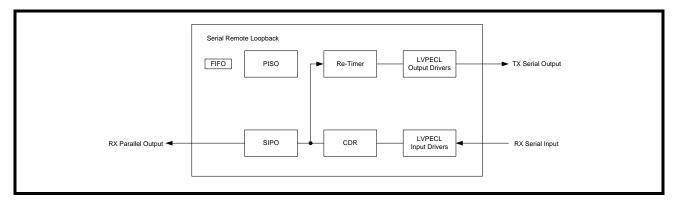

| RLOOPS | LVTTL | I    | 63  | Serial Remote Loopback The serial remote loopback mode interconnects the receive serial data input to the transmit serial data output. If serial remote loopback is enabled, the 8-bit parallel transmit data input is ignored while the 8-bit parallel receive data output is maintained.  "Low" = Disabled "High" = Serial Remote Loopback Mode Enabled  Note: DLOOP and RLOOPS can be enabled simultaneously to achieve a SPLIT loopback diagnostic feature in normal operation.                                |

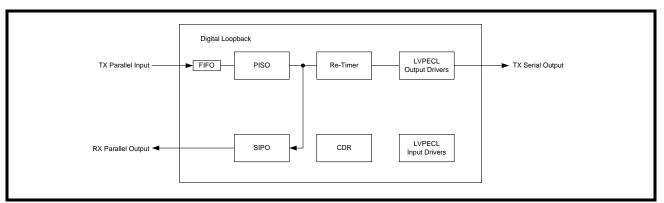

| DLOOP  | LVTTL | I    | 62  | Digital Local Loopback The digital local loopback mode interconnects the 8-bit parallel transmit data input and TxCLK to the 8-bit parallel receive data output and RxCLK respectively while maintaining the transmit serial data output. If digital local loopback is enabled, the receive serial data input is ignored.  "Low" = Disabled "High" = Digital Local Loopback Mode Enabled  Note: DLOOP and RLOOPS can be enabled simultaneously to achieve a SPLIT loopback diagnostic feature in normal operation. |

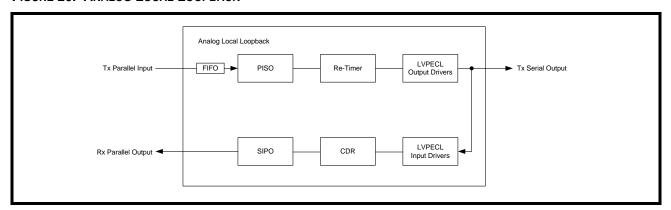

| ALOOP  | LVTTL | I    | 64  | Analog Local Loopback This loopback feature serializes the 8-bit parallel transmit data input and presents the data to the transmit serial output and in addition it also internally routes the serialized data back to the Clock and Data Recovery block for serial to parallel conversion. The received serial data input is ignored.  "Low" = Disabled "High" = Analog Local Loopback Mode Enabled                                                                                                              |

## TRANSMITTER SECTION

| NAME                                            | LEVEL       | Түре | Pin                                          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------|-------------|------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXDI0 TXDI1 TXDI2 TXDI3 TXDI4 TXDI5 TXDI6 TXDI7 | LVTTL       | I    | 58<br>57<br>56<br>55<br>54<br>53<br>51<br>50 | Transmit Parallel Data Input Transmit Parallel Clock Output Operation The 77.76 Mbps (STS-12/STM-4) / 19.44 Mbps (STS-3/STM-1) 8-bit parallel transmit data should be applied to the transmit parallel bus and simultaneously referenced to the rising edge of the TXPCLK_IO clock output. The 8-bit parallel interface is multiplexed into the transmit serial output interface with the MSB first (TXDI[7:0]).  Alternate Transmit Parallel Clock Input Operation When operating is this mode, TXPCLK_IO is no longer a parallel clock output reference but reverses direction and serves as the parallel transmit clock input reference for the PISO (Parallel Input to Serial Output) block. The 77.76 Mbps (STS-12/STM-4)                                                                                                                                                                                                                                                                                                 |

|                                                 |             |      |                                              | / 19.44 Mbps (STS-3/STM-1) 8-bit parallel transmit data should be applied to the transmit parallel bus and simultaneously referenced to the rising edge of the TXPCLK_IO clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

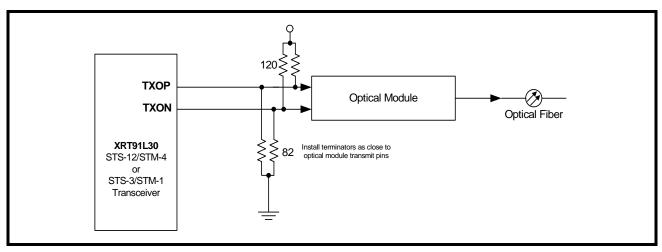

| TXOP<br>TXON                                    | LVPECL Diff | 0    | 5<br>6                                       | Transmit Serial Data Output  The transmit serial data stream is generated by multiplexing the 8-bit parallel transmit data input into a 622.08 Mbps STS-12/STM-4 or 155.52 Mbps STS-3/STM-1 serial data stream.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TXPCLK_IO                                       | LVTTL       | I/O  | 49                                           | Transmit Parallel Clock Input/Output (77.76/19.44 MHz) Transmit Parallel Clock Output Operation When the PIO_CTRL pin 48 is asserted "High," this pin will output a 77.76 MHz (STS-12/STM-4) or 19.44 MHz (STS-3/STM-1) clock output reference for the 8-bit parallel transmit data input TXDI[7:0]. This clock is used by the framer/mapper device to present the TXDI[7:0] data which the XRT91L30 will latch on the rising edge of this clock. This enables the framer/mapper device and the XRT91L30 transceiver to be in synchronization.  Alternate Transmit Parallel Clock Input Operation When the PIO_CTRL pin 48 is asserted "Low," this pin will accept a 77.76 MHz (STS-12/STM-4) or 19.44 MHz (STS-3/STM-1) clock input reference for the 8-bit parallel transmit data input TXDI[7:0]. The XRT91L30 will latch data at TXDI[7:0] on the rising edge of this clock. This has the enormous advantage of enabling the framer/mapper device transmit timing to be synchronized with the transceiver transmit timing. |

STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER

## TRANSMITTER SECTION

| NAME               | LEVEL       | Түре | Pin      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|-------------|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFCLKP<br>REFCLKN | LVPECL Diff | ı    | 16<br>17 | Reference Clock Input (77.76 MHz or 19.44 MHz)  This differential clock input reference is used for the transmit clock multiplier unit (CMU) and clock data recovery (CDR) to provide the necessary high speed clock reference for this device. It will accept either a 77.76 MHz or a 19.44 MHz Differential LVPECL clock source. Pin CMUFREQSEL determines the value used as the reference. See Pin CMUFREQSEL for more details. REFCLKP/N inputs are internally biased to 1.65V.  NOTE: In the event that TTLREFCLK LVTTL input is used instead of these differential inputs for clock reference, the REFCLKP should be tied to ground. |

| TTLREFCLK          | LVTTL       |      | 36       | TTL Reference Clock Input (77.76 MHz or 19.44 MHz)  This optional LVTTL clock input reference is used for the transmit clock multiplier unit (CMU) and clock data recovery (CDR) to provide the necessary high speed clock reference for this device rather than a differential clock source. It will accept either a 77.76 MHz or a 19.44 MHz LVTTL clock source. Pin CMUFREQSEL determines the value used as the reference. See Pin CMUFREQSEL for more details.  Note: In the event that REFCLKP/N differential inputs are used instead of this LVTTL input for clock reference, the TTLREFCLK should be tied to ground.                |

## **RECEIVER SECTION**

| NAME                                                                 | LEVEL       | Түре | Pin                                          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------|-------------|------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

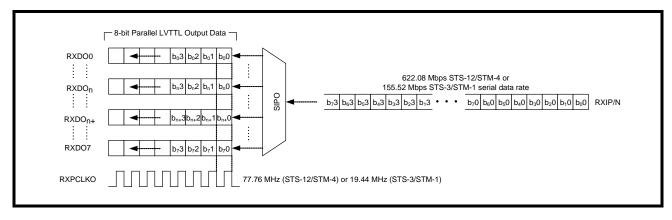

| RXDO0<br>RXDO1<br>RXDO2<br>RXDO3<br>RXDO4<br>RXDO5<br>RXDO6<br>RXDO7 | LVTTL       | 0    | 19<br>20<br>22<br>23<br>24<br>25<br>26<br>27 | Receive Parallel Data Output 77.76 Mbps (STS-12/STM-4) / 19.44 Mbps (STS-3/STM-1) 8-bit parallel receive data output is updated simultaneously on the rising edge of the RXPCLKO output. The 8-bit parallel interface is de-multiplexed from the receive serial data input MSB first (RXDO[7:0]). The XRT91L30 will output the data on the falling edge of this clock.                                                                                                                                                                |

| RXIP<br>RXIN                                                         | Diff LVPECL | _    | 13<br>14                                     | Receive Serial Data Input The differential receive serial data stream of 622.08 Mbps STS-12/STM-1 or 155.52 Mbps STS-3/STM-1 is applied to these input pins.                                                                                                                                                                                                                                                                                                                                                                          |

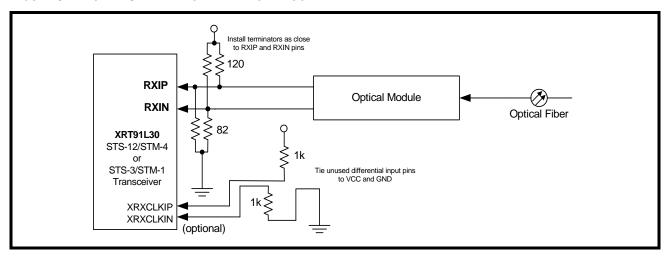

| XRXCLKIP<br>XRXCLKIN                                                 | Diff LVPECL | 1    | 8 9                                          | External Recovered Receive Clock Input The differential receive serial data stream of 622.08 Mbps STS-12/STM-1 or 155.52 Mbps STS-3/STM-1 is sampled on the rising edge of this externally recovered differential clock coming from the optical module. It is used when the internal CDR unit is disabled and bypassed by the CDRDIS pin.  Note: In the event that XRXCLKIP/N differential input pins are unused, XRXCLKIP should be tied to VCC with a 1k Ohm pull-up and XRXCLKIN should be tied to Ground with a 1k Ohm pull-down. |

| RXPCLKO                                                              | LVTTL       | 0    | 29                                           | Receive Parallel Clock Output (77.76 MHz or 19.44 MHz) 77.76 MHz (STS-12/STM-4) or 19.44 MHz (STS-3/STM-1) clock output reference for the 8-bit parallel receive data output RXDO[7:0]. The parallel received data output bus will be updated on the falling edge of this clock.                                                                                                                                                                                                                                                      |

| CDRAUX-<br>REFCLK                                                    | LVTTL       | I    | 32                                           | Clock and Data Recovery Auxillary Reference Clock 77.76 MHz ± 500 ppm auxillary reference clock for the CDR.  Note: In the event that CDRAUXREFCLK LVTTL input pin is unused, CDRAUXREFCLK should be tied to ground.                                                                                                                                                                                                                                                                                                                  |

| OOF                                                                  | LVTTL       | I    | 11                                           | Out of Frame Input Indicator  This level sensitive input pin is used to initiate frame detection and byte alignment recovery when OOF is declared by the downstream device. When this pin is held High, FRAME-PULSE will pulse for a single RXPCLKO period upon the detection of every third frame alignment A2 byte in the incoming SONET/SDH Frame.  "Low" = Normal Operation  "High" = OOF Indication initiating frame detection and byte boundary recovery and activating FRAMEPULSE                                              |

| FRAMEPULSE                                                           | LVTTL       | 0    | 30                                           | Sonet Frame Alignment Pulse This pin will generate a single pulse for an RXPCLKO clock period upon the detection of the third frame alignment A2 byte whenever the OOF input pin is held High. The parallel received data output bus will then be byte aligned to this newly recovered SONET/SDH frame.                                                                                                                                                                                                                               |

#### STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER

| TS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER REV. P1.0.8 |        |      |          |                                                                                                                     |  |  |  |

|--------------------------------------------------------------|--------|------|----------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                                                         | LEVEL  | Түре | Pin      | DESCRIPTION                                                                                                         |  |  |  |

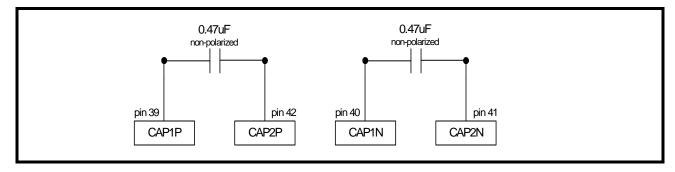

| CAP1P<br>CAP2P                                               | Analog | -    | 39<br>42 | CDR Non-polarized External Filter Capacitor C1 = 0.47μF ± 10% tolerance (Isolate from noise and place close to pin) |  |  |  |

| CAP1N                                                        | Analog | -    | 40       | CDR Non-polarized External Filter Capacitor                                                                         |  |  |  |

| CAP1N<br>CAP2N | Allalog   | - | 41 | C2 = $0.47\mu\text{F} \pm 10\%$ tolerance<br>(Isolate from noise and place close to pin)                                                                                                                                                                                                                                                                                                                                |

|----------------|-----------|---|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

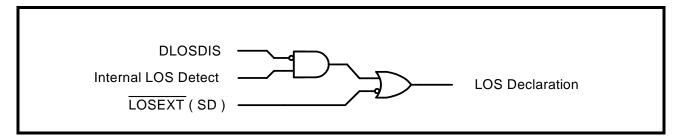

| DLOSDIS        | LVTTL     | I | 7  | LOS (Los of Signal) Detect Disable Disables internal LOS monitoring and automatic muting of RXDO[7:0] upon LOS detection. LOS is declared when a string of 128 consecutive zeros occur on the line. LOS condition is cleared when the 16 or more pulse transitions is detected for 128 bit period sliding window.  "Low" = Monitor and Mute received data upon LOS declaration "High" = Disable internal LOS monitoring |

| LOSEXT         | SE-LVPECL | I | 33 | LOS or Signal Detect Input from Optical Module  Active "Low." When active, this pin will force the received data output bus RXDO[7:0] to a logic state of '0.'  "Low" = Forced LOS  "High" = Normal Operation                                                                                                                                                                                                           |

## **POWER AND GROUND**

| NAME       | Түре | PIN                    | DESCRIPTION                                                                                                                                                                                                                                                                     |

|------------|------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD3.3     | PWR  | 15, 18, 31, 34, 47, 61 | 3.3V CMOS Power Supply VDD3.3 should be isolated from the Analog VDD power supplies. For best results, use a ferrite bead along with an internal power plane separation. The VDDD3.3 power supply pins should have bypass capacitors to the nearest ground.                     |

| AVDD3.3_TX | PWR  | 38                     | Analog 3.3V Transmitter Power Supply  AVDD3.3_TX should be isolated from the digital power supplies.  For best results, use a ferrite bead along with an internal power plane separation. The AVDD3.3_TX power supply pins should have bypass capacitors to the nearest ground. |

| AVDD3.3_RX | PWR  | 43                     | Analog 3.3V Receiver Power Supply  AVDD3.3_RX should be isolated from the digital power supplies.  For best results, use a ferrite bead along with an internal power plane separation. The AVDD3.3_RX power supply pins should have bypass capacitors to the nearest ground.    |

| VDD_LVPECL | PWR  | 4, 10                  | 3.3V Input/Output LVPECL Bus Power Supply These pins require a 3.3V potential voltage for properly biasing the Differential LVPECL input and output pins.                                                                                                                       |

| AGND_TX    | PWR  | 37                     | Transmitter Analog Ground for 3.3V Analog Power Supplies It is recommended that all ground pins of this device be tied together.                                                                                                                                                |

## STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER

| NAME    | Түре | Pin                    | DESCRIPTION                                                                                                                   |

|---------|------|------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| AGND_RX | PWR  | 44                     | Receiver Analog Ground for 3.3V Analog Power Supplies It is recommended that all ground pins of this device be tied together. |

| GND     | GND  | 21, 28, 35, 45, 46, 52 | Power Supply and Thermal Ground It is recommended that all ground pins of this device be tied together.                       |

#### 1.0 FUNCTIONAL DESCRIPTION

The XRT91L30 transceiver is designed to operate with a SONET Framer/ASIC device and provide a high-speed serial interface to optical networks. The transceiver converts 8-bit parallel data running at 77.76 Mbps (STS-12/STM-4) or 19.44 Mbps (STS-3/STM-1) to a serial Differential LVPECL bit stream at 622.08 Mbps or 155.52 Mbps and vice-versa. It implements a clock multiplier unit (CMU), SONET/SDH serialization/deserialization (SerDes), receive clock and data recovery (CDR) unit and a SONET/SDH frame and byte boundary detection circuit. The transceiver is divided into Transmit and Receive sections and is used to provide the front end component of SONET equipment, which includes primarily serial transmit and receive functions.

## 1.1 STS-12/STM-4 and STS-3/STM-1 Mode of Operation

Functionality of the transceiver can be configured by using the appropriate signal level on the STS-12/STS-3 pin. STS-3/STM-1 mode is selected by pulling STS-12/STS-3 "Low" as described in the Hardware Pin Descriptions. However, if STS-12/STM-4 mode is desired, it is selected by pulling STS-12/STS-3 "High." Therefore, the following sections describe the functionality rather than how each function is controlled. The Hardware Pin Descriptions and describe device configuration.

## 1.2 Clock Input Reference for Clock Multiplier (Synthesizer) Unit

The XRT91L30 can accept both a 19.44 MHz or a 77.76 MHz Differential LVPECL clock input at REFCLKP/N or a Single-Ended LVTTL clock at TTLREFCLK as its internal timing reference for generating higher speed clocks. The REFCLKP/N or TTLREFCLK input should be generated from an LVPECL/LVTTL crystal oscillator which has a frequency accuracy better than 20ppm in order for the transmitted data rate frequency to have the necessary accuracy required for SONET systems. The reference clock can be provided with one of two frequencies chosen by CMUFREQSEL. The reference frequency options for the XRT91L30 are listed in Table 1.

**REFCLKP/N OR TTLREFCLK** STS12/STS3 **CMUFREQSEL DATA RATE** REFERENCE FREQUENCY 0 0 77.76 MHz STS-3/STM-1 155.52 Mbps 0 1 77.76 MHz STS-12/STM-4 622.08 Mbps 1 19.44 MHz 0 STS-3/STM-1 155.52 Mbps 1 1 19.44 MHz STS-12/STM-4 622.08 Mbps

TABLE 1: CMU REFERENCE FREQUENCY OPTIONS (DIFFERENTIAL OR SINGLE-ENDED)

## 1.3 Data Latency

Due to different operating modes and data logic paths through the device, there is an associated latency from data ingress to data egress. Table 2 specifies the data latency for a typical path.

TABLE 2: DATA INGRESS TO DATA EGRESS LATENCY

| MODE OF<br>OPERATION   | Dата Ратн                          | CLOCK REFERENCE      | RANGE OF CLOCK<br>CYCLES |

|------------------------|------------------------------------|----------------------|--------------------------|

| Thru-mode              | MSB at RXIP/N to data on RXDO[7:0] | Recoved RXIP/N Clock | 25 to 35                 |

| Serial Remote Loopback | MSB at RXIP/N to MSB at TXOP/N     | Recoved RXIP/N Clock | 2 to 4                   |

### 2.0 RECEIVE SECTION

The receive section of XRT91L30 include the inputs RXIP/N, followed by the clock and data recovery unit (CDR) and receive serial-to-parallel converter. The receiver accepts the high speed Non-Return to Zero (NRZ) serial data at 622.08 Mbps or 155.52 Mbps through the input interfaces RXIP/N. The clock and data recovery unit recovers the high-speed receive clock from the incoming scrambled NRZ data stream. The recovered serial data is converted into an 8-bit-wide, 77.76 Mbps or 19.44 Mbps parallel data and presented to the RXDO[7:0] parallel interface. This parallel interface is designed for Single-Ended LVTTL operation. A divide-by-8 version of the high-speed recovered clock RXPCLKOP/N, is used to synchronize the transfer of the 8-bit RXDO[7:0] data with the receive portion of the framer/mapper device. Upon initialization or loss of signal or loss of lock, the external reference clock signal of 19.44 MHz or 77.76 MHz is used to start-up the clock recovery phase-locked loop for proper operation. In certain applications, the CDR block on the XRT91L30 can be disabled and bypassed by enabling the CDRDIS pin to permit the flexibility of using an externally recovered receive clock thru the XRXCLKIP/N pins.

## 2.1 Receive Serial Input

The receive serial inputs are applied to RXIP/N. The receive serial inputs can be AC or DC coupled to an optical module or an electrical interface. A simplified DC coupling block diagram is shown in Figure 3.

FIGURE 3. RECEIVE SERIAL INPUT INTERFACE BLOCK

**Note:** Some optical modules integrate AC coupling capacitors within the module. AC or DC coupling is largely specific to system design and optical module of choice.

## 2.2 Recieve Serial Data Input Timing

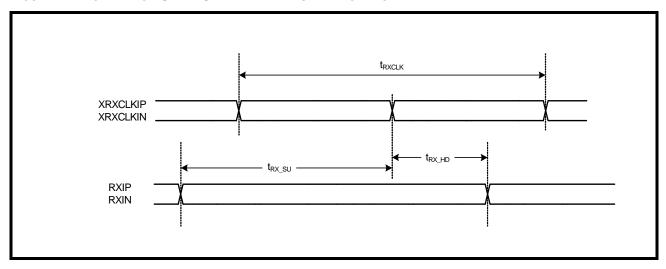

The received High-Speed Serial Differential Data Input must adhere to the set-up and hold time timing specifications below.

FIGURE 4. RECEIVE HIGH-SPEED SERIAL DATA INPUT TIMING DIAGRAM

TABLE 3: RECEIVE HIGH-SPEED SERIAL DATA INPUT TIMING (STS-12/STM-4 OPERATION)

| SYMBOL             | PARAMETER                                         | Min | Түр   | Max | Units |

|--------------------|---------------------------------------------------|-----|-------|-----|-------|

| t <sub>RXCLK</sub> | Receive external recovered clock period           |     | 1.608 |     | ns    |

| t <sub>RX_SU</sub> | Serial data setup time with respect to XRXCLKIP/N | 400 |       |     | ps    |

| t <sub>RX_HD</sub> | Serial data hold time with respect to XRXCLKIP/N  | 100 |       |     | ps    |

TABLE 4: RECEIVE HIGH-SPEED SERIAL DATA INPUT TIMING (STS-3/STM-1 OPERATION)

| SYMBOL             | PARAMETER                                         | Min | Түр  | Max | Units |

|--------------------|---------------------------------------------------|-----|------|-----|-------|

| t <sub>RXCLK</sub> | Receive external recovered clock period           |     | 6.43 |     | ns    |

| t <sub>RX_SU</sub> | Serial data setup time with respect to XRXCLKIP/N | 1.5 |      |     | ns    |

| t <sub>RX_HD</sub> | Serial data hold time with respect to XRXCLKIP/N  | 1.5 |      |     | ns    |

## 2.3 Receive Clock and Data Recovery

The clock and data recovery (CDR) unit accepts the high speed NRZ serial data from the Differential LVPECL receiver and generates a clock that is the same frequency as the incoming data. The clock recovery can either utilize the transmitter's CMU reference clock from either REFCLKP/N or TTLREFCLK or it can use independent clock source CDRAUXREFCLK to train and monitor its clock recovery PLL. Initially upon startup, the PLL locks to the local reference clock within ±500 ppm. Once this is achieved, the PLL then attempts to lock onto the incoming receive data stream. Whenever the recovered clock frequency deviates from the local reference clock frequency by more than approximately ±500 ppm, the clock recovery PLL will switch and lock back onto the local reference clock. Whenever a Loss of Lock or a Loss of Signal event occurs, the CDR will continue to supply a receive clock (based on the local reference) to the framer/mapper device. When the LOSEXT is asserted by the optical module or when LOS is detected, the receive parallel data output will be forced to a logic zero state for the entire duration that a LOS condition is detected. This acts as a receive data mute upon LOS function to prevent random noise from being misinterpreted as valid incoming data. When the LOSEXT becomes inactive and the recovered clock is determined to be within ±500 ppm accuracy with respect to the local reference source and LOS is no longer declared, the clock recovery PLL will switch and lock back onto the incoming receive data stream. Table 5 shows Clock and Data Recovery reference clock settings. Table 6 specifies the Clock and Data Recovery Unit performance characteristics.

TABLE 5: CLOCK DATA RECOVERY UNIT REFERENCE CLOCK SETTINGS

| CMUFREQSEL | CDRREFSEL | STS12/<br>STS3 | REFCLKP/N <sup>1</sup> or<br>TTLREFCLK <sup>1</sup><br>FREQUENCY (MHz) | CDRAUXREFCLK <sup>2</sup> FREQUENCY (MHz) | CDR OUTPUT<br>FREQUENCY (MHz) |

|------------|-----------|----------------|------------------------------------------------------------------------|-------------------------------------------|-------------------------------|

| 0          | 0         | 0              | 77.76 MHz                                                              | not used                                  | 155.52                        |

| 0          | 0         | 1              | 77.76 MHz                                                              | not used                                  | 622.08                        |

| 1          | 0         | 0              | 19.44 MHz                                                              | not used                                  | 155.52                        |

| 1          | 0         | 1              | 19.44 MHz                                                              | not used                                  | 622.08                        |

| Х          | 1         | 0              | not referenced by CDR                                                  | 77.76 MHz                                 | 155.52                        |

| Х          | 1         | 1              | not referenced by CDR                                                  | 77.76 MHz                                 | 622.08                        |

<sup>&</sup>lt;sup>1</sup>Requires frequency accuracy better than 20ppm in order for the transmitted data rate frequency to have the necessary accuracy required for SONET systems.

<sup>&</sup>lt;sup>2</sup>CDRAUXREFCLK requires accuracy of 77.76 MHz +/- 500ppm.

TABLE 6: CLOCK AND DATA RECOVERY UNIT PERFORMANCE

| NAME                 | PARAMETER                                                          | Min | Түр | Max | Units |

|----------------------|--------------------------------------------------------------------|-----|-----|-----|-------|

| REF <sub>DUTY</sub>  | Reference clock duty cycle                                         | 40  |     | 60  | %     |

| REF <sub>JIT</sub>   | Reference clock jitter (rms) with 19.44 MHz reference <sup>1</sup> |     |     | 5   | ps    |

| REF <sub>JIT</sub>   | Reference clock jitter (rms) with 77.76 MHz reference <sup>1</sup> |     |     | 13  | ps    |

| REF <sub>TOL</sub>   | Reference clock frequency tolerance <sup>2</sup>                   | -20 |     | +20 | ppm   |

| TOL <sub>JIT</sub>   | Input jitter tolerance with 1 MHz < f < 20 MHz PRBS pattern        | 0.3 | 0.4 |     | UI    |

| OCLK <sub>FREQ</sub> | Frequency output                                                   | 620 |     | 624 | MHz   |

| OCLK <sub>DUTY</sub> | Clock output duty cycle                                            | 40  |     | 60  | %     |

Jitter specification is defined using a 12kHz to 1.3/5MHz LP-HP single-pole filter.

#### 2.3.1 **Internal Clock and Data Recovery Bypass**

Optionally, the internal CDR unit can be disabled and bypassed in lieu of an externally recovered clock. Asserting the CDRDIS "High" disables the internal Clock and Data Recovery unit and the received serial data bypasses the integrated CDR block. RXINP/N is then sampled on the rising edge of the externally recovered differential clock XRXCLKIP/N coming from the optical module or an external clock recovery unit. Figure 5 shows the possible internal paths of the recovered clock and data.

FIGURE 5. INTERNAL CLOCK AND DATA RECOVERY BYPASS

<sup>&</sup>lt;sup>1</sup>These reference clock jitter limits are required for the outputs to meet SONET system level jitter requirements (<10 mUI<sub>rms</sub>).

<sup>&</sup>lt;sup>2</sup>Required to meet SONET output frequency stability requirements.

## 2.4 External Receive Loop Filter Capacitors

These  $0.47\mu F$  non-polarized external loop filter capacitors provide the necessary components to achieve the required receiver jitter performance. They must be well isolated to prohibit noise entering the CDR block and should be placed as close to the pins as much as possible. Figure 6 shows the pin connections and external loop filter components. These two non-polarized capacitors should be of +/- 10% tolerance.

FIGURE 6. EXTERNAL LOOP FILTERS

## 2.5 Loss Of Signal

XRT91L30 supports internal Loss of Signal detection (LOS) and external LOS detection. The internal Loss of Signal Detector monitors the incoming data stream and if the incoming data stream has no transition continuously for more than 128 bit periods, Loss of Signal is declared. This LOS detection will be removed when the circuit detects 16 transitions in a 128 bit period sliding window. Pulling the corresponding DLOSDIS signal to a high level will disable the internal LOS detection circuit. The external LOS function is supported by the LOSEXT input. The Single-Ended LVPECL input usually comes from the optical module through an output usually called "SD" or "FLAG" which indicates the lack or presence of optical power. Depending on the manufacturer of these devices the polarity of this signal can be either active "Low" or active "High." LOSEXT is an active "Low" signal requiring a low level to assert or invoke a forced LOS. The external LOSEXT input pin and internal LOS detector are Logically OR'ed to control detection and declaration of Loss of Signal. Whenever LOS is internally detected or an external LOS is asserted thru the LOSEXT pin, the XRT91L30 will automatically force the receive parallel data output to a logic state "0" for the entire duration that a LOS condition is declared. This acts as a receive data mute upon LOS function to prevent random noise from being misinterpreted as valid incoming data.

FIGURE 7. LOS DECLARATION CIRCUIT

## 2.6 SONET Frame Boundary Detection and Byte Alignment Recovery

A Frame and Byte Boundary Detection circuit searches the incoming data channel for three consecutive A1 (0xF6 Hex) bytes followed by three consecutive A2 (0x28 Hex) bytes. The detector operates under the control of the OOF (Out of Frame) signals provided from the SONET Framer. Detection is enabled when OOF is held "High" and remains active until OOF goes "Low." When framing pattern detection is enabled, the framing pattern is used to locate byte and frame boundaries in the incoming receive data stream. The receive serial-toparallel converter block uses the located byte boundary to assemble the incoming data stream into bytes for output on the parallel data output bus RXDO[7:0]. The frame boundary is reported on the frame pulse (FRAMEPULSE) output at the onset of detecting the third A2 byte pattern when any serial 48-bit pattern matching the framing pattern is detected on the incoming data stream. While in the pattern search and detection state and so long is OOF is active, the frame pulse (FRAMEPULSE) output is activated for one byte clock cycle (RXPCLKO = 12.86 ns pulse duration for STS-12/STM-4 or 51.44 ns pulse duration for STS-3/ STM-1) anytime a 48-bit pattern matching the framing pattern is detected on the incoming data stream. Once the SONET Framer Overhead Circuitry has verified that frame and byte synchronization are correct, the OOF input pin should be de-asserted by the SONET Framer to disable the XRT91L30 frame search process from trying to synchronize repeatedly and to de-activate FRAMEPULSE. When the XRT91L30's framing pattern detection is disabled upon the de-assertion of OOF input pin from the SONET Framer, the byte boundary will lock to the detected location and will remain locked to that location found when detection was previously enabled.

## 2.7 Receive Serial Input to Parallel Output (SIPO)

During STS-12/STM-4 operation, the SIPO is used to convert the 622.08 Mbps serial data input to 77.76 Mbps parallel data output which can interface to a SONET Framer/ASIC. If the XRT91L30 is operating in STS-3/STM-1, the SIPO will convert the 155.52 Mbps serial data input to 19.44 Mbps parallel data output. The SIPO bit de-interleaves the serial data input into an 8-bit parallel output to RXDO[7:0]. A simplified block diagram is shown in Figure 8. XRT91L30 clocks data out on RXDO[7:0] at the falling edge of RXPCLKO.

FIGURE 8. SIMPLIFIED BLOCK DIAGRAM OF SIPO

## 2.8 Receive Parallel Output Interface

The 8-bit Single-Ended LVTTL running at 77.76 Mbps (STS-12/STM-4) or 19.44 Mbps (STS-3/STM-1) parallel data output of the receive path is used to interface to a SONET Framer/ASIC synchronized to the recovered clock. A simplified block diagram is shown in Figure 9.

FIGURE 9. RECEIVE PARALLEL OUTPUT INTERFACE BLOCK

## 2.9 Disable Parallel Receive Data Output Upon LOS

The parallel receiver outputs are automatically pulled "Low" or forced to a logic state of "0" during a LOS <u>condition</u> to prevent data chattering unless LOS detection is <u>disabled</u> by asserting DLOSDIS and keeping <u>LOSEXT</u> input pin "high." In addition, the user can also assert <u>LOSEXT</u> input pin from the optical module to force an LOS and mute the parallel receiver outputs as well.

## 2.10 Receive Parallel Data Output Timing

The receive parallel data output from the STS-12/STM-4 or STS-3/STM-1 receiver will adhere to the setup and hold times shown in Figure 10 ,Table 7, and Table 8. Table 9 shows the PECL and TTL output timing specifications.

FIGURE 10. RECEIVE PARALLEL OUTPUT TIMING

TABLE 7: RECEIVE PARALLEL DATA OUTPUT TIMING (STS-12/STM-4 OPERATION)

| SYMBOL                  | PARAMETER                                                                                      | Min | Түр   | Max | Units |

|-------------------------|------------------------------------------------------------------------------------------------|-----|-------|-----|-------|

| <sup>t</sup> RXCLK      | Receive high-speed serial clock period                                                         |     | 1.608 |     | ns    |

| t <sub>RXPCLKO</sub>    | Receive parallel data output byte clock period                                                 |     | 12.86 |     | ns    |

| <sup>t</sup> RXDO_VALID | Time the data is valid on RXDO[7:0] and FRAMEPULSE before and after the rising edge of RXPCLKO | 4   |       |     | ns    |

| t <sub>PULSE_WID</sub>  | Pulse width of frame detection pulse on FRAMEPULSE                                             |     | 12.86 |     | ns    |

TABLE 8: RECEIVE PARALLEL DATA OUTPUT TIMING (STS-3/STM-1 OPERATION)

| SYMBOL                  | PARAMETER                                                                                      | Min | Түр   | Max | Units |

|-------------------------|------------------------------------------------------------------------------------------------|-----|-------|-----|-------|

| <sup>t</sup> RXCLK      | Receive high-speed serial clock period                                                         |     | 6.43  |     | ns    |

| t <sub>RXPCLKO</sub>    | Receive parallel data output byte clock period                                                 |     | 51.44 |     | ns    |

| <sup>t</sup> RXDO_VALID | Time the data is valid on RXDO[7:0] and FRAMEPULSE before and after the rising edge of RXPCLKO | 22  |       |     | ns    |

| t <sub>PULSE_WID</sub>  | Pulse width of frame detection pulse on FRAMEPULSE                                             |     | 51.44 |     | ns    |

XRT91L30

## TABLE 9: PECL AND TTL RECEIVE OUTPUTS TIMING SPECIFICATION

| SYMBOL              | PARAMETER                          | Min | Түр | Max | Units |

|---------------------|------------------------------------|-----|-----|-----|-------|

| t <sub>R_PECL</sub> | PECL output rise time (20% to 80%) |     | 350 |     | ps    |

| t <sub>F_PECL</sub> | PECL output fall time (80% to 20%) |     | 350 |     | ps    |

| t <sub>R_TTL</sub>  | TTL output rise time (10% to 90%)  |     | 2   |     | ns    |

| t <sub>F_TTL</sub>  | TTL output fall time (90% to 10%)  |     | 1.5 |     | ns    |

#### 3.0 TRANSMIT SECTION

The transmit section of the XRT91L30 accepts 8-bit parallel data and converts it to serial Differential LVPECL data output intented to interface to an optical module. It consists of an 8-bit parallel Single-Ended LVTTL interface, Parallel-to-Serial Converter, a clock multiplier unit (CMU), a Low Voltage Positive-referenced Emitter-Coupled Logic (LVPECL) differential line driver, and Loop Timing modes. The LVPECL serial data output rate is 622.08 Mbps for STS-12/STM-4 applications and 155.52 Mbps for STS-3/STM-1 applications. The high frequency serial clock is synthesized by a PLL, which uses a low frequency clock as its input reference. In order to synchronize the data transfer process, the synthesized 622.08 MHz for STS-12/STM-4 or 155.52 MHz STS-3/STM-1 serial clock output is divided by eight and the 77.76 MHz (STS-12/STM-4) or 19.44 MHz (STS-3/STM-1) clock respectively is presented to the framer/mapper device to be used as its timing source.

#### 3.1 Transmit Parallel Input Interface

The parallel data from an framer/mapper device is presented to the XRT91L30 through an 8-bit Single-Ended LVTTL parallel bus interface TXDI[7:0]. To directly interface to the XRT91L30, the SONET Framer/ASIC must be synchronized to the same timing source TXPCLK IO in presenting data on the parallel bus interface. The data must meet setup and hold times with respect to TXPCLK IO. This clock output source is used to synchronize the SONET Framer/ASIC to the XRT91L30. The framer/mapper device should use TXPCLK IO as its timing source so that parallel data is phase aligned with the serial transmit data. The data is latched into a parallel input register on the rising edge of TXPCLK IO. TXPCLK IO is derived from a divide-by-8 of the high speed synthesized clock resulting in a 77.76/ 19.44 MHz Single-Ended LVTTL clock output source to be used by the framer/mapper device for parallel bus synchronization. A simplified block diagram of the transmit parallel bus clock output system interface is shown in Figure 11.

FIGURE 11. TRANSMIT PARALLEL INPUT INTERFACE BLOCK

## 3.2 Transmit Parallel Data Input Timing

When applying parallel data input to the transmitter, the setup and hold times should be followed as shown in Figure 12 and Table 10, Table 11.

FIGURE 12. TRANSMIT PARALLEL INPUT TIMING

TABLE 10: TRANSMIT PARALLEL DATA INPUT TIMING (STS-12/STM-4 OPERATION)

| SYMBOL                  | PARAMETER                                          | Min | Түр   | Max | Units |

|-------------------------|----------------------------------------------------|-----|-------|-----|-------|

| t <sub>TXPCLK_</sub> IO | Transmit Clock <b>Output</b> period                |     | 12.86 |     | ns    |

| t <sub>TXDI_</sub> SU   | Transmit data setup time with respect to TXPCLK_IO | 2.0 |       |     | ns    |

| t <sub>TXDI_HD</sub>    | Transmit data hold time with respect to TXPCLK_IO  | 1.0 |       |     | ns    |

TABLE 11: TRANSMIT PARALLEL DATA INPUT TIMING (STS-3/STM-1 OPERATION).

| SYMBOL                 | PARAMETER                                          | Min | Түр   | Max | Units |

|------------------------|----------------------------------------------------|-----|-------|-----|-------|

| t <sub>TXPCLK_IO</sub> | Transmit Clock <b>Output</b> period                |     | 51.44 |     | ns    |

| t <sub>TXDI_SU</sub>   | Transmit data setup time with respect to TXPCLK_IO | 2.0 |       |     | ns    |

| t <sub>TXDI_HD</sub>   | Transmit data hold time with respect to TXPCLK_IO  | 1.0 |       |     | ns    |

## 3.3 Alternate Transmit Parallel Bus Clock Input Option

To decouple transmit parallel clock domains of the framer/mapper device and the XRT91L30 transceiver and to eliminate difficult timing issues between them, the transmit parallel clock TXPCLK\_IO can also be optionally configured as a clock input. Rather than provide a transmit parallel clock output reference to the framer/mapper device, the XRT91L30 can instead accept a reference transmit parallel clock input signal from the framer/mapper device to sample the transmit parallel bus. When PIO\_CTRL pin 48 is asserted "Low," TXPCLK\_IO switches into a clock input and the XRT91L30 will now sample data on the transmit parallel bus TXDI[7:0] based on TXPCLK\_IO clock input reference coming from the framer/mapper device. The use of the alternate transmit parallel bus clock input option permits the system to tolerate an arbitrary amount of phase mismatch and jitter between framer/mapper transmit parallel clock timing and transceiver transmit timing. Figure 13 provides a detailed overview of the alternate transmit parallel bus clock input system interface.