# XTR25020

# High Temperature Power Gate Driver

Rev 2 - August 2021 (DS-00662-14)

**Data Sheet**

**PRODUCTION**

## **FEATURES**

- Operational beyond the -60°C to +230°C temperature range.

- Supply voltage from 4.5V to 35V.

- Integrated charge-pump inside pull-up driver allowing 100% dutycycle PWM control signal.

- Internal 5V LDO regulator.

- · Safe start-up of normally-on devices.

- · Half bridge cross-conduction protection.

- Pull-up driver with 3A peak current and 1A continuous current capability.

- Pull-down driver with 3A peak current capability.

- On-chip active Miller clamp switch with 3A capability.

- Resistor-programmable Under voltage lockout (ULVO).

- Resistor-programmable over-current protection level (rail-to-rail, positive and negative current sense).

- Latch-up free.

- Ruggedized SMT packages. Also available as bare die.

### **APPLICATIONS**

- Reliability-critical, Automotive, Aeronautics & Aerospace, Downhole, Energy Conversion, Solar.

- Intelligent Power Modules (IPM).

- · Power inverters and motor drives.

- Uninterruptible power supplies (UPS).

- Power conversion and power factor correction (PFC).

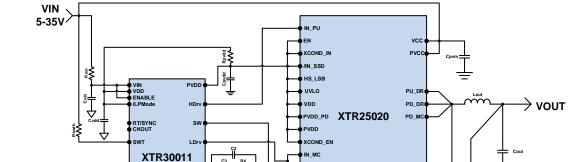

- DC/DC converters and switched mode power supplies (SMPS).

## DESCRIPTION

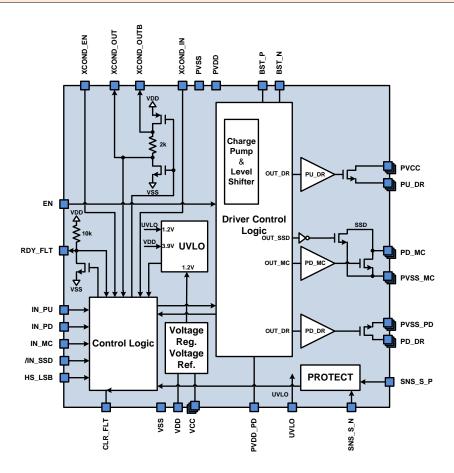

XTR25020 is a high-temperature, high reliability intelligent power transistor driver designed to provide a robust, reliable, compact and efficient solution for driving a large variety of high-temperature, high-voltage, and high-efficiency power transistors. XTR25020 is able to drive normally-On and normally-Off power transistors in Silicon Carbide (SiC), Gallium Nitride (GaN) and standard silicon, including JFETs, MOSFETs, BJTs, SJTs and MESFETs.

The XTR25020 includes one pull-up gate-drive-channel (PU\_DR) capable of sourcing a typical 3A peak current and two pull-down gate-drive-channels capable of sinking a typical 3A peak current (PD\_DR and PD\_MC). The PD\_DR channel is used for the effective turn-off of the power transistor, while PD\_MC channel is used for Active Miller Clamping (AMC) function thanks to its internal gate level detection.

The circuit includes soft shut-down capability that slowly shuts down the power transistor in case of fault. The XTR25020 is able to detect failures due to over-current in the power switch or to UVLO detected on the power supply. In addition, safe start-up and cross-conduction protection are implemented to guarantee safe operation at system level.

The XTR25020 can be used to extend the drive capability of the XTR26020. It can also be used with the XTR40010 to drive multiple power transistors connected in parallel for very high-power applications.

# PRODUCT HIGHLIGHT

## **ORDERING INFORMATION**

| Product Reference | Temperature Range | Package        | Pin Count | Marking  |

|-------------------|-------------------|----------------|-----------|----------|

| XTR25020-BD       | -60°C to +230°C   | Bare die       |           |          |

| XTR25021-LJ       | -60°C to +230°C   | Ceramic LJCC28 | 28        | XTR25021 |

Other packages and packaging configurations possible upon request. For some packages or packaging configurations, MOQ may apply.

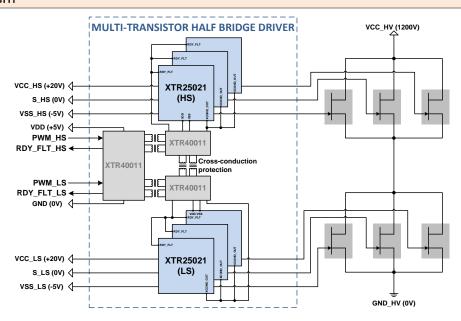

# TYPICAL APPLICATIONS

**Buck DC-DC Converter**

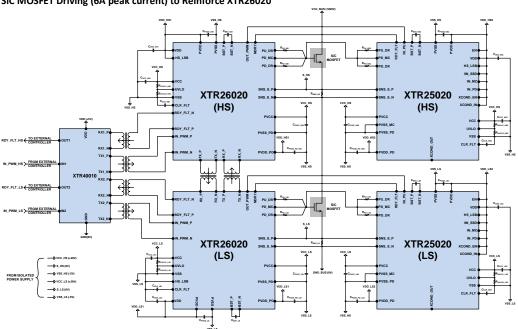

## SiC MOSFET Driving (6A peak current) to Reinforce XTR26020

## **ABSOLUTE MAXIMUM RATINGS**

| Supply voltage                       | VCC_PVSS                                                                             | -0.5V to 40V           |  |

|--------------------------------------|--------------------------------------------------------------------------------------|------------------------|--|

|                                      | PVCC                                                                                 | PVSS-0.5V to VCC+0.5V  |  |

|                                      | PVDD-PVSS                                                                            | -0.5V to 5.5V          |  |

|                                      | VDD, PVDD_PD                                                                         | PVSS-0.5V to PVDD+0.5V |  |

|                                      | VSS, PVSS_PD                                                                         | PVSS-0.5V to PVSS+0.5V |  |

| Input pins                           | IN_PU, IN_PD, IN_MC, /IN_SSD, ULVO, HS_LSB, RDY_FLT, CLR_FLT, EN, XCOND_EN, XCOND_IN | PVSS-0.5V to PVDD+0.5V |  |

|                                      | UVLO_SNS_S_P, SNS_S_N                                                                | PVSS-0.5V to VCC+0.5V  |  |

| Outputs pins                         | PU_DR, PD_MC, PD_DR                                                                  | PVSS-0.5V to VCC+0.5V  |  |

|                                      | RDY_FLT, XCOND_OUT                                                                   | PVSS-0.5V to PVDD+0.5V |  |

| Sense pins                           | SNS_S_P or SNS_S_N                                                                   | PVSS-0.5V to VCC+0.5V  |  |

|                                      | SNS_S_P versus SNS_S_N                                                               | -5V to +5V             |  |

| Storage Temperature Range            |                                                                                      | -65°C to +230°C        |  |

| Operating Junction Temperature Range |                                                                                      | -65°C to +300°C        |  |

| ESD Classification                   |                                                                                      | 1kV HBM MIL-STD-883    |  |

|                                      |                                                                                      |                        |  |

**Caution:** Stresses beyond those listed in "ABSOLUTE MAXIMUM RATINGS" may cause permanent damage to the device. These are stress ratings only and functionality of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to "ABSOLUTE MAXIMUM RATINGS" conditions for extended periods may permanently affect device reliability.

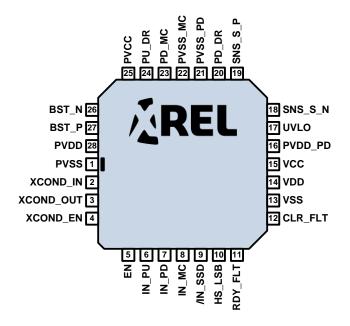

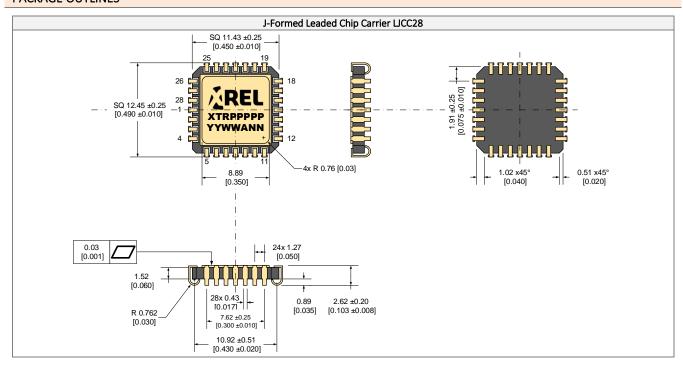

# **PACKAGING**

#### J-Formed Ceramic LJCC28 XTR25021-LJ

4

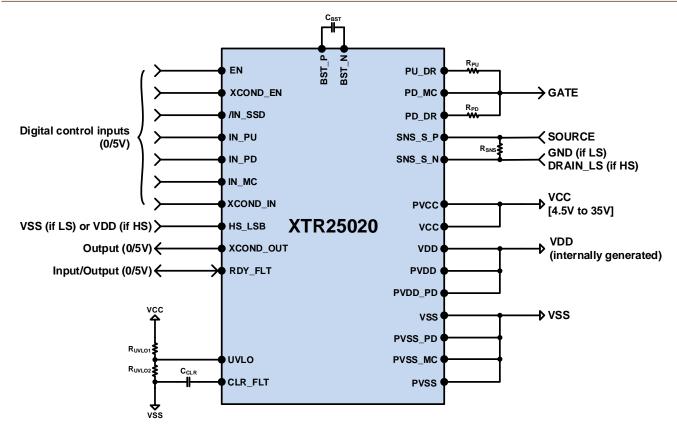

# PIN DESCRIPTION

| Pin number | Name      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | PVSS      | Negative power supply. Connect to <b>VSS</b> through a local plane.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2          | XCOND_IN  | 0/5V Schmitt triggered digital input versus <b>VSS</b> of the cross-conduction information between HS and LS. If this feature is not required, connect this pin to <b>VDD</b> ( <b>HS_LSB</b> must be connected to <b>VDD</b> to be in slave mode).                                                                                                                                                                                                                                             |

| 3          | XCOND_OUT | Open drain output versus VSS (for parallel connection of multiple XTR25020) of the cross-conduction information between HS and LS. If this feature is not required, leave this pin floating (HS_LSB must be connected to VDD to be in slave mode). If no parallel connection of multiple XTR25020 is needed, a second output XCOND_OUTB (only available in die form), can be shorted to XCOND_OUT to have a classical digital output instead of open drain.                                     |

| 4          | XCOND_EN  | 0/5V Schmitt triggered digital input versus <b>VSS</b> to enable, when driven high, internal cross-conduction prevention between pull-up and pull-down drivers. When driven low, the outputs <b>PU_DR</b> , <b>PD_DR</b> , <b>PD_MC</b> are independently controlled by the inputs <b>IN_PU</b> , <b>IN_PD</b> , <b>IN_MC</b> , <b>/IN_SSD</b> , respectively.                                                                                                                                  |

| 5          | EN        | 0/5V Schmitt triggered digital input versus VSS to enable, when driven high, the driver's outputs PU_DR, PD_DR, PD_MC are enabled. When driven low, the outputs PU_DR and SSD drivers are forced to high impedance mode and PD_DR, PD_MC are pulled-down to PVSS_PD and PVSS_MC respectively.                                                                                                                                                                                                   |

| 6          | IN_PU     | Active-high, Schmitt triggered digital input versus <b>VSS</b> for the pull-up driver PU_DR.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7          | IN_PD     | Active-high, Schmitt triggered digital input versus <b>VSS</b> for the pull-down driver PD_DR                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8          | IN_MC     | Active-high, Schmitt triggered digital input versus <b>VSS</b> for the Miller Clamp pull-down driver PD_MC.                                                                                                                                                                                                                                                                                                                                                                                     |

| 9          | /IN_SSD   | Active-low, Schmitt triggered digital input versus <b>VSS</b> for Soft Shut-Down pull-down driver SSD.                                                                                                                                                                                                                                                                                                                                                                                          |

| 10         | HS_LSB    | 0/5V Schmitt triggered digital input versus <b>VSS</b> for driver operation selection as high-side (HS_LSB=1, slave mode) or low-side (HS_LSB=0, master mode).                                                                                                                                                                                                                                                                                                                                  |

| 11         | RDY_FLT   | Open drain input/output giving the "ready" (when it is high) or "fault" (when it is low) information of the circuit. When the XTR25020 is used together with the XTR26020 (or other XTR25020 circuits) this pin must be connected to MRDY pin of the XTR26020 (or to RDY_FLT pin of XTR25020). Indeed, this connection allows to synchronize "ready" or "fault" states between the two circuits to guarantee safe operation. If the XTR25020 is used alone this pin must be kept not connected. |

| 12         | CLR_FLT   | Connect a capacitor between this pin and <b>VSS</b> to define the clear fault time-out. See section Theory of Operation for more details about the use of this pin.                                                                                                                                                                                                                                                                                                                             |

| 13         | VSS       | Most negative supply voltage of the driver (its value depends on the power transistor to be driven). Connect to the reference <b>VSS</b> ground plane of the circuit.                                                                                                                                                                                                                                                                                                                           |

| 14         | VDD       | 5V supply voltage versus <b>VSS</b> generated by the internal LDO and supplying all logic except the output stage of the drivers and the transceiver. Connect to a local <b>VDD</b> plane.                                                                                                                                                                                                                                                                                                      |

| 15         | vcc       | Positive supply voltage of the driver. This voltage must be larger than or equal to the positive supply of the output pull up driver (PVCC). Connect to <b>VCC</b> plane.                                                                                                                                                                                                                                                                                                                       |

| 16         | PVDD_PD   | Top plate of decoupling capacitor of the pull-down (PD_DR) pre-driver. Connect to <b>VDD</b> plane.                                                                                                                                                                                                                                                                                                                                                                                             |

| 17         | UVLO      | Sense node through external resistor divider for the UVLO on VCC pin versus VSS. Voltage on this node is compared to an internal reference of 1.2V versus VSS. If this feature is not required, connect this pin to VDD via a pull-up resistor in the range of $100 \text{k}\Omega$ .                                                                                                                                                                                                           |

| 18         | SNS_S_N   | Negative sense pin of the <b>SOURCE</b> terminal of the power transistor (over-current detection). Connect it to the bottom of the source sense resistor using a Kelvin electrical connection. If the sense current feature is not required, this pin must be shorted with <b>SNS_S_P</b> and connected to <b>VDD</b> plane.                                                                                                                                                                    |

| 19         | SNS_S_P   | Positive sense pin of the <b>SOURCE</b> terminal of the power switch source (over-current detection).  Connect it to the SOURCE of the switching device, on the top of the sense resistor, using a Kelvin electrical connection. If the sense current feature is not required, this pin must be shorted with <b>SNS_S_N</b> and connected to <b>VDD</b> plane.                                                                                                                                  |

| 20         | PD_DR     | Output of the pull-down driver PD_DR with a typical 3A peak drive current.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 21         | PVSS_PD   | Power <b>VSS</b> of the PD_DR driver. Connect to <b>VSS</b> plane.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 22         | PVSS_MC   | Power <b>VSS</b> of the PD_MC driver. Connect to <b>VSS</b> plane.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 23         | PD_MC     | Output of the Miller Clamp pull-down driver with a typical 3A peak drive current.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 24         | PU_DR     | Output of the pull-up driver PU_DR with typical 3A peak drive current.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 25         | PVCC      | Positive supply voltage of PU_DR driver. Connect to local power <b>PVCC</b> plane if different than VCC. Otherwise, connect to VCC plane.                                                                                                                                                                                                                                                                                                                                                       |

| 26         | BST_N     | Negative terminal of the bootstrap capacitor of the PU_DR driver.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 27         | BST_P     | Positive terminal of the bootstrap capacitor of the PU_DR driver.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 28         | PVDD      | 5V supply voltage versus <b>PVSS</b> supplying the transceiver and the low voltage IO ring. Connect to a local power <b>VDD</b> plane.                                                                                                                                                                                                                                                                                                                                                          |

## RECOMMENDED OPERATING CONDITIONS

| Parameter                                                                                       | Min | Тур | Max | Units |

|-------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| High voltage power supply VCC-VSS <sup>1</sup>                                                  | 4.5 |     | 35  | V     |

| High voltage inputs: SNS_S_N, SNS_S_P                                                           | VSS |     | VCC |       |

| High voltage outputs: PU_DR, PD_DR, PD_MC                                                       | VSS |     | VCC |       |

| Low voltage power supply VDD-VSS (generated from internal voltage regulator)                    |     |     | 5.5 | V     |

| Low voltage inputs: EN, XCOND_EN, /IN_SSD, IN_PU, IN_PD, IN_MC, HS_LSB, UVLO, RDY_FLT, XCOND_IN | VSS |     | VDD |       |

| Low voltage outputs: XCOND_OUT, RDY_FLT                                                         |     |     | VDD |       |

| Junction Temperature <sup>2</sup> T <sub>j</sub>                                                | -60 |     | 230 | °C    |

$<sup>^{1}</sup>For\ VCC\text{-}VSS{\leq}5.5V,\ VDD\ must\ be\ shorted\ to\ VCC.$

<sup>&</sup>lt;sup>2</sup> Operation beyond the specified temperature range is achieved.

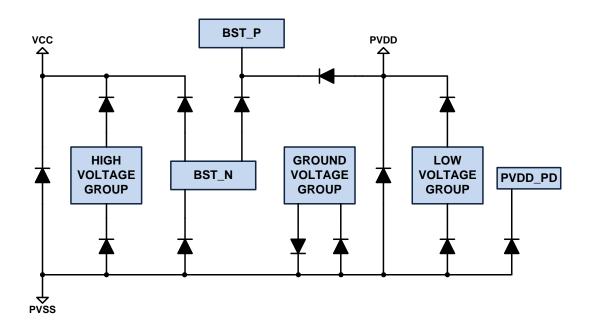

# **ESD CLAMPING SCHEME**

| Pin Groups                | Pins                                                                                           |

|---------------------------|------------------------------------------------------------------------------------------------|

| High voltage power supply | VCC-PVSS                                                                                       |

| High voltage group        | PD_DR, PU_DR, PVCC, SNS_S_N, SNS_S_P, PD_MC, UVLO                                              |

| Low voltage power supply  | PVDD-PVSS                                                                                      |

| Low voltage group         | VDD, RDY_FLT, IN_PU, IN_PD, /IN_SSD, IN_MC, CLR_FLT, HS_LSB, XCOND_IN, XCOND_OUT, XCOND_EN, EN |

| Bootstrap voltages        | BST_N, BST_P                                                                                   |

| Power VDD voltage         | PVDD_PD                                                                                        |

| Ground voltage group      | VSS, PVSS PD, PVSS MC                                                                          |

# **ELECTRICAL SPECIFICATIONS**

Unless otherwise stated, specification applies for VCC-VSS=25V and -60°C $\leq$ T $_{j}$  $\leq$ 230°C.

| Parameter                                | Condition                                                                            | Min  | Тур | Max  | Units        |

|------------------------------------------|--------------------------------------------------------------------------------------|------|-----|------|--------------|

| Supply Voltage                           |                                                                                      |      |     |      |              |

| VCC-VSS <sup>1</sup>                     |                                                                                      | 4.5  |     | 35   | V            |

| Source of power transistor               |                                                                                      | VSS  |     | VCC  | V            |

| Quiescent current consumption            | EN=0                                                                                 |      | 1   |      | mA           |

| e la | XCOND_EN=1 (IN_PU, IN_PD, IN_MC low, and                                             |      | 2   |      |              |

| Fault mode current consumption           | /IN_SSD high)                                                                        |      | 3   |      | mA           |

| Ready mode current consumption           | XCOND_EN=1 (IN_PU, IN_PD, IN_MC low, and                                             |      | 5   |      | mA           |

|                                          | /IN_SSD high)                                                                        |      |     |      |              |

|                                          | In ready mode with 200kHz, 50% duty cycle signal on IN PU, XCOND EN=1, (IN PD, IN MC |      |     |      |              |

| Functional mode current consumption      | and /IN SSD high) 1nF output capacitor on                                            |      | 10  |      | mA           |

| runctional mode current consumption      | driver output (PU_DR, PD_DR, PD_MC), and                                             |      | 10  |      | l IIIA       |

|                                          | HS_LSB high (slave mode).                                                            |      |     |      |              |

| Internal Linear Voltage Regulator (LDO)  | 113_E3B High (Slave Hlode).                                                          |      |     |      | <u> </u>     |

| internal Linear Voltage Regulator (LDO)  | 7V≤VCC-VSS≤35V, 1mA≤I <sub>LOAD</sub> ≤50mA                                          | -5   | T   | +5   | %            |

| Total accuracy                           | ·                                                                                    |      |     |      |              |

| 1                                        | 5.5V≤VCC-VSS≤7V, 1mA≤I <sub>LOAD</sub> ≤30mA                                         | -10  | 1   | +5   | %            |

| Load regulation                          | VCC-VSS=20V, 1mA≤I <sub>LOAD</sub> ≤50mA                                             |      | -1  |      | mV/mA        |

| Line regulation                          | 7V≤VCC-VSS≤35V, I <sub>LOAD</sub> =25mA                                              |      | ±1  |      | %            |

| Output current                           | 7V≤VCC-VSS≤35V                                                                       | 0    |     | 50   | mA           |

|                                          | 5.5V <vcc-vss<7v< td=""><td>0</td><td></td><td>30</td><td>mA</td></vcc-vss<7v<>      | 0    |     | 30   | mA           |

| Output load capacitance                  | 0.01Ω≤ESR≤0.1Ω                                                                       | 0.33 | 1   | 3.3  | μF           |

| UVLO                                     |                                                                                      |      |     |      |              |

| UVLO hysteresis                          |                                                                                      |      | 10  |      | %            |

| Internal comparator reference vs. VSS    |                                                                                      | 1.14 | 1.2 | 1.26 | V            |

| (for UVLO on VCC)                        |                                                                                      | 1.14 | 1.2 | 1.20 |              |

| Internal comparator reference vs. VSS    |                                                                                      |      | 2.0 |      | V            |

| (for UVLO on VDD)                        |                                                                                      |      | 3.9 |      |              |

| Allered in a transfer of 10/10 air       | UVLO pin when clamping at about 5.7V versus                                          |      |     | 1    | ^            |

| Allowed input current on UVLO pin        | VSS.                                                                                 |      |     | 1    | mA           |

| Leakage current on UVLO pin              | 1.14V≤V <sub>UVLO</sub> ≤1.26V                                                       |      |     | 1    | μΑ           |

| Over-current protection between SNS_S_P  | and SNS_S_N                                                                          |      |     |      |              |

| Sense threshold voltage                  |                                                                                      |      | 100 |      | mV           |

| Sense threshold voltage accuracy         |                                                                                      | -20  |     | +20  | %            |

| Sense threshold voltage hysteresis       |                                                                                      |      | 10  |      | %            |

| Driver                                   |                                                                                      |      | '   |      |              |

|                                          | from IN_PU, IN_PD, IN_MC to driver outputs                                           |      | 1   |      |              |

| Propagation delay/channel                | (PU DR, PD DR, PD MC)                                                                |      | 200 |      | ns           |

| Rise time                                | 1nF output capacitor per driver channel                                              |      | 15  |      | ns           |

| Fall time                                | 1nF output capacitor per driver channel                                              |      | 15  |      | ns           |

| Tun time                                 | external cross-conduction protection active                                          | 1    | 13  |      | μs           |

| Minimum ON time t <sub>ON_min</sub>      | without external cross-conduction protection                                         | 0.5  |     |      | μs           |

|                                          | external cross-conduction protection active                                          | 1    |     |      | μs           |

| Minimum OFF time toff_min                | ·                                                                                    | 0.5  | +   |      | <del>'</del> |

| D                                        | without external cross-conduction protection                                         | 0.5  | 1 2 |      | μs           |

| Peak output current of PU_DR driver      | V00 V00 71/2                                                                         |      | 3   |      | -            |

| Continuous output current of PU_DR       | VCC-VSS=7V <sup>2</sup>                                                              |      | 1   |      | A            |

| Peak output current of PD_DR driver      |                                                                                      |      | 3   |      |              |

| Peak output current of PD_MC driver      |                                                                                      |      | 3   |      |              |

| Soft-shutdown transistor R <sub>ON</sub> |                                                                                      | 50   | 100 | 150  | Ω            |

| Control Logic                            |                                                                                      |      |     |      |              |

| High-Level Input Voltage                 |                                                                                      | 4    |     |      |              |

| V <sub>IH</sub>                          | Schmitt triggered inputs (EN, XCOND_EN,                                              | 4    |     |      |              |

| Low-Level Input Voltage                  | /IN_SSD, IN_PU, IN_PD, IN_MC, HS_LSB,                                                |      |     | 1    | V            |

| V <sub>IL</sub>                          | XCOND_IN)                                                                            |      |     |      |              |

| Schmitt triggered input hysteresis       |                                                                                      |      | 2   |      |              |

| Blanking time                            | Internally fixed                                                                     | 0.3  | 0.4 | 0.0  |              |

| t <sub>BLANK</sub>                       | Internally fixed                                                                     | 0.2  | 0.4 | 0.8  | μs           |

| Clear fault time                         | Externally set with C 1-5                                                            |      | 30  |      |              |

| t <sub>CLR_FLT</sub>                     | Externally set with C <sub>CLR</sub> =1nF                                            |      | 30  |      | μs           |

| Miller Clamp activation threshold        |                                                                                      | 0.7  | 1   | 1.45 | V            |

<sup>&</sup>lt;sup>1</sup> For VCC-VSS≤5.5V, pins VDD, PVDD, and PVDD\_PD must be shorted to VCC.

<sup>&</sup>lt;sup>2</sup> Care must be taken with the temperature increase due to the power dissipated in the circuit.

#### THEORY OF OPERATION

#### Introduction

XTR25020 is a high-temperature, high reliability intelligent power transistor driver integrated circuit specifically designed to drive normally-On as well as normally-Off Silicon Carbide (SiC), Gallium Nitride (GaN) and standard silicon power transistors, such as MOSFETs, JFETs, SJTs, BJTs, MESFETs and HEMTs. The XTR25020's main features are:

- Internal 5V linear regulator.

- Cross-conduction protection between high-side and lowside power drivers, which can be disabled for free-control of the three outputs PU\_DR, PD\_DR, PD\_MC through their respective inputs IN\_PU, IN\_PD, IN\_MC.

- Pull-up gate-drive-channel (PU\_DR) capable of sourcing a peak current of 3A.

- Pull-down gate-drive-channel (PD\_DR) capable of sinking 3A peak current.

- Active Miller clamp (AMC) on PD\_MC channel with 3A current capability.

- On-chip soft-shut-down (SSD) capability that slowly shuts down on the PD\_MC output the power transistor in case of fault.

- Rail-to-rail, positive and negative over-current detection on the source terminals of the power transistor.

- Safe start-up through UVLO (Under Voltage Lockout) function.

#### **Truth Table**

|    | INPUTS   |         |       |       |       |                                    | OUT     | TPUTS   |                   |

|----|----------|---------|-------|-------|-------|------------------------------------|---------|---------|-------------------|

| EN | XCOND_EN | /IN_SSD | IN_PU | IN_PD | IN_MC | SSD <sup>1</sup> PU_DR PD_DR PD_MC |         |         |                   |

| 0  | X        | Χ       | X     | X     | X     | HZ                                 | HZ      | PVSS    | PVSS              |

| 1  | 0        | 0/1     | 0/1   | 0/1   | 0/1   | PVSS/HZ                            | HZ/PVCC | HZ/PVSS | HZ/PVSS           |

| 1  | 1        | 0       | Х     | Х     | 0     | PVSS                               | HZ      | HZ      | HZ                |

| 1  | 1        | 0       | Χ     | Х     | 1     | PVSS                               | HZ      | HZ      | PVSS <sup>2</sup> |

| 1  | 1        | 1       | 1     | Х     | X     | HZ                                 | PVCC    | HZ      | HZ                |

| 1  | 1        | 1       | 0     | 0     | X     | HZ                                 | HZ      | HZ      | HZ                |

| 1  | 1        | 1       | 0     | 1     | 0     | HZ                                 | HZ      | PVSS    | HZ                |

| 1  | 1        | 1       | 0     | 1     | 1     | HZ                                 | HZ      | PVSS    | PVSS <sup>2</sup> |

<sup>&</sup>lt;sup>1</sup> The drain of the SDD transistor is connected on chip to PD\_MC pin. For more clarity, it is added as an output in the truth table to show the state of the SSD transistor resulting from the state of the /IN\_SSD input.

#### Operation Modes XCOND\_EN="0"

In this mode, as soon as the power supply is present in the circuit and the EN input is high, the outputs PU\_DR, PD\_DR, and PD\_MC, follow with no condition ("0" corresponds to HZ, and "1" corresponds to PVCC for PU and to PVSS for PD) their respective inputs IN\_PU, IN\_PD, and IN\_MC. For the soft-shut-down (SSD) driver, which has a common output PD\_MC with the Miller Clamp driver, the output is inversed ("0" corresponds to PVSS, and "1" corresponds to HZ) versus its corresponding input /IN\_SSD. If the circuit is in startup phase (not ready) or a "FAULT" state is detected, due to UVLO or over-current, the fault is reported via RDY\_FLT output without any action on the outputs of the driver.

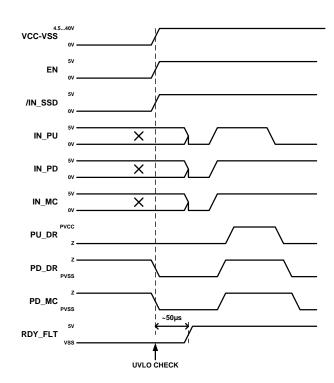

# XCOND\_EN="1" Startup phase

The startup phase is initialized by the turn on of the power supplies of the circuit VCC and VSS. After having enough voltage on the LDO output (around 3V for the logic to be operational), the PD\_DR and PD\_MC outputs are pulled-down to PVSS. This is mandatory to guarantee the charge of the bootstrap capacitor during the startup phase. The following checks are done during the startup phase:

- The UVLO on VCC checks if the power supply value is higher than the externally fixed threshold.

- An internal UVLO on VDD checks if VDD is higher than approximately 4V.

- The output gate is checked if it is close to VSS.

If all those checks are okay, an internal counter with a delay of 50µs is started. This delay secures the correct turn-on of the internal voltage reference. During the startup phase the PD\_DR and PD\_MC drivers outputs are activated for safe normally on start-up, and the input PWM is blanked (If a PWM signal is received, it is not transferred to the driver outputs). At the end of the counter, the signal RDY\_FLT goes to "1" (through internal pull-down resistor of  $10\text{k}\Omega$ ). The circuit enters into the functional phase: if a PWM signal is received, it is transferred to the driver outputs.

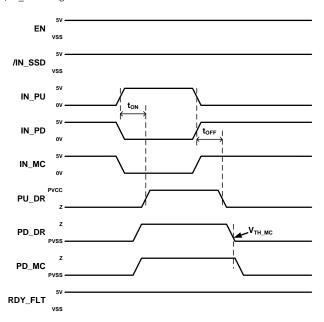

Hereafter is the timing diagram showing the operation of the circuit in startup phase (XCOND\_EN="1").

#### Functional phase

The functional phase starts when the RDY\_FLT output flags a "1". In this phase, the circuit is ready to receive the input signals from the user (PWM controller, microcontroller...).

If the EN and SSD inputs are high, the input signals are transferred after the propagation delays ( $t_{\text{ON}}$  and  $t_{\text{OFF}}$ ) from the inputs IN\_PU, IN\_PD, and IN\_MC, to their respective outputs PU\_DR, PD\_DR, PD\_MC. A minimum non-overlapping (of about 30ns) is guaranteed between PU and PD/MC drivers (PU is master). When the IN\_PU signal turns-off, the PU\_DR is

<sup>&</sup>lt;sup>2</sup> The Miller clamp transistor is activated when node PD\_MC goes under 1V. For PD\_MC above 1V, the miller clamp transistor remains inactive. This ensures that the power transistor being driven is properly turned-off before gate clamping.

turned off after the propagation delay  $t_{OFF}$  and if the IN\_PD is high, the PD\_DR driver is turned-on after the non-overlapping delay. Then, the PD\_MC driver is turned-on after checking the output gate to be close to VSS ( $V_{GATE} < V_{TH_MC} \approx 1V$ ). Note that during this normal operation mode, the soft shut down pull down transistor is always OFF provided that the input /IN\_SSD is high.

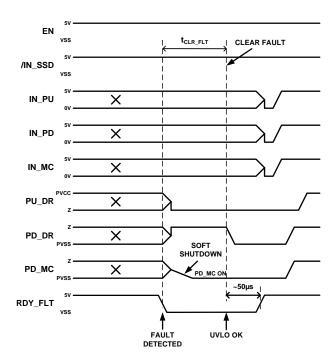

#### Fault phase

The fault phase is initialized if at least one of the following signals flags an error:

- UVLO on VCC supply versus VSS.

- UVLO on VDD versus VSS

- Over-current detection on the source or gate terminal of the power transistor that persists for a time longer than an internal blanking time of about 450ns.

Immediately after fault detection, RDY\_FLT goes to "0". Then, regardless the states of the inputs, the PU\_DR, PD\_DR, and PD\_MC drivers are turned-off and the Soft Shut-Down driver is turned-on. This slowly turns-off the power transistor via the PD\_MC output, which should be directly connected to the gate or base terminal, to avoid high dV/dt and high turn-off current. After checking the output gate to be close to VSS (VGATE<VTH\_MC~1V), the PD\_MC driver is turned-on to strongly maintain the off state.

To get out from this state, two alternatives are possible:

- If the CLR\_FLT pin is shorted to VSS, a power supply reset is necessary to clear the FAULT and initialize a new startup phase.

- If a capacitor C<sub>CLR</sub> is connected between CLR\_FLT pin and VSS, a new startup phase starts after a time-out of t<sub>CLR</sub> <sub>FLT</sub> given by:

#### $t_{\text{CLR\_FLT}} \!\!=\!\! 30 k \Omega^* C_{\text{CLR}}$

If no capacitor is connected the clear fault time out will be given by the parasitic capacitance on pin CLR\_FLT (few pF) times  $30k\Omega$ .

Note that at the first startup of the circuit, when VCC is turning ON, the UVLOs faults are automatically cleared once all supplies are above the defined thresholds. No clear fault event is required in order to operate normally the circuit. However, during operation, if an UVLO event occurs, a clear fault event is required in order to reset the circuit.

#### **Functional Features**

#### Cross conduction protection

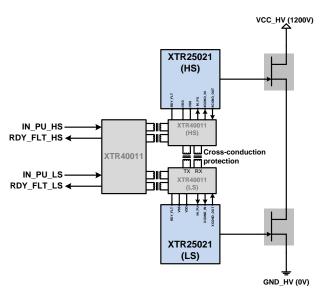

The cross-conduction protection has been implemented to prevent short-circuiting the high voltage power supply through the High Side (HS) and Low Side (LS) power transistors of a half bridge (see figure below).

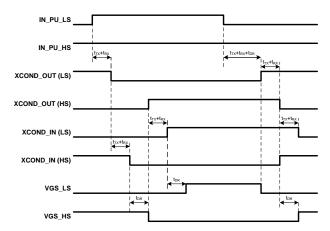

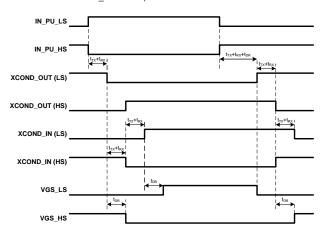

This is achieved through a bidirectional isolated data communication between the XTR25020 set as a HS driver and the XTR25020 set as a LS driver of the half bridge via 2 XTR40010 isolated transceivers. The XTR25020 LS is the master (HS\_LSB input low) and the XTR25020 HS is the slave (HS\_LSB input high). The operation of the cross-conduction protection is shown in the following timing diagrams for two states of the IN\_PU\_HS input:

## • IN\_PU\_HS set to a permanent "1":

When the IN\_PU\_LS signal turns-on, after  $t_{TX}+t_{RX}$  ( $t_{TX}\approx 20ns+50ns$  of Jitter and  $t_{RX}\approx 60ns$ ) delay the XCOND\_OUT (LS) sends a "0" to the XCOND\_IN (HS) which receives it after  $t_{TX}+t_{RX}$  forcing the HS to turn-off its PU\_DR and to turns-on its PD\_DR and then its PD\_MC. This takes  $t_{DR}$  delay ( $t_{DR}$  is composed of the propagation delay through the driver buffer and the rise or fall time). After checking that the gate of the HS power transistor is nearly discharged ( $V_{GATE}<1V$ ) using the PD\_MC pin, the XCOND\_OUT (HS) sends a "1" to the XCOND\_IN (LS) telling that the HS is off and that the LS can safely turn-on

after a delay of  $t_{TX}+t_{RX}$ . Then, the VGS\_LS is turned-on after  $t_{DR}$  delay. Hence, the total turn-off/turn-on delays of the HS/LS are given by:

$$t_{OFF\_HS}=2*(t_{TX}+t_{RX})+t_{DR}$$

$t_{ON\_LS}=3*(t_{TX}+t_{RX})+2*t_{DR}$

These delays include a non-overlapping delay of t<sub>TX</sub>+t<sub>RX</sub>+t<sub>DR</sub>.

When the IN\_PU\_LS signal turns-off, the LS turns-off its PU\_DR and turns-on its PD\_DR and then its PD\_MC after a delay of  $t_{\rm TX}+t_{\rm RX}+t_{\rm DR}$ . After checking that the gate of the LS power transistor is nearly discharged (V\_GATE<1V) using the PD\_MC pin, the XCOND\_OUT (LS) sends a "1" to the XCOND\_IN (HS) telling that the HS can turn-on after  $t_{\rm TX}+t_{\rm RX}$  delay. Finally, the high side turns-on its PU\_DR after  $t_{\rm DR}$  delay. Hence, the total turn-off/turn-on delays of the LS/HS are given by:

$$\begin{aligned} &t_{\text{OFF\_LS}} = t_{\text{TX}} + t_{\text{RX}} + t_{\text{DR}} \\ &t_{\text{ON\_HS}} = 2^*(t_{\text{TX}} + t_{\text{RX}}) + 2^*t_{\text{DR}} \end{aligned}$$

These delays include a non-overlapping delay of t<sub>TX</sub>+t<sub>RX</sub>+t<sub>DR</sub>.

In this case, where IN\_PU\_HS is set to a permanent "1", the pulse transformer that transfers the PWM signal to the XTR25020 HS is not necessary.

IN\_PU\_HS set to IN\_PU\_LS (this could be achieved easily by shorting PU\_IN\_HS to PU\_IN\_LS and setting POL\_TX of the XTR40010\_HS to "1"):

Using complementary signal on IN\_PU\_LS and IN\_PU\_HS, the same operation is obtained as with a permanent "1" on IN\_PU\_HS except that the propagation delay for turn-on from IN\_PU\_LS to VGS\_LS can be reduced by  $t_{\rm TX}+t_{\rm RX}$ . This allows to have the same turn-on delay for HS and LS ( $t_{\rm ON\_HS}=t_{\rm ON\_LS}$ ).

The cross-conduction protection can be disabled if the user wishes to manage it externally. To do this both the HS and LS drivers must be set as

slave (HS\_LSB pin connected to VDD) and the XCOND\_IN must receive a "1" (XCOND\_OUT must be kept floating).

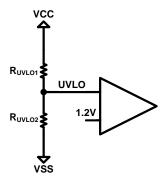

#### Under Voltage Lockout (UVLO) operation

The UVLO block checks the value of the external power supply (VCC-VSS), and the internally generated VDD supply (5V versus VSS). A fraction of VDD value is compared to an internal reference of 1.2V versus VSS and an UVLO\_VDD flag is set to "1" when the VDD reaches about 3.9V. For the external power supplies, the UVLO block compares an externally fixed threshold through a resistor divider to an internal reference of 1.2V versus VSS:

To simplify the equation for the computation of the UVLO threshold voltage  $V_{TH\_UVLO}$ , we consider VSS=0V. The  $V_{TH\_UVLO}$  is obtained in terms of  $R_{UVLO2}$  and  $R_{UVLO2}$  as follows:

$$V_{TH\_UVLO} = \frac{R_{UVLO1} + R_{UVLO2}}{R_{UVLO2}} \cdot 1.2V$$

The current that can be tolerated ( $100\mu A$  for example, it must be high enough compared to leakage current) in the resistor divider can give the value of  $R_{UVLO2}$  using:

$$R_{UVLO2} = \frac{1.2V}{100\mu A} = 12k\Omega$$

Then, for  $V_{TH\_UVLO}$ =15V, the  $R_{UVLO1}$  is obtained:

$$R_{UVLO1} = \left(\frac{V_{TH\_UVLO}}{1.2} - 1\right) \cdot R_{UVLO2} = 138k\Omega$$

The UVLO pin is internally clamped to VDD+0.7V with a maximum current sink of 1mA.

The UVLO thresholds on VDD and VCC have an internal hysteresis of about 10% when the power supply goes down after being up and higher than the UVLO thresholds defined above.

If this feature is not used, the UVLO pin must be pulled-up to VDD.

#### Over-current detection

The source or gate current is permanently measured using the differential voltage between SNS\_S\_P and SNS\_S\_N created by the sense resistor  $R_{SNS}$  and compared to an internal voltage reference of about 100mV. In the case of damage on the poser transistor or due to short-circuit in a half-bridge, the current should be higher than the fixed threshold indicating source failure for the circuit. The source or gate over-current threshold  $I_{TH}$  is given by:

$$I_{TH} = \frac{100 \text{mV}}{R_{SNS}}$$

The current sense is functional at any common-mode voltage between VCC and VSS (rail-to-rail) and for both positive and negative current flowing to or from the source of the power transistor. In order to avoid false over-current detections due to spikes during the switching of the driver outputs, an internal blanking time of about 400ns is implemented.

The current sense comparator can also be used for any other protection purpose such as gate/base current sense for fatigue detection or to implement a thermal shut-down with external temperature sensor.

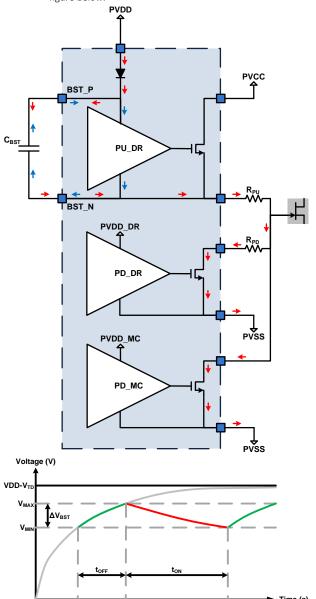

#### Bootstrap capacitors

The bootstrap capacitor value can be selected taking into account two conditions:

The bootstrap capacitor C<sub>BST</sub> is discharged in the PU\_DR driver during the ON time t<sub>ON</sub> as shown by the blue arrows in the figure below.

As shown in the graph above, in steady state, the voltage drop  $\Delta V_{BST}$  on  $C_{BST}$  during discharge (red curve, ON time  $t_{ON})$  is given by:

$$\Delta V_{BST} = (Iq*t_{ON}+C_{eq}*V_{MAX})/C_{BST}$$

Where  $I_Q$ =250µA is the quiescent current delivered from BST\_P to the pull-up driver,  $C_{eq} \approx 500 pF$  is the equivalent capacitor that must be charged by BST\_P up to the voltage  $V_{MAX}$ ,  $t_{ON}$ =1/fr-toff, and  $f_R$  is the PWM frequency.

To have a first guess for  $C_{BST}$ , we consider the extreme values for  $V_{MAX} = VDD - V_{TD}$  ( $V_{TD}$  is the threshold voltage of the bootstrap diode), and  $\Delta V_{BST} = 300 \text{mV}$  to ensure  $V_{MIN} > 4 \text{V}$ , which is the threshold to turn-on the integrated charge pump. Indeed, the integrated charge pump has been designed to be able to maintain the on state permanently (PWM DTC 100%). It is not able to provide enough charge to the bootstrap capacitor when the PWM signal is switching. Therefore, the following condition on  $C_{BST}$  is obtained, which gives a lower limit:

$$C_{BST} > [Iq*t_{ON}+C_{eq}*(VDD-V_{TD})]/\Delta V_{BST}$$

For VDD-V<sub>TD</sub>=4.3V, fr=50kHz, and t<sub>ON</sub>=19 $\mu$ s (t<sub>OFF</sub>=1 $\mu$ s), C<sub>BST</sub> must be higher than 23nF. As this is an extreme value, we recommend taking at least two times this value to reduce the voltage ripple  $\Delta V_{BST}$ .

• The bootstrap capacitor C<sub>BST</sub> is charged for the first time during the startup time given by the rise time of the power supply and the 50µs delay fixed by the startup counter. The charging path is, as described in the figure above with the red arrows, going from the 5V versus VSS power supply PVDD via the integrated bootstrap diode, then the external R<sub>PU</sub>, and finally the PD\_MC driver in parallel with the R<sub>PD</sub> and the PD\_DR driver. Hence, C<sub>BST</sub> must fulfill the following condition to guarantee its total charge during the startup, which gives an upper limit:

$$C_{BST} < 50 \mu s / (3*R_{PU})$$

As the on resistances of the PU, PD, MC transistors are in the range of 1...2 $\Omega$ , they are neglected compared to R<sub>PU</sub> and R<sub>PD</sub>. For R<sub>PU</sub>=20 $\Omega$ , C<sub>BST</sub> must be smaller than 833nF.

In steady state, as shown in the graph above, the voltage drop  $\Delta V_{\text{BST}}$  on  $C_{\text{BST}}$  during the charge (green curve, OFF time  $t_{\text{OFF}}$ ) is given by:

$$\Delta V_{BST} \hspace{-0.05cm}=\hspace{-0.05cm} (VDD \hspace{-0.05cm}-\hspace{-0.05cm} V_{TD} \hspace{-0.05cm}-\hspace{-0.05cm} V_{MIN})^* (1 \hspace{-0.05cm}-\hspace{-0.05cm} \exp[-t_{OFF}/(R_{eq} \hspace{-0.05cm}^* C_{BST})])$$

where  $R_{\text{\scriptsize eq}}$  is given by:

$$\mathsf{Req} = (\mathsf{R}_{\mathsf{PU}} + \mathsf{R}_{\mathsf{PD}})^* \mathsf{t}_{\mathsf{MC}} / \mathsf{t}_{\mathsf{OFF}} + \mathsf{R}_{\mathsf{PU}}^* (\mathsf{t}_{\mathsf{OFF}} - \mathsf{t}_{\mathsf{MC}}) / \mathsf{t}_{\mathsf{OFF}}$$

From the equation of  $\Delta V_{BST}$  during the charge, the following condition on  $R_{eq}$  is obtained:

$$R_{eq} < -t_{OFF}/(C_{BST}*In[1-\Delta V_{BST}/(VDD-V_{TD}-V_{MIN})])$$

For  $V_{\text{MIN}}\!\!=\!\!4V,~t_{\text{MC}}\!\!=\!\!100\text{ns},~t_{\text{OFF}}\!\!=\!\!1\mu\text{s},~\text{and}~C_{\text{BST}}\!\!=\!\!47\text{nF},~R_{\text{eq}}$  must be smaller than 32 $\Omega.$  With  $R_{\text{PU}}\!\!=\!\!R_{\text{PD}}\!\!=\!\!20\Omega$  ( $R_{\text{eq}}\!\!=\!\!22\Omega$ ), fr=50kHz,  $t_{\text{OFF}}\!\!=\!\!1\mu\text{s},~\text{and}~C_{\text{BST}}\!\!=\!\!47\text{nF},$  the following ripple characteristics are obtained:

$$\Delta V_{BST} = 150 \text{mV}$$

$V_{MAX} = 4.21 \text{V}$

$V_{MIN} = 4.06 \text{V}$

## **PACKAGE OUTLINES**

| Part Marking Convention  |                                                                                |  |  |  |  |

|--------------------------|--------------------------------------------------------------------------------|--|--|--|--|

| Part Reference: XTRPPPPP |                                                                                |  |  |  |  |

| XTR                      | X-REL Semiconductor, high-temperature, high-reliability product (XTRM Series). |  |  |  |  |

| PPPPP                    | Part number (0-9, A-Z).                                                        |  |  |  |  |

| Unique Lot As            | Unique Lot Assembly Code: YYWWANN                                              |  |  |  |  |

| YY                       | Two last digits of assembly year (e.g. 11 = 2011).                             |  |  |  |  |

| ww                       | Assembly week (01 to 52).                                                      |  |  |  |  |

| Α                        | Assembly location code.                                                        |  |  |  |  |

| NN                       | Assembly lot code (01 to 99).                                                  |  |  |  |  |

## **IMPORTANT NOTICE & DISCLAIMER**

Information in this document supersedes and replaces all information previously supplied. Information in this document is provided solely in connection with EASii IC products from the X-REL business unit.

The information contained herein is believed to be reliable. EASii IC makes no warranties regarding the information contain herein. EASii IC assumes no responsibility or liability whatsoever for any of the information contained herein. EASii IC assumes no responsibility or liability whatsoever for the use of the information contained herein. The information contained herein is provided "AS IS, WHERE IS" and with all faults, and the entire risk associated with such information is entirely with the user. EASii IC reserves the right to make changes, corrections, modifications or improvements, to this document and the information herein without notice. Customers should obtain and verify the latest relevant information before placing orders for EASii IC products. The information contained herein or any use of such information does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other intellectual property rights, whether with regard to such information itself or anything described by such information.

Unless expressly approved in writing by an authorized representative of EASii IC, EASii IC products are not designed, authorized or warranted for use in military, aircraft, space, lifesaving, or life sustaining applications, nor in products or systems where failure or malfunction may result in personal injury, death, or property or environmental damage.

General Sales Terms & Conditions apply.

For product information and a complete list of distributors, please go to our web site: www.x-relsemi.com

90, Avenue Leon Blum 38100 Grenoble -- France

① : +33 456 580 580

$\ \, \boxtimes \ \, : support.XREL@easii-ic.com$

EASii IC, X-REL Semiconductor, and the logo are trademarks of EASii IC in France and other countries. Data subject to change. Copyright © 2002-2021 EASii IC. All rights reserved.