# FEATURES

- Operational beyond the -60°C to +230°C temperature range.

- Drives P- as well as N-channel MOSFETs (V<sub>GS</sub>=5V).

- Input-to-output stages offset voltage from -30V to +35V.

- Operation as low-side or high-side driver.

- Under Voltage Lockout (UVLO) on PVDD domain.

- Standard Schmitt-trigger CMOS input.

- Plug-and-play with any digital 3.5V to 5V output.

- Up to 1A sink/source current (@ T<sub>j</sub>=+230°C).

- Desaturation protection for both P- and N-channel MOSFETs.

- Soft-shutdown function in case of desaturation detected.

- Error reporting to digital controller.

- Monolithic design.

- Latch-up free.

- Ruggedized ceramic SMD and through hole packages.

- Also available as bare die.

# APPLICATIONS

- Reliability-critical, Automotive, Aeronautics & Aerospace, Downhole.

- DC/DC converters, point-of-load power converters, switching power supplies, PWM control, motor drive, floating or ground-connected switches, Power switches (GaN).

### PRODUCT HIGHLIGHT

### DESCRIPTION

The XTR25410 gate driver family is an extremely flexible floating driver allowing the control of either PMOS or NMOS transistors (V<sub>GS</sub>=5V) and designed for extreme reliability and high temperature applications. XTR25410 is intended to drive both high-side and low-side switches by converting the digital input signal into a floating control signal referenced to PVDD-PGND. The driver operates in both negative and positive configurations with possible offsets between input and output of -30V to +35V.

XTR25410 parts can be directly driven by any digital output, making them fully plug-and-play devices. This driver features full short circuit protection by means of desaturation detection of the external transistor after a blanking time, with soft turn-off feature and reporting the fault through the ERR pin. Undervoltage protections are provided for floating voltage power supplies. The device also includes an Error status output that can be used as an Enable.

Full functionality is guaranteed from  $-60^{\circ}$ C to  $+230^{\circ}$ C, though operation well below and above this temperature range is achieved.

XTR25410 family parts have been designed to reduce system cost and ease adoption by reducing the learning curve and providing smart and easy to use features.

Parts from the XTR25410 family are available in ruggedized SMD and through hole hermetic packages, as well as bare die.

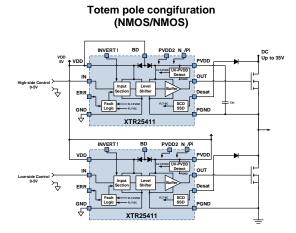

#### Push-pull configuration (PMOS/NMOS)

| ORDERING INFORMATION |  |

|----------------------|--|

|                      |  |

| х            | _   |

|--------------|-----|

| $\mathbf{+}$ | -   |

| Source:      |     |

| X = X-REL Se | emi |

Process: TR = HiTemp, HiRel

TR

25 ↓ Part family

410 ↓ Part number

| Product Reference | Temperature Range | Package                 | Pin Count | Marking  |

|-------------------|-------------------|-------------------------|-----------|----------|

| XTR25410-BD       | -60°C to +230°C   | Bare Die                |           |          |

| XTR25411-D        | -60°C to +230°C   | Ceramic side brazed DIP | 16        | XTR25411 |

Other packages and packaging configurations possible upon request. For some packages or packaging configurations, MOQ may apply.

# ABSOLUTE MAXIMUM RATINGS

| Voltage on IN, ERR, INVERT and VDD to GND -0.5 to 6.0V   Voltage on PVDD to PGND -0.5 to 7.5V |

|-----------------------------------------------------------------------------------------------|

|                                                                                               |

| Voltage on PVDD to PGND -0.5 to 7.5V                                                          |

|                                                                                               |

|                                                                                               |

| Voltage on PGND to GND -30V to 35V                                                            |

| Storage Temperature Range -70°C to +230°C                                                     |

|                                                                                               |

| Operating Junction Temperature Range -70°C to +300°C                                          |

| ESD Classification 1kV HBM MIL-STD-883                                                        |

**Caution:** Stresses beyond those listed in "ABSOLUTE MAXIMUM RATINGS" may cause permanent damage to the device. These are stress ratings only and functionality of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to "ABSOLUTE MAXIMUM RATINGS" conditions for extended periods may permanently affect device reliability.

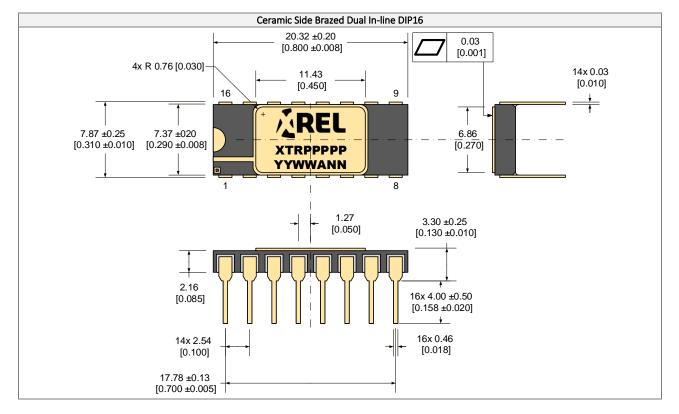

**Ceramic Side Brazed DIP16**

### PACKAGING

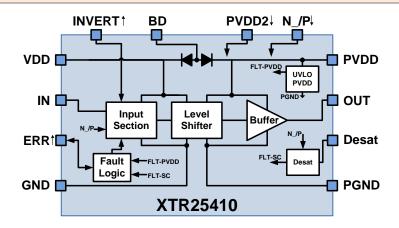

# **BLOCK DIAGRAM**

Arrows aside pin names indicate whether the input is internally pulled up or down.

# **PIN DESCRIPTION**

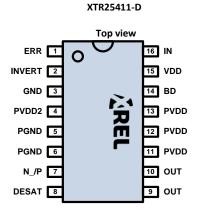

|            | XTR25411 |                                                                                                                                  |  |  |  |  |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Number | Name     | Description                                                                                                                      |  |  |  |  |

| 1          | ERR      | Enable and/or Reporting error. Connect to VDD to disable reporting function. Internal pull-up.                                   |  |  |  |  |

| 2          | INVERT   | Inverting input. Connect to GND to invert output logic. Internal pull-up.                                                        |  |  |  |  |

| 3          | GND      | Ground of input section.                                                                                                         |  |  |  |  |

| 4          | PVDD2    | Auxiliary supply voltage. Connect to PVDD when operating in negative area (PGND <gnd). internal="" pull-down.<="" th=""></gnd).> |  |  |  |  |

| 5          | PGND     | Ground of floating section.                                                                                                      |  |  |  |  |

| 6          | PGND     | Ground of floating section.                                                                                                      |  |  |  |  |

| 7          | N_/P     | Configuration pin. Connect to PVDD to drive PMOS; else NMOS type switch is targeted. Internal pull-down.                         |  |  |  |  |

| 8          | DESAT    | Desaturation detection Input. If not used, connect to PGND (PVDD) when driving NMOS (PMOS).                                      |  |  |  |  |

| 9          | OUT      | Gate drive output.                                                                                                               |  |  |  |  |

| 10         | Ουτ      | Gate drive output.                                                                                                               |  |  |  |  |

| 11         | PVDD     | Supply voltage of power section. Referenced to PGND.                                                                             |  |  |  |  |

| 12         | PVDD     | Supply voltage of power section. Referenced to PGND.                                                                             |  |  |  |  |

| 13         | PVDD     | Supply voltage of power section. Referenced to PGND.                                                                             |  |  |  |  |

| 14         | BD       | Integrated Bootstrap Diode (Anode). Connect to VDD to use the integrated bootstrap diode.                                        |  |  |  |  |

| 15         | VDD      | Supply voltage of the input section. Referenced to GND.                                                                          |  |  |  |  |

| 16         | IN       | Input signal. Referenced to GND.                                                                                                 |  |  |  |  |

# THERMAL CHARACTERISTICS

| Parameter               | Condition | Min | Тур | Max | Units |

|-------------------------|-----------|-----|-----|-----|-------|

| XTR25411-D (DIL16)      |           |     |     |     |       |

| Thermal Resistance: J-C |           |     | 22  |     | °C/W  |

| R <sub>Th_J-C</sub>     |           |     | 22  |     | C/ W  |

| Thermal Resistance: J-A |           |     | 95  |     | °C/W  |

| R <sub>Th_J-A</sub>     |           |     | 93  |     | C/ VV |

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter                                        | Min  | Тур | Max     | Units |

|--------------------------------------------------|------|-----|---------|-------|

| Supply voltage VDD to GND                        | 4.5  | 5   | 5.25    | V     |

| Supply voltage PVDD to PGND                      | 3.55 | 5   | 5.25    | V     |

| Voltage on PGND to GND                           | -30  |     | 35      | V     |

| Voltage on IN to GND                             | -0.3 |     | VDD+0.3 | V     |

| Junction Temperature <sup>1</sup> T <sub>j</sub> | -60  |     | 230     | °C    |

<sup>1</sup> Operation beyond the specified temperature range is achieved

# ELECTRICAL SPECIFICATIONS

### Static Characteristics

Unless otherwise stated, VDD=5V, PVDD=5V (to PGND), IN=0V, -60°C<Tj<230°C.

| Parameter                      | Condition                   | Min | Тур  | Max | Units |

|--------------------------------|-----------------------------|-----|------|-----|-------|

| Supply Current                 | · ·                         | ÷   |      |     |       |

| Static VDD Supply Current      |                             |     |      | 25  |       |

| VDD_Sta                        | V <sub>IN</sub> =GND or VDD |     |      | 25  | μA    |

| Static PVDD Supply Current     | V <sub>IN</sub> =GND or VDD |     |      | 100 |       |

| IPVDD_Sta                      |                             |     |      | 100 | μA    |

| Control INPUT                  |                             |     |      |     |       |

| Input Low voltage              |                             |     | 2.16 | 2   | V     |

| VIL                            |                             |     | 2.10 | 2   | v     |

| Input High voltage             |                             | 3.7 | 3.49 |     | V     |

| VIH                            |                             | 5.7 | 5.49 |     | v     |

| Input current                  | V <sub>IN</sub> =GND or VDD |     |      |     |       |

| In                             | Tj=25°C                     |     |      | 0.1 | nA    |

| IIN                            | Tj=230°C                    |     |      | 50  |       |

| Output Stage                   |                             |     |      |     |       |

| High side static ON resistance | Tj=25°C                     |     | 2.2  |     | Ω     |

| RON <sub>HS</sub>              | T <sub>j</sub> =230°C       |     | 2.2  |     | 12    |

| Low side static ON resistance  | Tj=25°C                     |     | 1.8  |     | Ω     |

| RONLS                          | Tj=230°C                    |     | 1.0  |     |       |

# **ELECTRICAL SPECIFICATIONS (CONTINUED)**

### Dynamic Characteristics

Unless otherwise stated, VDD=5V, PVDD=5V (to PGND), C<sub>LOAD</sub>=0.5nF, -60°C<T<sub>J</sub><230°C.

| Parameter               | Condition                         | Min       | Тур | Max | Units |

|-------------------------|-----------------------------------|-----------|-----|-----|-------|

| Reporting               |                                   | L         |     |     | I     |

| Reporting delay         | Tj=25°C                           |           | 250 |     | ns    |

| tPD_Rep                 | T <sub>j</sub> =230°C             |           | 350 |     |       |

| Disable time            | T <sub>j</sub> =25°C              |           | 1.5 |     | μs    |

| tDisable                | T <sub>j</sub> =230°C             |           | 1.6 |     |       |

| Desaturation Time       |                                   |           |     |     |       |

| Detection Blanking Time | Tj=25°C                           |           | 300 |     |       |

| t <sub>blank</sub>      | T <sub>j</sub> =230°C             |           | 400 |     | ns    |

| SoftShutDown Delay      | Tj=25°C                           |           | 100 |     |       |

| tssd                    | Tj=230°C                          |           | 140 |     | ns    |

| Output Current peak     |                                   | · · · · · |     |     |       |

| Peak current            | T <sub>j</sub> =25°C (10nF load)  |           | 1.5 |     |       |

| lPeak                   | T <sub>j</sub> =230°C (10nF load) |           | 1   |     | A     |

| Soft Turn Off current   | Tj=25°C                           |           | 110 |     | mA    |

| Isoft                   | Tj=230°C                          |           | 80  |     | mA    |

| Switching Time          |                                   |           |     |     |       |

| Delay ON Time           | Tj=25°C                           |           | 158 |     |       |

| td(ON)                  | Tj=230°C                          |           | 283 |     | ns    |

| Rise Time               | Tj=25°C                           |           | 6   |     |       |

| tr                      | Tj=230°C                          |           | 9   |     | ns    |

| Delay OFF Time          | Tj=25°C                           |           | 114 |     |       |

| td(OFF)                 | Tj=230°C                          |           | 192 |     | ns    |

| Fall Time               | Tj=25°C                           |           | 7   |     |       |

| tf                      | Tj=230°C                          |           | 11  |     | ns    |

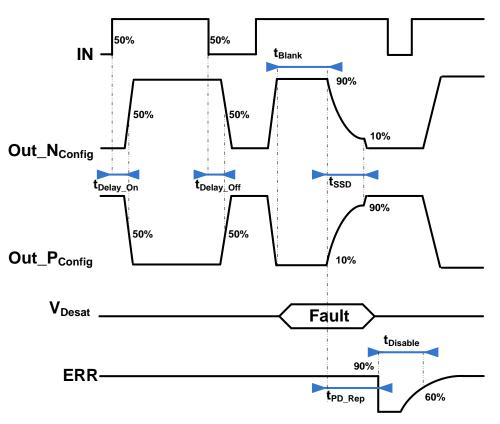

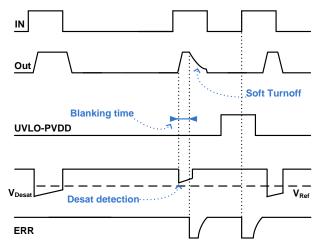

Figure 1. Soft Shutdown and Reporting Error Timing Waveform

Figure 1 shows the Soft Shutdown and error reporting timing waveforms. When OUT is high and  $V_{Desat}$  is higher than  $V_{Ref}$ , a desaturation error is detected. A blanking time ( $t_{Dlank}$ ) is used to avoid false detection when turning ON the external switch. The delay between desaturation detection and the error reporting is called  $t_{rep}$ .

The desaturation process takes t<sub>shut</sub> to smoothly turn OFF the external switch. The shut down time depends upon the characteristics of the gate of the transistor being driven as well as on any gate resistor between the driver's output and the gate of the transistor.

When the error reporting signal disappears, ERR/ENB signal is released (internally pulled up) through an integrated RC circuit producing a dead time called to isable.

# THEORY OF OPERATION

#### Product description

The XTR25410 is a high temperature, high reliability 5V gate driver able to operate from -60°C to 230°C. Depending on packaging options, multiple-versions are available. One important feature of those devices is their ability to shift the 0/5V control signal up to 30V/35V or down to -25V/-30V.

This unique and highly configurable gate driver allows the control of either PMOS or NMOS transistors. It can be used on each high side or low side configuration. Floating power supply (PVDD/PGND) may be positive or negative. At the same time, protection functions are provided as well as reporting errors function.

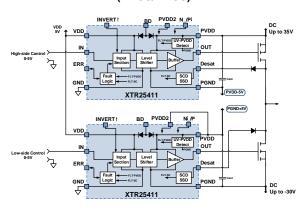

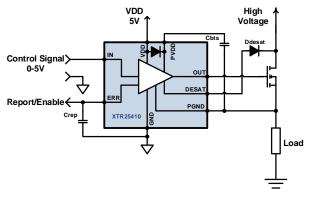

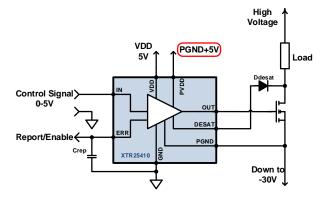

The full featured version is the XTR25411, presented in 16-pin packages (SB DIP). This device is able to drive either NMOS or PMOS transistors with voltage shifts from -30V to 35V.With integrated bootstrap diode, can be used as both high side (Figure 2) and low side drivers.

Figure 2. XTR25410 gate driver used with bootstrap supply on high side configuration

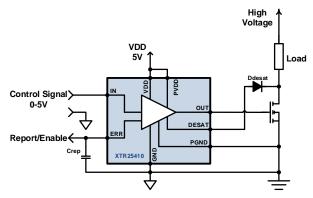

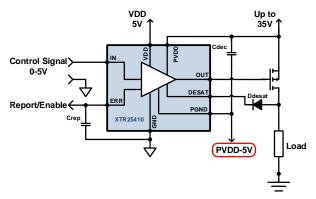

Without integrated bootstrap diode, can be used for positive (Figure 3) or negative (Figure 4) configuration.

Figure 3. XTR25410 gate driver used on positive configuration

#### Figure 4. XTR25410 gate driver used on negative configuration

The XTR25410 can be used as a high side (Figure 5) driver in push-pull configuration. As for the other parts in this driver family, desaturation protection is provided as well as error reporting functionality.

Figure 5. XTR25410 used as high side gate driver

### **Features Description**

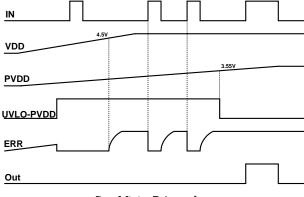

Start-Up

At power supply start-up, ERR signal is pulled down as long as the supply voltage isn't properly established (Figure 6). A minimum supply voltage of 4.5V on VDD is recommended to clear this fault and allow the driver to operate safely. At low supply on PVDD, UVLO on PVDD is reported (ERR signal low) only at the rising edge of IN.

Figure 6. Start-up Timing waveform

#### Normal Operation

After start-up, the ERR signal is set high and the driver is operative. Turning the input signal high to VDD produces output to turn high to PVDD when driving NMOS type load, or low to PGND when driving PMOS type.

Figure 7. Normal Operation Waveform when driving NMOS

#### Under Voltage Lock Out (UVLO)

To assure safe control of the external switch, the UVLO protection disables the driver's output when the floating supply voltage (PVDD vs. PGND) is less than the undervoltage threshold.

The recommended VDD range is between 4.5V and 5.25V. At lower VDD, the circuit could be functional with longer propagation delay.

However, when supply voltages are bellow recommended value, it is guaranteed that the driven load is protected whatever the control signal is (Output signal is low). In this condition, a fault signal is generated (ERR is low).

For PVDD floating side, UVLO condition can't be reported through ERR pin while input control signal is low (Figure 7).

### Desaturation protection

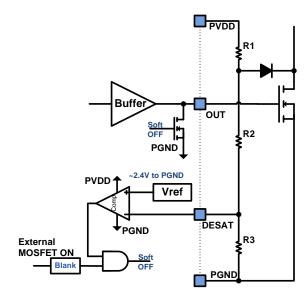

The XTR25410 desaturation circuit monitors the Drain to Source voltage of the driven switch through external diode. This voltage is compared to a reference voltage of 2.4V to PGND (Figure 8).

When desaturation event is detected a Soft Turnoff sequence begins to turn off the driven switch smoothly. This sequence will protect the driver from high dl/dt on the external MOSFET that may cause overvoltage on the driver side and so its destruction.

This protection is available for both PMOS and NMOS configurations.

Figure 8. Desaturation detection circuit

The external desaturation diode should have high breakdown voltage and low capacitance in order to minimize noise coupling and switching delay.

Pull-up resistor R1 is used to allow detection when the drain voltage is lower than PVDD-V<sub>diode</sub>. Typically, it is chosen to be higher than 15k to make sure there is no significant current being drawn from PVDD.

$\mathsf{R2}$  and  $\mathsf{R3}$  are optional resistors that can be used to tune-up the desaturation threshold:

$$V_{DSth} = V_{ref} \times \frac{R2 + R3}{R3} - V_{diode}$$

An example is giving in the following table:

| V <sub>DSth</sub> | R <sub>1</sub> | R <sub>2</sub> | R3   |

|-------------------|----------------|----------------|------|

| 2V                | 15k            | 33k            | 100k |

| 5V                | 15k            | 56k            | 33k  |

| 8V                | 15k            | 150k           | 56k  |

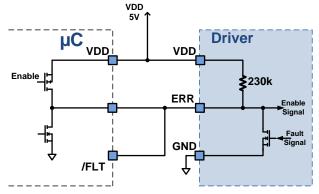

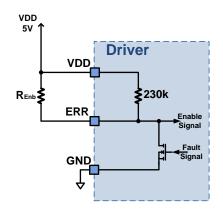

#### Error reporting

ERR pin can be used as an enable pin connected to 0/5V control signal of  $\mu$ C (Figure 9), or pulled up to VDD with an external resistor (Figure 10). A reporting error function is provided with the same pin. When UVLO or Desat errors appears, an integrated pull down set ERR signal to GND. Otherwise, if this function is not needed, ERR pin is set high to VDD (REnb=0 on Figure 10).

Figure 9. Error reporting function used with  $\mu$ C

Figure 10. ERR pin used for enable only

# PACKAGE OUTLINES

Dimensions shown in mm [inches].

|                   | Part Marking Convention                                                        |  |  |

|-------------------|--------------------------------------------------------------------------------|--|--|

| Part Reference: X | Part Reference: XTRPPPPP                                                       |  |  |

| XTR               | X-REL Semiconductor, high-temperature, high-reliability product (XTRM Series). |  |  |

| РРРРР             | Part number (0-9, A-Z).                                                        |  |  |

| Unique Lot Assen  | Unique Lot Assembly Code: YYWWANN                                              |  |  |

| YY                | Two last digits of assembly year (e.g. 11 = 2011).                             |  |  |

| WW                | Assembly week (01 to 52).                                                      |  |  |

| A                 | Assembly location code.                                                        |  |  |

| NN                | Assembly lot code (01 to 99).                                                  |  |  |

# **IMPORTANT NOTICE & DISCLAIMER**

Information in this document supersedes and replaces all information previously supplied. Information in this document is provided solely in connection with EASii IC products from the X-REL business unit.

The information contained herein is believed to be reliable. EASii IC makes no warranties regarding the information contain herein. EASii IC assumes no responsibility or liability whatsoever for any of the information contained herein. EASii IC assumes no responsibility or liability whatsoever for the use of the information contained herein. The information contained herein is provided "AS IS, WHERE IS" and with all faults, and the entire risk associated with such information is entirely with the user. EASii IC reserves the right to make changes, corrections, modifications or improvements, to this document and the information herein without notice. Customers should obtain and verify the latest relevant information before placing orders for EASii IC products. The information contained herein or any use of such information does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other intellectual property rights, whether with regard to such information itself or anything described by such information.

Unless expressly approved in writing by an authorized representative of EASii IC, EASii IC products are not designed, authorized or warranted for use in military, aircraft, space, lifesaving, or life sustaining applications, nor in products or systems where failure or malfunction may result in personal injury, death, or property or environmental damage.

General Sales Terms & Conditions apply.

For product information and a complete list of distributors, please go to our web site: www.x-relsemi.com

90, Avenue Leon Blum 38100 Grenoble -- France(1) : +33 456 580 580(2) : support.XREL@easii-ic.com

EASii IC, X-REL Semiconductor, and the logo are trademarks of EASii IC in France and other countries. Data subject to change. Copyright © 2002-2021 EASii IC. All rights reserved.

CONFIDENTIAL