# **XTR650**

# High Temperature Versatile Timer

Rev 3 – August 2021 (DS-00100-11)

**Data Sheet**

# **PRODUCTION**

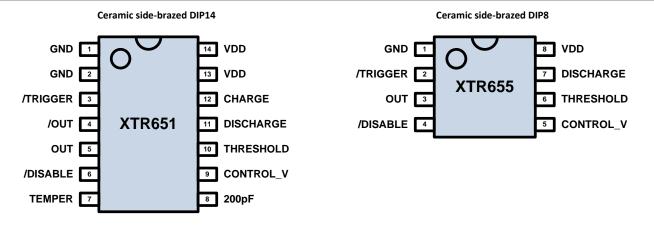

DIP14 XTR651

### **FEATURES**

- Supply voltage from 2.8V to 5.5V.

- Operational beyond the -60°C to +230°C temperature range.

- Monostable, Astable, PWM and PPM modes of operation.

- Complementary, non-overlapping outputs.

- Outputs can source or sink 50mA @ 230°C.

- Complementary high-voltage open-drain outputs.

- XTR655: drop-in replacement of 555.

- DISABLE mode.

- Integrated timing capacitor of 200pF for reduced BoM.

- Integrated coarse temperature sensor.

- Several packaging options including drop-in replacement of 555.

- Latch-up free.

- Ruggedized SMT and thru-hole packages.

# **APPLICATIONS**

- Reliability-critical, Automotive, Aeronautics & Aerospace, Downhole.

- Timing and pulse generation, frequency generation, pulse width modulation (PWM), pulse position modulation (PPM), linear ramp generator.

#### DESCRIPTION

XTR650 is a family of highly stable, small footprint and versatile timers designed for extreme reliability and temperature applications such as accurate time delays or frequency generators. Being able to operate from supply voltages from 2.8V to 5.5V, the XTR650 timers can generate timing periods from some hundreds of nanoseconds and oscillations with duty-cycles from virtually zero to 100%, overcoming the limitations of existing 555.

Other features include the availability of high current complementary and non-overlapping outputs, complementary high-voltage open-drain outputs, integrated timing capacitor of 200pF for reduced bill-of-material (BoM), and integrated coarse temperature sensor.

Especial design techniques were used allowing the XTR650 parts to offer a precise, robust and reliable operation in critical applications. Full functionality is guaranteed from -60°C to +230°C, though operation well below and above this temperature range is achieved.

XTR650 has been designed to reduce system cost and ease adoption by reducing the learning curve and providing smart and easy to use features.

Parts from the XTR650 family are available in ruggedized SMT and thruhole packages.

### **PRODUCT HIGHLIGHT**

### ORDERING INFORMATION

| Product Reference | Temperature Range | Package                | Pin Count | Marking |

|-------------------|-------------------|------------------------|-----------|---------|

| XTR650-TD         | -60°C to +230°C   | Tested bare die        |           |         |

| XTR651-D          | -60°C to +230°C   | Ceramic side braze DIP | 14        | XTR651  |

| XTR655-D          | -60°C to +230°C   | Ceramic side braze DIP | 8         | XTR655  |

Other packages and packaging configurations possible upon request. For some packages or packaging configurations, MOQ may apply.

#### **ABSOLUTE MAXIMUM RATINGS** Voltage to GND CHARGE -35V to VDD+0.5V DISCHARGE -0.5V to 50V All other pins -0.5V to 6.0V -70°C to +230°C Storage Temperature Range -70°C to +300°C **Operating Junction Temperature Range ESD Classification** CHARGE 250V HBM MIL-STD-883 DISCHARGE 500V HBM MIL-STD-883 All other pins 2kV HBM MIL-STD-883

**Caution:** Stresses beyond those listed in "ABSOLUTE MAXIMUM RATINGS" may cause permanent damage to the device. These are stress ratings only and functionality of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to "ABSOLUTE MAXIMUM RATINGS" conditions for extended periods may permanently affect device reliability.

# **PRODUCT VARIANTS**

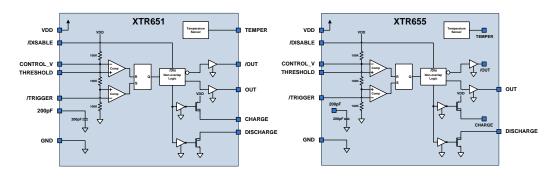

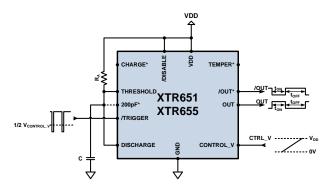

# **BLOCK DIAGRAM**

# PIN DESCRIPTION

| Pin Number Name |        | Namo                  | Description                                                                                          |  |  |

|-----------------|--------|-----------------------|------------------------------------------------------------------------------------------------------|--|--|

| XTR651          | XTR655 | Name                  | Description                                                                                          |  |  |

| 1               | 1      | GND                   | Circuit ground.                                                                                      |  |  |

| 2               | _      | GND                   | Circuit ground.                                                                                      |  |  |

| 3               | 2      | /TRIGGER              | Sets the internal flip-flop when going under 1/3VDD.                                                 |  |  |

| 4               | _      | /OUT                  | Complementary output.                                                                                |  |  |

| 5               | 3      | OUT                   | Main output.                                                                                         |  |  |

| 6               | 4      | /DISABLE <sup>1</sup> | Active LOW disable. Sets the device in the disable state.                                            |  |  |

| 7               | _      | TEMPER                | Coarse temperature sensor. Output voltage decreases as temperature increases.                        |  |  |

| 8               | _      | 200pF                 | Internal timing capacitor. Second terminal is internally grounded.                                   |  |  |

| 9               | 5      | CONTROL_V             | Tap from internal resistor divider. It can be externally forced to change the triggering thresholds. |  |  |

| 10              | 6      | THRESHOLD             | Resets the internal flip-flop when going above 2/3VDD.                                               |  |  |

| 11              | 7      | DISCHARGE             | N-type, open-drain output with respect to GND.                                                       |  |  |

| 12              | _      | CHARGE                | P-type, open-drain output with respect to VDD.                                                       |  |  |

| 13              | _      | VDD                   | Supply voltage.                                                                                      |  |  |

| 14              | 8      | VDD                   | Supply voltage.                                                                                      |  |  |

Table 1. Function Table

| /DISABLE       | THRESHOLD           | /TRIGGER            | ОПТ            | /OUT           | DISCHARGE      | CHARGE         |

|----------------|---------------------|---------------------|----------------|----------------|----------------|----------------|

| L <sup>1</sup> | Don't care          | Don't care          | L              | L              | ON             | OFF            |

| Н              | >2/3V <sub>DD</sub> | Don't care          | L              | Н              | ON             | OFF            |

| Н              | <2/3V <sub>DD</sub> | <1/3V <sub>DD</sub> | Н              | L              | OFF            | ON             |

| Н              | <2/3V <sub>DD</sub> | >1/3V <sub>DD</sub> | Previous state | Previous state | Previous state | Previous state |

$<sup>^1 \</sup>textit{This state does not reset the timer. When recovering from the disable state, outputs will return to their state previous to asserting \textit{/DISABLE=LOW}.}$

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter                                         | Min  | Тур | Max                  | Units |

|---------------------------------------------------|------|-----|----------------------|-------|

| Supply voltage V <sub>DD</sub>                    | 2.8  |     | 5.5                  | V     |

| Voltage on /TRIGGER, THRESHOLD, CONTROL_V, 200PF  | -0.3 |     | V <sub>DD</sub> +0.3 | V     |

| Voltage on <b>DISCHARGE</b> (with respect to GND) |      |     | 40                   | V     |

| Voltage on <b>CHARGE</b> (with respect to VDD)    | -30  |     |                      | V     |

| Maximum operating frequency Fo                    |      | 4   |                      | MHz   |

| Junction Temperature <sup>1</sup>                 | -60  |     | 230                  | °C    |

$<sup>^{1}\,</sup>$  Operation beyond the specified temperature range is achieved.

# **ELECTRICAL SPECIFICATIONS**

Unless otherwise stated, specification applies for  $V_{DD}=5V$ ,  $-60^{\circ}C< T_{j}< 230^{\circ}C$ .

| Parameter                      | Condition                                   | Min | Тур      | Max | Units            |

|--------------------------------|---------------------------------------------|-----|----------|-----|------------------|

| Supply                         |                                             | ·   |          |     |                  |

| Supply voltage                 |                                             | 2.0 |          |     | V                |

| $V_{DD}$                       |                                             | 2.8 |          | 5.5 | V                |

| Supply current                 | $R_A=R_B=\infty$                            |     | 170      | 250 |                  |

| loo                            |                                             |     | 170      | 230 | μΑ               |

| Complementary Output Stage (   | OUT, /OUT)                                  |     |          |     |                  |

| Peak output current            |                                             |     |          |     |                  |

| (source or sink)               | T <sub>j</sub> =230°C                       | ±50 |          |     | mA               |

| lopk                           |                                             |     |          |     |                  |

| Pull-up output resistance      | Output sourcing 10mA. T <sub>i</sub> =230°C |     |          | 40  | [?]              |

| Roн                            | Output sourcing forms. I)=230 C             |     |          | 70  |                  |

| Pull-down output resistance    | Output sinking 10mA. T <sub>i</sub> =230°C  |     |          | 35  | ?                |

| RoL                            | ,                                           |     |          | 33  |                  |

| Open Drain Outputs (CHARGE, I  | DISCHARGE)                                  |     |          |     |                  |

| Maximum DISCHARGE              |                                             |     |          |     |                  |

| voltage                        | With respect to GND                         |     |          | 40  | V                |

| VDISCHMax                      |                                             |     |          |     |                  |

| DISCHARGE switch               | V <sub>DISCH</sub> =500mV                   |     |          |     |                  |

| on-state resistance            | T <sub>j</sub> =150°C                       |     | 17       |     | ?                |

| Rdischon                       | T <sub>j</sub> =230°C                       |     | 20       |     | E E              |

| DISCHARGE switch               | V <sub>DISCH</sub> =V <sub>DD</sub>         |     |          |     |                  |

| off-state leakage current      | T <sub>j</sub> =150°C                       |     | 0.02     |     | μΑ               |

| DISCHOFF                       | T <sub>j</sub> =230°C                       |     | 1        |     |                  |

| Minimum CHARGE                 |                                             |     |          |     |                  |

| voltage                        | With respect to VDD                         | -30 |          |     | V                |

| V <sub>CHMax</sub>             |                                             |     |          |     |                  |

| CHARGE switch                  | VDD-V <sub>CH</sub> =500mV                  |     |          |     |                  |

| on-state resistance            | T <sub>i</sub> =150°C                       |     | 28       |     |                  |

| R <sub>CHON</sub>              | T <sub>i</sub> =230°C                       |     | 35       |     | ?                |

| CHARGE switch                  | V <sub>CH</sub> =0V (GND)                   |     |          |     |                  |

| off-state leakage current      | T <sub>i</sub> =150°C                       |     | 0.150    |     | μΑ               |

| ICHOFF                         | T <sub>i</sub> =230°C                       |     | 7        |     | ļ                |

| Tripping Voltages              | 1 *                                         |     | <u> </u> |     |                  |

| Control voltage                |                                             |     |          |     |                  |

| (open circuit)                 | 2.8V <v<sub>DD&lt;5.5V</v<sub>              |     | 66.7     |     | %V <sub>DD</sub> |

| Vcv                            |                                             |     |          |     |                  |

| Control voltage operating      |                                             |     |          |     |                  |

| range                          | 2.8V <v<sub>DD&lt;5.5V</v<sub>              | 1.7 |          | VDD | V                |

| Vcontrol_v                     |                                             |     |          |     |                  |

| Threshold voltage <sup>1</sup> | 2.0\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\     |     | 66.7     |     | 0/1/             |

| V <sub>TH</sub>                | 2.8V <v<sub>DD&lt;5.5V</v<sub>              |     | 66.7     |     | %V <sub>DD</sub> |

| Trigger voltage <sup>2</sup>   | 2.8V <v<sub>DD&lt;5.5V</v<sub>              |     | 33.3     |     | %V <sub>DD</sub> |

| $V_{TR}$                       | 1 / AV< VDDS > >V                           | 1   | 1 333    |     |                  |

<sup>&</sup>lt;sup>1</sup> The tripping voltage of the THRESHOLD input is equal to the voltage applied on the CONTROL\_V pin.

$<sup>^2</sup>$  The tripping voltage of the /TRIGGER input is equal to half the voltage applied on the CONTROL\_V pin.

# **ELECTRICAL SPECIFICATIONS (CONTINUED)**

Unless otherwise stated, specification applies for  $V_{DD}=5V$ ,  $-60^{\circ}C< T_{J}< 230^{\circ}C$ .

| Parameter                          | Condition                                                             | Min | Тур  | Max | Units                                 |

|------------------------------------|-----------------------------------------------------------------------|-----|------|-----|---------------------------------------|

| Internal Timing Capacitor (20      | 00pF)                                                                 |     |      |     |                                       |

| Capacitor value                    |                                                                       | 170 | 200  | 230 | pF                                    |

| CINT                               |                                                                       | 170 | 200  | 230 | þr.                                   |

| Leakage current                    | V <sub>DD</sub> =5V                                                   |     | 50   |     | nA                                    |

| ICINT                              | T <sub>j</sub> =230°C                                                 |     | 30   |     | l IIA                                 |

| Temperature Sensor (TEMPE          |                                                                       |     |      |     |                                       |

|                                    | T <sub>j</sub> =-60°C                                                 |     | 1.75 |     |                                       |

| Output voltage                     | T <sub>j</sub> =25°C                                                  |     | 1.50 |     | V                                     |

| V <sub>TEMP</sub>                  | T <sub>j</sub> =150°C                                                 |     | 1.11 |     | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

|                                    | T <sub>j</sub> =230°C                                                 |     | 0.85 |     |                                       |

| <b>Dynamic Timing Characterist</b> | tics                                                                  |     |      |     |                                       |

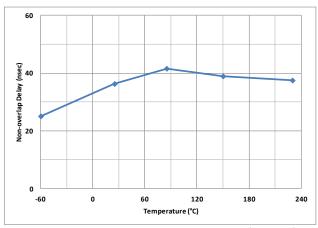

| Non-overlap time                   | Time from OUT (/OUT) going down to /OUT (OUT) going up.               | 20  | 45   | 80  | nsec                                  |

| t <sub>no</sub>                    | OUT and /OUT loaded with 100pF                                        | 20  | 45   | 80  | 11300                                 |

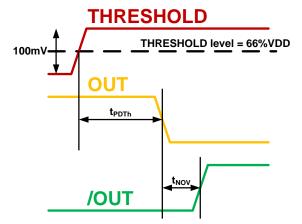

| THRESHOLD to OUT                   |                                                                       |     |      |     |                                       |

| propagation delay                  | OUT and /OUT loaded with 100pF                                        |     | 250  | 290 | nsec                                  |

| t <sub>PDTh</sub>                  |                                                                       |     |      |     |                                       |

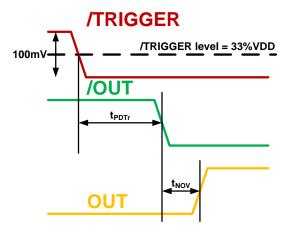

| /TRIGGER to /OUT                   |                                                                       |     |      |     |                                       |

| propagation delay                  | OUT and /OUT loaded with 100pF                                        |     | 105  | 150 | nsec                                  |

| t <sub>PDTr</sub>                  |                                                                       |     |      |     |                                       |

| Astable Configuration              |                                                                       |     |      |     |                                       |

| Initial accuracy                   | $R_A = R_B = 1 k\Omega$ to $1 M\Omega$ , C=10nF, $T_j = 85^{\circ}$ C |     | -2.5 |     | %                                     |

| Drift with temperature             | $R_A=R_B=1k\Omega$ to $1M\Omega$ , $C=10nF$                           |     | -130 |     | ppm/°C                                |

|                                    | $R_A=R_B=1k\Omega$ to $1M\Omega$ , $C=10nF$                           |     |      |     |                                       |

| Drift with supply voltage          | 2.8V <v<sub>DD&lt;5.5V</v<sub>                                        |     | 1    |     |                                       |

| ziiic miii sappi, voitage          | 4.5V <v<sub>DD&lt;5.5V</v<sub>                                        |     | 0.3  |     | %/V                                   |

| Monostable Configuration           |                                                                       |     |      | I.  |                                       |

| Initial accuracy                   | $R_A=1k\Omega$ to $1M\Omega$ , $C=10nF$                               |     | -2   |     | %                                     |

|                                    | .,,                                                                   |     | -    |     | 1,0                                   |

| Drift with temperature             | $R_A=1k\Omega$ to $1M\Omega$ , $C=10nF$                               |     | -150 |     | ppm/°C                                |

| Drift with supply voltage          | $R_A$ =1k $\Omega$ to 1M $\Omega$ , C=10nF                            |     | 1    |     | %/V                                   |

| Difft with supply voltage          | 2.8V <v<sub>DD&lt;5.5V</v<sub>                                        |     | 1    |     | /0/ V                                 |

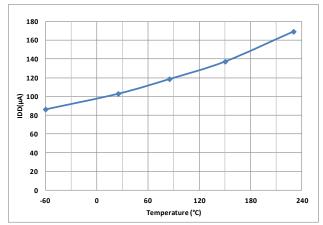

# TYPICAL PERFORMANCE

Figure 1. Quiescent Supply Current vs. Temperature for V<sub>DD</sub>=5.5V.

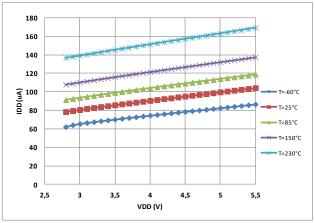

Figure 2. Quiescent Supply Current vs. Supply Voltage ( $V_{\text{DD}}$ ) for different temperatures.

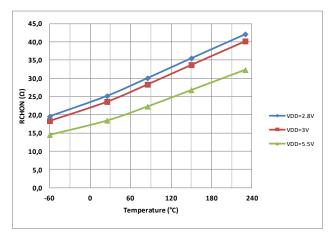

Figure 3. Charge Transistor On-resistance vs. Temperature for different supply voltages.  $V_{\text{DD}}$ - $V_{\text{CH}}$ =0.5V.

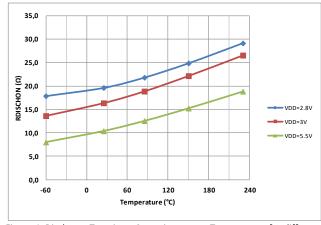

Figure 4. Discharge Transistor On-resistance vs. Temperature for different supply voltages.  $V_{\text{DISCH}}$ =0.5V.

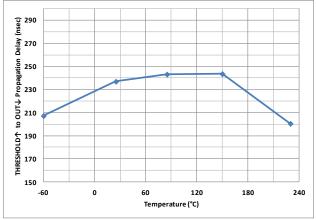

Figure 5. THRESHOLD  $\uparrow$  to OUT  $\downarrow$  propagation delay vs. Temperature: t<sub>PDTh</sub> (50%-50%). OUT and /OUT loaded with 100pF. V<sub>DD</sub>=5.0V. **Erreur!** Source du renvoi introuvable.

# TYPICAL PERFORMANCE (CONTINUED)

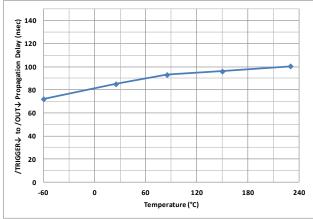

Figure 6. /TRIGGER  $\downarrow$  to /OUT  $\downarrow$  propagation delays vs. Temperature:  $t_{PDTr}$  (50%-50%). OUT and /OUT loaded with 100pF.  $V_{DD}$ =5.0V.

Figure 7. Non-overlap delay vs. Temperature:  $t_{no}$  (OUT to /OUT and /OUT to OUT, 50%-50%). OUT and /OUT loaded with 100pF.  $V_{DD}$ =5.0V.

### TYPICAL PERFORMANCE (CONTINUED)

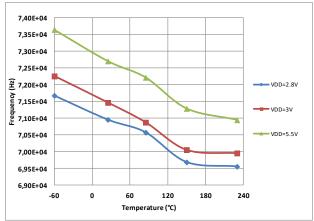

Figure 8. Oscillation frequency in a stable mode vs. Temperature.  $R_A\!\!=\!\!1k$  ,  $R_B\!\!=\!\!1k$  ,  $C\!\!=\!\!9.7nF$  .

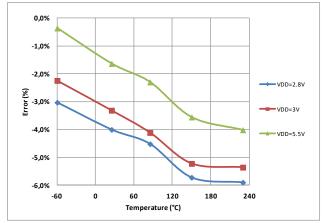

Figure 9. Error of oscillation frequency in a stable mode vs. Temperature with respect to the theoretical value.  $R_A=1k$ ,  $R_B=1k$ , C=9.7nF.

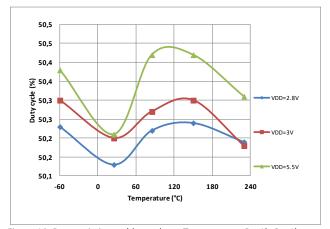

Figure 10. Duty-ratio in a stable mode vs. Temperature. R<sub>A</sub>=1k, R<sub>B</sub>=1k, C=9.7nF.

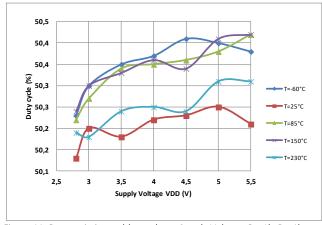

Figure 11. Duty-ratio in a stable mode vs. Supply Voltage.  $R_{A}\!\!=\!\!1k,\,R_{B}\!\!=\!\!1k,\,C\!\!=\!\!9.7nF.$

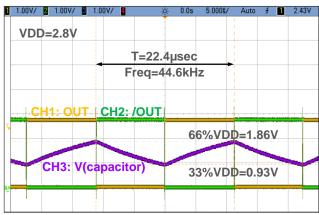

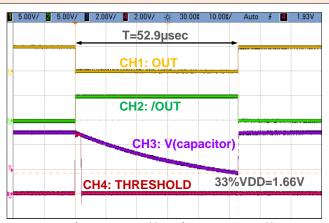

Figure 12. Waveforms in a stable configuration.  $V_{DD}$ =2.8V, Ra=15k, Rb=15k, C=1.06nF.

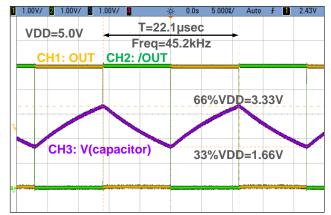

Figure 13. Waveforms in a stable configuration.  $V_{DD}$ =5.0V, Ra=15k, Rb=15k, C=1.06nF.

# TYPICAL PERFORMANCE (CONTINUED)

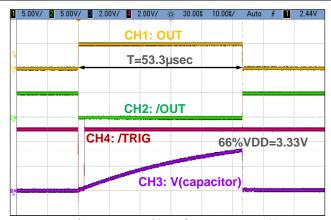

Figure 14. Waveforms in monostable configuration. Triggered by a negative going trigger signal applied on /TRIGGER (see Figure 20).  $V_{DD}$ =5.0V,  $R_A$ =15k, C=1.06nF.

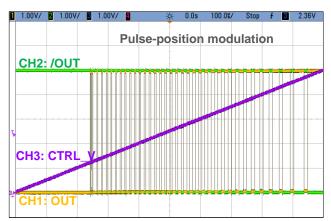

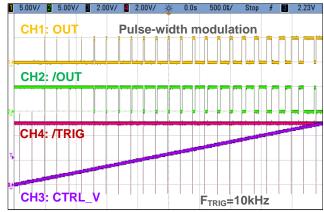

Figure 16. Waveforms in Pulse Position Modulation (PPM): astable configuration with modulating signal on CONTROL\_V (see Figure 22).  $V_{DD}$ =5.0V,  $R_A$ = $R_B$ =15k, C=1.06nF.

Figure 15. Waveforms in monostable configuration. Triggered by a positive going trigger signal applied on THRESHOLD (see Figure 21).  $V_{DD}$ =5.0V,  $R_A$ =15k, C=1.06nF.

Figure 17. Waveforms in Pulse Width Modulation (PWM): externally retriggered monostable configuration with modulating signal on CONTROL\_V (see Figure 23).  $V_{DD}$ =5.0V,  $F_{TRIG}$ =10kHz,  $R_A$ = $R_B$ =15k, C=1.06nF.

# **TEST CIRCUIT CONFIGURATION**

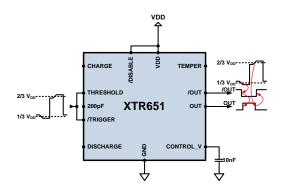

Figure 18. Test circuit used for propagation delay and non-overlap time measurements.

Figure 19. Test circuit used for astable oscillation.

Figure 20. Test circuit for monostable configuration with negative going trigger signal applied on /TRIGGER.

Figure 21. Test circuit for monostable configuration with positive going trigger signal applied on THRESHOLD.

Figure 22. Test circuit for Pulse Position Modulation (PPM): astable configuration with modulating signal on CONTROL\_V.

Figure 23. Test circuit for Pulse Width Modulation (PWM): externally retriggered monostable configuration with modulating signal on CONTROL\_V.

#### THEORY OF OPERATION

#### Introduction

The XTR650 is a family of versatile timers able to operate from  $-60^{\circ}\text{C}$  to  $+230^{\circ}\text{C}$ , with supply voltages from 2.8V to 5.5V. It can operate as astable, monostable, pulse-width modulator and pulse-position modulator.

Packaging configuration XTR655 can be used as a drop-in replacement of the well-known 555. The only difference in the functionality of XTR655 and another commercial 555 concerns the behavior when /DISABLE of the XTR655 is pulled LOW. In the XTR655, the disabled state does not reset the timer. When recovering from the disabled state, outputs will return to their state previous to asserting /DISABLE=LOW or to those determined by the state of THRESHOLD and /TRIGGER.

The XTR650 offers several other packaging configurations allowing the use of the XTR650 specific features.

XTR650 design presents a symmetry with respect to VDD/GND. This feature is implemented by the inclusion of complementary outputs (OUT and /OUT) as well as complementary high-voltage open-drain switches (CHARGE and DISCHARGE). This symmetry allows the XTR650 to implement monostable configurations which can be triggered with either falling or rising edges, circumventing the limitation of the standard 555. Additionally, as only one resistor is used as charge or discharge path of the timing capacitor when operating in astable mode, the output duty cycle can be selected from virtually zero to 100%, which also circumvents a limitation of the standard 555.

# Operation Modes

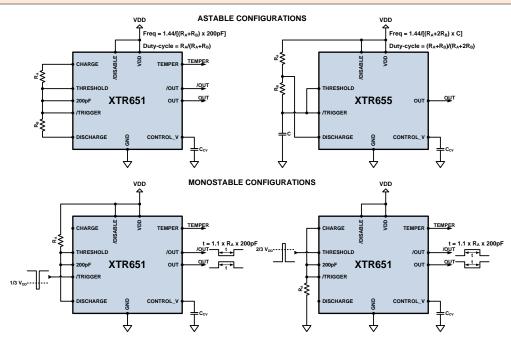

#### Astable Modes

Astable configurations can be implemented in several ways. The principle of the astable configuration is to periodically charge and discharge a capacitor (internal or external) between two fixed levels. In XTR650 parts, as well as in any "555" part, the timing capacitor charges and discharges between the threshold ( $\approx\!2/3V_{DD}$ ) and trigger ( $\approx\!1/3V_{DD}$ ) levels. As the timing capacitor charges, the output remains at the HIGH state for a period equal to  $t_{ON}$ . When the voltage on the capacitor reaches  $2/3V_{DD}$ , the output pin goes down and remains LOW for toppe seconds. During this period, the capacitor is discharged until its voltage reaches  $1/3V_{DD}$ . At this moment, the output goes up to  $V_{DD}$  and the capacitor starts charging again starting a new oscillation cycle.

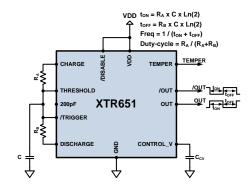

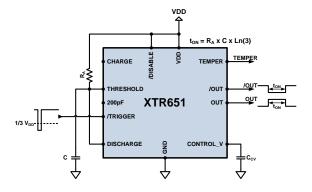

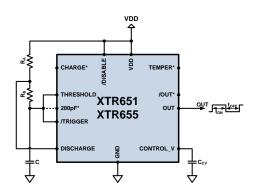

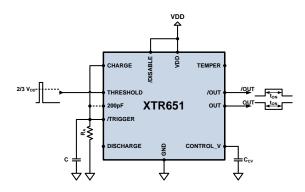

The most known astable, though not the most flexible, is the standard one used with the "555" where a capacitor is charged and discharged through two distinct current paths. The "charge" path uses  $R_A$  in series with  $R_B$ , whereas the "discharge" path uses only  $R_B$ . This configuration can be implemented with both XTR651 and XTR655 parts as shown in the figure below. Pins marked with asterisk (\*) are only present in the XTR651 and can be left floating in this configuration, though it is recommended to connect CHARGE and 200pF pins to  $V_{DD}$ . Notice that the internal 200pF capacitor can be used as timing capacitor.

The timing equations are the following:

$$\begin{aligned} t_{ON} &= Ln2 \cdot (R_A + R_B) \cdot C \\ t_{OFF} &= Ln2 \cdot R_B \cdot C \\ t &= t_{ON} + t_{OFF} \end{aligned}$$

$$Freq = \frac{1}{t} = \frac{1}{Ln2 \cdot (R_A + 2R_B) \cdot C} \approx \frac{1.44}{(R_A + 2R_B) \cdot C}$$

$$Duty-cycle = \frac{t_{ON}}{t_{ON}+t_{OFF}} = \frac{R_A+R_B}{R_A+2R_B} > 50\%$$

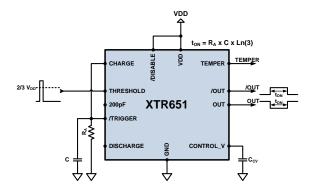

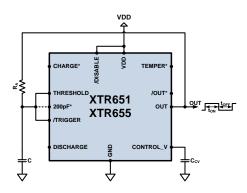

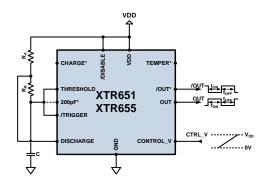

Another possibility is to implement a single resistor configuration as shown in the image below, where the same resistor is used in the "charge" and "discharge" paths. As in the previous case, the internal 200pF capacitor can be used as timing capacitor and CHARGE and DISCHARGE can be left floating if not used. However, it is recommended to connect CHARGE to VDD and DISCHARGE to GND in order to reduce noise.

The timing equations in this configuration are:

$$\begin{split} t_{ON} &= Ln2 \cdot R_A \cdot C \\ t_{OFF} &= Ln2 \cdot R_A \cdot C \\ t &= t_{ON} + t_{OFF} \end{split}$$

$$Freq = \frac{1}{t} = \frac{1}{Ln2 \cdot 2R_A \cdot C} \approx \frac{0.72}{R_A \cdot C}$$

$$Duty - cycle = \frac{t_{ON}}{t_{ON} + t_{OFF}} = \frac{R_A}{2R_A} = 50\%$$

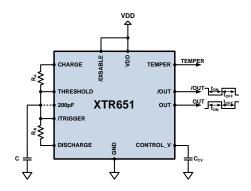

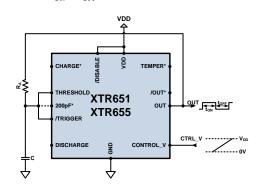

A more flexible astable configuration can be implemented with the XTR651 versions. This configuration uses two resistors, each used only in either the charge or discharge path of the timing capacitor. The timing capacitor can be internal (200pF), external or a combination of the internal and external one.

The timing equations in this configuration are:

$t_{ON} = Ln2 \cdot R_A \cdot C$

$$\begin{aligned} t_{OFF}^{o} &= Ln2 \cdot R_B \cdot C \\ t &= t_{ON} + t_{OFF} \end{aligned}$$

$$Freq = \frac{1}{t} = \frac{1}{Ln2 \cdot (R_A + R_B) \cdot C} \approx \frac{1.44}{(R_A + R_B) \cdot C}$$

$$Duty - cycle = \frac{t_{ON}}{t_{ON} + t_{OFF}} = \frac{R_A}{R_A + R_B}$$

Notice that in the last a stable configuration the oscillation frequency depends only on  $(R_A \! + \! R_B)$  and C whereas the duty-cycle can be chosen to

be any value, from virtually 0% to 100%, by selecting the appropriate  $R_{\text{A}},$  provided that  $R_{\text{A}} + R_{\text{B}}$  remains constant.

In all astable configurations the duty-cycle is independent of the value of the timing capacitor.

### Monostable Modes

Two simple monostable configurations can be implemented with the XTR651. One of these configurations is identical to that implemented with any 555. A second monostable configuration is derived from the previous one, and makes use of the symmetry of the XTR651 structure. These two configurations can be seen as the complementary from each other. In both cases, the timing capacitor charges and discharges through a single resistor R<sub>A</sub>.

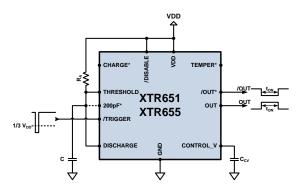

In the first configuration, initially output OUT is LOW (/OUT is HIGH) and the timing capacitor is discharged. When /TRIGGER is shortly pulled under  $1/3V_{\rm DD}$ , OUT goes HIGH (/OUT goes LOW) and the timing capacitor starts charging to  $V_{\rm DD}$  through  $R_{\rm A}$ . When the voltage on the timing capacitor reaches  $2/3V_{\rm DD}$ , the internal flip-flop is reset and the DISCHARGE switch shorts the capacitor to GND. In this case OUT presents a positive pulse and /OUT presents a negative pulse. This configuration can also be implemented with an XTR655. In the figure below, pins marked with an asterisk (\*) are available only in the XTR651 version.

In the second configuration, initially output OUT is HIGH (/OUT is LOW) and the timing capacitor is fully charged to  $V_{\rm DD}.$  When THRESHOLD is shortly pulled above  $2/3V_{\rm DD},$  OUT goes to LOW (/OUT goes HIGH) and the timing capacitor starts discharging to GND through  $R_{\rm A}.$  When the voltage on the timing capacitor reaches  $1/3V_{\rm DD},$  the internal flip-flop is set and the CHARGE switch shorts the capacitor to  $V_{\rm DD}.$  In this case OUT presents a negative pulse and /OUT presents a positive pulse.

In both monostable configurations the timing period lasts

$$t_{ON} = Ln3 \cdot R_A \cdot C \approx 1.1 \cdot R_A \cdot C$$

#### **Applications**

#### Pulse Position Modulation (PPM) Generator

A pulse position modulator is a system that generates a fixed width pulse (positive or negative) with a varying total period (frequency) which depends upon the value of a modulating signal.

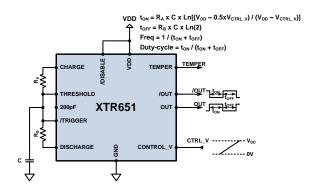

This modulator can be derived from the astable configuration, where the modulating signal is provided through the CONTROL\_V pin. Any of the three astable configurations presented above can be used. What changes among these configurations is the dependence of the ON-time upon the control voltage.

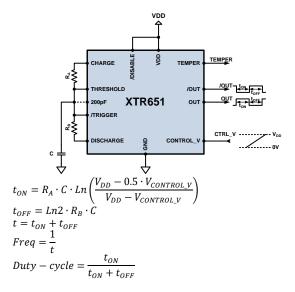

Below are shown the different astable configurations and the associated timing equations. In the figures below, pins marked with an asterisk (\*) are only available in the XTR651 version.

$$\begin{split} &t_{\text{ON}} = (R_{\text{A}} + R_{\text{B}}) \cdot C \cdot Ln \left( \frac{V_{\text{DD}} - 0.5 \cdot V_{\text{CONTROL\_V}}}{V_{\text{DD}} - V_{\text{CONTROL\_V}}} \right) \\ &t_{\text{OFF}} = Ln2 \cdot R_{\text{B}} \cdot C \\ &t = t_{\text{ON}} + t_{\text{OFF}} \\ &\text{Freq} = \frac{1}{t} \\ &\text{Duty} - \text{cycle} = \frac{t_{\text{ON}}}{t_{\text{ON}} + t_{\text{OFF}}} \end{split}$$

$$\begin{split} t_{ON} &= R_{A} \cdot C \cdot Ln \left( \frac{V_{DD} - 0.5 \cdot V_{CONTROL\_V}}{V_{DD} - V_{CONTROL\_V}} \right) \\ t_{OFF} &= Ln2 \cdot R_{A} \cdot C \\ t &= t_{ON} + t_{OFF} \\ Freq &= \frac{1}{t} \\ Duty - cycle &= \frac{t_{ON}}{t_{ON} + t_{OFF}} \end{split}$$

Notice that in this configuration the duty-cycle is independent of the timing resistor and capacitor.

12

In all PPM generators presented the OFF-time does not depend on the modulation voltage.

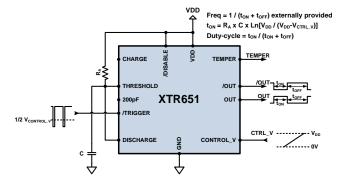

#### Pulse Width Modulation (PWM) Generator

A pulse width modulator is a system that generates a fixed frequency signal with duty-cycle depending upon a modulating signal.

This modulator can be implemented based on the standard monostable configuration triggered in a periodic manner by an external fixed frequency source, where the modulating signal is provided through the CONTROL\_V pin.

$$\begin{aligned} Freq &= \frac{1}{t} \\ t_{ON} &= R_A \cdot C \cdot Ln \left( \frac{V_{DD}}{V_{DD} - V_{CONTROL\_V}} \right) \\ Duty &- cycle = t_{ON} \cdot Freq \end{aligned}$$

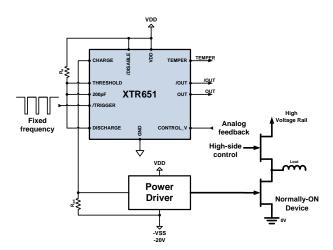

# High-voltage Open-drain Outputs (CHARGE / DISCHARGE)

The high-voltage capability of CHARGE and DISCHARGE open-drain outputs widely opens the field of possible applications.

The following figure shows an application where the XTR651 is used to send a PWM signal to a driver with a negative VSS supply voltage. This is typically the case where a power driver is used to control a normally-on jFET transistor. In this case, the CHARGE output (open drain of a PMOS transistor) is used to provide a signal referenced to a negative voltage, used as the control input of a power driver. The power driver is then able to provide a gate signal to the jFET transistor slewing from –VSS to +VDD. A fixed frequency input signal must be provided to the XTR651 in order to periodically trigger the turn-on of the CHARGE output. Input CONTROL\_V is used as the analog feedback in order to set the PWM duty-cycle.

In the following figure, the XTR651 is used to implement a low-power flyback converter. The DISCHARGE output (open drain of an NMOS transistor) is used to drive the primary winding of the flyback transformer. Input CONTROL\_V is used as the analog feedback in order to set the PWM duty-cycle to control the output voltage VOUT.

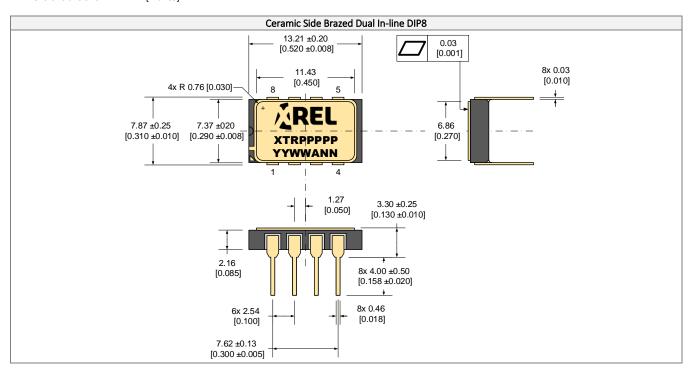

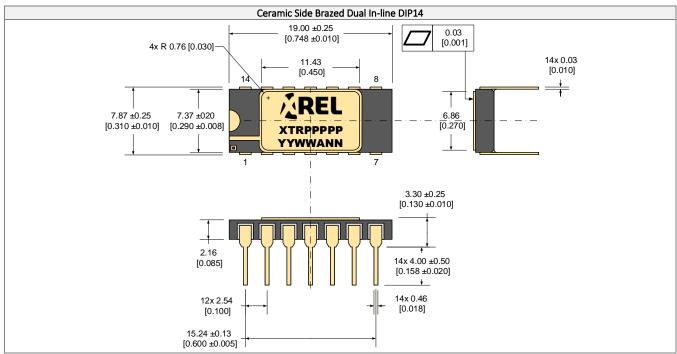

# **PACKAGE OUTLINES**

Dimensions are shown in mm [inches].

|                                   | Part Marking Convention                                                        |  |  |

|-----------------------------------|--------------------------------------------------------------------------------|--|--|

| Part Referen                      | Part Reference: XTRPPPPPP                                                      |  |  |

| XTR                               | X-REL Semiconductor, high-temperature, high-reliability product (XTRM Series). |  |  |

| PPPPP                             | Part number (0-9, A-Z).                                                        |  |  |

| Unique Lot Assembly Code: YYWWANN |                                                                                |  |  |

| YY                                | Two last digits of assembly year (e.g. 11 = 2011).                             |  |  |

| ww                                | WW Assembly week (01 to 52).                                                   |  |  |

| Α                                 | Assembly location code.                                                        |  |  |

| NN                                | Assembly lot code (01 to 99).                                                  |  |  |

### **IMPORTANT NOTICE & DISCLAIMER**

Information in this document supersedes and replaces all information previously supplied. Information in this document is provided solely in connection with EASii IC products from the X-REL business unit.

The information contained herein is believed to be reliable. EASii IC makes no warranties regarding the information contain herein. EASii IC assumes no responsibility or liability whatsoever for any of the information contained herein. EASii IC assumes no responsibility or liability whatsoever for the use of the information contained herein. The information contained herein is provided "AS IS, WHERE IS" and with all faults, and the entire risk associated with such information is entirely with the user. EASii IC reserves the right to make changes, corrections, modifications or improvements, to this document and the information herein without notice. Customers should obtain and verify the latest relevant information before placing orders for EASii IC products. The information contained herein or any use of such information does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other intellectual property rights, whether with regard to such information itself or anything described by such information.

Unless expressly approved in writing by an authorized representative of EASii IC, EASii IC products are not designed, authorized or warranted for use in military, aircraft, space, lifesaving, or life sustaining applications, nor in products or systems where failure or malfunction may result in personal injury, death, or property or environmental damage.

General Sales Terms & Conditions apply.

For product information and a complete list of distributors, please go to our web site: www.x-relsemi.com

90, Avenue Leon Blum 38100 Grenoble — France ③ :+33 456 580 580

☑ : support.XREL@easii-ic.com

EASii IC, X-REL Semiconductor, and the logo are trademarks of EASii IC in France and other countries. Data subject to change. Copyright © 2002-2021 EASii IC. All rights reserved.