# **Y8002 Microprocessor**

### **Technical Manual**

Systemyde International Corporation

Every effort has been made to ensure the accuracy of the information contain herein. If you find errors or inconsistencies please bring them to our attention. In all cases, however, the Verilog HDL source code for the Y8002 design defines "proper operation".

Copyright © 2003, 2009, 2012, Systemyde International Corporation. All rights reserved.

Notice:

<sup>&</sup>quot;Z8000", "Z8001", "Z8002" and "Zilog" are registered trademarks of Zilog, Inc. All uses of these terms in this document are to be construed as adjectives, whether or not the noun "microprocessor", "CPU" or "device" are actually present.

# Index

| Introduction                                    |     |

|-------------------------------------------------|-----|

| Programming Model                               | 5   |

| Addressing and Address Modes                    | 9   |

| Instruction Format                              | 13  |

| Instruction Set                                 |     |

| External Interface and Timing                   |     |

| Interrupts and Traps                            | 197 |

| Reset                                           | 201 |

| Verilog HDL Source                              |     |

| Test Bench                                      | 207 |

| Appendix 1: Execution Details                   |     |

| Appendix 2: Unimplemented Features/Instructions |     |

| Appendix 3: Trapped Opcodes                     |     |

| Appendix 4: Known Timing Differences            | 231 |

# **Chapter 1**

### Introduction

This book documents the operation of the Y8002 microprocessor. The Y8002 design is supplied in Verilog HDL format and can be implemented in any technology supported by a logic synthesis tool that accepts Verilog HDL. The design requires roughly 15K logic gate equivalents. Included in the design package is a test bench that exercises all implemented instructions, flag settings, and representative data patterns. The test patterns should achieve at least 95% fault coverage.

The Y8002 CPU was designed in a clean-room environment and is a clone of the Zilog Z8002 microprocessor. Only publicly available documentation was used to create this design so there may be minor differences where the public documentation is misleading or lacking. With only a couple of exceptions, the instruction execution times are identical between the two designs. All known differences for individual instructions are listed in the instruction description chapter as notes.

The Y8002 design, depending on the version, may not implement all of the instructions, features or operating modes of the Z8000 architecture. The specific differences, for any given version of the design, are covered in the various appendices.

The Z8002 CPU is one of four variants of the Z8000 architecture, introduced by Zilog in 1979. The Z8002 and Z8004 support a 16-bit linear address space and are identical except that the Z8004 added support for virtual memory. The Z8001 and Z8003 support a 23-bit segmented address and are identical except that the Z8003 added support for virtual memory. All of these devices were implemented in NMOS technology and the Z8001 CPU and the Z8002 CPU were available for -55C to +125C operation. Manufacturing of these devices ceased around 1990.

This document should always be used as the final word on the operation of the Y8002 CPU, but it is useful to refer to the Zilog documentation if the description given here is too cryptic. The Z8000 architecture is over twenty years old, so it is assumed that it is already at least somewhat familiar to the reader, but an overview is presented here. This document will make no attempt to describe the segmented addressing mode of the Z8000 architecture because it is not present in the Y8002 CPU.

The Z8000 architecture includes sixteen 16-bit general-purpose registers, and uses eight distinct data types ranging from single bits to 64-bit quadruple words and byte strings. The architecture supports eight different types of addressing modes. A Z8000 architecture CPU (like the Y8002) has 111 instruction types in its instruction set. The multiple addressing modes and data types, when coupled with the instruction types, produces 447 different instructions for the Y8002 processor instruction set.

The architecture includes status signals that can be used to determine the nature of each bus transaction. The status signals can be decoded and used to implement systems having multiple memory address spaces, each space being dedicated to a specific purpose.

The architecture includes two operating modes: system mode, and normal mode. This feature allows the operating system functions to be easily separated from application program functions to enhance operating system and application data security.

The architecture provides dedicated instructions for input/output operations, allowing the separation I/O operations from memory-related operations (the I/O space is separate from the memory space). The dedicated I/O instructions can only be accessed while operating in system mode. Applications running in normal mode cannot directly affect the operation of the I/O ports. This architecture does not prevent the user from designing a system with memory-mapped I/O.

The architecture includes an interrupt mechanism that processes interrupts and exceptions from various sources. These sources include a single non-maskable interrupt, a single non-vectored interrupt, up to 256 vectored interrupt sources, and traps caused by the following events: execution of a privileged instruction while in normal mode, execution of an extended instruction, execution of the system call instruction, and a segment trap. The interrupt mechanism stores the program status, transfers program control to an interrupt service routine, and restores program status at the end of the interrupt process. The interrupt mechanism of the Z8000 architecture includes a means of assigning priorities to the interrupts, but this is external to the CPU itself.

The full Z8000 architecture implements a segmented memory map that allows the processor to directly address six memory spaces up to 8 Megabytes (8,388,608 bytes) each. Each memory segment consists of a 64K (65,536) byte block. The sixteen address lines present on the Z8000 processors are used to access the individual locations within the memory segment while a seven-bit segment register is used to provide access to each of the segments. As mentioned previously, the Y8002 processor does not implement the segmented memory scheme. It is capable of addressing six separate memory spaces, each being a maximum of 64K bytes.

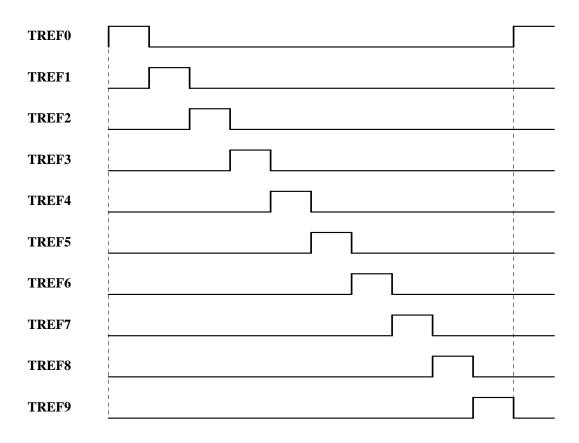

The architecture includes a refresh-control block that is designed to generate memory refresh cycles for dynamic random access memory that may be used in conjunction with the processor.

The architecture includes provisions to allow the processor to yield control of the system address/data, control, and status signals to another processor in the system in response to a bus request signal. When a bus request is granted, the processor enters the bus-disconnect state. Program execution is suspended and the CPU disconnects itself from the bus (signals are placed into a high-impedance state). When the bus request is removed from the processor, the CPU regains control of the bus, and continues with program execution.

The architecture includes a feature known as the Extended Processing Architecture (EPA). This feature allows the instruction set of the processor to be augmented by external devices (Extended Processing Units, or EPUs) on the bus. The extended instructions are used to exploit this feature. If an extended processing unit is available, the processor will handle only the data transfer portion of the instruction, and leave execution of the instruction to the EPU. If no EPU is present, the processor can handle the instruction itself using an extended instruction trap handling software routine. The EPA bit located in the Flag and Control Word (FCW) determines how the instruction will be handled.

# **Chapter 2**

## **Programming Model**

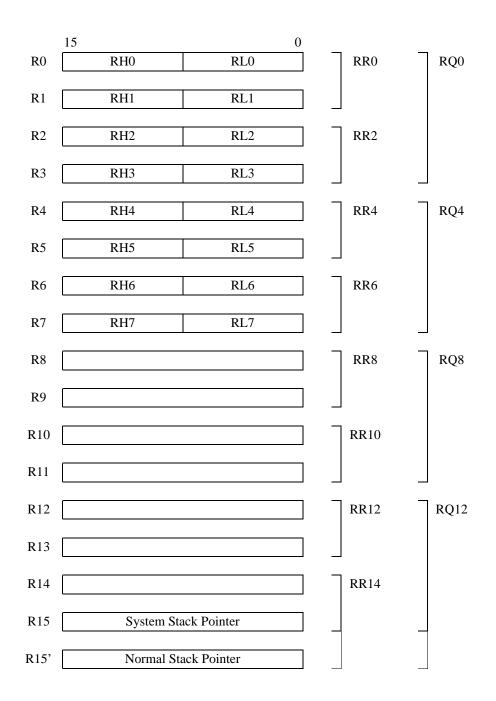

The Z8000 architecture contains sixteen 16-bit general-purpose registers. With only a few exceptions, all general-purpose registers can be used for any instruction operand. These registers allow data ranging from bytes to quadruple words. None of the general purpose registers are affected by reset.

Word registers are specified in assembly language as R0 through R15. Sixteen byte registers (RH0-RL7) can be used as accumulators, and overlap the first eight word registers. Registers may be paired into eight double word registers RR0 through RR14 for 32-bit operands. Registers may also be grouped in groups of four quadruple word registers RQ0 through RQ12 for 64-bit operands. The double word and quadruple word registers are used by operations such as Multiply, Divide, and Extend Sign.

The Z8000 architecture includes two hardware stack pointers, one for each operating mode (normal and system). The system stack pointer is used in system mode, during interrupt or trap handling, and for system calls. The normal stack pointer is used in normal mode and only the normal stack pointer is accessible. When operating in system mode the system stack pointer is accessed as a general-purpose register and the normal stack pointer is accessed as a special control register. Register R15 is the stack pointer.

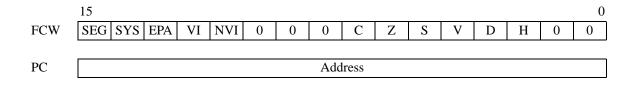

The program status reflects the current operating state of the processor. Included in the program status is the Flag and Control Word (FCW) and Program Counter (PC). The program status is automatically pushed onto the system stack in response to an interrupt or trap. After reset, the Y8002 CPU fetches the FCW from memory address 0x0002 and the PC from memory address 0x0004 before starting execution. Both of these addresses are in the Program address space.

The Flag and Control Word register contains both processor status bits and processor control bits. The loworder byte contains system status flags that are used by the processor instructions to control program branching and looping. The high order byte contains processor control bits that are used to enable and disable the processor interrupt system and control certain processor operating modes.

The six processor status bits are:

- Carry (C) -- This bit indicates that a carry out of the high order bit position of a register being used as an accumulator has occurred.

- Zero (Z) -- This bit indicates that the result of a processor operation is zero.

- Sign (S) -- This bit indicates that the result of an processor operation has produced a negative number.

- Overflow (V)-- This bit indicates that an overflow has occurred (on processor arithmetic operations) or even parity (after processor logical operations).

- Decimal-Adjust (D) -- This bit is used in BCD arithmetic to indicate the type of instruction that was executed (addition or subtraction).

• Half-Carry (H) --This bit is used to convert the binary result of a previous addition or subtraction of BCD numbers into the correct decimal result.

The control bits in the high order byte of the FCW are:

- Non-Vectored Interrupt Enable (NVI) -- This bit is used to enable or disable the processor's response to interrupts on its non-vectored interrupt input.

- Vectored Interrupt Enable (VI) -- This bit is used to enable or disable the processor's response to interrupts on its vectored interrupt input.

- System Mode (SYS) -- This bit determines if the processor is to operate in the system mode (High) or normal mode (Low). The Normal/System hardware output signal of the processor is the complement of this bit.

- Extended Processor Architecture (EPA) -- This bit indicates the presence or absence of Extended Processing Units (EPU) in the system architecture. If EPUs are present, this bit should be set to one, and the processor will execute extended instructions as they are encountered. If EPUs are not present in the system and an extended instruction is fetched for execution, the processor will generate an extended instruction trap.

- Segmentation Mode (SEG) -- This bit is present only in a segmented Z8000 processor. When set to one, the processor is executing in segmented mode. When set to zero, the processor is executing in non-segmented mode. This bit is permanently set to 0 in the Y8002 processor.

The Program Counter is a sixteen bit register. All instruction fetches are 16 bits wide, so the least significant bit of the PC should always be zero. However, the hardware neither forces or checks that this is true.

The Program Status Area Pointer (PSAP) contains the address of the Program Status Area, which is a table that contains FCW and PC values used by the interrupt and exception handling hardware of the processor. When an interrupt or trap occurs in the processor execution cycle, the Program Status Area is where the processor obtains new values for the FCW and PC in order to process the exception. The lower byte of the PSAP is always zero. The PSAP points to an area in the Program memory address space and is cleared to all zeros by reset.

The Z8000 architecture contains hardware that can be used to automatically refresh dynamic memory in the system. The Refresh Control register contains a 9-bit row counter, and a six-bit rate counter, as well as an enable/disable control bit. Bit 15 of this register is cleared by reset. Modern dynamic RAMs have no need of this feature.

**General Purpose Registers**

#### **Program Status Registers**

| Upper Pointer | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|---------------|---|---|---|---|---|---|---|---|

#### Program Status Area Pointer

| REN Rate | Row |

|----------|-----|

|----------|-----|

**Refresh Control**

# **Chapter 3**

## **Addressing and Address Modes**

The Z8000 architecture supports separate memory and I/O address spaces, and each of these address spaces can be further subdivided if necessary. The exact address space that is being accessed is encoded on the four status signals that are output buy the processor with each bus transaction. The available address spaces are:

- Program address space, with two separate status encodings to distinguish the first word of an instruction fetch from some other program memory fetch.

- Data address space, used to access data.

- Stack address space, used to access data via the stack pointer R15.

- Standard I/O address space, used for all regular I/O operations.

- Special I/O address space, which is usually reserved for I/O operations between the processor and a Memory Management Unit (MMU) or a Direct Memory Access controller (DMA).

In this architecture, each of the memory address spaces can be a maximum of 64K bytes, allowing the Y8002 CPU to address 384 KB of memory. Each I/O address space is a maximum of 64K port addresses.

Each of the memory spaces can be further separated externally according to the system or normal mode. This provides the ability to design and implement operating systems that protect the system operation and information from being corrupted or accessed by user applications.

I/O address space is accessible only from the system mode of operation. This prevents user programs from gaining access to system resources directly, giving the system software complete control over peripheral devices.

The Z8000 architecture is big-endian, meaning that the most-significant data element is addressed at the lowest memory address. Bytes transferred to or from odd memory address locations (address bit 0 = 1) are always transmitted on lines AD7-AD0 (data bit 0 on AD0). Bytes transferred to or from even memory address locations (address bit 0 = 0) are always transmitted on lines AD15-AD8 (data bit 0 on AD8).

During byte writes, the CPU places the same byte on both halves of the bus. The system hardware must use AD0 to determine which half of the bus contains the actual data to be written. For byte reads, the CPU will read all 16-bits of data on the AD15-AD0 lines and automatically select the proper half of the bus that contains the active data.

I/O devices can use either 8-bit or 16-bit data busses for either I/O address space. The address of a peripheral with a 16-bit wide data bus may be odd or even. Peripherals having 8-bit wide data busses connected on lines AD7-AD0 must either be addressed using odd addresses or ignore the least significant bit of the address and use two I/O addresses per I/O port. Normally special I/O devices connect to the upper half of the bus, and thus use even addresses.

Each memory address space consists of a block of 64KB of memory, with addresses being consecutively numbered in ascending order. The 8-bit byte is the basic addressable element in memory address space. The Z8000 architecture supports three additional addressable data elements:

- Bits, either in bytes or words

- 16-bit words

- 32-bit long words

The type of data element being accessed depends upon the instruction being executed. The assembler mnemonics allow for addressing bit, byte, word, or long word data. Not all instructions can access all types of data. Addressable data elements are shown below:

| bits   | 15                        | 14 | 13 | 12 | 11 | 10 | 9      | 8       | 7             | 6     | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|---------------------------|----|----|----|----|----|--------|---------|---------------|-------|---|---|---|---|---|---|

| bytes  | address "n"               |    |    |    |    |    |        |         | address "n+1" |       |   |   |   |   |   |   |

| word   |                           |    |    |    |    | ,  | addres | s "n" ( | ("n" is       | even) |   |   |   |   |   |   |

| double | address "n" ("n" is even) |    |    |    |    |    |        |         |               |       |   |   |   |   |   |   |

| word   | address "n+2"             |    |    |    |    |    |        |         |               |       |   |   |   |   |   |   |

A bit can be addressed by specifying an address (byte or word) and the location of the bit within the byte (7-0) or word (15-0). Bits are numbered right to left, from the least significant bit to the most significant bit.

The address of a data element longer than one byte (word, long word) is the same as that of the byte with the lowest memory address within the word or long word. This byte is the leftmost, highest-order (most significant) byte of the word or long word.

Word and long word addresses are always even-numbered. Low bytes of words are stored in odd-numbered addresses and high bytes of words are stored in even numbered addresses. Byte data can be stored in odd or even addresses.

Memory locations 0x0000-0x0005 in the Program memory space are reserved for the FCW and PC that are fetched after a reset. Except for this reserved memory space, there are no restrictions placed on any locations within the processor memory space, although the 256-byte block addressed by the PSAP is used for the Program Status information for interrupts, traps and system calls rather than program information.

The architecture supports eight data types directly, although Extended Processing Units may create and access new data types, such as floating point numbers. Five of the eight data types are fixed length data and the remaining three data types have variable lengths. Each data type is supported by numerous instructions that operate upon it directly. The data types are as follows:

- Bit

- Signed and unsigned byte, word, double word or quadruple word binary data

- Byte or word logical data

- Word address

- Byte of packed BCD (binary coded decimal) integer

- Dynamic-length string of byte data

- Dynamic-length of word data

- Dynamic-length of stack data

Bit data can be manipulated either in the general-purpose registers or in memory. Binary and BCD integers, and logical values may be manipulated in registers, although operands can be fetched directly from memory. Addresses can only be manipulated in registers while strings and stack data can only be manipulated in memory.

The operands for instructions can be specified using one of eight addressing modes. For some instructions no addressing mode is used, because the operand is implied. The majority of instructions can use any of the five common addressing modes: register, immediate, indirect register, direct address and indexed. A few instructions can use the relative address mode and only load and store instructions can use base address and base index addressing modes.

Because of the way that the addressing modes are encoded into the opcode, register R0 (and double register RR0) cannot be used in the indirect address, index, base address or base index modes.

- Register: the contents of the register.

- Immediate: in the instruction.

- Indirect Register: the contents of the location whose address is in the register.

- Direct Address: the contents of the location whose address is in the instruction.

- Index: the contents of the location whose address is the sum of the address in the instruction plus the contents of the register.

- Relative Address: the contents of the location whose address is the sum of the contents of the Program Counter plus the displacement in the instruction.

- Base Address: the contents of the location whose address is the sum of the contents of a register plus the displacement in the instruction.

- Base Index: the contents of the location addressed by the sum of the contents of one register plus the contents of another register.

# **Chapter 4**

### **Instruction Format**

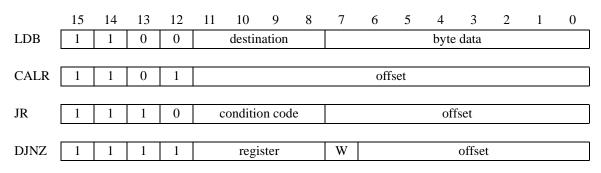

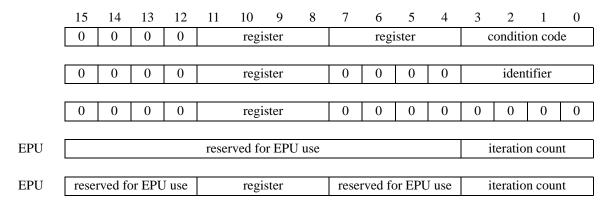

The format of instructions in the Z8000 architecture is quite regular. The general instruction format uses a two bit field to select the addressing mode, a five or six bit field for the operation code (opcode), a four bit field to select the source operand and a four bit field to select the destination operand.

In the addressing mode field the bit combination 00 usually selects either immediate data or Indirect Register addressing, the bit combination 01 selects either Direct addressing or Index addressing and the bit combination 10 selects Register addressing. The choice between Immediate and Indirect Register or between Direct and Index is made using one of the bit combinations in bits 7-4. This is why R0 cannot be used with Indirect Register or Index addressing.

|      | 15   | 14   | 13     | 12 | 11     | 10  | 9    | 8       | 7       | 6       | 5       | 4     | 3       | 2     | 1       | 0     |

|------|------|------|--------|----|--------|-----|------|---------|---------|---------|---------|-------|---------|-------|---------|-------|

| Byte | ad n | node |        | (  | opcode | e   |      | 0       | sour    | ce or o | lestina | ation | sour    | ce or | destina | ation |

|      |      |      |        |    |        |     |      |         |         |         |         |       |         |       |         |       |

| Word | ad n | node | opcode |    |        | 1   | sour | ce or o | lestina | ation   | sour    | ce or | destina | ation |         |       |

|      |      |      |        |    |        |     |      |         |         |         |         |       |         |       |         |       |

| Long | ad n | node |        |    | opc    | ode |      |         | sour    | ce or o | destina | ation | sour    | ce or | destina | ation |

#### General Instruction Format (first word of instruction)

The bit combination 11 in the address mode field is used to specify the compact format for the instruction. Four of the most commonly used instructions have their own compact format.

#### **Special Compact Instruction Format**

Some infrequently used or complex instructions require two words to encode all of the information. All EPU instructions also require at least two words.

General Instruction Format (second word of instruction)

# **Chapter 5**

## **Instruction Set**

This chapter presents the assembly language syntax, addressing modes, flag settings, binary encoding, and execution time for the Y8002 instruction set. The entire instruction set is presented in alphabetical order, without regard to whether or not a particular instruction has been implemented in a particular version of the design. For a list of implemented versus unimplemented instructions, refer to the appropriate Appendix.

The assembly language syntax is identical to that used by the original Zilog assembler. Different assembler programs may or may not use identical syntax. The syntax is presented generically at the beginning of each instruction, with the details presented for each addressing mode later in each entry.

The operation of each instruction is specified in a format similar to Verilog HDL for minimum ambiguity, but no descriptive text or examples are included.

The effect of the instruction on each flag is listed, with a brief description. Normally the flags are updated by the main operation of the instruction, but for some complex instructions different flags may be affected by different parts of the instruction. This is specified in the description. Where the same flag is reused during a complex instruction a note is included at the end of the instruction description with the details.

Fields in the instruction are listed using shortcuts for common fields. These shortcuts should be self-explanatory in most cases, but will be detailed here for completeness.

The most common fields in the instruction specify a CPU register, employing the following shortcuts:

| Rbdd | Byte register used as a destination operand.        |

|------|-----------------------------------------------------|

| Rbss | Byte register used as a source operand.             |

| Rddd | Word register used as a destination operand.        |

| Rdnz | Word register used in addressing the destination.   |

| Rrrr | Word register (usually specifies a counter).        |

| Rsss | Word register used as a source operand.             |

| Rsnz | Word register used in addressing the source.        |

| R1nz | Word register used in addressing the first source.  |

| R2nz | Word register used in addressing the second source. |

| Rxxx | Word register used as an index.                     |

| RQdd | Register quad used as a destination operand.        |

| RRdd | Register pair used as a destination operand.        |

| RRss | Register pair used as a source operand.             |

The registers are encoded according to the following table. Note that in the case of Rdnz, Rsnz, R1nz and R2nz the "0000" case is illegal and is usually used to select a different addressing mode. The illegal cases for RRdd, RRss and RQdd should not be used. The instructions will still execute with an illegal register

encoding, but the results will be scrambled in the registers because of the way the register addresses are treated internally in the design

| encoding in<br>opcode | Rbss or Rbdd | Rddd, Rsss,<br>Rrrr or Rxxx | Rsnz, Rdnz,<br>R1nz or R2nz | RRdd, RRss | RQdd    |

|-----------------------|--------------|-----------------------------|-----------------------------|------------|---------|

| 0000                  | RH0          | R0                          | illegal                     | RR0        | RQ0     |

| 0001                  | RH1          | R1                          | R1                          | illegal    | illegal |

| 0010                  | RH2          | R2                          | R2                          | RR2        | illegal |

| 0011                  | RH3          | R3                          | R3                          | illegal    | illegal |

| 0100                  | RH4          | R4                          | R4                          | RR4        | RQ4     |

| 0101                  | RH5          | R5                          | R5                          | illegal    | illegal |

| 0110                  | RH6          | R6                          | R6                          | RR6        | illegal |

| 0111                  | RH7          | R7                          | R7                          | illegal    | illegal |

| 1000                  | RL0          | R8                          | R8                          | RR8        | RQ8     |

| 1001                  | RL1          | R9                          | R9                          | illegal    | illegal |

| 1010                  | RL2          | R10                         | R10                         | RR10       | illegal |

| 1011                  | RL3          | R11                         | R11                         | illegal    | illegal |

| 1100                  | RL4          | R12                         | R12                         | RR12       | RQ12    |

| 1101                  | RL5          | R13                         | R13                         | illegal    | illegal |

| 1110                  | RL6          | R14                         | R14                         | RR14       | illegal |

| 1111                  | RL7          | R15                         | R15                         | illegal    | illegal |

Immediate data is encoded in the instruction in a number of different ways, depending on the instruction. Note that the assembly language mnemonics will always use just "#data" or "#n", independent of the actual width or encoding in the instruction. The following shortcuts are employed:

| b              | Positive (or zero) twos-complement number used for shift left count.          |

|----------------|-------------------------------------------------------------------------------|

| -b             | Negative twos-complement number used for shift right count                    |

| bbb            | Three bit unsigned value (range $0x0 - 0x7$ , corresponding to $0 - 7$ ).     |

| bbbb           | Four bit unsigned value (range 0x0 - 0xF, corresponding to 0 - 15).           |

| #data          | Four, eight or sixteen bit immediate data.                                    |

| #data (high)   | Most significant word of thirty-two bit immediate data.                       |

| #data (low)    | Least significant word of thirty-two bit immediate data.                      |

| dddd           | Four bit unsigned value (range 0x0 - 0xF, corresponding to 0 - 15).           |

| ddd_dddd       | Seven bit unsigned value (range $0x00 - 0x7F$ , corresponding to $0 - 127$ ). |

| dddd_dddd      | Eight bit signed value (range 0x00 - 0xFF, or -127 to +128)                   |

| dddd_dddd_dddd | Twelve bit signed value (range 0x000 - 0xFFF, or -2048 to +2047).             |

| nnnn           | Four bit unsigned value (range 0x0 - 0xF, corresponding to 1 - 16).           |

| SSSSTCCC       | Eight bit System Call identifier (range 0x00 - 0xFF)                          |

The "cccc" field encodes one of sixteen possible flags combinations to be tested as part of the instruction, as shown in the table below. Note that some encodings have more than one possible assembly language mnemonic, and the "always true" case is implied when no other case is specified.

| сссс      | encoding<br>in opcode | Flag combination                                           | Meaning                                    |

|-----------|-----------------------|------------------------------------------------------------|--------------------------------------------|

| F         | 0000                  | any                                                        | Always False                               |

| LT        | 0001                  | $(S \land V) = 1$                                          | Less Than                                  |

| LE        | 0010                  | $(\mathbb{Z} \parallel (\mathbb{S} \land \mathbb{V})) = 1$ | Less Than or Equal                         |

| ULE       | 0011                  | (C    Z) = 1                                               | Unsigned Less Than or Equal                |

| OV<br>PE  | 0100                  | <b>V</b> = 1                                               | Overflow<br>Parity Even                    |

| MI        | 0101                  | S = 1                                                      | Minus                                      |

| Z<br>EQ   | 0110                  | Z = 1                                                      | Zero<br>Equal                              |

| C<br>ULT  | 0111                  | C = 1                                                      | Carry<br>Unsigned Less Than                |

|           | 1000                  | any                                                        | Always True                                |

| GE        | 1001                  | $(S ^ V) = 0$                                              | Greater Than or Equal                      |

| GT        | 1010                  | $(Z \parallel (S \land V)) = 0$                            | Greater Than                               |

| UGT       | 1011                  | (!C && !Z) = 1                                             | Unsigned Greater Than                      |

| NOV<br>PO | 1100                  | $\mathbf{V} = 0$                                           | No Overflow<br>Parity Odd                  |

| PL        | 1101                  | $\mathbf{S} = 0$                                           | Plus                                       |

| NZ<br>NE  | 1110                  | $\mathbf{Z} = 0$                                           | Not Zero<br>Not Equal                      |

| NC<br>UGE | 1111                  | $\mathbf{C} = 0$                                           | No Carry<br>Unsigned Greater Than or Equal |

The remaining shortcuts should be self-explanatory. The shortcut "CZSV" is a four bit field where each bit corresponds to the flag of the same name. The shortcut "VN" is a two bit field with each bit corresponding to one of the interrupt enable bits of the same name in the FCW.

The execution times are listed here only as a number of clock cycles. These numbers assume no wait states and no interrupts during execution of an iterative instruction. The details of both internal and external execution sequences are available in an Appendix.

## ADC Add With Carry

| ADC dst, src<br>ADCB |                                                                                                                                                                                                                                                                                                                                                                                                                 | dst: R<br>src: R   |        |  |  |  |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|--|--|--|--|--|

| Operation:           | $dst \le dst + src + C$                                                                                                                                                                                                                                                                                                                                                                                         |                    |        |  |  |  |  |  |

| Flags:               | <ul> <li>C: Set if arithmetic carry from result MSB; cleared otherwise.</li> <li>Z: Set if result is zero; cleared otherwise.</li> <li>S: Set if result is negative; cleared otherwise.</li> <li>V: Set if arithmetic overflow; cleared otherwise.</li> <li>D: Cleared (ADCB);<br/>Unaffected (ADC).</li> <li>H: Set if arithmetic carry from bit 3; cleared otherwise (ADCB);<br/>Unaffected (ADC).</li> </ul> |                    |        |  |  |  |  |  |

| Addressing<br>Modes  | Assembly Syntax                                                                                                                                                                                                                                                                                                                                                                                                 | Encoding           | Clocks |  |  |  |  |  |

| R:                   | ADC Rd, Rs                                                                                                                                                                                                                                                                                                                                                                                                      | 10110101_Rsss_Rddd | 5      |  |  |  |  |  |

|                      | ADCB Rbd, Rbs                                                                                                                                                                                                                                                                                                                                                                                                   | 10110100_Rbss_Rbdd | 5      |  |  |  |  |  |

## ADD

Add

| ADD dst, src<br>ADDB<br>ADDL | dst: R<br>src: R, IM, IR, DA, X                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:                   | $dst \le dst + src$                                                                                                                                                                                                                                                                                                                                                                                      |

| Flags:                       | <ul> <li>C: Set if arithmetic carry from MSB; cleared otherwise.</li> <li>Z: Set if result is zero; cleared otherwise.</li> <li>S: Set if result is negative; cleared otherwise.</li> <li>V: Set if arithmetic overflow; cleared otherwise.</li> <li>D: Cleared (ADDB);<br/>Unaffected (ADD).</li> <li>H: Set if arithmetic carry from bit 3; cleared otherwise (ADDB);<br/>Unaffected (ADD).</li> </ul> |

| Addressing<br>Modes | Assembly Syntax | Encoding                            | Clocks |

|---------------------|-----------------|-------------------------------------|--------|

| R:                  | ADD Rd, Rs      | 10000001_Rsss_Rddd                  | 4      |

|                     | ADDB Rbd, Rbs   | 1000000_Rbss_Rbdd                   | 4      |

|                     | ADDL RRd, RRs   | 10010110_RRss_RRdd                  | 8      |

| IM:                 | ADD Rd, #data   | 00000001_0000_Rddd<br>#data         | 7      |

|                     | ADDB Rbd, #data | 00000000_0000_Rbdd<br>#data   #data | 7      |

|                     | ADDL RRd, #data | 00010110_0000_RRdd                  | 14     |

|                     |                 | #data (high)<br>#data (low)         |        |

| Addressing<br>Modes | Assembly Syntax    | Encoding                      | Clocks |

|---------------------|--------------------|-------------------------------|--------|

| IR:                 | ADD Rd, @Rs        | 00000001_Rsnz_Rddd            | 7      |

|                     | ADDB Rbd, @Rs      | 00000000_Rsnz_Rbdd            | 7      |

|                     | ADDL RRd, @Rs      | 00010110_Rsnz_RRdd            | 14     |

| DA:                 | ADD Rd, address    | 01000001_0000_Rddd<br>address | 9      |

|                     | ADDB Rbd, address  | 01000000_0000_Rbdd<br>address | 9      |

|                     | ADDL RRd, address  | 01010110_0000_RRdd<br>address | 15     |

| Х:                  | ADD Rd, addr(Rs)   | 01000001_Rsnz_Rddd<br>address | 10     |

|                     | ADDB Rbd, addr(Rs) | 01000000_Rsnz_Rbdd<br>address | 10     |

|                     | ADDL RRd, addr(Rs) | 01010110_Rsnz_RRdd<br>address | 16     |

| AND dst, src<br>ANDB | dst: R<br>src: R, IM, IR, DA, X                                                                                                                                                                                                                                                              |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:           | dst <= dst & src                                                                                                                                                                                                                                                                             |

| Flags:               | <ul> <li>C: Unaffected.</li> <li>Z: Set if result is zero; cleared otherwise.</li> <li>S: Set if result is negative; cleared otherwise.</li> <li>V: Set if result parity is even; cleared otherwise (ANDB);<br/>Unaffected (AND).</li> <li>D: Unaffected.</li> <li>H: Unaffected.</li> </ul> |

| Addressing<br>Modes | Assembly Syntax   | Encoding                            | Clocks |

|---------------------|-------------------|-------------------------------------|--------|

| R:                  | AND Rd, Rs        | 10000111_Rsss_Rddd                  | 4      |

|                     | ANDB Rbd, Rbs     | 10000110_Rbss_Rbdd                  | 4      |

| IM:                 | AND Rd, #data     | 00000111_0000_Rddd<br>#data         | 7      |

|                     | ANDB Rbd, #data   | 00000110_0000_Rbdd<br>#data   #data | 7      |

| IR:                 | AND Rd, @Rs       | 00000111_Rsnz_Rddd                  | 7      |

|                     | ANDB Rbd, @Rs     | 00000110_Rsnz_Rbdd                  | 7      |

| DA:                 | AND Rd, address   | 01000111_0000_Rddd<br>address       | 9      |

|                     | ANDB Rbd, address | 01000110_0000_Rbdd<br>address       | 9      |

| Addressing<br>Modes | Assembly Syntax    | Encoding           | Clocks |

|---------------------|--------------------|--------------------|--------|

| X:                  | AND Rd, addr(Rs)   | 01000111_Rsnz_Rddd | 10     |

|                     |                    | address            |        |

|                     | ANDB Rbd, addr(Rs) | 01000110_Rsnz_Rbdd | 10     |

|                     |                    | address            |        |

| BIT dst, src<br>BITB | dst: R, IR, DA, X<br>src: IM                                                                                                                                                                   |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Operation:           | Z <= !dst[src]                                                                                                                                                                                 |  |

| Flags:               | <ul> <li>C: Unaffected.</li> <li>Z: Set if selected bit is zero; cleared otherwise.</li> <li>S: Unaffected.</li> <li>V: Unaffected.</li> <li>D: Unaffected.</li> <li>H: Unaffected.</li> </ul> |  |

| Addressing<br>Modes | Assembly Syntax   | Encoding                      | Clocks |

|---------------------|-------------------|-------------------------------|--------|

| R:                  | BIT Rd, #b        | 10100111_Rddd_bbbb            | 4      |

|                     | BITB Rbd, #b      | 10100110_Rbdd_0bbb            | 4      |

| IR:                 | BIT @Rd, #b       | 00100111_Rdnz_bbbb            | 8      |

|                     | BITB @Rd, #b      | 00100110_Rdnz_0bbb            | 8      |

| DA:                 | BIT address, #b   | 01100111_0000_bbbb<br>address | 10     |

|                     | BITB address, #b  | 01100110_0000_0bbb<br>address | 10     |

| X:                  | BIT addr(Rd), #b  | 01100111_Rdnz_bbbb<br>address | 11     |

|                     | BITB addr(Rd), #b | 01100110_Rdnz_0bbb<br>address | 11     |

#### Notes:

1. Only bits 2-0 of the opcode are used to select the bit in the case of BITB, and bit 3 of the opcode is ignored.

10

| BIT dst, src<br>BITB |                                                                                                                                                                                   | dst: R<br>src: R                          |        |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--------|

| Operation:           | Z <= !dst[src]                                                                                                                                                                    |                                           |        |

| Flags:               | <ul> <li>C: Unaffected.</li> <li>Z: Set if selected bit is zero; clear</li> <li>S: Unaffected.</li> <li>V: Unaffected.</li> <li>D: Unaffected.</li> <li>H: Unaffected.</li> </ul> | red otherwise.                            |        |

| Addressing<br>Modes  | Assembly Syntax                                                                                                                                                                   | Encoding                                  | Clocks |

| R:                   | BIT Rd, Rs                                                                                                                                                                        | 00100111_0000_Rsss<br>0000 Rddd 0000 0000 | 10     |

#### Notes:

BITB Rbd, Rs

1. The Z8000 microprocessor restricts the source register to be one of R0 - R7 for BITB. This restriction does not apply to the Y8002 design. Any register may be used as the source.

00100110\_0000\_Rsss

0000\_Rbdd\_0000\_0000

2. Only bits 3-0 of the source operand are used for the bit select for BIT; only bits 2-0 of the source operand are used for the bit select for BITB.

3. Only bits 11-8 of the second word of the opcode are used. All other bits in the second word of the opcode are ignored.

### CALL

Call

| CALL dst   |                                                    | dst: IR, DA, X |

|------------|----------------------------------------------------|----------------|

| Operation: | SP <= SP - 2<br>@SP <= PC<br>PC <= dst             |                |

| Flags:     | C: Unaffected.<br>Z: Unaffected.                   |                |

|            | S: Unaffected.<br>V: Unaffected.<br>D: Unaffected. |                |

|            | <b>H:</b> Unaffected.                              |                |

| Addressing<br>Modes | Assembly Syntax  | Encoding                      | Clocks |

|---------------------|------------------|-------------------------------|--------|

| IR:                 | CALL @Rd         | 00011111_Rdnz_0000            | 10     |

| DA:                 | CALL address     | 01011111_0000_0000<br>address | 12     |

| Х:                  | CALL address(Rd) | 01011111_Rdnz_0000<br>address | 13     |

Notes:

1. The address loaded into the PC is the *address* of the destination operand, not the data *at* the destination address.

2. In the case of CALL @Rd a data (or stack) memory access at the address in Rd is performed but the data is discarded.

3. Bits 3-0 of the opcode are ignored.

| CALR dst            |                                                                                                                                                            | dst: RA            |        |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|

| Operation:          | SP <= SP - 2<br>@SP <= PC<br>PC <= PC - (2 x displacement)                                                                                                 |                    |        |

| Flags:              | <ul> <li>C: Unaffected.</li> <li>Z: Unaffected.</li> <li>S: Unaffected.</li> <li>V: Unaffected.</li> <li>D: Unaffected.</li> <li>H: Unaffected.</li> </ul> |                    |        |

| Addressing<br>Modes | Assembly Syntax                                                                                                                                            | Encoding           | Clocks |

| RA:                 | CALR address                                                                                                                                               | 1101dddd_dddd_dddd | 10     |

#### Notes:

1. The Zilog documentation incorrectly states that the displacement is *added* to the Program Counter. The Zilog Z8000 devices actually *subtract* the displacement from the Program Counter. The Y8002 design matches this behavior

2. The PC used for the address calculation is the PC of the *next* instruction.

3. The displacement is a 12-bit twos-complement number in the range -2048 to +2047. Thus the destination must be in the range -4092 to +4098 from the address of the CALR instruction.

## CLR

Clear

| CLR dst<br>CLRB     |                                                                                                                                                            | dst: R, IR, DA, X             |        |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------|

| Operation:          | dst <= 0                                                                                                                                                   |                               |        |

| Flags:              | <ul> <li>C: Unaffected.</li> <li>Z: Unaffected.</li> <li>S: Unaffected.</li> <li>V: Unaffected.</li> <li>D: Unaffected.</li> <li>H: Unaffected.</li> </ul> |                               |        |

| Addressing<br>Modes | Assembly Syntax                                                                                                                                            | Encoding                      | Clocks |

| R:                  | CLR Rd                                                                                                                                                     | 10001101_Rddd_1000            | 7      |

|                     | CLRB Rbd                                                                                                                                                   | 10001100_Rbdd_1000            | 7      |

| IR:                 | CLR @Rd                                                                                                                                                    | 00001101_Rdnz_1000            | 8      |

|                     | CLRB @Rd                                                                                                                                                   | 00001100_Rdnz_1000            | 8      |

| DA:                 | CLR address                                                                                                                                                | 01001101_0000_1000<br>address | 11     |

|                     | CLRB address                                                                                                                                               | 01001100_0000_1000<br>address | 11     |

|                     |                                                                                                                                                            |                               | 10     |

X:

CLR addr(Rd)

01001101\_Rdnz\_1000

12

address

CLRB addr(Rd)

01001100\_Rdnz\_1000

12

address

12

12

| COM dst<br>COMB | dst: R, IR, DA, X                                                                                                                                                                                                                                                                            |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:      | dst <= ~dst                                                                                                                                                                                                                                                                                  |

| Flags:          | <ul> <li>C: Unaffected.</li> <li>Z: Set if result is zero; cleared otherwise.</li> <li>S: Set if result is negative; cleared otherwise.</li> <li>V: Set if result parity is even; cleared otherwise (COMB);<br/>Unaffected (COM).</li> <li>D: Unaffected.</li> <li>H: Unaffected.</li> </ul> |

| Addressing<br>Modes | Assembly Syntax | Encoding                      | Clocks |

|---------------------|-----------------|-------------------------------|--------|

| R:                  | COM Rd          | 10001101_Rddd_0000            | 7      |

|                     | COMB Rbd        | 10001100_Rbdd_0000            | 7      |

| IR:                 | COM @Rd         | 00001101_Rdnz_0000            | 12     |

|                     | COMB @Rd        | 00001100_Rdnz_0000            | 12     |

| DA:                 | COM address     | 01001101_0000_0000            | 15     |

|                     |                 | address                       | 15     |

|                     | COMB address    | 01001100_0000_0000<br>address | 15     |

| X:                  | COM addr(Rd)    | 01001101_Rdnz_0000            | 16     |

|                     |                 | address                       |        |

|                     | COMB addr(Rd)   | 01001100_Rdnz_0000<br>address | 16     |

|                     |                 |                               |        |

## COMFLG

#### **Complement Flag**

| <b>COMFLG</b> flags |                                                                                                                                                                                                                                  | flag: C, Z, S, P, V  |        |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------|--|

| Operation:          | FCW[7:4] <= FCW[7:4] ^ inst[7:4]                                                                                                                                                                                                 |                      |        |  |

| Flags:              | <ul> <li>C: Complemented if specified; u</li> <li>Z: Complemented if specified; u</li> <li>S: Complemented if specified; u</li> <li>V: Complemented if specified; u</li> <li>D: Unaffected.</li> <li>H: Complemented.</li> </ul> | naffected otherwise. |        |  |

| Addressing<br>Modes | Assembly Syntax                                                                                                                                                                                                                  | Encoding             | Clocks |  |

|                     | COMFLG flags                                                                                                                                                                                                                     | 10001101_CZSV_0101   | 7      |  |

|                     |                                                                                                                                                                                                                                  |                      |        |  |

#### Notes:

1. The Z8000 documentation lists the H flag as undefined, when in fact it is always complemented. The Y8002 design matches this behavior.

| CP dst, src<br>CPB<br>CPL | dst: R<br>src: R, IR, DA, X                                                                                                                                                                                                                                                                             |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:                | dst - src                                                                                                                                                                                                                                                                                               |

| Flags:                    | <ul> <li>C: Set if arithmetic borrow from MSB; cleared otherwise.</li> <li>Z: Set if result is zero; cleared otherwise.</li> <li>S: Set if result is negative; cleared otherwise.</li> <li>V: Set if arithmetic overflow; cleared otherwise.</li> <li>D: Unaffected.</li> <li>H: Unaffected.</li> </ul> |

| Addressing<br>Modes | Assembly Syntax | Encoding           | Clocks |

|---------------------|-----------------|--------------------|--------|

| R:                  | CP Rd, Rs       | 10001011_Rsss_Rddd | 4      |

|                     | CPB Rbd, Rbs    | 10001010_Rbss_Rbdd | 4      |

|                     | CPL RRd, RRs    | 10010000_RRss_RRdd | 8      |

| IM:                 | CP Rd, #data    | 00001011_0000_Rddd | 7      |

|                     |                 | #data              |        |

|                     | CPB Rbd, #data  | 00001010_0000_Rbdd | 7      |

|                     |                 | #data   #data      |        |

|                     | CPL RRd, #data  | 00010000_0000_RRdd | 14     |

|                     |                 | #data (high)       |        |

|                     |                 | #data (low)        |        |

| Addressing<br>Modes | Assembly Syntax   | Encoding                      | Clocks |

|---------------------|-------------------|-------------------------------|--------|

| IR:                 | CP Rd, @Rs        | 00001011_Rsnz_Rddd            | 7      |

|                     | CPB Rbd, @Rs      | 00001010_Rsnz_Rbdd            | 7      |

|                     | CPL RRd, @Rs      | 00010000_Rsnz_RRdd            | 14     |

| DA:                 | CP Rd, address    | 01001011_0000_Rddd<br>address | 9      |

|                     |                   | audress                       |        |

|                     | CPB Rbd, address  | 01001010_0000_Rbdd            | 9      |

|                     |                   | address                       |        |

|                     | CPL RRd, address  | 01010000_0000_RRdd            | 15     |

|                     |                   | address                       |        |

| X:                  | CP Rd, addr(Rs)   | 01001011_Rsnz_Rddd            | 10     |

|                     |                   | address                       |        |

|                     | CPB Rbd, addr(Rs) | 01001010_Rsnz_Rbdd            | 10     |

|                     |                   | address                       |        |

|                     | CPL RRd, addr(Rs) | 01010000_Rsnz_RRdd            | 16     |

|                     |                   | address                       |        |

| CP dst, src<br>CPB | dst: IR, DA, X<br>src: IM                                                                                                                                                                                                                                                                               |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:         | dst - src                                                                                                                                                                                                                                                                                               |

| Flags:             | <ul> <li>C: Set if arithmetic borrow from MSB; cleared otherwise.</li> <li>Z: Set if result is zero; cleared otherwise.</li> <li>S: Set if result is negative; cleared otherwise.</li> <li>V: Set if arithmetic overflow; cleared otherwise.</li> <li>D: Unaffected.</li> <li>H: Unaffected.</li> </ul> |

| Addressing<br>Modes | Assembly Syntax     | Encoding                      | Clocks |

|---------------------|---------------------|-------------------------------|--------|

| IR:                 | CP @Rd, #data       | 00001101_Rdnz_0001            | 11     |

|                     |                     | #data                         |        |

|                     | CPB @Rd, #data      | 00001100_Rdnz_0001            | 11     |

|                     | ,                   | #data   #data                 |        |

| DA:                 | CP address, #data   | 01001101_0000_0001            | 14     |

| DA.                 | CF address, #data   | address                       | 14     |

|                     |                     | #data                         |        |

|                     | CPB address, #data  | 01001100_0000_0001            | 14     |

|                     | CI D address, #data | address                       | 14     |

|                     |                     | #data   #data                 |        |

| V.                  | CD (addr)Dd #data   | 01001101 Ddmg 0001            | 15     |

| Х:                  | CP (addr)Rd, #data  | 01001101_Rdnz_0001<br>address | 15     |

|                     |                     | #data                         |        |

|                     | CPB (addr)Rd, #data | 01001100_Rdnz_0001            | 15     |

|                     |                     | address                       | 10     |

|                     |                     | #data   #data                 |        |

## CPD

#### **Compare and Decrement**

| CPD dst, src, r, c<br>CPDB | cc dst: R<br>src: IR                                                                                                                                                                                                                                                                                                                                             |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:                 | dst - src<br>Rs <= (Word) ? Rs - 2 : Rs - 1<br>r <= r - 1                                                                                                                                                                                                                                                                                                        |

| Flags:                     | <ul> <li>C: Set if arithmetic borrow from MSB for compare; cleared otherwise.</li> <li>Z: Set if flags match cc after the last compare; cleared otherwise.</li> <li>S: Set if result is negative for compare; cleared otherwise.</li> <li>V: Set if r is zero after the decrement; cleared otherwise.</li> <li>D: Unaffected.</li> <li>H: Unaffected.</li> </ul> |

| Addressing<br>Modes | Assembly Syntax     | Encoding                                  | Clocks |

|---------------------|---------------------|-------------------------------------------|--------|

| IR:                 | CPD Rd, @Rs, r, cc  | 10111011_Rsnz_1000<br>0000_Rrrr_Rddd_cccc | 20     |

|                     | CPDB Rd, @Rs, r, cc | 10111010_Rsnz_1000<br>0000_Rrrr_Rddd_cccc | 20     |

|                     |                     |                                           |        |

#### Notes:

1. The C, Z, S and V flags are set as usual by the compare. This flag combination is used by the cc check. The Z and V flags are subsequently set per the instruction description.

2. Because the Rd, Rs and r registers are changed by the instruction, they must be separate and non-overlapping.

3. Bits 15-12 of the second word of the opcode are ignored.

# CPDR

### **Compare, Decrement and Repeat**

| CPDR dst, src, r<br>CPDRB | ;, cc                                                                                                                                                                                                                                                     | dst: R<br>src: IR                                                 |              |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------|

| Operation:                | dst - src<br>Rs <= (Word) ? Rs - 2 : Rs - 1<br>$r \le r - 1$<br>repeat until cc is true or $r = 0$                                                                                                                                                        |                                                                   |              |

| Flags:                    | <ul> <li>C: Set if arithmetic borrow from M</li> <li>Z: Set if flags match cc after the la</li> <li>S: Set if result is negative for the la</li> <li>V: Set if r is zero after the decremender</li> <li>D: Unaffected.</li> <li>H: Unaffected.</li> </ul> | st compare; cleared otherwise.<br>ast compare; cleared otherwise. | l otherwise. |

| Addressing<br>Modes       | Assembly Syntax                                                                                                                                                                                                                                           | Encoding                                                          | Clocks       |

| IR:                       | CPDR Rd, @Rs, r, cc                                                                                                                                                                                                                                       | 10111011_Rsnz_1100<br>0000_Rrrr_Rddd_cccc                         | 11 + 9n      |

| CPDRB Rd, @Rs, r, cc | 10111010_Rsnz_1100  | 11 + 9n |

|----------------------|---------------------|---------|

|                      | 0000_Rrrr_Rddd_cccc |         |

#### Notes:

1. The C, Z, S and V flags are set as usual by the compare. This flag combination is used by the cc check. The Z and V flags are subsequently set per the instruction description.

2. Because the Rd, Rs and r registers are changed by the instruction, they must be separate and non-overlapping.

3. Bits 15-12 of the second word of the opcode are ignored.

4. This instruction samples interrupts during each iteration. If an interrupt is pending, the instruction is stopped and the interrupt accepted. The PC saved during the interrupt acknowledge cycle in this case is the PC of the running instruction, allowing the instruction to restart after the interrupt has been serviced.

# CPI

### **Compare and Increment**

| <b>CPI</b> dst, src, r, cc<br><b>CPIB</b> | dst: R<br>src: IR                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:                                | dst - src<br>Rs <= (Word) ? Rs + 2 : Rs + 1<br>r <= r - 1                                                                                                                                                                                                                                                                                                  |

| Flags:                                    | <ul> <li>C: Set if arithmetic borrow from MSB for the last compare; cleared otherwise.</li> <li>Z: Set if flags match cc after the last compare; cleared otherwise.</li> <li>S: Set if result is negative for the last compare; cleared otherwise.</li> <li>V: Set if r is zero after the decrement; cleared otherwise.</li> <li>D: Unaffected.</li> </ul> |

| Addressing<br>Modes | Assembly Syntax     | Encoding                                  | Clocks |

|---------------------|---------------------|-------------------------------------------|--------|

| IR:                 | CPI Rd, @Rs, r, cc  | 10111011_Rsnz_0000<br>0000_Rrrr_Rddd_cccc | 20     |

|                     | CPIB Rd, @Rs, r, cc | 10111010_Rsnz_0000<br>0000_Rrrr_Rddd_cccc | 20     |

### Notes:

1. The C, Z, S and V flags are set as usual by the compare. This flag combination is used by the cc check. The Z and V flags are subsequently set per the instruction description.

2. Because the Rd, Rs and r registers are changed by the instruction, they must be separate and non-overlapping.

3. Bits 15-12 of the second word of the opcode are ignored.

### **CPIR** Compare, Increment and Repeat

| CPIR dst, src, r,<br>CPIRB | сс                                                                                                                                                                                                                                           | dst: R<br>src: IR                                               |        |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------|

| Operation:                 | dst - src<br>Rs <= (Word) ? Rs + 2 : Rs + 1<br>$r \le r - 1$<br>repeat until cc is true or $r = 0$                                                                                                                                           |                                                                 |        |

| Flags:                     | <ul> <li>C: Set if arithmetic borrow from</li> <li>Z: Set if flags match cc after the</li> <li>S: Set if result is negative for the</li> <li>V: Set if r is zero after the decrem</li> <li>D: Unaffected.</li> <li>H: Unaffected.</li> </ul> | last compare; cleared otherwis<br>last compare; cleared otherwi | se.    |

| Addressing<br>Modes        | Assembly Syntax                                                                                                                                                                                                                              | Encoding                                                        | Clocks |

| induces |                      |                     |         |

|---------|----------------------|---------------------|---------|

|         |                      |                     |         |

| IR:     | CPIR Rd, @Rs, r, cc  | 10111011_Rsnz_0100  | 11 + 9n |

|         |                      | 0000_Rrrr_Rddd_cccc |         |

|         |                      |                     |         |

|         | CPIRB Rd, @Rs, r, cc | 10111010_Rsnz_0100  | 11 + 9n |

|         |                      | 0000_Rrrr_Rddd_cccc |         |

|         |                      |                     |         |

#### Notes:

1. The C, Z, S and V flags are set as usual by the compare. This flag combination is used by the cc check. The Z and V flags are subsequently set per the instruction description.

2. Because the Rd, Rs and r registers are changed by the instruction, they must be separate and non-overlapping.

3. Bits 15-12 of the second word of the opcode are ignored.

4. This instruction samples interrupts during each iteration. If an interrupt is pending, the instruction is stopped and the interrupt accepted. The PC saved during the interrupt acknowledge cycle in this case is the PC of the running instruction, allowing the instruction to restart after the interrupt has been serviced.

## CPSD

### **Compare String and Increment**

| CPSD dst, src,<br>CPSDB | , r, cc dst: IR<br>src: IR                                                                                                                                                                                                                                                                                                                                                         |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Operation:              | dst - src<br>Rs <= (Word) ? Rs - 2 : Rs - 1<br>Rd <= (Word) ? Rd - 2 : Rd - 1<br>r <= r - 1                                                                                                                                                                                                                                                                                        |  |

| Flags:                  | <ul> <li>C: Set if arithmetic borrow from MSB for the last compare; cleared otherwise.</li> <li>Z: Set if flags match cc after the last compare; cleared otherwise.</li> <li>S: Set if result is negative for the last compare; cleared otherwise.</li> <li>V: Set if r is zero after the decrement; cleared otherwise.</li> <li>D: Unaffected.</li> <li>H: Unaffected.</li> </ul> |  |

| Modes | Assembly Syntax       | Encoding                                  | Clocks |

|-------|-----------------------|-------------------------------------------|--------|