## Dalian Good Display Co.,Ltd.

# LCD Module User Manual YM160160FSF-1

## Dalian Good Display Co., Ltd.

Tel: +86-411-84619565 Fax: +86-411-84619585 WebSite: http://www.good-lcd.com

## CONTENTS

| MAI | N FEATURES                                                                      | 4                |

|-----|---------------------------------------------------------------------------------|------------------|

|     | Module Classification Information                                               |                  |

| MEC | CHANICAL SPECIFICATIONS                                                         | 4                |

|     | Physical Characteristics                                                        |                  |

| ΟΡΤ | ICAL SPECIFICATIONS                                                             | 4                |

|     | Optical Characteristics<br>Optical Definitions<br>LED Backlight Characteristics | 4                |

| ELE | CTIRCAL SPECIFICATIONS                                                          | 4                |

|     | Details of Interface Pin Functions                                              | 4<br>4<br>4<br>4 |

|     | OULE RELIABILIGY AND LONGEVITY                                                  |                  |

|     | Module Reliability                                                              |                  |

| CAR | RE AND HANDLING PRECAUTIONS                                                     | 21               |

|     | Design and Mounting                                                             | 21<br>21<br>21   |

|     | Storage and Recycling                                                           |                  |

| QUALITY ASSURANCE STANDARDS                |    |

|--------------------------------------------|----|

| Inspection Condition                       |    |

| Color Definitions                          | 23 |

| Definition of Active Area and Viewing Area | 23 |

| Acceptance Sampling                        |    |

| Defects Classification                     | 24 |

| Acceptance Standards                       |    |

## **MAIN FEATURES**

| ITEM                              | STANDARD VALUE                                         | UNIT  |

|-----------------------------------|--------------------------------------------------------|-------|

| Dot Matrix                        | 160 X 160                                              | Dots  |

| LCD Type                          | FSTN/Transflective/Positive                            |       |

| LCD Duty                          | 1/160                                                  | Duty  |

| LCD Bias                          | 1/10                                                   | Bias  |

| Viewing Direction                 | 6:00                                                   | Clock |

| Backlight Type                    | Edge LED Backlight with white color                    |       |

| Connecter                         | FPC                                                    |       |

| IC Package                        | COG                                                    |       |

| Outline Dimension with FPC Folded | 79.85(W) × 72.7(H) × 5.00(T) (MAX)                     | mm    |

| Active Area (Diagonal)            | 3.73                                                   | inch  |

| Dot size                          | 0.32 ×0.32                                             | mm    |

| Dot Pitch                         | 0.34 ×0.34                                             | mm    |

| Operating Temperature             | -20 ~ +70                                              | °C    |

| Storage Temperature               | -30 ~ +80                                              | °C    |

| Net Weight                        | 36.0 ± 15% grams (typical)                             | g     |

| Interface                         | 3-wire,4-wire serial bus and 4-bit ,8-bit parallel bus |       |

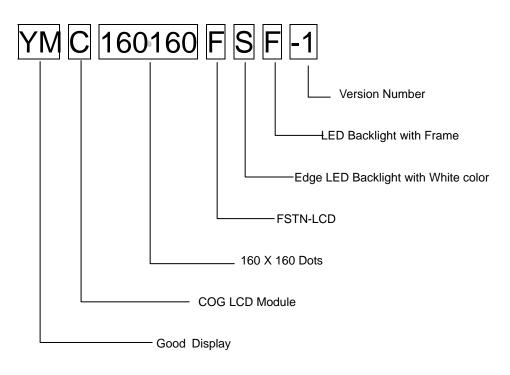

## **Module Classification Information**

## **Ordering Information**

| Part Number    | LCD Type       | Background Color | Display Color | Display Image |

|----------------|----------------|------------------|---------------|---------------|

| YM160160FSF-1  | FSTN Postive   | White Color      | Black Color   |               |

| YM160160SBSF-1 | STN BLUE       | Blue Color       | White Color   |               |

| YM160160DNSF-1 | FFSTN Negative | Black Color      | White Color   |               |

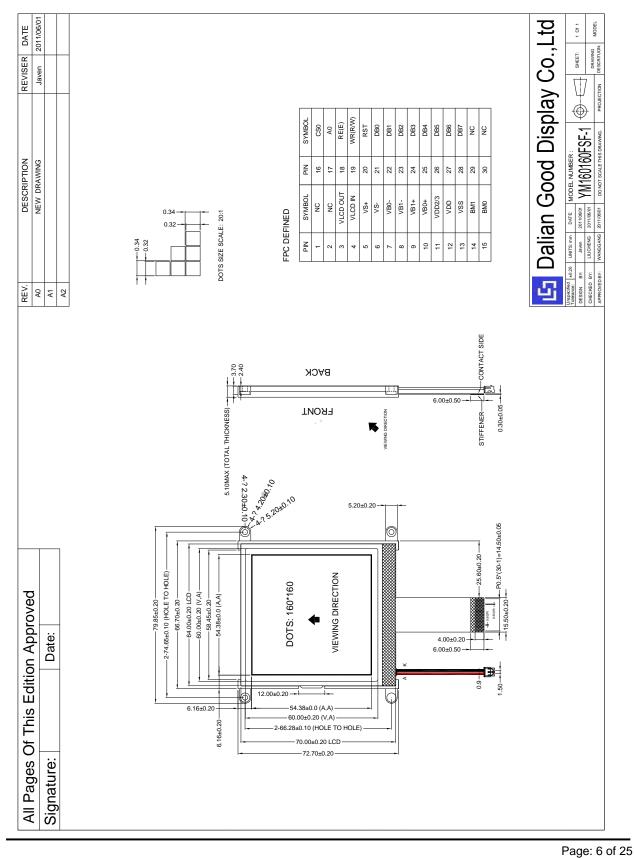

## **MECHANICAL SPECIFICATIONS**

## **Physical Characteristics**

| ITEM                             | SIZE                                |

|----------------------------------|-------------------------------------|

| Number of Dots                   | 160 X 160 Dots = 25600 Dots         |

| Dot Size                         | 0.32 (W)×0.32 (H) mm                |

| Dot Pitch                        | 0.34 (W)×0.34 (H) mm                |

| Active Area Diagonal             | Inches: 3.00"                       |

| Actic Arec Width and Llaight     | Millimeters: 64.0 (W) X 70.0 (H) mm |

| Actie Area Width and Height      | Inches: 2.52"(W) X 2.76" (H)        |

| Viewing Area Width and Llaight   | Millimeters: 60.0 (W) X60.0 (H) mm  |

| Viewing Area Width and Height    | Inches: 2.36"(W) X 2.36" (H)        |

| Module Width                     | Millimeters: 72.7mm                 |

|                                  | Inches: 2.86"                       |

| Overall Height with EDC unfolded | Millimeters:70.00 mm                |

| Overall Height with FPC unfolded | Inches: 2.76"                       |

| Overall Lieisht with EDC folded  | Millimeters:110.00 mm               |

| Overall Height with FPC folded   | Inches: 4.33"                       |

| Madula Dapth                     | Millimeters:5.10 mm                 |

| Module Depth                     | Inches: 0.20"                       |

| Module Connector Pitch           | 0.50mm                              |

| FPC Bend Radius                  | >R.40                               |

| Weight                           | 36.0 ± 15% grams (typical)          |

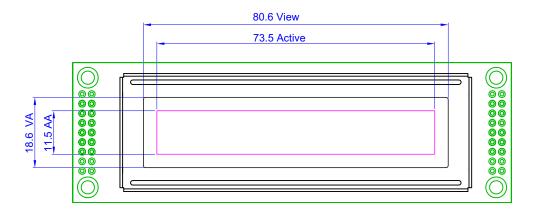

## YM160160FSF-1

### **Outline Module Drawing**

Dalian Good Display Co.,Ltd

## **ELECTRICAL SPECIFICATIONS**

### **Details of Interface Pin Functions**

| Pin No. | Pin Name | Туре | Descriptions                                                                                                               |  |  |

|---------|----------|------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | NC       |      | NO Connection                                                                                                              |  |  |

| 2       | NC       |      |                                                                                                                            |  |  |

| 3       | VLCD-OUT |      | High voltage LCD Power Supply. When internal $V_{\mbox{\tiny LCD}}$ is used,                                               |  |  |

|         |          |      | connect these pins together. When external $V_{\mbox{\tiny LCD}}$ source is                                                |  |  |

| 4       | VLCD-IN  | PWR  | used, connect external VLCD source to VLCDIN pins and leave VLCDOUT open.                                                  |  |  |

|         |          |      | Capacitor $C_{L}$ should be connected between $V_{LCD}$ and $V_{SS}$ . In                                                  |  |  |

|         |          |      | COG applications, keep the ITO trace resistance around $20\Omega$ .                                                        |  |  |

| 5       | VS+      |      | LCD SEG driving voltages. These are the voltage sources to                                                                 |  |  |

| 6       | VS-      |      | provide SEG driving currents. These voltages are generated                                                                 |  |  |

|         |          |      | internally.                                                                                                                |  |  |

| 7       | VBO-     |      | Connect capacitors of CBX value between V <sub>BX+</sub> and <sub>BX-</sub> ,and a                                         |  |  |

| 8       | VB1-     | PWR  | capacitor of CS value between Vs+ and Vs                                                                                   |  |  |

| 9       | VB1+     |      | The resistance of these traces directly affects the driving                                                                |  |  |

| 10      | VBO+     |      | strength of SEG electrodes and impacts the image of the LCD module, Minimize the trace resistance is critical in achieving |  |  |

|         |          |      | high quality image.                                                                                                        |  |  |

| 11      | VDD2/3   |      | VDD is the digital power supply and it should be connected to                                                              |  |  |

|         |          |      | a voltage source that is no higher than VDD2/ VDD3. VDD2/ VDD3                                                             |  |  |

| 12      | VDD      |      | is the analog power supply and it should be connected to the                                                               |  |  |

|         |          | PWR  | same power source.                                                                                                         |  |  |

|         |          |      | Please maintain the following relationship:                                                                                |  |  |

|         |          |      | $V_{DD}+1.3V \ge V_{DD2/3} \ge V_{DD}$                                                                                     |  |  |

|         |          |      | Minimize the trace resistance for this node.                                                                               |  |  |

| 10      | Vss      |      | Ground. Connect Vss and Vss2 to the shared GND pin                                                                         |  |  |

| 13      |          | GND  | Minimize the trace resistance for this node.                                                                               |  |  |

| 14      | DN4      |      | Rus mode: The interface bus made is determined by PM(4:0)                                                                  |  |  |

|         | BM1      | I    | Bus mode: The interface bus mode is determined by BM[1:0] by the following relationship:                                   |  |  |

| 15      | BM0      |      | BM(1:0) Mode                                                                                                               |  |  |

|         |          | I    | 01 6800/8-bit                                                                                                              |  |  |

|         |          | •    | 00 8080/8-bit                                                                                                              |  |  |

|         |          |      |                                                                                                                            |  |  |

| 16      | CS0      | I    | Chip Select. Chip is selected when "CS0="L". When the chip is                                                              |  |  |

|         |          |      | not selected [7:0] will be high impedance.                                                                                 |  |  |

| 17    | AO      | I/O | This is connected to the least significant bit of the normal MPU address bus, and it determines whether the data bits are data or a command.<br>A0 = "H": Indicate that D0 to D7 are display data<br>A0 = "L": Indicates that D0 to D7 are control data                                                                                          |

|-------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18    | R0[E]   | Γ   | When connected to an 8080 MPU, it is active LOW. This pad<br>is connected to the /RD signal of the 8080MPU, and the<br>NT7538 data bus is in an output status when this signal is "L".<br>When connected to a 6800 Series MPU, this is active HIGH.<br>This is used as an enable clock input of the 6800 series<br>MPU                           |

| 19    | WR[R/W] | I   | When connected to an 8080 MPU, this is active LOW. This terminal connects to the 8080 MPU /WR signal. The signals on the data bus are latched at the rising edge of the /WR signal.<br>When connected to a 6800 Series MPU, this is the read/write control signal input terminal.<br>When R/W = "H": Read<br>When R/W = "L": Write               |

| 20    | RST     | I   | When RST="L",all control registers are re-initialized by their default States. Since UC1698u has built-in Power-ON reset and software reset commands,RST pin is not required for proper chip operation.<br>An RC Fitter has been included on-chip. These are no need for external RC noise fitter. When RST is not used, connect the pin to VDD. |

| 21~28 | D0~D7   | I/O | 8-bit bi-directional data bus that is connected to the standard<br>8-bit microprocessor data bus.<br>When chip select is not active, DB0 to DB7 may be high<br>impedance.                                                                                                                                                                        |

| 29    | NC      |     | No Connection                                                                                                                                                                                                                                                                                                                                    |

| 30    | NC      |     |                                                                                                                                                                                                                                                                                                                                                  |

## **OPTICAL SPECIFICATIONS**

## **Optical Characteristics**

| ITEM                                                                                                           | SYMBOL | CONDITION        | MINIMUM | ТҮРІСАL | MAXIMUM |  |

|----------------------------------------------------------------------------------------------------------------|--------|------------------|---------|---------|---------|--|

| Viewing Angle (6 o'clock)<br>(Vertical, Horizontal)                                                            | (V)θ   | CR <u>&gt;</u> 2 | 30°     |         | 60°     |  |

| (venical, nonzonial)                                                                                           | (H)φ   | CR <u>≥</u> 2    | -45°    |         | 45°     |  |

| Contrast Ratio                                                                                                 | CR     |                  |         | 8       |         |  |

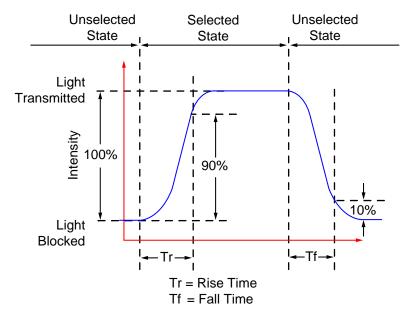

| LCD Response Time*                                                                                             | T rise | Ta = 25°C        |         | 150 ms  | 200 ms  |  |

|                                                                                                                | T fall | Ta = 25°C        |         | 150 ms  | 200 ms  |  |

| *Response Time: The amount of time it takes a liquid crystal cell to go from active to inactive or back again. |        |                  |         |         |         |  |

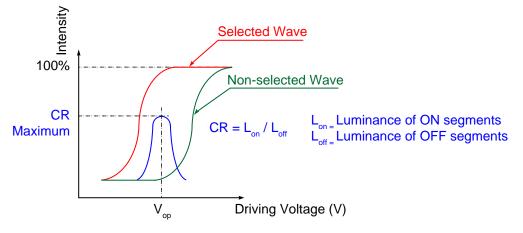

## **Optical Defination**

- Operating Voltage (V<sub>LCD</sub>): V<sub>OP</sub>

- Viewing Angle

- Vertical (V)0: 0°

- Horizontal (H)φ: 0°

- Frame Frequency: 64 Hz

- Driving Waveform: 1/16 Duty, 1/5 Bias

- Ambient Temperature (Ta): 25°C

## **Definition of Operation Voltage (Vop)**

Figure 6. Definition of Operation Voltage (V<sub>OP</sub>) (Negative)

## Definition of Response Time (Tr, Tf0)

Figure 7. Definition of Response Time (Tr, Tf) (Negative)

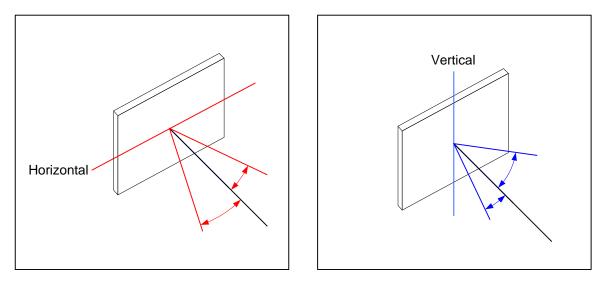

## Definition of Vertical and Horizontal Viewing Angles (CR $\geq$ 2)

Figure 8. Definition of Horizontal and Vertical Viewing Angles (CR>2)

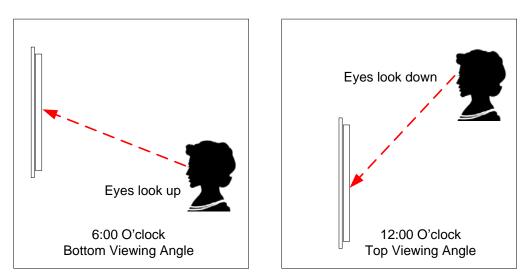

## Definition of 6 O'Clock and 12:00 O'Clock Viewing Angles

This module has a 6:00 o'clock viewing angle. A 6:00 o'clock viewing angle is a bottom viewing angle like what you would see when you look at a cell phone or calculator. A 12:00 o'clock viewing angle is a top viewing angle like what you would see when you look at the gauges in a golf cart or airplane.

Figure 9. Definition of 6:00 O'Clock and 12:00 O'Clock Viewing Angles

LEDs are "current" devices. The important aspect of driving an LED is the current flowing through it, not the voltage across it. Ideally, a current source would be used to drive the LEDs. In practice, a simple current limiting resistor in line from a voltage source will work well in most applications and is much less complex than a current source.

| Backlight Characteristics                      |         |       |       |  |  |

|------------------------------------------------|---------|-------|-------|--|--|

| PARAMETER                                      | MAXIMUM |       |       |  |  |

| Forward Current (I <sub>LED)</sub><br>V = 3.3V | 80 mA   | 90 mA | 95 mA |  |  |

| Forward Voltage (V <sub>LED</sub> )            |         | 3.30V |       |  |  |

## YM160160FSF-1

## Absolute Maximum Ratings

In accordance with IEC134, Note 1 and 2

| Symbol                 | Parameter                                                         | Min. | Max.                  | Unit |

|------------------------|-------------------------------------------------------------------|------|-----------------------|------|

| V <sub>DD</sub>        | Logic Supply voltage                                              | -0.3 | +4.0                  | V    |

| V <sub>DD2</sub>       | LCD Generator Supply voltage                                      | -0.3 | +4.0                  | V    |

| V <sub>DD3</sub>       | Analog Circuit Supply voltage                                     | -0.3 | +4.0                  | V    |

| $V_{DD2/3}$ - $V_{DD}$ | Voltage difference between $V_{\text{DD}}$ and $V_{\text{DD}2/3}$ |      | 1.6                   | V    |

| V <sub>LCD</sub>       | LCD Driving voltage (-25 <sup>o</sup> C ~ +75 <sup>o</sup> C)     | -0.3 | +19.8                 | V    |

| V <sub>IN</sub>        | Digital input signal                                              | -0.4 | V <sub>DD</sub> + 0.5 | V    |

| T <sub>OPR</sub>       | Operating temperature range                                       | -30  | +85                   | °C   |

| T <sub>STR</sub>       | Storage temperature                                               | -55  | +125                  | °C   |

#### NOTE:

- 1.  $V_{DD}$  is based on  $V_{SS} = 0V$

- 2. Stress beyond ranges listed above may cause permanent damages to the device.

## **DC** Characteristics

| Symbol               | Parameter                  | Conditions                                  | Min.        | Тур. | Max.               | Unit |

|----------------------|----------------------------|---------------------------------------------|-------------|------|--------------------|------|

| V <sub>DD</sub>      | Supply for digital circuit |                                             | 1.65        |      | 3.3                | V    |

| V <sub>DD2/3</sub>   | Supply for bias & pump     |                                             | 2.7         |      | 3.3                | V    |

| V <sub>LCD</sub>     | Charge pump output         | $V_{DD2/3} = 2.8V, 25^{\circ}C$             |             | 15.2 | 18                 | V    |

| VD                   | LCD data voltage           | $V_{DD2/3} = 2.8V, 25^{\circ}C$             | 1.09        |      | 1.95               | V    |

| V <sub>IL</sub>      | Input logic LOW            |                                             |             |      | $0.2V_{\text{DD}}$ | V    |

| VIH                  | Input logic HIGH           |                                             | $0.8V_{DD}$ |      |                    | V    |

| V <sub>OL</sub>      | Output logic LOW           | 0                                           |             |      | $0.2V_{\text{DD}}$ | V    |

| V <sub>OH</sub>      | Output logic HIGH          |                                             | $0.8V_{DD}$ |      |                    | V    |

| IIL                  | Input leakage current      |                                             |             |      | 1.5                | μΑ   |

| I <sub>SB</sub>      | Standby current            | $V_{DD} = V_{DD2/3} = 3.3V,$<br>Temp = 85°C |             |      | 50                 | μΑ   |

| C <sub>IN</sub>      | Input capacitance          |                                             |             | 5    | 10                 | PF   |

| COUT                 | Output capacitance         |                                             |             | 5    | 10                 | PF   |

| $R_{ON(SEG)}$        | SEG output impedance       | $V_{LCD} = 16.5V$                           |             | 850  | 1100               | Ω    |

| R <sub>ON(COM)</sub> | COM output impedance       | V <sub>LCD</sub> = 16.5V                    |             | 950  | 1100               | Ω    |

| f <sub>LINE</sub>    | Average line rate          | LC[4:3] = 10b, 25 <sup>o</sup> C            | -10%        | 37.0 | +10%               | Klps |

#### **AC CHARACTERISTICS**

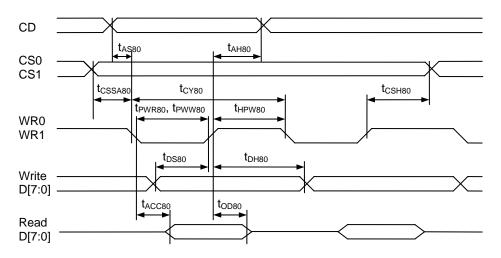

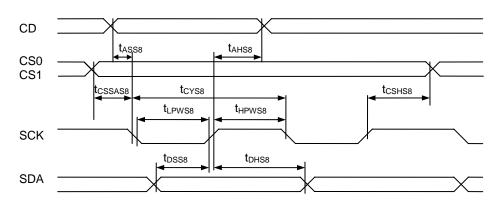

FIGURE 15: Parallel Bus Timing Characteristics (for 8080 MCU)

$(2.5V \le V_{DD} < 3.3V, Ta = -30 \text{ to } +85^{\circ}C)$

| Symbol                                    | Signal   | Description                                                                      | Condition                  | Min.                          | Max.     | Units |

|-------------------------------------------|----------|----------------------------------------------------------------------------------|----------------------------|-------------------------------|----------|-------|

| t <sub>AS80</sub><br>t <sub>AH80</sub>    | CD       | Address setup time<br>Address hold time                                          |                            | 0<br>0                        | -        | nS    |

| t <sub>CY80</sub>                         |          | System cycle time<br>16-bit bus (read)<br>(write)<br>8-bit bus (read)<br>(write) | LC[7:6]=10b<br>LC[7:6]=01b | 170<br>130<br>100<br>80<br>90 | I        | nS    |

| t <sub>PWR80</sub>                        | WR1      | Pulse width 16-bit (read)<br>8-bit                                               |                            | 85<br>50                      | 1        | nS    |

| t <sub>PWW80</sub>                        | WR0      | Pulse width 16-bit (write)<br>8-bit                                              | LC[7:6]=10b<br>LC[7:6]=01b | 65<br>40<br>45                | Ι        | nS    |

| t <sub>HPW80</sub>                        | WR0, WR1 | High pulse width<br>16-bit bus (read)<br>(write)<br>8-bit bus (read)<br>(write)  | LC[7:6]=10b<br>LC[7:6]=01b | 85<br>65<br>50<br>40<br>45    | Ι        | nS    |

| t <sub>DS80</sub><br>t <sub>DH80</sub>    | D0~D15   | Data setup time<br>Data hold time                                                |                            | 30<br>0                       | I        | nS    |

| t <sub>ACC80</sub><br>t <sub>OD80</sub>   |          | Read access time<br>Output disable time                                          | C <sub>L</sub> = 100pF     | -<br>15                       | 60<br>30 | nS    |

| T <sub>CSSA80</sub><br>t <sub>CSH80</sub> | CS1/CS0  | Chip select setup time                                                           |                            | 5<br>5                        |          | nS    |

| Symbol                                    | Signal   | Description                                                                      | Condition                  | Min.                            | Max.      | Units |

|-------------------------------------------|----------|----------------------------------------------------------------------------------|----------------------------|---------------------------------|-----------|-------|

| t <sub>AS80</sub><br>t <sub>AH80</sub>    | CD       | Address setup time<br>Address hold time                                          |                            | 0<br>0                          | -         | nS    |

| t <sub>CY80</sub>                         |          | System cycle time<br>16-bit bus (read)<br>(write)<br>8-bit bus (read)<br>(write) | LC[7:6]=10b<br>LC[7:6]=01b | 320<br>270<br>180<br>145<br>220 | Ι         | nS    |

| t <sub>PWR80</sub>                        | WR1      | Pulse width 16-bit (read)<br>8-bit                                               |                            | 160<br>90                       | -         | nS    |

| t <sub>PWW80</sub>                        | WR0      | Pulse width 16-bit (write)<br>8-bit                                              | LC[7:6]=10b<br>LC[7:6]=01b | 135<br>73<br>110                | -         | nS    |

| t <sub>HPW80</sub>                        | WR0, WR1 | High pulse width<br>16-bit bus (read)<br>(write)<br>8-bits bus (read)<br>(write) | LC[7:6]=10b<br>LC[7:6]=01b | 160<br>135<br>90<br>72<br>110   | Ι         | nS    |

| t <sub>DS80</sub><br>t <sub>DH80</sub>    | D0~D15   | Data setup time<br>Data hold time                                                |                            | 60<br>0                         | -         | nS    |

| t <sub>ACC80</sub><br>t <sub>OD80</sub>   |          | Read access time<br>Output disable time                                          | C <sub>L</sub> = 100pF     | -<br>30                         | 120<br>60 | nS    |

| t <sub>CSSA80</sub><br>t <sub>CSH80</sub> | CS1/CS0  | Chip select setup time                                                           |                            | 10<br>10                        |           | nS    |

$(1.65V \le V_{DD} < 2.5V, Ta = -30 \text{ to } +85^{\circ}C)$

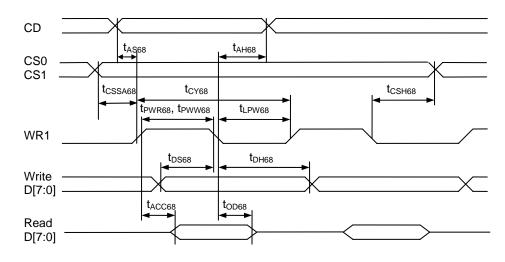

FIGURE 16: Parallel Bus Timing Characteristics (for 6800 MCU)

$(2.5V \le V_{DD} < 3.3V, Ta = -30 \text{ to } +85^{\circ}C)$

| Symbol                                    | Signal  | Description                                                                      | Condition                  | Min.                          | Max.     | Units |

|-------------------------------------------|---------|----------------------------------------------------------------------------------|----------------------------|-------------------------------|----------|-------|

| t <sub>AS68</sub><br>t <sub>AH68</sub>    | CD      | Address setup time<br>Address hold time                                          |                            | 0<br>0                        | -        | nS    |

| t <sub>CY68</sub>                         |         | System cycle time<br>16-bit bus (read)<br>(write)<br>8-bit bus (read)<br>(write) | LC[7:6]=10b<br>LC[7:6]=01b | 170<br>130<br>100<br>80<br>90 | _        | nS    |

| t <sub>PWR68</sub>                        | WR1     | Pulse width 16-bit (read)<br>8-bit                                               |                            | 85<br>50                      | -        | nS    |

| t <sub>PWW68</sub>                        |         | Pulse width 16-bit (write)<br>8-bit                                              | LC[7:6]=10b<br>LC[7:6]=01b | 65<br>40<br>45                | Ι        | nS    |

| t∟pw68                                    |         | Low pulse width<br>16-bit bus (read)<br>(write)<br>8-bit bus (read)<br>(write)   | LC[7:6]=10b<br>LC[7:6]=01b | 85<br>65<br>50<br>40<br>45    | -        | nS    |

| t <sub>DS68</sub><br>t <sub>DH68</sub>    | D0~D7   | Data setup time<br>Data hold time                                                |                            | 30<br>0                       | Ι        | nS    |

| t <sub>ACC68</sub><br>t <sub>OD68</sub>   |         | Read access time<br>Output disable time                                          | C <sub>L</sub> = 100pF     | -<br>15                       | 60<br>30 | nS    |

| t <sub>CSSA68</sub><br>t <sub>CSH68</sub> | CS1/CS0 | Chip select setup time                                                           |                            | 5<br>5                        |          | nS    |

| Symbol              | Signal  | Description                           | Condition        | Min. | Max. | Units |

|---------------------|---------|---------------------------------------|------------------|------|------|-------|

| t <sub>AS68</sub>   | CD      | Address setup time                    |                  | 0    | -    | nS    |

| t <sub>AH68</sub>   |         | Address hold time                     |                  | 0    |      |       |

| t <sub>CY68</sub>   |         | System cycle time                     |                  |      | -    | nS    |

|                     |         | 16-bit bus (read)                     |                  | 320  |      |       |

|                     |         | (write)                               |                  | 270  |      |       |

|                     |         | 8-bit bus (read)                      |                  | 180  |      |       |

|                     |         | (write)                               | LC[7:6]=10b      | 145  |      |       |

|                     |         |                                       | LC[7:6]=01b      | 220  |      |       |

| t <sub>PWR68</sub>  | WR1     | Pulse width 16-bit (read)             |                  | 160  | _    | nS    |

|                     |         | 8-bit                                 |                  | 90   |      |       |

| t <sub>PWW68</sub>  |         | Pulse width 16-bit (write)            |                  | 135  | _    | nS    |

|                     |         | 8-bit                                 | LC[7:6]=10b      | 73   |      |       |

|                     |         |                                       | LC[7:6]=01b      | 110  |      |       |

| t <sub>LPW68</sub>  |         | Low pulse width                       |                  |      | _    | nS    |

|                     |         | 16-bit bus (read)                     |                  | 160  |      |       |

|                     |         | (write)                               |                  | 135  |      |       |

|                     |         | 8-bit bus (read)                      |                  | 90   |      |       |

|                     |         | (write)                               | LC[7:6]=10b      | 72   |      |       |

|                     |         | , , , , , , , , , , , , , , , , , , , | LC[7:6]=01b      | 110  |      |       |

| t <sub>DS68</sub>   | D0~D7   | Data setup time                       |                  | 60   | _    | nS    |

| t <sub>DH68</sub>   |         | Data hold time                        | ٩                | 0    |      |       |

| t <sub>ACC68</sub>  |         | Read access time                      | $C_{L} = 100 pF$ | -    | 120  | nS    |

| t <sub>OD68</sub>   |         | Output disable time                   |                  | 30   | 60   |       |

| t <sub>CSSA68</sub> | CS1/CS0 | Chip select setup time                |                  | 10   |      | nS    |

| t <sub>CSH68</sub>  | 031/030 | Chip select setup tille               |                  | 10   |      |       |

$(1.65V \le V_{DD} < 2.5V, Ta = -30 \text{ to } +85^{\circ}C)$

FIGURE 17: Serial Bus Timing Characteristics (for S8/S8uc)

| $(2.5V \le V_{DD} < 3.3V, Ta = -30 \text{ to } +85^{\circ}C)$ | (2.5V | $\leq V_{DD} <$ | 3.3V, | Ta= | -30 to | +85 | C) |

|---------------------------------------------------------------|-------|-----------------|-------|-----|--------|-----|----|

|---------------------------------------------------------------|-------|-----------------|-------|-----|--------|-----|----|

| Symbol                                 | Signal  | Description                       | Condition | Min.    | Max. | Units |

|----------------------------------------|---------|-----------------------------------|-----------|---------|------|-------|

| t <sub>ASS8</sub>                      | CD      | Address setup time                |           | 0       | -    | nS    |

| t <sub>AHS8</sub>                      |         | Address hold time                 |           | 0       | -    | nS    |

| t <sub>CYS8</sub>                      | SCK     | System cycle time                 |           | 40      | _    | nS    |

| t <sub>LPWS8</sub>                     |         | Low pulse width                   | C C       | 20      | _    | nS    |

| t <sub>HPWS8</sub>                     |         | High pulse width                  |           | 20      | _    | nS    |

| t <sub>DSS8</sub><br>t <sub>DHS8</sub> | SDA     | Data setup time<br>Data hold time |           | 15<br>0 | -    | nS    |

| tcssas8<br>t <sub>CSHS8</sub>          | CS1/CS0 | Chip select setup time            |           | 5<br>5  |      | nS    |

(1.65V  $\leq$  V\_{DD} < 2.5V, Ta= –30 to +85  $^{\rm o}C)$

| Symbol                                 | Signal  | Description                       | Condition | Min.     | Max. | Units |

|----------------------------------------|---------|-----------------------------------|-----------|----------|------|-------|

| t <sub>ASS8</sub>                      | CD      | Address setup time                |           | 0        | -    | nS    |

| t <sub>AHS8</sub>                      |         | Address hold time                 |           | 0        | -    | nS    |

| t <sub>CYS8</sub>                      | SCK     | System cycle time                 |           | 75       | -    | nS    |

| t <sub>LPWS8</sub>                     |         | Low pulse width                   |           | 37       | -    | nS    |

| t <sub>HPWS8</sub>                     |         | High pulse width                  |           | 38       | -    | nS    |

| t <sub>DSS8</sub><br>t <sub>DHS8</sub> | SDA     | Data setup time<br>Data hold time |           | 30<br>0  | -    | nS    |

| tcssas8<br>t <sub>cshs8</sub>          | CS1/CS0 | Chip select setup time            |           | 10<br>10 |      | nS    |

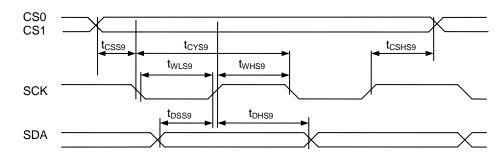

FIGURE 18: Serial Bus Timing Characteristics (for S9)

$(2.5V \le V_{DD} < 3.3V, Ta = -30 \text{ to } +85^{\circ}C)$

| Symbol                                 | Signal  | Description                       | Condition | Min.    | Max. | Units |

|----------------------------------------|---------|-----------------------------------|-----------|---------|------|-------|

| t <sub>CYS9</sub>                      | SCK     | System cycle time                 |           | 40      | Ι    | nS    |

| t <sub>LPWS9</sub>                     |         | Low pulse width                   |           | 20      | Ι    | nS    |

| t <sub>HPWS9</sub>                     |         | High pulse width                  | ч.<br>Т   | 20      | -    | nS    |

| t <sub>DSS9</sub><br>t <sub>DHS9</sub> | SDA     | Data setup time<br>Data hold time |           | 15<br>0 | Ι    | nS    |

| tcssas9<br>t <sub>CSHS9</sub>          | CS1/CS0 | Chip select setup time            |           | 5<br>5  |      | nS    |

(1.65V  $\leq$  V\_{DD} < 2.5V, Ta= –30 to +85  $^{\circ}\text{C}\text{)}$

| Symbol                                 | Signal  | Description                       | Condition | Min.     | Max. | Units |

|----------------------------------------|---------|-----------------------------------|-----------|----------|------|-------|

| t <sub>CYS9</sub>                      | SCK     | System cycle time                 |           | 75       | Ι    | nS    |

| t <sub>LPWS9</sub>                     |         | Low pulse width                   |           | 38       | -    | nS    |

| t <sub>HPWS9</sub>                     |         | High pulse width                  |           | 38       | -    | nS    |

| t <sub>DSS9</sub><br>t <sub>DHS9</sub> | SDA     | Data setup time<br>Data hold time |           | 30<br>0  | -    | nS    |

| tcssas9<br>t <sub>CSHS9</sub>          | CS1/CS0 | Chip select setup time            |           | 10<br>10 |      | nS    |

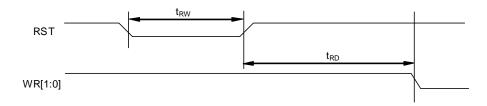

#### FIGURE 19: Reset Characteristics

$(1.65V \le V_{DD} < 3.3V, Ta = -30 \text{ to } +85^{\circ}C)$

| Symbol          | Signal  | Description             | Condition | Min. | Max. | Units |

|-----------------|---------|-------------------------|-----------|------|------|-------|

| t <sub>RW</sub> | RST     | Reset low pulse width   |           | 3    | -    | μS    |

| t <sub>RD</sub> | RST, WR | Reset to WR pulse delay |           | 10   | -    | mS    |

## **Command Table**

The following is a list of host commands supported by UC1698u

| TI | he following is a list of ho<br>C/D: 0: Control,<br>W/R: 0: Write Cycle,<br>#: Useful Data bits | st cor | 1<br>1 | ids su<br>: Data<br>: Rea<br>: Do | a<br>d Cyc  | cle          | UC1    | 698u               |        |             |             |                          |                                                      |           |

|----|-------------------------------------------------------------------------------------------------|--------|--------|-----------------------------------|-------------|--------------|--------|--------------------|--------|-------------|-------------|--------------------------|------------------------------------------------------|-----------|

|    | Command                                                                                         | C/D    | W/R    | D7                                | D6          | D5           | D4     | D3                 | D2     | D1          | D0          | Actio                    | n                                                    | Default   |

| 1  | Write Data Byte                                                                                 | 1      | 0      | #                                 | #           | #            | #      | #                  | #      | #           | #           | Write 1                  | byte                                                 | N/A       |

| 2  | Read Data Byte                                                                                  | 1      | 1      | #                                 | #           | #            | #      | #                  | #      | #           | #           | Read 1                   | byte                                                 | N/A       |

| 3  | Get Status & PM                                                                                 | 0      | 1      | GE<br>Ver                         | MX          | MY<br>Code ( |        | DE<br>MO[6:<br>PID |        | MD          | MS<br>[1:0] | Get {Statu<br>PMO, Produ | Get {Status, Ver,<br>PMO, Product Code,<br>PID, MID} |           |

|    | Set Column Address LSB                                                                          | 0      | 0      | 0                                 | 0           | 0            | 011)   | #                  | #      | #           | [1.0]<br>#  | Set CA[3:0]              |                                                      | 0         |

| 4  | Set Column Address LSB                                                                          | 0      | 0      | 0                                 | 0           | 0            | 1      | #<br>0             | #      | #           | #           | Set CA                   |                                                      | 0         |

| 5  | Set Temp. Compensation                                                                          | 0      | 0      | 0                                 | 0           | 1            | 0      | 0                  | #<br>1 | #           | #           | Set CA                   |                                                      | 0         |

| 6  | Set Power Control                                                                               | 0      | 0      | 0                                 | 0           | 1            | 0      | 1                  | 0      | #           | #           | Set PC                   |                                                      | 10b       |

| -  | Set Adv. Program Control                                                                        | 0      | 0      | 0                                 | 0           | 1            | 1      | 0                  | 0      | #<br>0      | R #         | Set APC[F                |                                                      | 100       |

| 7  | (double-byte command)                                                                           | 0      | 0      | #                                 | #           | #            | #      | #                  | #      | #           | к<br>#      | R = 0 (                  |                                                      | N/A       |

|    |                                                                                                 | 0      | 0      | #<br>0                            | #<br>1      | #<br>0       | #<br>0 | #                  | #      | #           | #           |                          |                                                      | 0         |

| 8  | Set Scroll Line LSB                                                                             | -      | -      | -                                 |             | -            | -      |                    |        |             |             | Set SL[                  |                                                      | 0         |

|    | Set Scroll Line MSB                                                                             | 0      | 0      | 0                                 | 1           | 0            | 1      | #                  | #      | #           | #           | Set SL                   |                                                      | 0         |

| 9  | Set Row Address LSB                                                                             | 0      | 0      | 0                                 | 1           | 1            | 0      | #                  | #      | #           | #           | Set RA                   |                                                      | 0         |

|    | Set Row Address MSB                                                                             | 0      | 0      | 0                                 | 1           | 1            | 1      | #                  | #      | #           | #           | Set RA                   | [7:4]                                                | 0         |

| 10 | Set V <sub>BIAS</sub> Potentiometer (double-byte command)                                       | 0<br>0 | 0<br>0 | 1<br>#                            | 0<br>#      | 0<br>#       | 0<br># | 0<br>#             | 0<br># | 0<br>#      | 1<br>#      | Set PM                   |                                                      | 40H       |

| 11 | Set Partial Display Control                                                                     | 0      | 0      | 1                                 | 0           | 0            | 0      | 0                  | 1      | 0           | _#          | Set LC                   |                                                      | 0         |

| 12 | Set RAM Address Control                                                                         | 0      | 0      | 1                                 | 0           | 0            | 0      | 1                  | #      | #           | <b>#</b>    | Set AC                   | [2:0]                                                | 001b      |

| 13 | Set Fixed Lines                                                                                 | 0<br>0 | 0<br>0 | 1<br>#                            | 0<br>#      | 0<br>#       | 1<br># | 0<br>#             | 0<br># | 0<br>#      | 0<br>#      | Set {FLT,                | FLB}                                                 | 0         |

| 14 | Set Line Rate                                                                                   | 0      | 0      | 1                                 | 0           | 1            | 0      | 0                  | 0      | #           | #           | Set LC                   | 4:31                                                 | 10b       |

| _  | Set All-Pixel-ON                                                                                | 0      | 0      | 1                                 | 0           | 1            | 0      | 0                  | 1      | 0           | #           | Set DC                   |                                                      | 0         |

|    | Set Inverse Display                                                                             | 0      | 0      | 1                                 | 0           | 1            | 0      | 0                  | 1      | 1           | #           | Set DC                   |                                                      | 0         |

| 17 | Set Display Enable                                                                              | 0      | 0      | 1                                 | 0           | 1            | 0      | 1                  | #      | #           | #           | Set DC[4:2]              |                                                      | 110b      |

| 18 |                                                                                                 | 0      | 0      | 1                                 | 1           | 0            | Ø 0    | 0                  | #      | #           | #           | Set LC[2:0]              |                                                      | 0         |

|    | Set N-Line Inversion                                                                            | 0      | 0      | 1                                 | 1           | 0            | 0<br># | 1<br>#             | 0<br># | 0<br>#      | 0<br>#      | Set NIV                  |                                                      | 1DH       |

| 20 | Set Color Pattern                                                                               | 0      | 0      | 1                                 | 1           | 0            | 1      | <i>#</i>           | #<br>0 | <i>#</i>    | #           | Set LC                   | 151                                                  | 0 (BGR)   |

| 20 | Set Color Mode                                                                                  | 0      | 0      | 1                                 | 1           | 0            | 1      | 0                  | 1      | #           | #           | Set LC                   |                                                      | 10b       |

| 22 | Set COM Scan Function                                                                           | 0      | 0      | 1                                 |             | 0            | 1      | 1                  | #      | #           | #           | Set CSF                  |                                                      | 000b      |

|    |                                                                                                 | 0      | -      | 1                                 |             | 1            |        | 0                  |        | #<br>1      | #<br>0      |                          |                                                      | N/A       |

| 23 | System Reset                                                                                    | -      | 0      | 1                                 | 1           |              | 0      |                    | 0      | 1           |             | System F                 |                                                      |           |

| 24 | NOP                                                                                             | 0      | 0      |                                   | 1           | 1            | 0      | 0                  | 0      |             | 1           | No oper                  |                                                      | N/A       |

| 25 | Set Test Control                                                                                | 0      | 0      | 1                                 | 1           | 1            | 0      | 0                  | 1      |             | T           | For testing              |                                                      | N/A       |

| -  | (double-byte command)                                                                           | 0      | 0      | #                                 | #           | #            | #      | #                  | #      | #           | #           | Do not                   |                                                      | 111 10    |

| 26 | Set LCD Bias Ratio                                                                              | 0      | 0      | 1                                 | 1           | 1            | 0      | 1                  | 0      | #           | #           | Set BR                   | [1:0]                                                | 11b: 12   |

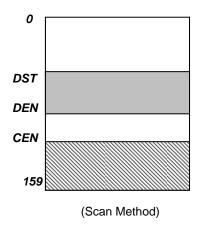

| 27 | Set COM End                                                                                     | 0<br>0 | 0<br>0 | 1<br>-                            | 1<br>#      | 1<br>#       | 1<br># | 0<br>#             | 0<br># | 0<br>#      | 1<br>#      | Set CEN                  | l[6:0]                                               | 159       |

| 28 | Set Partial Display Start                                                                       | 0<br>0 | 0<br>0 | 1<br>-                            | 1<br>#      | 1<br>#       | 1<br># | 0<br>#             | 0<br># | 1<br>#      | 0<br>#      | Set DST                  | [6:0]                                                | 0         |

| 29 | Set Partial Display End                                                                         | 0<br>0 | 0<br>0 | 1<br>-                            | 1<br>#      | 1<br>#       | 1<br># | 0<br>#             | 0<br># | 1<br>#      | 1<br>#      | Set DEN                  | I[6:0]                                               | 159       |

| 30 | Set Window Program<br>Starting Column Address                                                   | 0      | 0      | 1<br>-                            | 1<br>#      | 1<br>#       | 1<br># | 0<br>#             | 1<br># | 0<br>#      | 0<br>#      |                          | Set<br>WPC0                                          | 0         |

| 31 | Set Window Program<br>Starting Row Address                                                      | 0      | 0      | 1<br>#                            | 1<br>#      | 1<br>#       | 1<br># | 0<br>#             | 1<br># | 0<br>#      | 1<br>#      | Shared                   | Set<br>WPP0                                          | 0         |

| 32 | Set Window Program<br>Ending Column Address                                                     | 0      | 0      | 1                                 | #<br>1<br># | 1<br>#       | 1<br># | 0<br>#             | 1<br># | #<br>1<br># | #<br>0<br># | with MTP commands        | Set<br>WPC1                                          | 127       |

| 33 | Set Window Program                                                                              | 0      | 0      | - 1                               | 1           | 1            | 1      | 0                  | 1      | 1           | 1           |                          | Set                                                  | 159       |

|    | Ending Row Address                                                                              | 0      | 0      | #                                 | #           | #            | #      | #                  | #      | #           | #           | 0.140                    | WPP1                                                 |           |

| 34 | Window Program Mode                                                                             | 0      | 0      | 1<br>1                            | 1           | 1            | 1      | 1                  | 0      | 0           | #<br>0      | Set AC                   | • •                                                  | 0: Inside |

| 35 | Set MTP Operation control                                                                       | 0      | 0      | -                                 | -           | -            | #      | #                  | 0<br># | 0<br>#      | 0<br>#      | Set MTP                  | C[4:0]                                               | 10H       |

|    | Command                             | C/D         | W/R         | D7          | D6          | D5          | D4          | D3          | D2          | D1          | D0          | Actio                 | n           | Default |

|----|-------------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-----------------------|-------------|---------|

| 36 | Set MTP Write Mask                  | 0<br>0<br>0 | 0<br>0<br>0 | 1<br>-<br>- | 0<br>#<br>- | 1<br>#<br>- | 1<br>#<br>- | 1<br>#<br>- | 0<br>#<br>- | 0<br>#<br># | 1<br>#<br># | Set MTPN<br>MTPM1     |             | 0       |

| 37 | Set V <sub>MTP1</sub> Potentiometer | 0<br>0      | 0<br>0      | 1<br>#      | 1<br>#      | 1<br>#      | 1<br>#      | 0<br>#      | 1<br>#      | 0<br>#      | 0<br>#      |                       | Set<br>MTP1 | N/A     |

| 38 | Set V <sub>MTP2</sub> Potentiometer | 0<br>0      | 0<br>0      | 1<br>#      | 1<br>#      | 1<br>#      | 1<br>#      | 0<br>#      | 1<br>#      | 0<br>#      | 1<br>#      | Shared with<br>Window | Set<br>MTP2 | N/A     |

| 39 | Set MTP Write Timer                 | 0<br>0      | 0<br>0      | 1<br>#      | 1<br>#      | 1<br>#      | 1<br>#      | 0<br>#      | 1<br>#      | 1<br>#      | 0<br>#      | Program commands      | Set<br>MTP3 | N/A     |

| 40 | Set MTP Read Timer                  | 0<br>0      | 0<br>0      | 1<br>#      | 1<br>#      | 1<br>#      | 1<br>#      | 0<br>#      | 1<br>#      | 1<br>#      | 1<br>#      |                       | Set<br>MTP4 | N/A     |

NOTE:

- All other bit patterns other than commands listed above may result in undefined behavior.

- The interpretation of commands (36)~(40) depends on the setting of register MTPC[3].

- Commands (37)~(40) are shared with commands (30)~(33). These two sets of commands share exactly the same code and control registers. When MTPC[3]=0, they are interpreted as Window Program commands and registers. When MTPC[3]=1, they function as MTP Control commands and registers.

- After MTP ERASE or PROGRAM operation, before resuming normal operation, please always

a) Remove TST4 power source,

a)

- b) Do a full V<sub>DD</sub> ON-OFF-ON cycle.

- Under 16-bit bus mode and CD=0, D[15:8] is ignored and only D[7:0] is used. As a result, the bus cycles

for commands under 16-bit bus and 8-bit bus are the same, and double-byte commands still need two

bus cycles under 16-bit bus mode.

Example:

8-bit bus mode:

| Set PL[1:0] = 2'b11 : | D[7:0] = 0010 1011                 |

|-----------------------|------------------------------------|

| Set PM[7:0] = 8'h8b : | $1^{\text{st}}$ D[7:0] = 1000 0001 |

|                       | 2 <sup>nd</sup> D[7:0] = 1000 1011 |

16-bit bus mode:

| Set PL[1:0] = 2'b11:                 | D[15:0] =              | 0000 0000 | 0010 1011 |

|--------------------------------------|------------------------|-----------|-----------|

| Set PM[7:0] = 8'h8b: 1 <sup>st</sup> | D[15:0] =              | 0000 0000 | 1000 0001 |

| 2 <sup>nc</sup>                      | <sup>i</sup> D[15:0] = | 0000 0000 | 1000 1011 |

## **Command Description**

#### (1) WRITE DATA TO DISPLAY MEMORY

| Action     | C/D | W/R | D7 | D6  | D5      | D4     | D3      | D2    | D1 | D0 |

|------------|-----|-----|----|-----|---------|--------|---------|-------|----|----|

| Write data | 1   | 0   |    | 8-b | oit dat | ta wri | tten to | o SRA | ١M |    |

UC1698u will convert input RAM data to 16-bit of RGB data. Please refer to command Set Color Mode for detail of data-write sequence.

#### (2) READ DATA FROM DISPLAY MEMORY

| Action    | C/D | W/R | D7 | D6  | D5      | D4    | D3     | D2    | D1 | D0 |

|-----------|-----|-----|----|-----|---------|-------|--------|-------|----|----|

| Read data | 1   | 1   |    | 8-b | oit dat | a rea | d fror | n SR/ | ١M |    |

Each RGB triplet is stored as 16-bit in the display RAM. Each 16-bit of RGB data takes 1 (/ 2) RAM read cycles for 16 (/ 8) -bit bus mode, respectively. The read out RGB data is after-extension for 64K color mode.

| R4 | R3 | R2 | R1                 | R0     | G5 | G4 | G3 | G2 | G1 | G0 | B4                  | <b>B</b> 3 | B2 | B1 | <b>B</b> 0 |

|----|----|----|--------------------|--------|----|----|----|----|----|----|---------------------|------------|----|----|------------|

|    |    | 1  | <sup>st</sup> 8-bi | t Read | b  |    |    |    |    | 2  | 2 <sup>nd</sup> 8-b | it Rea     | d  |    |            |

Write/Read Data Byte (commands (1) and (2)) operation uses internal Row Address register (RA) and Column Address register (CA). RA and CA can be programmed by issuing commands Set Row Address and Set Column Address. If wrap-around (WA, AC[0]) is OFF (0), CA will stop incrementing after reaching the CA boundary, and system programmers need to set the values of RA and CA explicitly. If WA is ON (1), when CA reaches end of column address, CA will be reset to 0 and RA will be increased or decreased, depending on the setting of Row Increment Direction (RID, AC[2]). When RA reaches the boundary of RAM (i.e. RA = 0 or 127), RA will be wrapped around to the other end of RAM and continue.

For 8-bit / 16-bit interface, the first 1 byte / 2 bytes of read, respectively, is a dummy read. Please ignore the data read out.

#### (3) GET STATUS & PM

| Action     | C/D | W/R | D7  | D6    | D5    | D4 | D3   | D2    | D1  | D0    |

|------------|-----|-----|-----|-------|-------|----|------|-------|-----|-------|

|            | 0   | 1   | GE  | MX    | MY    | WA | DE   | WS    | MD  | MS    |

| Get Status | 0   | 1   | Ver |       |       | PI | MO[6 | :0]   |     |       |

|            | 0   | 1   | Р   | roduc | t Coc | le | PID  | [1:0] | MID | [1:0] |

Status1 definitions:

- GE: Green Enhancing enable flag. Green Enhance Mode is disabled when GE = 1.

- MX: Status of register LC[1], mirror X.

- MY: Status of register LC[2], mirror Y.

- *WA* : Status of register AC[0]. Automatic column/row wrap around. DE: Display enable flag. DE=1 when display is enabled

- WS: MTP Operation succeeded

- MD: MTP Option (1 for MTP version, 0 for non-MTP version)

- MS: MTP action status

Status2 definitions:

Ver: IC Version Code. 0 or 1. PMO[6:0] : PM offset value.

Status3 definitions:

Product Code: 1000b (8h) PID[1:0] : Provide access to ID pins connection status. *MID*[1:0] : LCM manufacturer's configuration.

If multiple Get Status commands are issued consecutively within one single CD 1 $\Rightarrow$ 0 $\Rightarrow$ 1 transaction, the Get Status command will return {Status1, Status2, Status3, Status1, Status2, Status3, Status1.} alternately.

#### (4) SET COLUMN ADDRESS

| Action                         | C/D | W/R | D7 | D6 | D5 | D4 | D3  | D2  | D1  | D0  |

|--------------------------------|-----|-----|----|----|----|----|-----|-----|-----|-----|

| Set Column Address LSB CA[3:0] | 0   | 0   | 0  | 0  | 0  | 0  | CA3 | CA2 | CA1 | CA0 |

| Set Column Address MSB CA[7:4] | 0   | 0   | 0  | 0  | 0  | 1  | 0   | CA6 | CA5 | CA4 |

Set SRAM column address for read/write access. CA is counted in RGB triplets, not individual SEG electrode.

CA value range: 0~127

#### (5) SET TEMPERATURE COMPENSATION

| Action                        | C/D | W/R | D7 | D6 | D5 | D4 | D3 | D2 | D1  | D0  |

|-------------------------------|-----|-----|----|----|----|----|----|----|-----|-----|

| Set Temperature Comp. TC[1:0] | 0   | 0   | 0  | 0  | 1  | 0  | 0  | 1  | TC1 | TC0 |

Set V<sub>BIAS</sub> temperature compensation coefficient (%-per-degree-C)

Temperature compensation curve definition:  $00b = -0.00\%/^{\circ}C$   $01b = -0.05\%/^{\circ}C$

10b = -0.15%/°C 11b = -0.25%/°C

(6) SET POWER CONTROL

| Set Panel Loading PC[1:0] 0 0 0 0 0 1 0 1 0 PC1 | Action                    | C/D | W/R | D7 | D6 | D5 | D4 | D3 | D2 | D1  | <b>D0</b> |

|-------------------------------------------------|---------------------------|-----|-----|----|----|----|----|----|----|-----|-----------|

| 5 1 1                                           | Set Panel Loading PC[1:0] | 0   | 0   | 0  | 0  | 7  | 0  | 1  | 0  | PC1 | PC0       |

Set PC[0] according to the capacitance loading of LCD panel.

Panel loading definition: **0b** :  $LCD \le 13nF$  1b :  $13nF < LCD \le 22nF$

Set PC[1] to program the build-in charge pump stages. Before changing PC[1] value, always ensure the IC is in a RESET state. Avoid changing PC[1] when the display is enabled.

Pump control definition: 0b = External V<sub>LCD</sub> 1b = Internal V<sub>LCD</sub> (x10)

(7) SET ADVANCED PROGRAM CONTROL

| Action                | C/D | W/R | D7 | D6 | D5     | D4     | D3     | D2    | D1 | D0 |

|-----------------------|-----|-----|----|----|--------|--------|--------|-------|----|----|

| Set APC[R][7:0]       | 0   | 0   | 0  | 0  | 1      | 1      | 0      | 0     | 0  | R  |

| (Double-byte command) | 0   | 0   |    | Α  | NPC re | egiste | r para | amete | er |    |

0

For UltraChip only. Please do NOT use.

#### (11) SET PARTIAL DISPLAY CONTROL

| Action                           | C/D | W/R | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

|----------------------------------|-----|-----|----|----|----|----|----|----|----|-----|

| Set Partial Display Enable LC[8] | 0   | 0   | 1  | 0  | 0  | 0  | 0  | 1  | 0  | LC8 |

This command is used to enable partial display function.

LC[8] : **0**b: Disable Partial Display, Mux-Rate = CEN+1 (DST, DEN not used.) 1b: Enable Partial Display, Mux-Rate = DEN-DST+1+ LC[0]x(FLT+FLB)x2

#### (12) SET RAM ADDRESS CONTROL

| Action       | C/D | W/R | D7 | D6 | D5 | D4 | D3 | D2  | D1  | D0  |

|--------------|-----|-----|----|----|----|----|----|-----|-----|-----|

| Set AC [2:0] | 0   | 0   | 1  | 0  | 0  | 0  | 1  | AC2 | AC1 | AC0 |

Program registers AC[2:0] for RAM address control.

AC[0]: WA, Automatic column/row wrap around.

0: CA or RA (depends on AC[1]= 0 or 1) will stop incrementing after reaching boundary

1: CA or RA (depends on AC[1]= 0 or 1) will restart, and RA or CA will increment by one step.

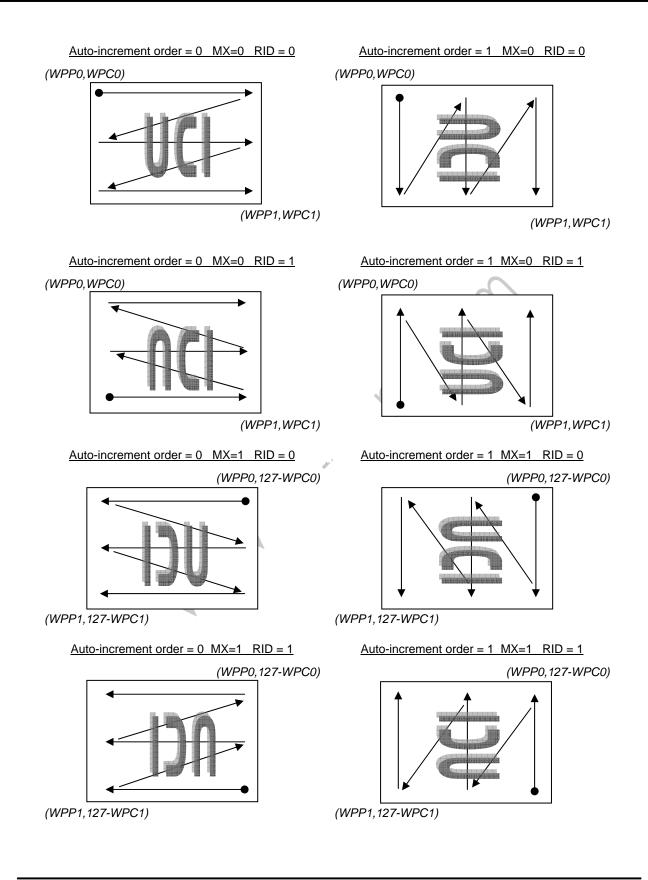

AC[1]: Auto-Increment order

- 0 : column (CA) increment (+1) first until CA reaches CA boundary, then RA will increment by (+/-1).

- 1 : row (RA) increment (+/-1) first until RA reach RA boundary, then CA will increment by (+1).

AC[2]: RID, row address (RA) auto increment direction (**0**/1 = +/- 1) When WA=1 and CA reaches CA boundary, RID controls whether row address will be adjusted by +1 or -1.

AC[2:0] controls the auto-increment behavior of CA and RA. For Window Program mode (AC[3]=ON), see section *Command Description* (32) ~ (35) for more details. If WPC[1:0] and WPP[1:0] values are the default values, the behavior of CA, RA auto-increment will be the same, no matter what the setting of AC[3] is.

#### (13) SET FIXED LINES

| Action                    | C/D | W/R | D7 | D6  | D5    | D4 | D3 | D2  | D1    | D0 |

|---------------------------|-----|-----|----|-----|-------|----|----|-----|-------|----|

| Set Fixed Lines {FLT,FLB} | 0   | 0   | 1  | 0   | 0     | 1  | 0  | 0   | 0     | 0  |

| (Double-byte command)     | 0   | 0   |    | FLT | [3:0] |    |    | FLB | [3:0] |    |

The fixed line function is used to implement the partial scroll function by dividing the screen into scroll and fixed area. The Set Fixed Lines command will define the fixed area, which will not be affected by the SL scroll function. The fixed area covers the top 2xFLT and bottom 2xFLB rows for mirror Y (MY) is 0, or covers the top 2xFLB and bottom 2xFLT rows for MY=1. One example of the visual effect on LCD is illustrated in the figure below.

| Fixed Area       | 1        |   | Fixed Area  | 1   |

|------------------|----------|---|-------------|-----|

| (2xFLT)          |          |   | (2xFLB)     |     |

| Scroll Area      |          |   | Scroll Area |     |

|                  |          |   |             |     |

|                  |          |   |             |     |

| Fixed Area       | <b>↓</b> |   | Fixed Area  | ↓   |

| (2xFLB) <b>1</b> | 60       |   | (2xFLT)     | 160 |

| MY = 0           |          | 1 | MY = 1      |     |

| 1011 - 0         |          |   | 1011 - 1    |     |

When partial display mode is activated, the display of these 2x(FLT+FLB) lines is also controlled by LC[0]. Before turning on LC[0], ensure:

| MY=0 | DST ≥ FLTx2             |

|------|-------------------------|

|      | $DEN \leq (CEN-FLBx2).$ |

$\begin{array}{ll} MY=1 & DST \geq FLBx2 \\ DEN \leq (CEN-FLTx2) \end{array}$

#### (14) SET LINE RATE

| Action                 | C/D | W/R | D7 | D6 | D5 | D4 | D3 | D2 | D1  | D0  |

|------------------------|-----|-----|----|----|----|----|----|----|-----|-----|

| Set Line Rate LC [4:3] | 0   | 0   | 1  | 0  | 1  | 0  | 0  | 0  | LC4 | LC3 |

Program LC [4:3] for line rate setting (Frame-Rate = Line-Rate / Mux-Rate). The line rate is automatically scaled down by 2/3, 1/2, 1/3 and 1/4 at Mux-Rate = 108, 80, 56, and 40.

| The following are line rates at | Mux Rate = 109 ~ 160. |                |                |

|---------------------------------|-----------------------|----------------|----------------|

| 00b: 25.2 Klps                  | 01b: 30.5 Klps        | 10b: 37.0 Klps | 11b: 44.8 Klps |

| In On/Off Mode                  |                       |                |                |

| 00b: 8.5 Klps                   | 01b: 10.4 Klps        | 10b: 12.6 Klps | 11b: 15.2 Klps |

| (Klps: Kilo-L                   | ine-per-second)       |                |                |

#### (15) SET ALL PIXEL ON

|                                   |   |   | - |   |   | <b>D0</b> |

|-----------------------------------|---|---|---|---|---|-----------|

| Set All Pixel ON DC [1] 0 0 1 0 1 | 0 | 0 | 0 | 1 | 0 | DC1       |

Set DC[1] to force all SEG drivers to output ON signals. This function has no effect on the existing data stored in display RAM.

#### (16) SET INVERSE DISPLAY

| Action                     | C/D | W/R | D7 | D6 | D5 | D4 | D3 | D2 | D1 | <b>D0</b> |

|----------------------------|-----|-----|----|----|----|----|----|----|----|-----------|

| Set Inverse Display DC [0] | 0   | 0   | 1  | 0  | 1  | 0  | 0  | 1  | 1  | DC0       |

Set DC[0] to force all SEG drivers to output the inverse of the data (bit-wise) stored in display RAM. This function has no effect on the existing data stored in display RAM.

#### (13) SET FIXED LINES

| Action                    | C/D | W/R | D7 | D6  | D5    | D4 | D3 | D2  | D1    | D0 |

|---------------------------|-----|-----|----|-----|-------|----|----|-----|-------|----|

| Set Fixed Lines {FLT,FLB} | 0   | 0   | 1  | 0   | 0     | 1  | 0  | 0   | 0     | 0  |

| (Double-byte command)     | 0   | 0   |    | FLT | [3:0] |    |    | FLB | [3:0] |    |

The fixed line function is used to implement the partial scroll function by dividing the screen into scroll and fixed area. The Set Fixed Lines command will define the fixed area, which will not be affected by the SL scroll function. The fixed area covers the top 2xFLT and bottom 2xFLB rows for mirror Y (MY) is 0, or covers the top 2xFLB and bottom 2xFLT rows for MY=1. One example of the visual effect on LCD is illustrated in the figure below.

| Fixed Area 1       |   | Fixed Area  | 1   |

|--------------------|---|-------------|-----|

| (2xFLT)            |   | (2xFLB)     |     |

| Scroll Area        |   | Scroll Area |     |

|                    |   |             |     |

|                    |   |             |     |

| Fixed Area 🛛 🕁     |   | Fixed Area  | ★   |

| (2xFLB) <b>160</b> |   | (2xFLT)     | 160 |

| MY = 0             | _ | MY = 1      |     |

| W = 0              |   | 111 - 1     |     |

When partial display mode is activated, the display of these 2x(FLT+FLB) lines is also controlled by LC[0]. Before turning on LC[0], ensure:

| MY=0 | DST ≥ FLTx2             |

|------|-------------------------|

|      | $DEN \leq (CEN-FLBx2).$ |

$\begin{array}{ll} MY=1 & DST \geq FLBx2 \\ DEN \leq (CEN-FLTx2) \end{array}$

#### (14) SET LINE RATE

| Action                 | C/D | W/R | D7 | D6 | D5 | D4 | D3 | D2 | D1  | D0  |

|------------------------|-----|-----|----|----|----|----|----|----|-----|-----|

| Set Line Rate LC [4:3] | 0   | 0   | 1  | 0  | 1  | 0  | 0  | 0  | LC4 | LC3 |

Program LC [4:3] for line rate setting (Frame-Rate = Line-Rate / Mux-Rate). The line rate is automatically scaled down by 2/3, 1/2, 1/3 and 1/4 at Mux-Rate = 108, 80, 56, and 40.

| The following are line rates at I | Mux Rate = 109 ~ 160. |                |                |

|-----------------------------------|-----------------------|----------------|----------------|

| 00b: 25.2 Klps                    | 01b: 30.5 Klps        | 10b: 37.0 Klps | 11b: 44.8 Klps |

| In On/Off Mode                    |                       |                |                |

| 00b: 8.5 Klps                     | 01b: 10.4 Klps        | 10b: 12.6 Klps | 11b: 15.2 Klps |

| (Klps: Kilo-Li                    | ine-per-second)       |                |                |

#### (15) SET ALL PIXEL ON

| Action C/D                | ••/1 | וט | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

|---------------------------|------|----|----|----|----|----|----|----|-----|

| Set All Pixel ON DC [1] 0 | 0    | 1  | 0  | 1  | 0  | 0  | 1  | 0  | DC1 |

Set DC[1] to force all SEG drivers to output ON signals. This function has no effect on the existing data stored in display RAM.

#### (16) SET INVERSE DISPLAY

| Action                     | C/D | W/R | D7 | D6 | D5 | D4 | D3 | D2 | D1 | <b>D0</b> |

|----------------------------|-----|-----|----|----|----|----|----|----|----|-----------|

| Set Inverse Display DC [0] | 0   | 0   | 1  | 0  | 1  | 0  | 0  | 1  | 1  | DC0       |

Set DC[0] to force all SEG drivers to output the inverse of the data (bit-wise) stored in display RAM. This function has no effect on the existing data stored in display RAM.

#### (18) SET LCD MAPPING CONTROL

| Action                           | C/D | W/R | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

|----------------------------------|-----|-----|----|----|----|----|----|----|----|-----|

| Set LCD Mapping Control LC [2:0] | 0   | 0   | 1  | 1  | 0  | 0  | 0  | MY | MX | LC0 |

This command is used for programming LC[2:0] to control COM (row) mirror (MY), SEG (column) mirror (MX).

LC[2] controls Mirror Y (MY): MY is implemented by reversing the mapping order between RAM and COM electrodes. The data stored in RAM is not affected by the MY action. MY will have immediate effect on the display image.

LC[1] controls Mirror X (MX): MX is implemented by selecting the CA or 127-CA as write/read (from host interface) display RAM column address so this function will only take effect after rewriting the RAM data.

LC[0] controls whether soft icon sections (2xFLT, 2xFLB) are displayed during partial display mode.

#### (19) SET N-LINE INVERSION

|            | Action         | n         |       | C/D     | W/R    | D7    | D6    | D5     | D4        | D3   | D2   | D1   | D0      |

|------------|----------------|-----------|-------|---------|--------|-------|-------|--------|-----------|------|------|------|---------|

| Set        | N-line inversi | ion NIV[3 | 3:0]  | 0       | 0      | 1     | 1     | 0      | 0         | 1    | 0    | 0    | 0       |

| (E         | Double-byte c  | ommand    | )     | 0       | 0      | -     | -     | -      | NIV4      | NIV3 | NIV2 | NIV1 | NIV0    |

| N-Line Inv | version:       |           |       |         |        |       | _     |        | _         |      |      |      | -       |

| NIV[2:0]:  | 000b: 11 line  | es        | 001b  | : 19 li | nes    |       | 01    | 10b: 2 | 1 line    | s 🌑  |      | 011  | b: 25 l |

|            | 100b: 29 line  | es        | 101b  | : 31 I  | ines   |       | 11    | 10b: 3 | 87 line   | s    |      | 111  | b: 43 l |

| NIV[3]:    | 0b: non-XOF    | २         | 1b: X | OR      |        |       |       |        |           |      |      |      |         |

| NIV[4]:    | 0b: Disable I  | NIV       | 1b: E | nabl    | e NIV  |       |       |        |           |      |      |      |         |

|            | NIV[3]=0       |           | 31    |         | ؛<br>ا | 5  26 | 3<br> |        | <u>31</u> |      |      |      |         |

| 51 |         |  |

|----|---------|--|

|    | Frame 2 |  |

#### (20) SET COLOR PATTERN

NIV[3]=1

| Action                   | C/D | W/R | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

|--------------------------|-----|-----|----|----|----|----|----|----|----|-----|

| Set Color Pattern LC [5] | 0   | 0   | 1  | 1  | 0  | 1  | 0  | 0  | 0  | LC5 |

UC1698u supports on-chip swapping of R⇔B data mapping to the SEG drivers.

Frame 1

31

| LC[5] | SEG1 | SEG2 | SEG3 | SEG4 | SEG5 | SEG6 | <br>SEG382 | SEG383 | SEG384 |

|-------|------|------|------|------|------|------|------------|--------|--------|

| 0     | В    | G    | R    | В    | G    | R    | <br>В      | G      | R      |

| 1     | R    | G    | В    | R    | G    | В    | <br>R      | G      | В      |

26

The definition of R/G/B input data is determined by LC[7:6], as described in Set Color Mode below.

#### (21) SET COLOR MODE

| Action                  | C/D | W/R | D7 | D6 | D5 | D4 | D3 | D2 | D1  | D0  |

|-------------------------|-----|-----|----|----|----|----|----|----|-----|-----|

| Set Color Mode LC [7:6] | 0   | 0   | 1  | 1  | 0  | 1  | 0  | 1  | LC7 | LC6 |

Program color mode and RGB input pattern. Color mode (LC[7:6]) definition:

*Note:* For serial bus modes, please refer to 8-bit tables below.

#### Green Enhance Mode disabled (DC[4]=1):

LC[7:6] = 01b (RRR-GGGG-BBBB, 4K-color)

12 bits of input RGB data are stored to 16 RAM bits. No dither is performed. Every 3 bytes of input data will be merged into 2 sets of RGB data.

| Data Write Sequence (8-bit)      | <b>D[</b> ] | 7:0]       |    |            |            |            |           |            |

|----------------------------------|-------------|------------|----|------------|------------|------------|-----------|------------|

| 1 <sup>st</sup> Write Data Cycle | R3          | R2         | R1 | R0         | G3         | G2         | G1        | G0         |

| 2 <sup>nd</sup> Write Data Cycle | <b>B</b> 3  | <b>B</b> 2 | B1 | <b>B</b> 0 | R3         | R2         | R1        | <b>R</b> 0 |

| 3 <sup>rd</sup> Write Data Cycle | G3          | G2         | G1 | G0         | <b>B</b> 3 | <b>B</b> 2 | <b>B1</b> | <b>B</b> 0 |

| Data Write Sequence (16-bit)     | <b>D[</b> | 15:0 | 1 |   |    |    |    |    |    |    |    |    |            |            |           |            |

|----------------------------------|-----------|------|---|---|----|----|----|----|----|----|----|----|------------|------------|-----------|------------|

| 1 <sup>st</sup> Write Data Cycle | 0         | 0    | 0 | 0 | R3 | R2 | R1 | R0 | G3 | G2 | G1 | G0 | <b>B</b> 3 | <b>B</b> 2 | <b>B1</b> | <b>B</b> 0 |

| 2 <sup>nd</sup> Write Data Cycle | 0         | 0    | 0 | 0 | R3 | R2 | R1 | R0 | G3 | G2 | G1 | G0 | <b>B</b> 3 | <b>B</b> 2 | <b>B1</b> | <b>B</b> 0 |