# Motorcommo Motorcommitor Motorcommito Notorcomm for Midea Motorcom YT8512C YT8512H Datasheet FAST ETHERNET TRANSCEIVER

V1.15 DATE 2022/05/11

|       | -11 to           |              |                                                  |          |

|-------|------------------|--------------|--------------------------------------------------|----------|

|       |                  |              |                                                  |          |

| *     | Motorcomm YT     | 8512C YT8512 | 2H Datasheet 裕太微电子<br>Motor Comm                 | <u>-</u> |

| Motor | Revision History | NOTE         |                                                  |          |

| 6.    | Revision         | Release Date | Summary                                          |          |

|       | 1.0              | 2019/07/11   | Add POS, WOL description                         | •        |

|       |                  |              | Update Register table                            |          |

|       | 1.01             | 2019/09/04   | Update Electrical Characteristics                |          |

|       | 1.02             | 2019/09/11   | Modify RBIAS resistor to 2.49k ohm               |          |

|       | 1.03             | 2019/10/16   | Modify errors                                    |          |

|       | 1.04             | 2019/11/05   | Update Register                                  |          |

|       | 1.05             | 2019/11/12   | Update Block diagram                             | -        |

|       | 1.06             | 2020/01/13   | Add EPAD description                             |          |

|       | 1.07             | 2020/03/16   | Modify package information, ordering information |          |

|       |                  | LOD          | Add thermal resistance                           | Midea    |

|       | 1.08             | 2020/03/23   | Add Copyright Statement and Disclaimer           | NIN MARK |

|       | FOR              |              | Add Reg ext 0x200a                               |          |

|       |                  |              |                                                  |          |

| 5     | 1.09             | 2020/03/26   | Add Packaging Type<br>Release                    |          |

| Motor |                  | NOTE         | Release                                          |          |

| 12    | 1.10             | 2020/04/22   | Modify Thermal resistance description            |          |

|       |                  |              | Pin 30,31,32 pin Description                     |          |

|       | 1.11             | 2020/04/24   | Update Register                                  |          |

|       |                  |              | Modify RMII description                          |          |

|       | 1.12             | 2020/10/16   | Modify company name and logo                     |          |

|       | 1.13             | 2020/12/17   | Modify power sequence description.               |          |

|       | 1.14             | 2021/10/17   | Modify RMII timing                               |          |

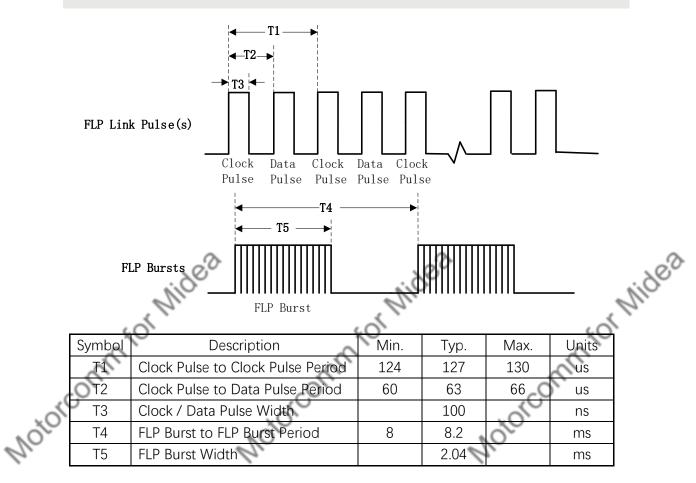

|       | 1.15             | 2022/05/11   | Add FLPs timing                                  |          |

comm for Midea crom for Midea ann for Midea

本文档版权归苏州裕太微电子有限公司(以下简称"裕太微电子")所有,并保留一切权利。未经裕太微电 子书面许可,任何公司和个人不得将此文档中的任何部分复制、传播、披露或以其他方式散发给第三方。 否则裕太微电子将保留追究其法律责任的权利。

This document is copyright of Suzhou Motorcomm Electronic Technology Co., Ltd. ("Motorcomm"). All rights reserved. No company or individual may copy, disseminate, disclose or otherwise distribute any part of this document to any third party without the written consent of Motorcomm. If any company or individual so does, Motorcomm reserves the right to hold it or him liable therefor.

# 免责声明 Disclaimer

crown for Midea

本文档仅提供阶段性信息,所含内容将/可根据产品的实际情况随时更新,恕不另行通知。如因文档使用不 当造成直接或间接损失,裕太微电子不承担任何责任。

MotorcommforMidea This document only provides periodic information, and its contents will/may be updated from time to time according to actual situation of Motorcomm's products without further notice. Motorcomm will not take any responsibility for Motorcomment .dir. any direct or indirect losses caused due to improper use of this document.

crown for Midea

comm for Midea

裕太微电子 MotorComm

|      | 1.             | General Description                     | 8    |      |

|------|----------------|-----------------------------------------|------|------|

|      |                | Target Application                      | 8    |      |

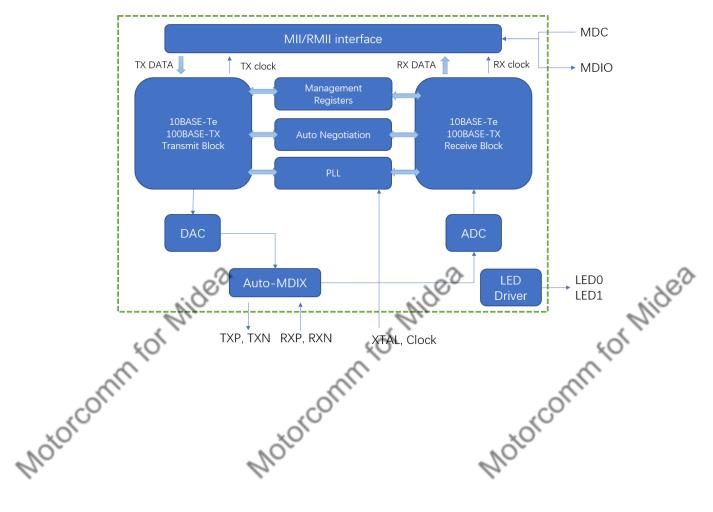

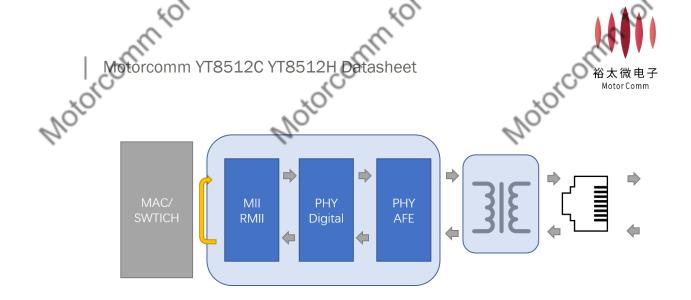

|      |                | Block Diagram                           | 9    |      |

|      | 2.             | Feature                                 | 10   |      |

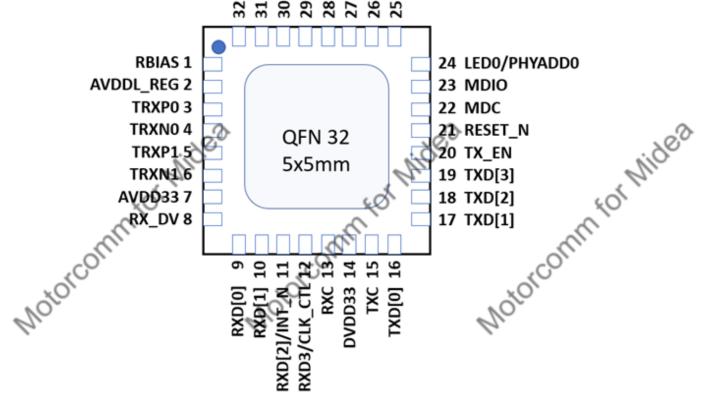

|      | 3.             | Pin Assigment                           | 11   |      |

|      |                | YT8512C YT8512H QFN32 5x5mm             | 11   |      |

|      |                | Pin Descriptions                        | 12   |      |

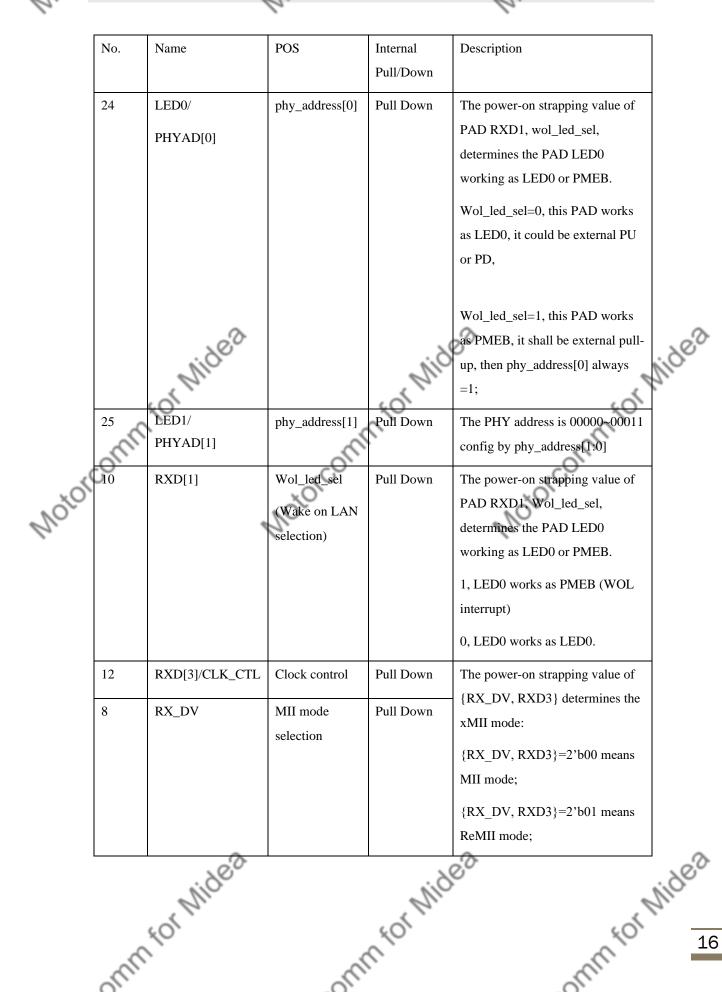

|      |                | Power on strapping                      | 16   |      |

|      |                | Mode config                             | 17   | ð    |

|      |                | PHY address                             | 17   | 50   |

|      |                | PHY address                             |      |      |

|      | 3              | Function Description                    | 19   |      |

|      | <sub>c</sub> o | Application Diagram                     | 19   |      |

| NOTO | 0              | 100Base-Tx/10Base-Te application        | 19   |      |

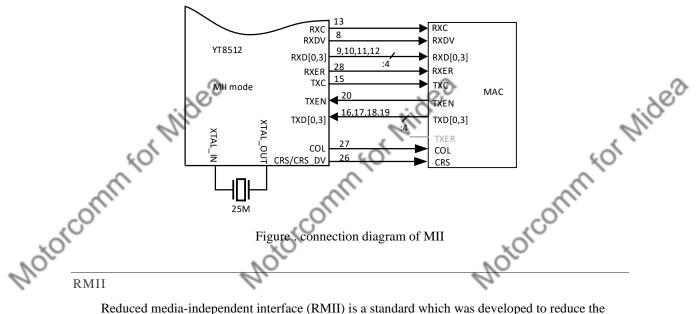

| No   |                | MII interface                           | 19   |      |

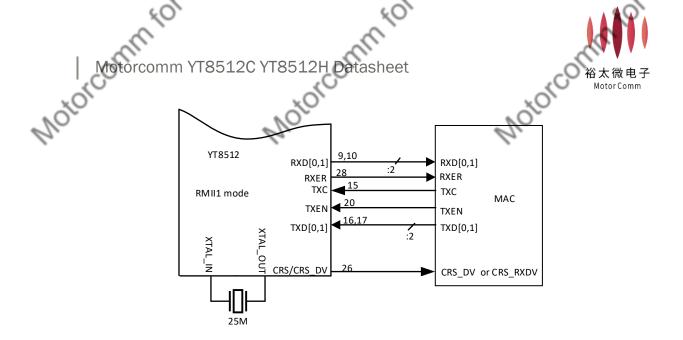

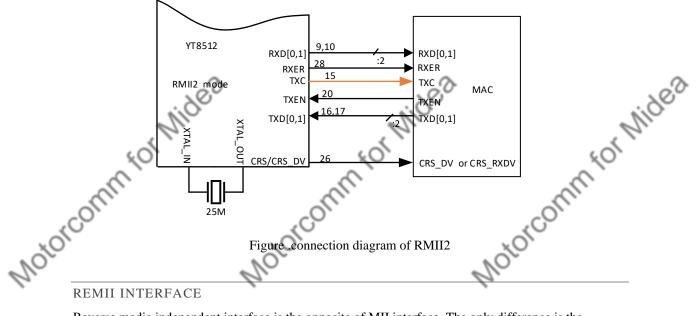

|      |                | RMII interface                          | 20   |      |

|      |                | Management interface                    | 20   |      |

|      |                | DAC                                     | 20   |      |

|      |                | ADC                                     | 20   |      |

|      |                | Adaptive equalizer                      | 21   |      |

|      |                | Auto- negotiation                       | 21   |      |

|      |                | Polarity detection and auto correction  | 21   |      |

|      |                | EEE                                     | 21   |      |

|      | 4              | Operational Description                 | 22   |      |

|      |                | Reset                                   | 22   | 2    |

|      |                | PHY Address                             | 22   | \$°° |

|      |                | all | 1 CM |      |

|      |                | Reset                                   | 22   | 3    |

|      | Ċ              |                                         |      |      |

|          | 40° 40°                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <u>``</u>         |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

| Mo       | torcomm YT8512C YT8512H Datasheet 裕太行                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ▼<br>微电子<br>rComm |

| NOTON -  | torcomm YT8512C YT8512H Datasheet<br>XMII interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23                |

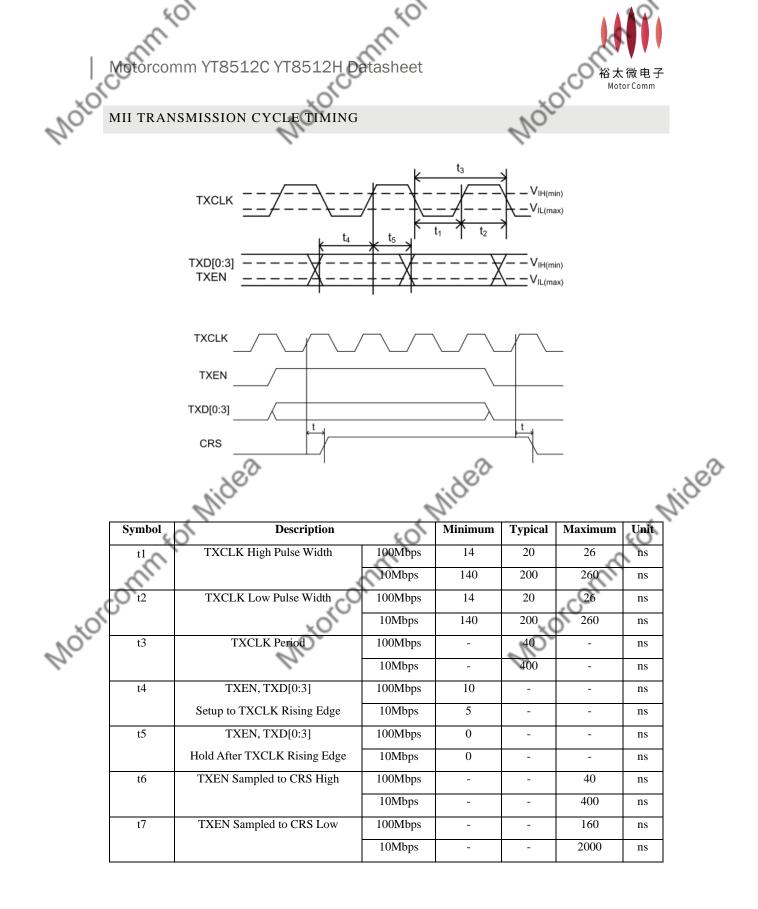

| C/2      | MII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23                |

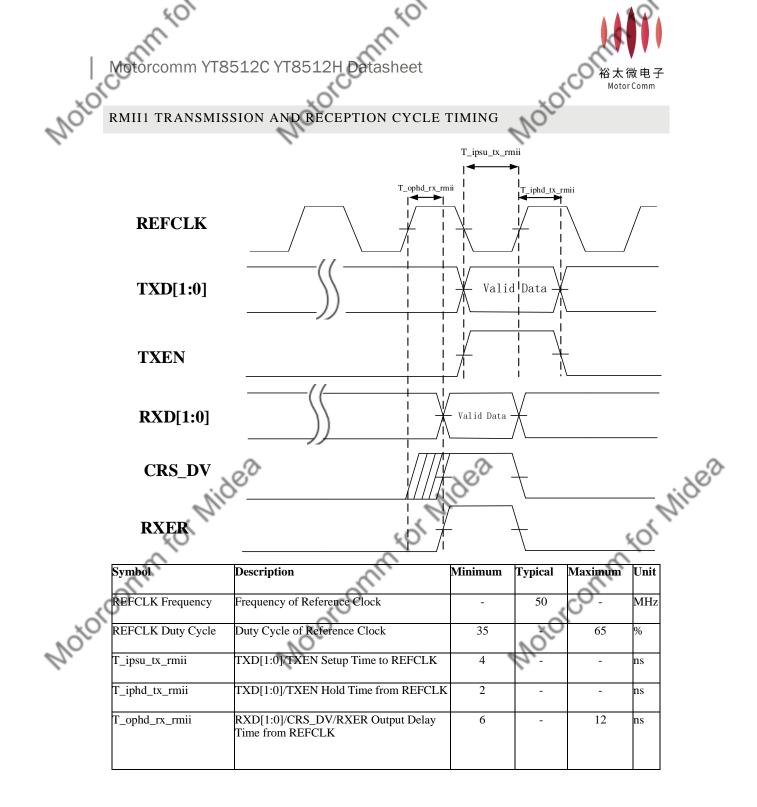

|          | RMII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23                |

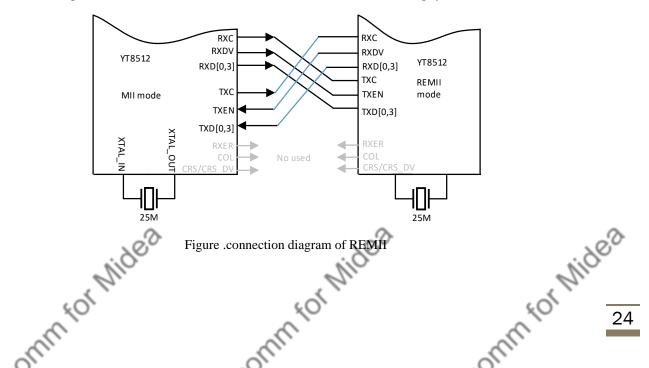

|          | REMII interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24                |

|          | Loopback mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25                |

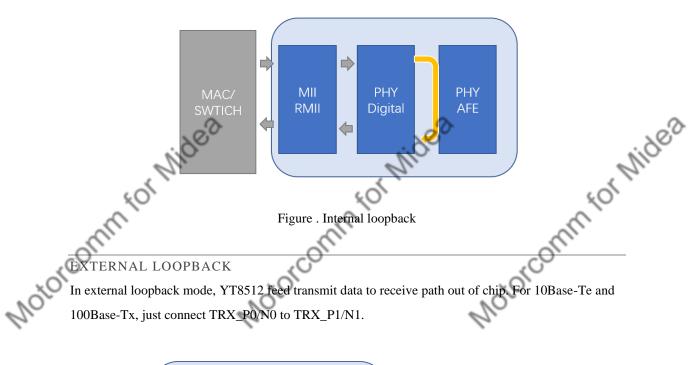

|          | Internal loopback:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25                |

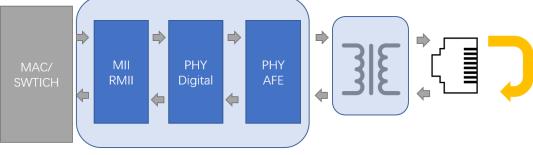

|          | External loopback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25                |

|          | Remote loopback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25                |

|          | WoL Wake on lan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27                |

|          | WOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 27                |

|          | WOL mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27                |

|          | WOL Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28                |

| 5        | Register Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29 Nice           |

|          | MII Management Interface Clause 22 Register Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |

|          | MII Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30                |

| Motorcor | Mii register 00h: Basic control register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30                |

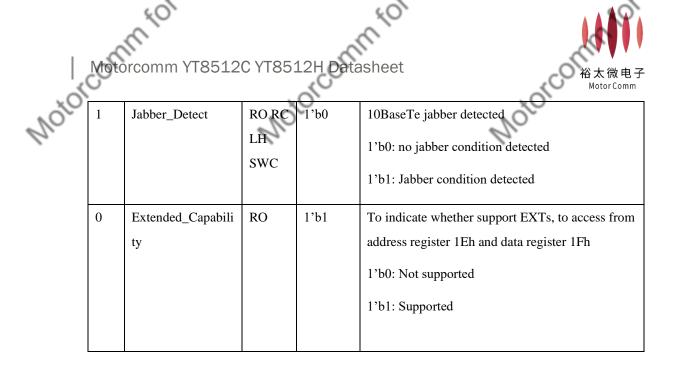

| ALON C   | Mii register 01h: Basic status register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 31                |

| N        | Mii register 01h: Basic status register<br>Mii register 02h: PHY identification register1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33                |

|          | Mii register 03h: PHY identification register2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33                |

|          | MII register 04h: Auto-Negotiation advertisement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33                |

|          | MII register 05h: Auto-Negotiation link partner ability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36                |

|          | MII register 06h: Auto-Negotiation expansion register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38                |

|          | MII register 07h: Auto-Negotiation Next Page register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39                |

|          | MII register 08h: Auto-Negotiation link partner Received Next Page register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 39                |

|          | MII register 0Ah: MASTER-SLAVE status register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 40                |

|          | MII register 0Dh: MMD access control register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41                |

|          | MII register 0Eh: MMD access data register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 42                |

|          | Mii register 0Fh: Extended status register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 42                |

|          | MII register 10h: PHY specific function control register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42                |

|          | it is it is a second se | 1 <u> </u>        |

|          | Mii register 0Fh: Extended status register<br>MII register 10h: PHY specific function control register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4                 |