**ZAD2836**

16-Bit High-Speed Sampling

A/D Converter

### Applications

- ☐ Medical Imaging Data Acquisition

- ☐ High-Speed Automatic Test

- ☐ Wide Dynamic Range Scientific Instrumentation

- ☐ Professional Audio

- □ Multiplexed Data Acquisition

### **Key Features**

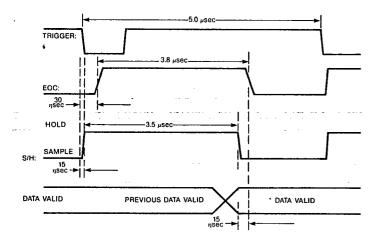

- $\square$  3.5  $\mu$ s A/D Conversion Time

- ☐ 200 kHz Total Throughput

- ☐ Superior Linearity Throughout Signal Range

- ☐ Built-In Ultra-Linear Sample/Hold

- ☐ Sample/Hold Dielectric Absorption < 0.001%

- $\square$  Aperture Uncertainty < 50 ps.

- ☐ Dynamic Gain and Offset Correction Capabilities

- ☐ Tri-State Output Latches

## Solutions for Data Conversion

Offering a five microsecond total throughput time and improved linearity and drift, the ZAD2836 sets the performance standard for 16-bit sampling A/D converters. Utilizing the latest IC technology and advanced Analog Solutions' proprietary circuit designs, the ZAD2836 provides significantly enhanced performance at a cost less than many older, slower designs.

The ZAD2836 is the solution to your high-speed 16-bit conversion needs.

#### General Description

The ZAD2836 is a high-performance, five microsecond, 16-bit sampling ADC which includes an ultralinear Sample/Hold and high-speed A/D converter in one compact, fully tested module. The ZAD2836 has been optimized for performance in critical CT and MRI systems, where the dynamic range, accuracy around zero and repeatability are all critical.

Utilizing an advanced Digitally Corrected Sub-Ranging (DCSR) A/D converter approach and a novel Sample/Hold circuit, the ZAD2836 assures 16-bit total performance.

The ZAD2836's excellent long-term drift and temperature stability are accomplished by using specially selected and tested resistor networks in a proprietary DCSR circuit design that reduces the converter's sensitivity to individual component drift.

#### Description of Converter

The ZAD2836 utilizes a unique three-pass Digitally Corrected Sub-Ranging (DCSR) technique in conjunction with our proven "monobit" D/A converter architecture to provide premium converter performance.

The unit consists of an ultra-linear Sample/Hold, a 6-bit flash to ensure long-term accuracy, and our monobit DAC for reduced sensitivity to resistor drift.

The combination of the three-pass DCSR technique and monobit design DAC provides up to four times more allowance for component variation and drift than older two-pass sub-ranging converters.

This conservative design approach assures that the unit stays within specification over its full temperature range and that long-term drift is minimized.

#### ■ 8253887 0000579 2 ■

### PERFORMANCE SPECIFICATIONS ZAD2836 LOW-DISTORTION 16-BIT SAMPLING A/D CONVERTER

|                                                                                                                  | UNIPOLAR                                                                                                                                                                                                                                                                                        | BIPOLAR                      |                                                                        | UNIPOLAR E                                                                                                                                        | BIPOLAR          |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| ANALOG INPUT Voltage Range Input Impedance Input Bias Current Initial Offset Voltage Stability of Offset Voltage | 0 to +10 V 100 MΩ//5 pF typical ±2 nA max (+10°C to +60°C) ±5mV max³ ±100 μV/72 hrs typical                                                                                                                                                                                                     | ±5 V                         | HOLD MODE Droop Rate  Dielectric Absorption  S/H Feedthrough           | 5 μV/μs max (typically doubles every 10°C) ±0.001% of input signal voltage change, typical —96 dB typical, —90 dB max                             | •                |

| ACCURACY Resolution Quantization Error Relative Accuracy¹ FSR Factory-Calibrated to Absolute Accuracy            | 16 bits<br>±0.5 LSB<br>±0.003% FSR, max<br>0 ±0.01% <sup>3</sup><br>±0.003% FSR max <sup>2</sup>                                                                                                                                                                                                | * * * *                      | SAMPLE MODE Siew Rate Bandwidth Acquisition Time  DIGITAL INPUTS/OUTPU | 20 V/µs min<br>5 MHz typical, 2 MHz min<br>1.5 µs typical                                                                                         | *                |

| Differential Non-Linearity  Reference Output                                                                     | ±0.5 LSB typical,<br>±0.75 LSB max<br>+10.000 V ±20 mV,<br>load = 2 mA max                                                                                                                                                                                                                      | 4                            | Logic Levels Data Outputs Trigger Input                                | LSTTL/CMOS compatible 16 bits data; Tri-state latch 10 LS loads Negative edge;                                                                    | *<br>1 *<br>*    |

| Nolse Unipolar Bipolar Missing Codes  Harmonic Distortion                                                        | 40 μV RMS max<br>50 μV RMS max<br>No missing codes<br>10° to 50°C                                                                                                                                                                                                                               | +<br>+<br>-90 dB,<br>typical | Trigger Load Tri-State Control End of Conversion                       | 1 μs pulse width min.,<br>3 μs max. (see timing diagra<br>1 LSTTL loads<br>Logic 1 on HI BYTE EN or<br>LO BYTE EN generates<br>HI impedance state | *                |

| (±5 V input, 10 kHz)                                                                                             | ng di Salaman di Kabupat di Salaman di Salaman di Salaman<br>Bagtary Halaman di Salaman di Salaman di Salaman<br>Bagtary di Salaman di Salaman di Salaman di Salaman di Salaman<br>Bagtaryan di Salaman | ,                            | (EOC)                                                                  | Data valid on EOC high to low transition                                                                                                          | *                |

| STABILITY  Differential Non-Linearity Temperature Coefficient                                                    | ±0.5 ppm/⁰C max                                                                                                                                                                                                                                                                                 |                              | POWER REQUIREMENT<br>+15 V ±0.25 V<br>-15 V ±0.25 V<br>+ 5 V ±0.25 V   | 65 mA typical<br>85 mA typical<br>100 mA typical                                                                                                  | *                |

| Offset Temperature Coefficient                                                                                   | ±20 μV/°C typical,<br>±40 μV/°C max<br>100 μV/1%                                                                                                                                                                                                                                                |                              | ENVIRONMENTAL & MECHANICAL Operating Temperature                       |                                                                                                                                                   |                  |

| Offset Versus Supply Gain Temperature Coefficient Warm-up Time                                                   | thange in supply, max  ±2 ppm/°C typical  ±5 ppm/°C max  15 minutes to specified accuracy                                                                                                                                                                                                       | *                            | Range Storage Temperature Range Relative Humidity Shielding            | +10°C to +60°C  -10°C to +75°C  0 to 85%, non-condensing up to 40°C  RFI 6 sides, EMI 5 sides                                                     | *<br>*<br>*<br>* |

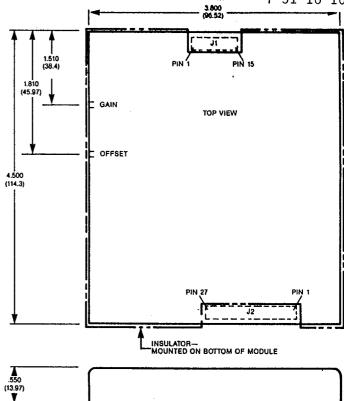

| THROUGHPUT Throughput Time (ADC and S/H)  A/D Conversion Time                                                    | 5.0 μs max<br>(200 kHz throughput)<br>3.5 μsec, typical                                                                                                                                                                                                                                         | *                            | MATING CONNECTOR                                                       | J1: Amp 103183-7 or equiv.<br>(analog, 16 pin)<br>J2: Amp 1-103183-2 or equiv<br>(digital, 28 pin)                                                | . *              |

| SAMPLE-TO-HOLD SWI<br>Aperture Delay<br>Aperture Uncertainty                                                     | TCHING  15 ns typical  ±50 ps typical  ±100 ps max                                                                                                                                                                                                                                              | *                            | PACKAGE SIZE®                                                          | 3.8 in. (96.5mm) × 4.5 in<br>(114.3mm) × 0.562 in.<br>(14.3mm) max. pkg. heigi                                                                    |                  |

(Specifications apply @ 25°C unless otherwise noted)

Same as Unipolar

- 1. Worst case summation of S/H and A/D non-linearity errors. Best fit straight-line.

- 2. After OFFSET/GAIN adjustment.

- 3. Internal (or external customer installed) pots allow field calibration.

- 4. Shaded areas denotes enhanced performance.

- 5. External 10 kΩ pull-up required.

- 6. Consult factory for mounting dimensions. 7 ZAD2846 is recommended for ultra low distortion applications.

ZAD2836 Three-Pass Digitally Corrected Sub-Ranging (DCSR) Architecture

#### Sample/Hold Characteristics:

The Sample/Hold is one of the most critical and difficult portions of any data acquisition system.

Through careful design, utilizing unique circuitry, the Sample/Hold section of the ZAD2836 provides true 16-bit linearity, dielectric absorption of 0.001% (< 1 LSB) necessary for accurately acquiring wide dynamic range inputs, and 1.5 microseconds total acquisition and settling time.

The ZAD2836's Sample/Hold is truly leading the state-of-the-art.

**Timing Diagram**

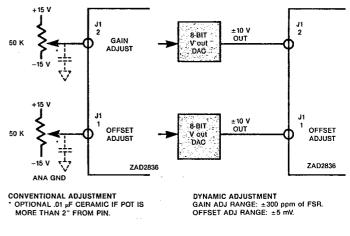

# Dynamic Adjustment of Gain and Offset:

In addition to internal gain and offset adjustment, provision has been made for the addition of external adjustments. By utilizing these pins and external voltage output D/A's, the gain and offset of the A/D can be dynamically adjusted by the host computer or microcomputer. The available adjustment range for the

ZAD2836 has been increased beyond that normally required to enable this dynamic adjustment to handle typical system gain and offset errors.

**External Offset and Gain Adjustment**

This provides the system designer with the capability to dynamically correct system errors, which results in increased accuracy, system stability and reduced long-term drift.

#### PC Board Layout

The analog input lead lengths should be as short as possible, preferably surrounded on both sides by an analog ground plane. The module has been carefully laid out internally to separate the analog input from the digital output. This practice should be extended to the PC board as much as possible. All digital control signals should also be kept away from the analog input.

Separate ground planes for analog and digital circuits associated with the ZAD2836 are extremely important. Of equal importance is the use of completely

8253887 0000581 0

T-51-10-16

separate analog and digital ground returns to their respective power supplies. No interconnection of these two returns should occur anywhere in the system except for that which is located within the ZAD2836. In addition, the use of the ANALOG RETURN PIN as an analog ground mecca is recommended. All of these precautions are suggested in order to minimize the effects of ground loops and to eliminate the possibility of digital noise coupling into the analog circuitry.

#### Power Supplies

In order to take advantage of the full 16-bit accuracy of the ZAD2836, it is recommended that well-regulated linear power supplies be used for the  $\pm 15V$  required by the ZAD2836.

#### **Output Coding**

| Unipolar<br>Binary | Offset<br>Binary | MSB LSB |

|--------------------|------------------|---------|

| + 9.99985 V        | +4.99985 V       | 1111    |

| + 5.00000 V        | +0.00000 V       | 1000    |

| +0.00000 V         | -5.00000 V       | 0000    |

|                    | ·                |         |

Note: For 2's complement coding use the MSB in place of the MSB output.

#### Input range selection:

| Range          | Connect                                 |

|----------------|-----------------------------------------|

| 0 to +10 Volts | signal Input is PIN 15,<br>GND PIN 9    |

| ±5 Volts       | PIN 10 to PIN 9, signal input is PIN 15 |

#### Additional Products from Analog Solutions

Precision A/D and D/A Converters

Precision 16-bit and 18-bit D/A Converters

High-Performance Sample/Hold Amplifiers

Logarithmic, Isolation and Special-Purpose Amplifiers

High-Speed Telecommunications A/D and D/A Systems

Precision Load Cell and Strain-Gage Sub-Systems

High Speed Industrial Control Interfaces

#### Custom Products

We invite customers to take full advantage of our custom design capability to provide the optimum product solution. Please contact our sales department for further information.

Ordering Guide

To Order Specify:

ZAD2836 16-Bit High-Speed Sampling A/D Converter

To place your order, contact Analog Solutions at (408) 433-1900

#### **Physical Outline**

NUMBERS IN PARENTHESIS ARE IN MM

#### J1 Pin Assignments

| 1. | OFFSET ADJ | 9.  | BIPOLAR  |

|----|------------|-----|----------|

| 2. | GAIN ADJ.  | 10. | REF, OUT |

| 3. | -15 V      | 11, | S/H OUT  |

| 4. | – 15V      | 12. | REF. RTN |

| 5. | ANALOG RTN | 13. | SIG. RTN |

| 6. | ANALOG RTN | 14. | SIG. RTN |

| 7. | +15 V      | 15. | SIG, IN  |

| 8. | +15 V      | 16. | SIG. RTN |

|    |            |     |          |

#### J2 Pin Assignments

| <i>3                                    </i> | Fin Assignments |                                  |

|----------------------------------------------|-----------------|----------------------------------|

| 1.                                           | TRIGGER         | 19. LO BYTE ENABLE*              |

| 2.                                           | EOC             | 20. HI BYTE ENABLE*              |

| 3.                                           | N/C             | 21. BIT 7                        |

| 4.                                           | N/C             | 22. BIT 8                        |

| 5.                                           | +5 V            | 23. BIT 5                        |

| 6.                                           | +5 V            | 24. BIT 6                        |

| 7.                                           | DIGITAL RTN     | 25. BIT 3                        |

| 8.                                           | DIGITAL RTN     | 26. BIT 4                        |

| 9.                                           | BIT 1           | 27. BIT 1 MSB                    |

| 10.                                          | DIGITAL RTN     | 28. BIT 2                        |

| 11.                                          | BIT 15          |                                  |

| 12.                                          | BIT 16 LSB      | N/C: Do Not Connect.             |

| 13.                                          | BIT 13          |                                  |

| 14.                                          | BIT 14          | SIG RTN, Analog RTN and          |

| 15.                                          | BIT 11          | Digital RTN Internally           |

| 16.                                          | BIT 12          | Connected                        |

| 17.                                          | BIT 9           |                                  |

| 18.                                          | BIT 10          | <ul><li>Open = Enabled</li></ul> |

#### Analog Solutions

85 West Tasman Drive San Jose, CA 95134-1703 Telephone: 408-433-1900 FAX: 408-433-9308 European Sales Office London; England Telephone: 0372-377779 Telex: 897628

4.5M 3/87 Data subject to change without notice.