# CEL California Eastern Laboratories

# APPLICATIONS

- Home Automation and Security

- Automatic Meter Reading

- Factory Automation and Motor Control

- Medical Patient Monitoring

- Voice Applications

- Replacement for legacy wired UART

- Energy Management

- Remote Keyless Entry w/ Acknowledgement

- Toys

- PC peripherals

# **KEY FEATURES**

- Embedded 8051 Compatible Microprocessor with 96KB Embedded Flash Memory for Program Space plus 8KB of Data Memory

- Scalable Data Rate: 250kbps for ZigBee, 500kbps and 1Mbps for custom applications.

- Voice Codec Support: µ-law/a-law/ADPCM

- High RF RX Sensitivity: -98dBm @1.5V

- High RF TX Power: +8dBm @1.5V

- 4 Level Power Management Scheme with Deep Sleep Mode (0.3µA)

- Single Voltage operation: 1.9 to 3.3V using an internal regulator (1.5V core)

- Software Tools and Libraries for the Development of Custom Applications

#### DESCRIPTION:

**ZIC2410** is a true single-chip solution, compliant with ZigBee specifications and IEEE802.15.4, a complete wireless solution for all ZigBee applications. The **ZIC2410** consists of an RF transceiver with baseband modem, a hardwired MAC and an embedded 8051 microcontroller with internal flash memory. The device provides numerous general-purpose I/O pins,

# peripheral functions such as timers and UART and is one of the first devices to provide an embedded Voice CODEC. This chip is ideal for very low power applications.

ZIC2410 Datasheet

The **ZIC2410** is available in two industry standard packages: a 48-pin QFN (7x7mm) or a 72-pin VFBGA (5x5mm) package.

CEL provides its customers with the *CEL ZigBee Stack*, software in a compiled library, as well as all the hardware & software tools required to develop custom applications. User application software can be compiled using any popular C-language compiler such as Keil.

- Single-chip 2.4GHz RF Transceiver

- Programmable Output Power up to +8dBm@1.5V

- High Sensitivity of –98dBm@1.5V

- Scalable Data Rate: 250Kbps for ZigBee, 500Kbps and 1Mbps for custom application

- On-chip VCO, LNA, and PA

- Low Operating Voltage of 1.5V

- Direct Sequence Spread Spectrum

- O-QPSK Modulation

- RSSI Measurement

- Compliant to IEEE802.15.4

- No External T/R Switch or Filter needed

# Hardwired MAC

- Two 256-byte circular FIFOs

- FIFO management

- AES Encryption/Decryption Engine (128bit)

- CRC-16 Computation and Check

#### 8051-Compatible Microcontroller

- 8051 Compatible (single cycle execution)

- 96KB Embedded Flash Memory

- 8KB Data Memory

- 128-byte CPU dedicated Memory

- 1KB Boot ROM

- Dual DPTR Support

- Multi-Bank Support for 96KB Program Memory (3Banks of 32KB)

- I2S/PCM Interface with two128-byte FIFOs

- µ-law/a-law/ADPCM Voice Codec

- Two High-Speed UARTs with Two 16-byte FIFOs (up to 1Mbps)

- 4 Timers/2 PWMs

- Watchdog Timer

- Sleep Timer

- Quadrature Signal Decoder

- 24 General Purpose I/Os

- Internal RC oscillator for Sleep Timer

- On-chip Power-on-Reset

- 4-channel 8-bit ADC

- SPI Master/Slave Interface

- ISP (In System Programming)

- Internal Temperature Sensor

#### **Clock Inputs**

- 16MHz Crystal for System Clock (optional 19.2MHz)

- 32.768KHz Crystal for Sleep Timer (optional)

Lcom

#### Power

- Internal Regulator for Single Voltage Operation w/ a large input voltage range (1.9~3.3V)

- À-Level Power Management Scheme with Deep Sleep Mode (0.3µA)

- Separate On-chip Regulators for Analog and Digital Circuitry.

- Battery Monitoring Support

#### **Included Software**

- Application Framework

- Software Tools

- IEEE and ZigBee Compliant Libraries

# **Package Options**

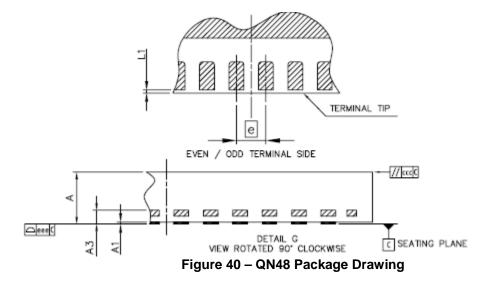

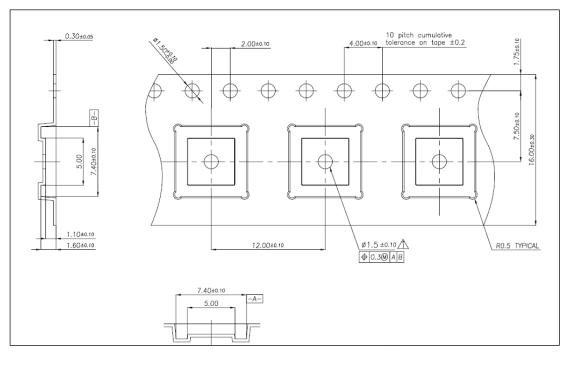

- Lead-Free 48-pin QFN Package (shown below) (7mm x 7mm x 0.9mm)

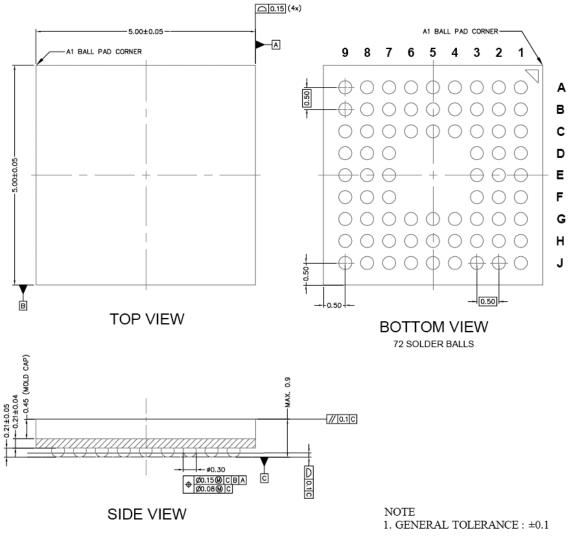

- Lead-Free 72-pin VFBGA Package (5mm × 5mm x 0.9mm)

#### **ORDERING INFORMATION**

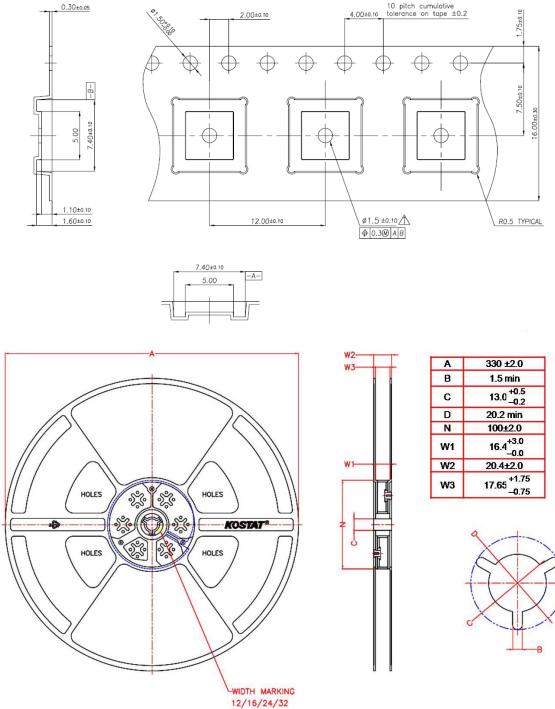

| Ordering Part Number | Description                | Minimum Order Quantity (MOQ) |

|----------------------|----------------------------|------------------------------|

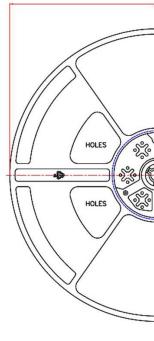

| ZIC2410QN48R         | 48-pin QFN Package (T/R)   | Tape & Reel (2500 per reel)  |

| ZIC2410FG72R         | 72-pin VFBGA Package (T/R) | Tape & Reel (2500 per reel)  |

| ZIC2410-EDK-1        | Demonstration Kit          | 1                            |

# **Table of Contents**

| 1 | FUNCTIONAL DESCRIPTION                                 | 5  |

|---|--------------------------------------------------------|----|

|   | 1.1 FUNCTIONAL OVERVIEW                                | 6  |

|   | 1.2 MEMORY ORGANIZATION                                | 7  |

|   | 1.2.1 PROGRAM MEMORY                                   |    |

|   |                                                        | 8  |

|   | 1.2.3 GENERAL PURPOSE REGISTERS (GPR)                  | 9  |

|   | 1.2.4 SPECIAL FUNCTION REGISTERS (SFR)<br>1.3 RESET    |    |

|   | 1.4 CLOCK SOURCE                                       |    |

|   | 1.5 INTERRUPT SCHEMES                                  |    |

|   | 1.6 POWER MANAGEMENT                                   |    |

|   | 1.7 ON-CHIP PERIPHERALS                                |    |

|   | 1.7.1 TIMER 0/1                                        |    |

|   | 1.7.2 TIMER 2/3, PWN 2/3                               |    |

|   | 1.7.3 WATCHDOG TIMER                                   |    |

|   | 1.7.4 SLEEP TIMER                                      |    |

|   | 1.7.5 INTERNAL RC OSCILLATOR<br>1.7.6 UART0/1          |    |

|   | 1.7.7 SPI MASTER/SLAVE                                 |    |

|   | 1.7.8 VOICE                                            |    |

|   | 1.7.9 RANDOM NUMBER GENERATOR (RNG)                    |    |

|   | 1.7.10 QUAD DECODER                                    | 52 |

|   | 1.7.11 INTERNAL VOLTAGE REGULATOR                      |    |

|   | 1.7.12 4-CHANNEL 8-BIT SENSOR ADC                      |    |

|   | 1.7.13 ON-CHIP POWER-ON RESET                          |    |

|   | 1.7.14 TEMPERATURE SENSOR<br>1.7.15 BATTERY MONITORING |    |

|   | 1.8 MEDIUM ACCESS CONTROL LAYER (MAC)                  |    |

|   | 1.8.1 RECEIVED MODE                                    |    |

|   | 1.8.2 TRANSMIT MODE                                    |    |

|   | 1.8.3 DATA ENCRYPTION AND DECRYPTION                   |    |

|   | 1.9 PHYSICAL LAYER (PHY)                               | 66 |

|   | 1.9.1 INTERRUPT                                        |    |

|   | 1.9.2 REGISTERS                                        |    |

|   | 1.10 IN-SYSTEM PROGRAMMING (ISP)                       |    |

|   | 1.11 ZIC2410 INSTRUCTION SET SUMMARY                   |    |

| _ | 1.12 DIGITAL I/O                                       |    |

| 2 | AC & DC CHARACTERISTICS                                | 93 |

|   | 2.1 ABSOLUTE MAXIMUM RATINGS                           |    |

|   | 2.2 DC CHARACTERISTICS                                 |    |

|   | 2.3 ELECTRICAL SPECIFICATIONS                          |    |

|   | 2.3.1 ELECTRICAL SPECIFICATIONS with an 8MHz CLOCK     |    |

|   | 2.3.2 ELECTRICAL SPECIFICATIONS with a 16MHz CLOCK     |    |

|   | 2.3.3 AC CHARACTERISTICS                               |    |

| 3 | PACKAGE & PIN DESCRIPTIONS                       | 101 |

|---|--------------------------------------------------|-----|

|   | 3.1 PIN ASSIGNMENTS                              | 101 |

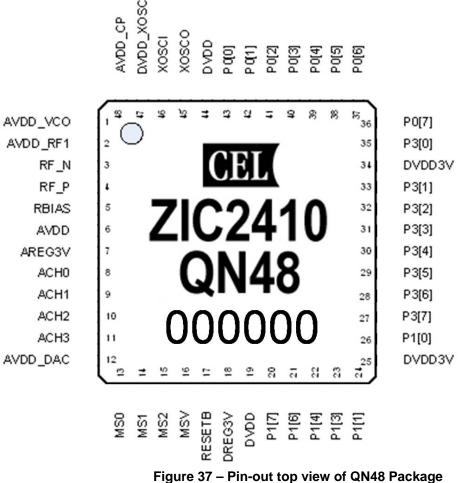

|   | 3.1.1 QN48 Package                               | 101 |

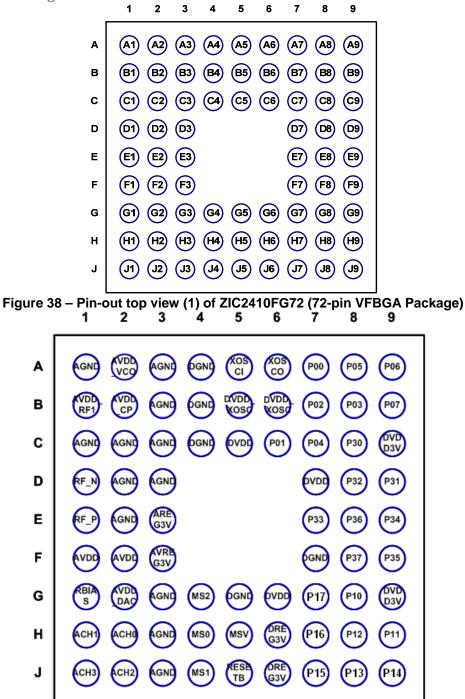

|   | 3.1.2 FG72 Package                               | 104 |

|   | 3.2 PACKAGE INFORMATION                          | 107 |

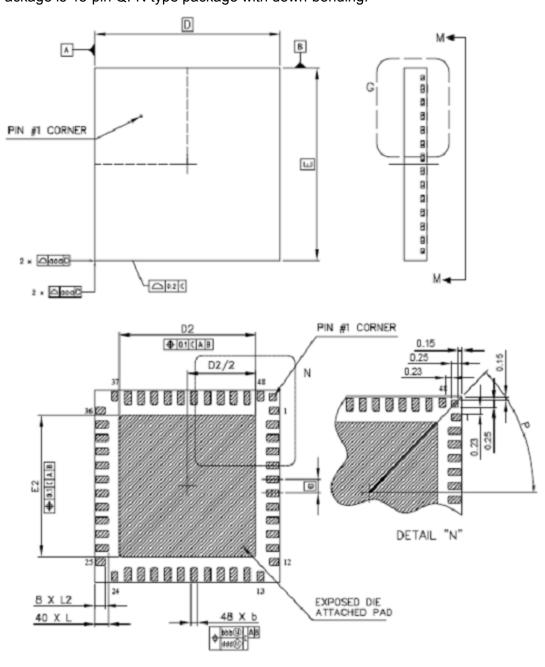

|   | 3.2.1 PACKAGE INFORMATION: ZIC2410QN48 (QN48pkg) | 107 |

|   | 3.2.2 PACKAGE INFORMATION: ZIC2410FG72 (FG72pkg) | 110 |

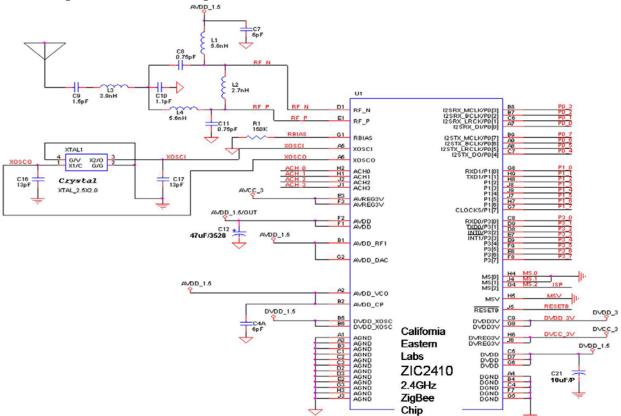

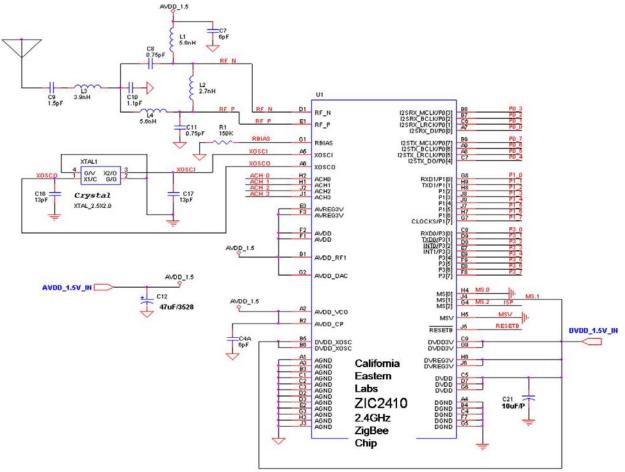

|   | 3.3 APPLICATION CIRCUITS                         | 112 |

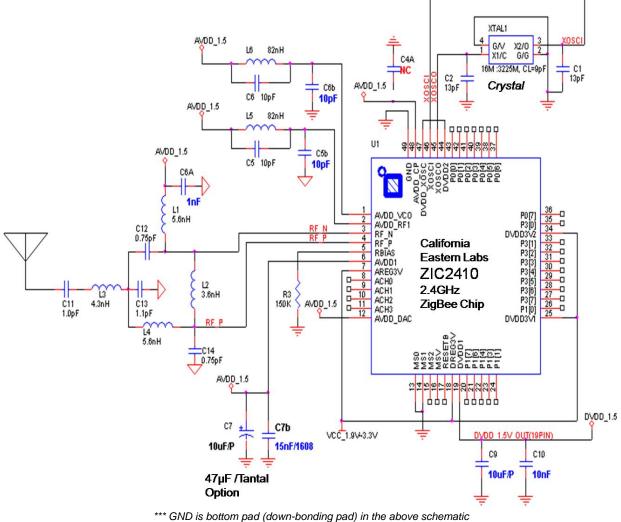

|   | 3.3.1 APPLICATION CIRCUITS (QN48 package)        | 112 |

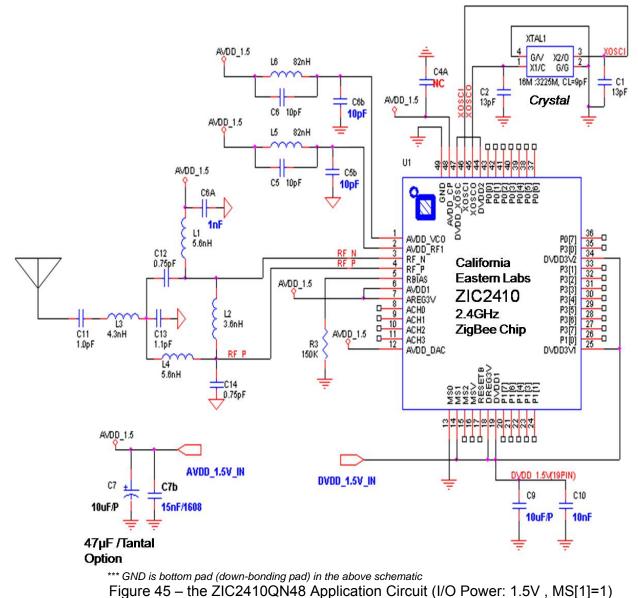

|   | 3.3.2 APPLICATION CIRCUITS (FG72 package)        | 114 |

| 4 | REFERENCES                                       | 116 |

|   | 4.1 TABLE OF TABLES                              | 116 |

|   | 4.2 TABLE OF FIGURES                             |     |

|   | 4.3 TABLE OF EQUATIONS                           |     |

| 5 | REVISION HISTORY                                 | 119 |

# **1 FUNCTIONAL DESCRIPTION**

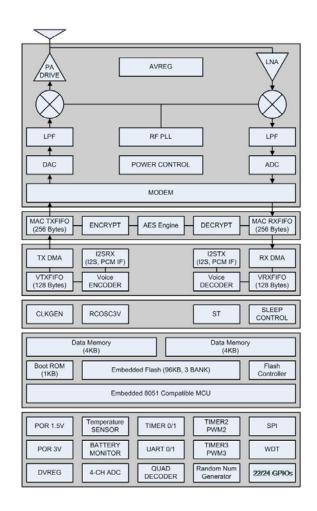

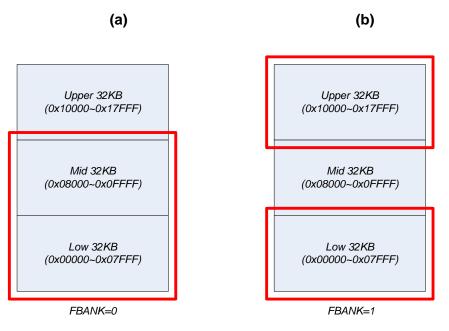

Figure 1 shows the block diagram of ZIC2410. The ZIC2410 consists of a 2.4GHz RF, Modem (PHY Layer), a MAC hardware engine, a Voice CODEC block, Clocks, Peripherals, and a memory and Microcontroller (MCU) block.

# **1.1 FUNCTIONAL OVERVIEW**

In the receive mode, the received RF signal is amplified by the Low Noise Amplifier (LNA), down-converted to a quadrature signal and then to baseband. The baseband signal is filtered, amplified, converted to a digital signal by the ADC and transferred to a modem. The data, which is the result of signal processing such as dispreading, is transferred to the MAC block.

In transmit mode, the buffered data at the MAC is transferred to a baseband modem which, after signal processing such as spreading and pulse shaping, outputs a signal through the DAC. The Analog baseband signal is filtered by the low-pass filter, converted to RF signal by the up-conversion mixer, is amplified by PA, and finally applied to the antenna.

The MAC block provides IEEE802.15.4 compliant hardware and it is located between microprocessor and a baseband modem. MAC block includes FIFOs for transmitting/receiving packet, AES engine for security operation, CRC and related control circuit. In addition, it supports automatic CRC check and address decoding.

ZIC2410 integrates a high performance embedded microcontroller, compatible to an Intel i8051 microcontroller in an instruction level. This embedded microcontroller has 8-bit operation architecture sufficient for controller applications. The embedded microcontroller has 4-stage pipeline architecture to improve the performance over previous compatible chips making it capable of executing simple instructions during a single cycle.

The memory organization of the embedded microcontroller consists of program memory and data memory. The data memory has 2 memory areas. For more detailed explanation, refer to the data memory section (1.2.2.)

The ZIC2410 includes 22 GPIO for the QN48 packaged device and 24 GPIO for the FG72 packaged part and various peripheral circuits to aid in the development of an application circuit with an interrupt handler to control the peripherals. ZIC2410 uses 16MHz crystal oscillator for RF PLL and 8MHz clock generated from 16MHz in clock generator is used for microcontroller, MAC, and the clock of a baseband modem.

The ZIC2410 supports a voice function as follows. The data generated by an external ADC is input to the voice block via I2S interface. After the data is received via I2S it is compressed by the voice codec, and stored in Voice TXFIFO. The data in Voice TXFIFO is transferred to the MAC TXFIFO and then transmitted via PHY. In contrast, the received data in MAC RXFIFO is transferred to voice RXFIFO via DMA operation. The data in voice RXFIFO is decompressed by the internal voice codec. The decompressed data is then transferred to the external DAC via I2S interface.

# **1.2 MEMORY ORGANIZATION**

# 1.2.1 PROGRAM MEMORY

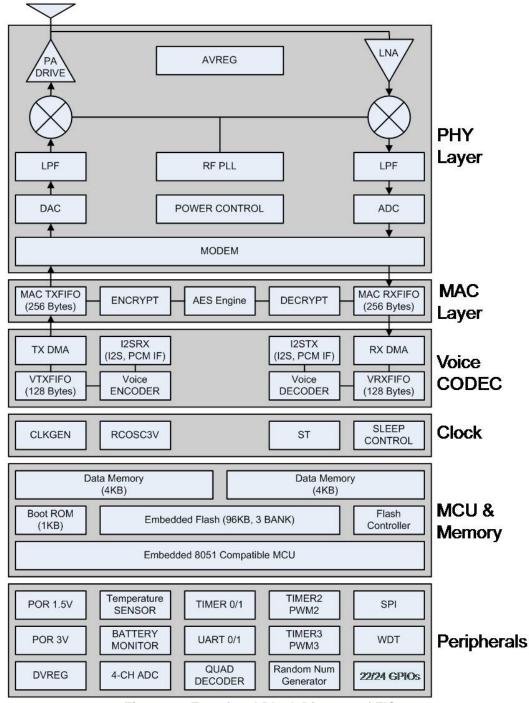

The address space of the program memory is 64KB (0x0000~0XFFFF). Basically, the lower 63KB of program memory is implemented by Non-volatile memory. The upper 1KB from 0XFC00 to 0XFFFF is implemented by both Non-volatile memory and ROM. As shown in Figure 2 below, there are two types of memory in the same address space. The address space, which is implemented by Non-volatile memory, is used as general program memory and the address space, which is implemented by ROM, is used for ISP (In-System Programming).

As shown in (a) of Figure 2 below, when Power is turned on, the upper 1KB of program memory is mapped to ROM. As shown in (b) of Figure 2, if this program area (1KB) is used as non-volatile program memory, ENROM should be set to '0'. See the SFR section (1.2.4) for ENROM.

Figure 2 – Address Map of Program Memory

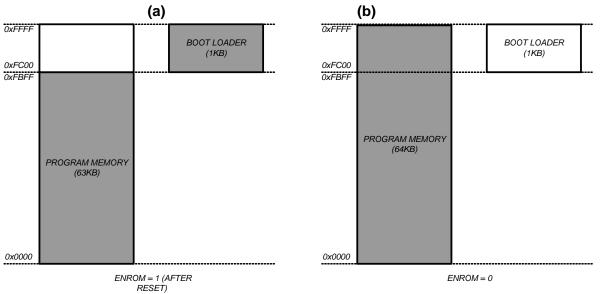

ZIC2410 includes non-volatile memory of 96KB. However, as described already, program memory area is 64KB. Therefore, if necessary, the upper 64KB of physical 96KB non-volatile memory is separated into two 32KB memory banks. Each bank is logically mapped to the program memory. When FBANK value is '0', lower 64KB of non-volatile memory is used as shown in (a) of Figure 3. When FBANK value is '1', lower 32 KB and upper 32KB of non-volatile memory are used as shown in (b) of Figure 3. See the SFR section (1.2.4) for FBANK.

Figure 3 – Bank Selection of Program Memory

#### **1.2.2 DATA MEMORY**

ZIC2410 reserves 64 KB of data memory address space. This address space can be accessed

by the MOVX command.

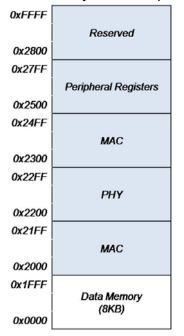

Figure 4 shows the address map of this data memory.

Figure 4 – Address Map of Data Memory

The data memory used in the application programs resides in the address range 0x0000-0x1FFF.

The registers and memory used in the MAC block reside in the address range 0x2000-0x21FF and 0x2300-0x24FF respectively. The registers to control or report the status of the PHY block reside in the address range 0x2200-0x22FF.

Registers related to the numberous peripheral functions of the embedded microprocessor reside in the address range of 0x2500-0x27FF.

# 1.2.3 GENERAL PURPOSE REGISTERS (GPR)

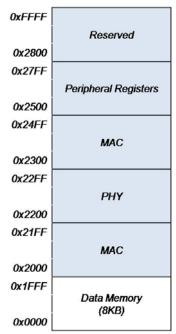

Figure 5 describes the address map of the General Purpose Registers (GPRs). GPRs can be addressed either directly or indirectly. As shown in the lower address space of Figure 5, a bank consists of 8 registers.

The address space above the bank area is the bit addressable area, which is used as a flag by software or by a bit operation. The address space above the bit addressable area includes registers used as a general purpose of a byte unit. For the detailed information, refer to the paragraphs following Figure 5 below.

Figure 5 – GPRs Address Map

**Register Bank 0-3:** It is located from 0x00 to 0x1F (32 bytes). One bank consists of each 8 registers out of 32 registers. Therefore, there are total 4 banks. Each bank should be selected by software as referring the RS field in PSW register. The bank (8 registers) selected by RS value can be accessed by a name (R0-R7) by software. After reset, the default value is set to bank0.

**Bit Addressable Area:** The address is assigned to each bit of 16 bytes (0x20~0x2F) and registers, which is the multiple of 8, in SFR. Each bit can be accessed by the address which is assigned to these bits. 128 bits (16 bytes, 0x20~0x2F) can be accessed by direct addressing for each bit (0~127) and by a byte unit as using the address from 0x20~0x2F.

**Data RAM Area:** A user can use registers (0x30~0x7F) as a general purpose.

# **1.2.4 SPECIAL FUNCTION REGISTERS (SFR)**

Generally, a register is used to store the data. MCU needs the memory to control the embedded hardware or the memory to show the hardware status. Special Function Registers (SFRs) process the functions described above. SFRs include the status or control of the I/O ports, the timer registers, the stack pointers and so on. Table 1 shows the address to all SFRs in ZIC2410.

All SFRs are accessed by a byte unit. However, when SFR address is a multiple of 8, it can be accessed by a bit unit.

| Register<br>Name | SFR<br>Address | B7 | B6    | B5    | B4    | B3   | B2    | B1   | B0   | Initial<br>Value |

|------------------|----------------|----|-------|-------|-------|------|-------|------|------|------------------|

| EIP              | 0xF8           |    | VCEIP | SPIIP | RTCIP | T3IP | AESIP | T2IP | RFIP | 0x00             |

| В                | 0xF0           |    |       |       |       |      |       |      |      | 0x00             |

| EIE              | 0xE8           |    | VCEIE | SPIIE | RTCIE | T3IE | AESIE | T2IE | RFIE | 0x00             |

| Table 1 – | Special | Function  | Register ( | (SFR) Ma | n |

|-----------|---------|-----------|------------|----------|---|

|           | opeciai | I unction | Register   |          |   |

| Register<br>Name | SFR<br>Address | B7    | B6    | B5   | B4    | B3    | B2        | B1       | B0        | Initial<br>Value |

|------------------|----------------|-------|-------|------|-------|-------|-----------|----------|-----------|------------------|

| ACC              | 0xE0           |       |       |      |       |       |           |          |           | 0x00             |

| EICON            |                |       |       |      |       | RTCIF |           |          |           |                  |

| WDT              | 0xD8<br>0xD2   |       |       |      | WDTWE | WDTEN | WDTCLR    |          | I<br>TPRE | 0x00<br>0x0B     |

| PSW              | 0xD2<br>0xD0   | CY    | AC    | F0   | R     |       | OV        | F1       | P         | 0x0B             |

| WCON             | 0xD0<br>0xC0   | Cr    | AC    | FU   | ĸ     | 3     | ISPMODE   | ENROM    | P         | 0x00<br>0x00     |

| P3REN            | 0xC0<br>0xBC   |       |       |      |       |       | ISPIVIODE | EINROIVI |           | 0x00<br>0xFF     |

| P3REN<br>P1REN   | 0xBC<br>0xBA   |       |       |      |       |       |           |          | -         | 0xFF<br>0xFF     |

| POREN            | 0xBA           |       |       |      |       |       |           |          |           | 0xFF             |

| IP               | 0xB9           |       | PS1   |      | PS0   | PT1   | PX1       | PT0      | PX0       | 0x00             |

| P3OEN            | 0xB8           |       | FOI   |      | F30   | FII   | FAI       | FIU      | FAU       | 0x00             |

| P10EN            | 0xB2           |       |       |      |       |       |           |          |           | 0x00             |

| POOEN            | 0xB1           |       |       |      |       |       |           |          |           | 0x00             |

| P3               | 0xB0           |       |       |      |       |       |           |          |           | 0x3F             |

| TL3              | 0xAD           |       |       |      |       |       |           |          |           | 0x00             |

| TL2              | 0xAC           |       |       |      |       |       |           |          |           | 0x00             |

| TH3              | 0xAB           |       |       |      |       |       |           |          |           | 0x00             |

| TH2              | 0xAA           |       |       |      |       |       |           |          |           | 0x00             |

| T23CON           | 0xA9           |       |       |      |       | TR3   | M3        | TR2      | M2        | 0x00             |

| IE               | 0xA8           | EA    | ES1   |      | ES0   | ET1   | EX1       | ET0      | EX0       | 0x00             |

| AUXR1            | 0xA2           |       | -     |      |       |       |           |          | DPS       | 0x00             |

| FBANK            | 0xA1           | RAM1  | RAM0  |      |       |       |           | FB/      | ANK       | 0x00             |

| EXIF             | 0x91           | T3IF  | AESIF | T2IF | RFIF  |       |           |          |           | 0x00             |

| P1               | 0x90           |       |       |      |       |       |           |          |           | 0xFF             |

| TH1              | 0x8D           |       |       |      |       |       |           |          |           | 0x00             |

| TH0              | 0x8C           |       |       |      |       |       |           |          |           | 0x00             |

| TL1              | 0x8B           |       |       |      |       |       |           |          |           | 0x00             |

| TL0              | 0x8A           |       |       |      |       |       |           |          |           | 0x00             |

| TMOD             | 0x89           | GATE1 | CT1   |      | M1    | GATE0 | CT0       | N        | /0        | 0x00             |

| TCON             | 0x88           | TF1   | TR1   | TF0  | TR0   | IE1   | IT1       | IE0      | IT0       | 0x00             |

| PCON             | 0x87           |       |       |      |       |       |           | PD       | IDLE      | 0x00             |

| P0SEL            | 0x85           |       |       |      |       |       |           | ExNoEdge | P0AndSEL  | 0x00             |

| P0MSK            | 0x84           |       |       |      |       |       |           |          |           | 0xFF             |

| DPH              | 0x83           |       |       |      |       |       |           |          |           | 0x00             |

| DPL              | 0x82           |       |       |      |       |       |           |          |           | 0x00             |

| SP               | 0x81           |       |       |      |       |       |           |          |           | 0x07             |

| P0               | 0x80           |       |       |      |       |       |           |          |           | 0xFF             |

The following section describes each SFR related to microprocessor.

# Table 2 – Register Bit Conventions

| Symbol | Access Mode |

|--------|-------------|

| RW     | Read/write  |

| RO     | Read Only   |

| Bit                            | Name                                                       | Descriptions                                                                                                                                                                                                                                                                                                                                          | <u>R/W</u>            | <u>Reset</u><br>Value |

|--------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|

|                                |                                                            | NTROL REGISTER, 0xC0)                                                                                                                                                                                                                                                                                                                                 |                       |                       |

|                                | register can coi                                           | ntrol the upper 1KB of program memory.                                                                                                                                                                                                                                                                                                                |                       | 0                     |

| 7:3                            |                                                            | Reserved                                                                                                                                                                                                                                                                                                                                              |                       | 0                     |

| 2                              | ISPMODE                                                    | <b>ISP Mode Indication</b> : When MS [1:0], an external pin, is '3', this field is set to 1 by hardware. It notifies the MCU whether ISPMODE or not.                                                                                                                                                                                                  | RO                    | -                     |

| 1                              | ENROM                                                      | When this field is '1', the upper 1KB (0xFC00~0xFFFF) is mapped to ROM. When this field is '0', the upper 1KB (0xFC00~0xFFFF) is mapped to non-volatile memory.                                                                                                                                                                                       | R/W                   | 1                     |

| 0                              |                                                            | Reserved                                                                                                                                                                                                                                                                                                                                              |                       | 0                     |

| -                              | NK (PROGRAM                                                | MEMORY BANK SELECTION REGISTER, 0xA1)                                                                                                                                                                                                                                                                                                                 | 1                     |                       |

| 7:1                            |                                                            | Reserved                                                                                                                                                                                                                                                                                                                                              |                       | 0x00                  |

| 0                              | FBANK                                                      | Program Memory Bank Select.<br>0: Bank0 (Default)<br>1: Bank1<br>2: Not Used<br>3: Not Used                                                                                                                                                                                                                                                           | R/W                   | 0                     |

| ACC                            | UMULATOR (0                                                |                                                                                                                                                                                                                                                                                                                                                       |                       |                       |

|                                |                                                            | ed as A or ACC and it is related to all the operations.                                                                                                                                                                                                                                                                                               |                       |                       |

| 7:0                            | A                                                          | Accumulator                                                                                                                                                                                                                                                                                                                                           | R/W                   | 0x00                  |

| conta<br>opera<br>time,        | ains the MSB dation, this regist                           | e used as a general-purpose register. After multiplication is process<br>ata and 'A register' contains LSB data for the multiplication result. In<br>the stores the value before division (dividend) and the remainder after<br>, the divisor should be stored in 'A register' and result value (quotien<br>B register. Used in MUL/DIV instructions. | division<br>divisior  | . At this             |

|                                |                                                            | S WORD (PSW, 0xD0)<br>the status of the program. The explanation for each bit is as follows.                                                                                                                                                                                                                                                          |                       |                       |

| 7                              | CY                                                         | Carry flag                                                                                                                                                                                                                                                                                                                                            | R/W                   | 0                     |

| 6                              | AC                                                         | Auxiliary carry flag                                                                                                                                                                                                                                                                                                                                  | R/W                   | 0                     |

| 5                              | F0                                                         | Flag0. User-defined                                                                                                                                                                                                                                                                                                                                   | R/W                   | 0                     |

| 4:3                            | RS                                                         | Register bank select.<br>0: Bank0<br>1: Bank1<br>2: Bank2<br>3: Bank3                                                                                                                                                                                                                                                                                 | R/W                   | 0                     |

| 2                              | OV                                                         | Overflow flag                                                                                                                                                                                                                                                                                                                                         | R/W                   | 0                     |

| 1                              | F1                                                         | Flag1. User-defined                                                                                                                                                                                                                                                                                                                                   | R/W                   | 0                     |

| 0                              | Р                                                          | Parity flag.<br>Set to 1 when the value in accumulator has odd number of '1'<br>bits.                                                                                                                                                                                                                                                                 | R/W                   | 0                     |

| Whei<br>store<br>a ger<br>This | d in stack to inf<br>neral purpose ((<br>register value is |                                                                                                                                                                                                                                                                                                                                                       | h can be<br>ased afte | used for<br>the data  |

| Table 3 – Special Function Registers |  |

|--------------------------------------|--|

|                                      |  |

| <u>Bit</u> | <u>Name</u>  | Descriptions                                                                                                                                                                  | <u>R/W</u> | <u>Reset</u><br>Value |  |  |  |  |

|------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------|--|--|--|--|

| DAT        | A POINTER (D | PH: 0x83, DPL: 0x82)                                                                                                                                                          |            |                       |  |  |  |  |

|            |              | s of a high byte (DPH) and a low byte (DPL) to support 16-bit addres<br>register or by two 8-bit registers respectively.                                                      | ss. It can | be                    |  |  |  |  |

| 7:0        | DPH          | Data pointer, high byte                                                                                                                                                       | R/W        | 0x00                  |  |  |  |  |

| 7:0        | DPL          | Data pointer, low byte                                                                                                                                                        | R/W        | 0x00                  |  |  |  |  |

|            |              | Y CONTROL REGISTER, 0xA2)                                                                                                                                                     |            |                       |  |  |  |  |

|            |              | I to implement Dual DPTR functions. Physically, DPTR consists of D                                                                                                            |            |                       |  |  |  |  |

|            |              | DPTR0 and DPTR1 can be accessed depending on the DPS value of<br>prevention they compare the accessed at the same time.                                                       | of AUXR1   |                       |  |  |  |  |

| 7:1        |              | er words, they cannot be accessed at the same time.                                                                                                                           |            | 0x00                  |  |  |  |  |

| 0          | DPS          | Dual DPTR Select:       Used to select either DPTR0 or DPTR1.         DPS       When DSP is '0', DPTR0 is selected. When DSP is '1', DPTR1 is selected.         B0)           |            |                       |  |  |  |  |

| P3 (0      | )xB0)        | Selected.                                                                                                                                                                     |            |                       |  |  |  |  |

|            |              | n be used as other functions besides general purpose I/O.                                                                                                                     |            |                       |  |  |  |  |

|            | P3.7         | This port register is used as a general purpose I/O port (12mA Drive).                                                                                                        |            |                       |  |  |  |  |

|            | /PWM3        | When Timer3 is operated as a PWM mode, it outputs PWM wave (PWM3) of Timer3.                                                                                                  |            |                       |  |  |  |  |

| 7          | /CTS1        | When port register is used as UART1, it is used as a CTS signal (CTS1) of UART1.                                                                                              | R/W        | 0                     |  |  |  |  |

|            | /SPICSN      | When used as a Master mode, SPI Slave Select signal is outputted. When used as a Slave mode, this port register receives SPI Slave Select signal. This signal activate in low |            |                       |  |  |  |  |

|            | P3.6         | This port register is used as a general purpose I/O port (12mA Drive)                                                                                                         |            |                       |  |  |  |  |

|            | /PWM2        | When Timer2 is operated as a PWM mode, it outputs PWM wave (PWM2) of Timer2.                                                                                                  |            |                       |  |  |  |  |

| 6          | /RTS1        | When port register is used as UART1, it is used as a RTS signal (RTS1) of UART1.                                                                                              | R/W        | 0                     |  |  |  |  |

|            | /SPICLK      | When used as a Master mode, SPI clock is outputted. When used as a Slave mode, this port register receives SPI clock.                                                         |            |                       |  |  |  |  |

|            | P3.5         | This port register is used as a general purpose I/O port.                                                                                                                     |            |                       |  |  |  |  |

|            | /T1          | When Timer1 is operated as a COUNTER mode, it is operated as a counter input signal (T1) of Timer1.                                                                           | -          |                       |  |  |  |  |

| 5          | /CTS0        | When port register is used as UART0, it is used as a CTS signal (CTS0) of UART0.                                                                                              | R/W        | 1                     |  |  |  |  |

| 5          | /SPIDO       | In a Master mode or a Slave mode, this port register is used for outputting SPI data.                                                                                         |            |                       |  |  |  |  |

|            | /QUADYB      | When port register is used as QUAD function, it is used as the input signal of YB value.                                                                                      |            |                       |  |  |  |  |

|            | P3.4         | This port register is used as a general purpose I/O port.                                                                                                                     |            |                       |  |  |  |  |

| 4          | /ТО          | When Timer0 is operated as a COUNTER mode, it is operated as a counter input signal (T0) of Timer0.                                                                           | R/W        | 1                     |  |  |  |  |

|            | /RTS0        | When port register is used as UART0, it is used as a RTS signal (RTS0) of UART0.                                                                                              |            |                       |  |  |  |  |

| <u>Bit</u> | <u>Name</u>                                                                                                         | Descriptions                                                                                                                                  | <u>R/W</u> | <u>Reset</u><br>Value |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------|--|--|--|

|            | /SPIDI                                                                                                              | In a Master mode or a Slave mode, this port register is used for receiving SPI data.                                                          |            |                       |  |  |  |

|            | /QUADYA                                                                                                             | When port register is used as QUAD function, it is used as the input signal of YA value.                                                      |            |                       |  |  |  |

| 2          | P3.3                                                                                                                | <b>P3.3</b> This port register is used as a general purpose I/O port.                                                                         |            |                       |  |  |  |

| 3          | <ul> <li><sup>3</sup> /INT1</li> <li>P3.2</li> <li>2 /INT0</li> <li>P3.1</li> <li>/TXD0</li> <li>/QUADXB</li> </ul> | When port register is used as an input signal, it can receive an external interrupt (INT1).                                                   | R/W        | 1                     |  |  |  |

|            | P3.2                                                                                                                | This port register is used as a general purpose I/O port.                                                                                     |            |                       |  |  |  |

| 2          | /INT0                                                                                                               | When port register is used as an input signal, it can receive an external interrupt (INT0).                                                   | R/W        | 1                     |  |  |  |

|            | P3.1                                                                                                                | This port register is used as a general purpose I/O port.                                                                                     |            |                       |  |  |  |

| 1          | /TXD0                                                                                                               | When port register is used as UART0, it is used as a UART0 data output (TXD0).                                                                | R/W        | 1                     |  |  |  |

|            | /QUADXB                                                                                                             | When port register is used as QUAD function, it is used as the input signal of XB value.                                                      |            |                       |  |  |  |

|            | P3.0                                                                                                                | This port register is used as a general purpose I/O port.                                                                                     |            |                       |  |  |  |

| 0          | /RXD0                                                                                                               | R/W                                                                                                                                           | 1          |                       |  |  |  |

|            | /QUADXA                                                                                                             | When port register is used as QUAD function, it is used as the input signal of XA value.                                                      |            |                       |  |  |  |

|            | 0x90)<br>port register ca<br>P1.7                                                                                   | n be used as other functions besides general purpose I/O.                                                                                     |            |                       |  |  |  |

|            | P1.7                                                                                                                | This port register is used as a general purpose I/O port.                                                                                     |            |                       |  |  |  |

| 7          | /P0AND                                                                                                              | When P0AndSel value in P0SEL register is set to '1', P1.7 outputs the result of bit-wise AND operation of (P0 OR P0MSK).                      | R/W        | 1                     |  |  |  |

|            | /TRSW                                                                                                               | It can be used as TRSW (RF TX/RX Indication signal) signal by setting the PHY register.                                                       |            |                       |  |  |  |

|            | P1.6                                                                                                                | This port register is used as a general purpose I/O port.                                                                                     |            |                       |  |  |  |

| 6          | /TRSWB                                                                                                              | It can be used as TRSWB (TRSW Inversion) signal by setting the PHY register.                                                                  | R/W        | 1                     |  |  |  |

| 5          | P1.5                                                                                                                | This port register is used as a general purpose I/O port.                                                                                     | R/W        | 1                     |  |  |  |

|            | P1.4                                                                                                                | This port register is used as a general purpose I/O port.                                                                                     |            |                       |  |  |  |

| 4          | /QUADZB                                                                                                             | When this port register is used as QUAD function, it is used as the input signal of ZB value.                                                 | R/W        | 1                     |  |  |  |

|            | /RTXTALI                                                                                                            | This port register is used for connecting to the external crystal (32.768KHz), which is used in the Sleep Timer, by setting the PHY register. |            |                       |  |  |  |

|            | P1.3                                                                                                                | This port register is used as a general purpose I/O port.                                                                                     |            |                       |  |  |  |

|            | F I.J                                                                                                               |                                                                                                                                               |            |                       |  |  |  |

| <u>Bit</u>   | <u>Name</u>                      | Descriptions                                                                                                                                  | <u>R/W</u> | <u>Reset</u><br>Value |

|--------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------|

|              | /RTXTALO                         | This port register is used for connecting to the external crystal (32.768KHz), which is used in the Sleep Timer, by setting the PHY register. |            |                       |

|              | /RTCLKO                          | This port register is used to output the internal RCOSC by setting the PHY register.                                                          |            |                       |

| 2            | P1.2                             | This port register is used as a general purpose I/O port.                                                                                     | R/W        | 1                     |

|              | P1.1                             | This port register is used as a general purpose I/O port.                                                                                     |            |                       |

| 1            | /TXD1                            | When this port register is used as UART1, it is used as UART1 data output (TXD1).                                                             | R/W        | 1                     |

|              | P1.0                             | This port register is used as a general purpose I/O port.                                                                                     |            |                       |

| 0            | /RXD1                            | When this port register is used as UART1, it is used as UART1 data input (RXD1).                                                              | R/W        | 1                     |

|              | <b>)x80)</b><br>port register ca | n be used as other functions besides general purpose I/O.                                                                                     |            |                       |

|              | P0.7                             | This port register is used as a general purpose I/O port.                                                                                     |            |                       |

| 7            | /I2STXMCL<br>K                   | When this port register is used as I2S, it is operated as TX<br>Master clock of I2S interface.                                                | R/W        | 1                     |

|              | P0.6                             | This port register is used as a general purpose I/O port.                                                                                     |            |                       |

| 6            | /I2STXBCL<br>K                   | When this port register is used as I2S, it is operated as TX Bit clock of I2S interface.                                                      | R/W        | 1                     |

|              | P0.5                             | This port register is used as a general purpose I/O port.                                                                                     |            |                       |

| 5            | /I2STXLRC<br>K                   | When this port register is used as I2S, it is operated as TX LR clock of I2S interface.                                                       | R/W        | 1                     |

|              | P0.4                             | This port register is used as a general purpose I/O port.                                                                                     |            |                       |

| 4            | /I2STXDO                         | When this port register is used as I2S, it is operated as TX data output of I2S interface.                                                    | R/W        | 1                     |

| _            | P0.3                             | This port register is used as a general purpose I/O port.                                                                                     |            | _                     |

| 3            | /I2SRXMCL<br>K                   | When this port register is used as I2S, it is operated as RX<br>Master clock of I2S interface.                                                | R/W        | 1                     |

| -            | P0.2                             | This port register is used as a general purpose I/O port.                                                                                     |            |                       |

| 2            | /I2SRXBCL<br>K                   | When this port register is used as I2S, it is operated as RX Bit clock of I2S interface.                                                      | R/W        | 1                     |

|              | P0.1                             | This port register is used as a general purpose I/O port.                                                                                     | 544        |                       |

| 1            | /I2SRXLRC<br>K                   | When this port register is used as I2S, it is operated as the RX LR clock of the I2S interface.                                               | R/W        | 1                     |

|              | P0.0                             | This port register is used as a general purpose I/O port.                                                                                     | ]          |                       |

| 0            | /I2SRXDI                         | When this port register is used as I2S, it is operated as the RX data input of the I2S interface.                                             | R/W        | 1                     |

| P0O<br>outpu | EN, P1OEN and                    |                                                                                                                                               |            | e output              |

| 1            |                                  | Reserved                                                                                                                                      |            | 0                     |

| Bit  | <u>Name</u>    | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <u>R/W</u>   | <u>Reset</u><br>Value |

|------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------|

| 7:0  | P30EN          | It controls the TX buffer function for each pin in Port3. When each bit field is set to '0', the TX buffer of the corresponding pin outputs the value.                                                                                                                                                                                                                                                                                                                                                                   | R/W          | 0x00                  |

| 6:0  | P10EN          | It controls the TX buffer function for each pin in Port1. When each bit field is set to '0', the TX buffer of the corresponding pin outputs the value. P1.7 only acts as output.                                                                                                                                                                                                                                                                                                                                         | R/W          | 0x00                  |

| 7:0  | P00EN          | It controls the TX buffer function for each pin in Port0. When each bit field is set to '0', the TX buffer of the corresponding pin outputs the value.                                                                                                                                                                                                                                                                                                                                                                   | R/W          | 0x00                  |

| PORE | EN, P1REN, P3  | REN (0xB9, 0xBA, 0xBC)<br>BREN enable Pull-up of port 0, 1 and 3. When each bit area is cleare<br>ding port is enabled.                                                                                                                                                                                                                                                                                                                                                                                                  | ed to '0', i | the Pull-             |

| 7    |                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | 1                     |

| 7:0  | P3REN          | It controls the Pull-up function for each pin in Port3. When each bit field is set to '0', the Pull-up function of the corresponding pin is operated.                                                                                                                                                                                                                                                                                                                                                                    | R/W          | 0xFF                  |

| 6:0  | P1REN          | It controls the Pull-up function for each pin in Port1. When each bit field is set to '0', the Pull-up function of the corresponding pin is operated.<br>*P1.7 doesn't have a control field because it is operated as an output.                                                                                                                                                                                                                                                                                         | R/W          | 0x7F                  |

| 7:0  | POREN          | It controls the Pull-up function for each pin in Port0. When each bit field is set to '0', the Pull-up function of the corresponding pin is operated.                                                                                                                                                                                                                                                                                                                                                                    | R/W          | 0xFF                  |

| P0M  | SK (P0 INPUT   | MASK REGISTER, 0x84)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |                       |

| 7:0  | POMSK          | This register is used for masking the input of P0 pin (Refer to P0AndSel in P0SEL register).                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W          | 0xFF                  |

| POSE | EL (P0 INPUT S | SELECTION REGISTER, 0x85)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                       |

| 7:2  |                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | 0                     |

| 1    | ExNoEdge       | Controls the wake up of the MCU by an external interrupt when in<br>the power-down mode.<br>When this field is '0', the MCU wakes up when INT0 or INT1<br>signal is high (This is the normal case in the MCU.)<br>When this field is '1', the MCU is woken up by the wakeup signal<br>of the SleepTimer. Remote control function can be implemented<br>by the interrupt service routine of the MCU when the WAKEUP<br>signal occurs by adjusting the RTDLY value in the Sleep Timer<br>while either INT0 or INT1 is low. | R/W          | 0                     |

| 0    | P0AndSel       | When this field is set to '1', P0 and P0MSK are ORed per bit. The bits of the result value are to be ANed and then output to P1.7. This function is used to implement remote control function.                                                                                                                                                                                                                                                                                                                           | R/W          | 0                     |

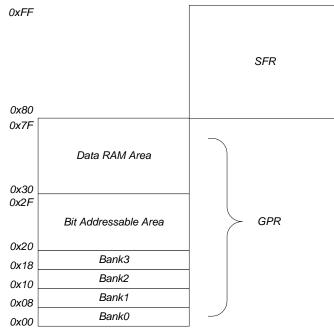

# **1.3 RESET**

The ZIC2410 should be reset to be operated. There are three kinds of reset sources. The first one is to use an external reset pin (RESET#). When applying a low signal to this pin for more than 1ms, ZIC2410 is reset. Second, ZIC2410 can be reset by an internal POR when it is powered up as using the internal Power-On-Reset (POR) block. Third, as a reset by the watchdog timer, a reset signal is generated when the internal counter of watchdog timer reaches a pre-set value.

| Parameter           | MIN | ТҮР  | MAX | UNIT |

|---------------------|-----|------|-----|------|

| 1.5V POR Release    |     | 1.18 |     | V    |

| 1.5V POR Hysteresis |     | 0.11 |     | V    |

# NOTE

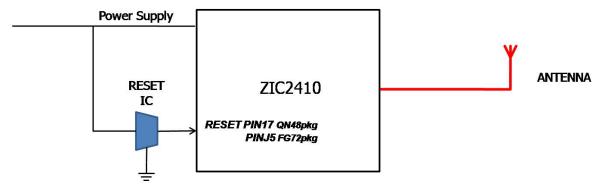

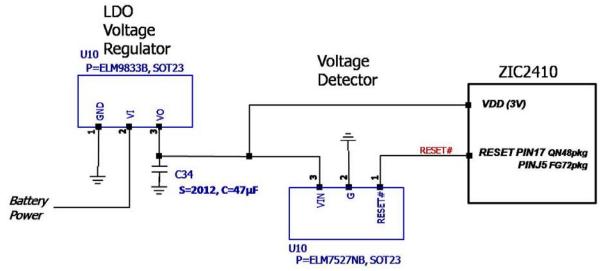

Reference circuit of ZIC2410 is as follows. When the ZIC2410 is operated below minimum operating voltage, a reset error will occur because of the unstable voltage. It is recommended to use an external reset IC to improve stability in low voltage conditions.

# [Application Circuit by adjusting RESET-IC]

#### [Reset Circuit by adjusting ELM7527NB]

Figure 7 – Reset Circuit Using ELM7527NB

# Checking the RESET-IC Circuit

- 1. In the application circuit of ZIC2410, please connect RESET# PIN to Pull-up register and should not connect it to capacitor.

- 2. When applying RESET-IC, detection voltage should be set over 1.9V.

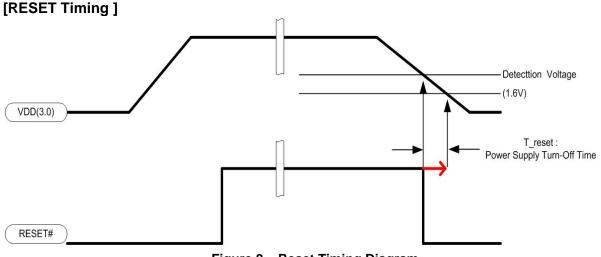

- 3. The interval (T\_reset) until from the time which reset signal by Reset IC has been adjusted to the time which the voltage of VDD (3.0) is dropped to 1.6V should be longer than 1ms.

- 4. T\_reset time is adjusted when modifying capacitor value connected to VDD (3.0).

# **1.4 CLOCK SOURCE**

The ZIC2410 can use either a 16MHz or a 19.2MHz crystal as the system clock source. An external 32.768 KHz crystal or the internal clock generated from internal the RCOSC is used for the Sleep Timer clock.

For the internal 8051 MCU Clock in the ZIC2410, either 8MHz or 16MHz can be used. When selecting the 8051 MCU Clock (8MHz, 16MHz), the CLKDIV0 register should be set as follows.

Please note the crystal oscillator input (XOSCI) can also be driven by a CMOS clock source.

# CLKDIV0 (OPERATING FREQUENCY CONTROL REGISTER, 0x22C3)

Table 5 – Clock Registers

| <u>Bit</u> | <u>Name</u> | <b>Descriptions</b>                                                                                                                                                                                                                | <u>R/W</u> | <u>Reset</u><br>Value |

|------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------|

| 7:0        | CLKDIV0     | This register is used to control the clock of the internal 8051 MCU. When this register is set to 0xFF, the clock is set to 8MHz; when set to 0x00, the clock is set to 16MHz. All other values except 0xFF and 0x00 are reserved. | R/W        | 0xFF                  |

# **1.5 INTERRUPT SCHEMES**

The program interrupt functions of the embedded MCU are similar to other microprocessors. When an interrupt occurs, the interrupt service routine at the corresponding vector address is executed. When the interrupt service routine process is completed, the program is resumed from the point of time at which the interrupt occurred. Interrupts can be initiated from the internal operation of the embedded microprocessor (e.g. the overflow of the timer count) or from an external signal.

The ZIC2410 has 13 interrupt sources. Table 6 describes the detailed information for each of the interrupt sources. The 'Interrupt Address' indicates the address where the interrupt service routine is located. The 'Interrupt Flag' is the bit that notifies the MCU that the corresponding interrupt has occurred. 'Interrupt Enable' is the bit which decides whether each interrupt has been enabled. 'Interrupt Priority' is the bit which decides the priority of the interrupt. The 'Interrupt Number' is the interrupt priority fixed by the hardware. That is, when two or more interrupts having the same 'Interrupt Priority' value, occur simultaneously, the lower 'Interrupt Number' is processed first.

| Interrupt     | Interrupt Type                               | Interrupt | Interrupt Flag | Interrupt     | Interrupt       |

|---------------|----------------------------------------------|-----------|----------------|---------------|-----------------|

| <u>Number</u> |                                              | Address   | <u></u>        | <u>Enable</u> | <u>Priority</u> |

| 0             | External Interrupt0                          | 0003H     | TCON.IE0       | IE.EX0        | IP.PX0          |

| 1             | Timer0 Interrupt                             | 000BH     | TCON.TF0       | IE.ET0        | IP.PT0          |

| 2             | External Interrupt1                          | 0013H     | TCON.IE1       | IE.EX1        | IP.PX1          |

| 3             | Timer1 Interrupt                             | 001BH     | TCON.TF1       | IE.ET1        | IP.PT1          |

| 4             | UART0 Interrupt (TX)<br>UART0 Interrupt (RX) | 0023H     | Note 1         | IE.ES0        | IP.PS0          |

| 7             | UART1Interrupt (TX)<br>UART1 Interrupt (RX)  | 003BH     | Note 1         | IE.ES1        | IP.PS1          |

| 8             | PHY Interrupt                                | 0043H     | EXIF.PHYIF     | EIE.RFIE      | EIP.RFIP        |

| 9             | Timer2 Interrupt                             | 004BH     | EXIF.T2IF      | EIE.T2IE      | EIP.T2IP        |

| 10            | AES Interrupt                                | 0053H     | EXIF.AESIF     | EIE.AESIE     | EIP.AESIP       |

| 11            | Timer3 Interrupt                             | 005BH     | EXIF.T3IF      | EIE.T3IE      | EIP.T3IP        |

| 12            | Sleep Timer Interrupt                        | 0063H     | EICON.RTCIF    | EIE.RTCIE     | EIP.RTCIP       |

| 13            | SPI Interrupt                                | 0068H     | Note 2         | EIE.SPIIE     | EIP.SPIIP       |

| 14            | Voice Interrupt                              | 0073H     | Note 3         | EIE.VCEIE     | EIP.VCEIP       |

#### Table 6 – Interrupt Descriptions

**Note 1:** In the case of a UART Interrupt, bit [0] of the IIR register (0x2502, 0x2512) in the UART block is used as a flag. Also, the Tx, Rx, Timeout, Line Status and Modern Status interrupts can be distinguished by bit [3:1] value. For more detailed information, refer to the UART0/1 description in Section 1.7.6.

**Note 2:** In the case of an SPI interrupt, there is another interrupt enable bit in the SPI register besides EIE.SPIIE. In order to enable an SPI interrupt, both SPIE in the SPCR (0x2540) register and EIE.SPIIE should be set to '1. SPIF in the SPSR (0x2541) register acts as an interrupt flag.

**Note 3:** In case of a Voice interrupt, there are interrupt enable registers and interrupt flag registers in the voice block. The interrupt enable register are VTFINTENA (0x2770), VRFINTENA (0x2771) and VDMINTENA (0x2772). The interrupt flag register are VTFINTVAL (0x2776), VRFINTVAL (0x2777), and VDMINTVAL (0x2778). There are 24 interrupt sources. When both an interrupt enable signal and an interrupt flag signal are set to '1,' voice interrupt is enabled.

# Table 7 – INTERRUPT Registers

| Bit                      | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                          | R/W           | <u>Reset</u> |  |  |  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|--|--|--|

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                          | <u></u>       | <u>Value</u> |  |  |  |

| The I<br>interr<br>the s | <b>IE (INTERRUPT ENABLE REGISTER, 0xA8)</b><br>The EA bit in the IE register is the global interrupt enable signal for all interrupts. In addition, each interrupt is masked by each interrupt enable bit. Therefore, in order to use an interrupt, both EA and the specific interrupt enable bit should be set to '1'. When the bit for each interrupt is '0', that interrupt is disabled. When the bit for each interrupt is (1', that interrupt is enabled) |                                                                                                                                                                          |               |              |  |  |  |

| interi                   | interrupt is disabled. When the bit for each interrupt is '1', that interrupt is enabled. Global interrupt enable                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                          |               |              |  |  |  |

| 7                        | EA                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>0: No interrupt will be acknowledged.</li> <li>1: Each interrupt source is individually enabled or disabled by setting its corresponding enable bit.</li> </ul> | R/W           | 0            |  |  |  |

| 6                        | ES1                                                                                                                                                                                                                                                                                                                                                                                                                                                            | UART1 interrupt enable 1: interrupt enabled.                                                                                                                             | R/W           | 0            |  |  |  |

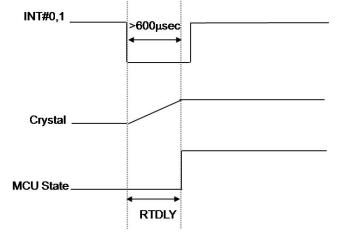

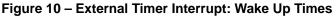

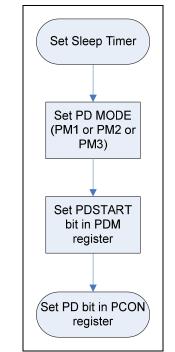

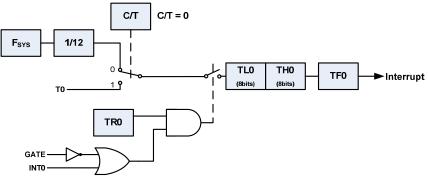

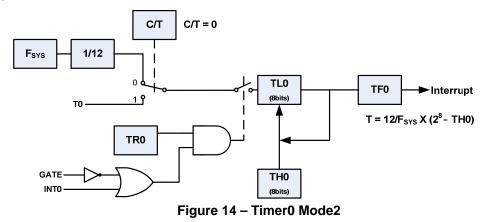

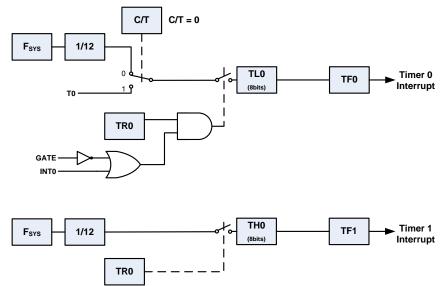

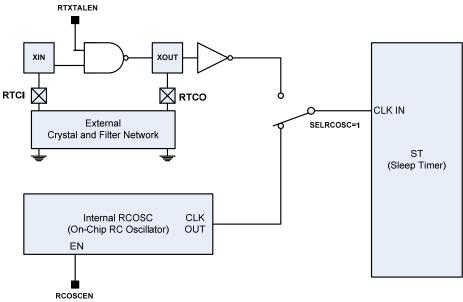

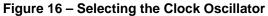

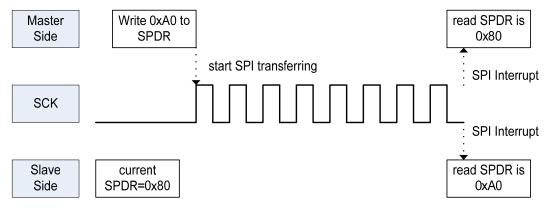

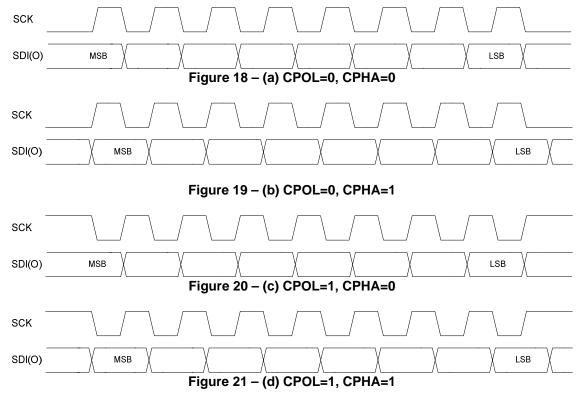

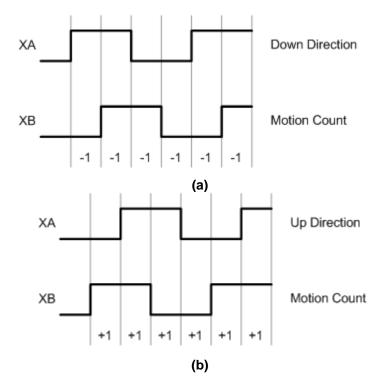

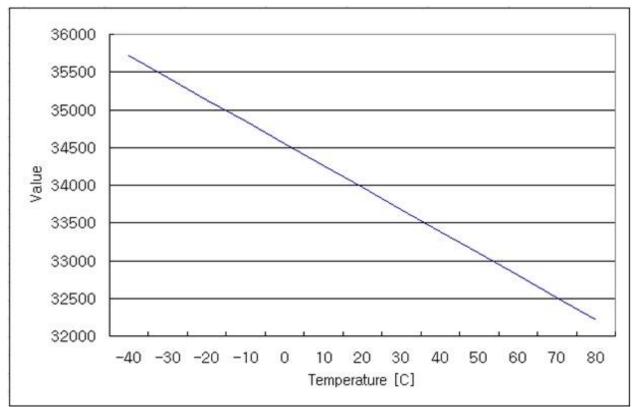

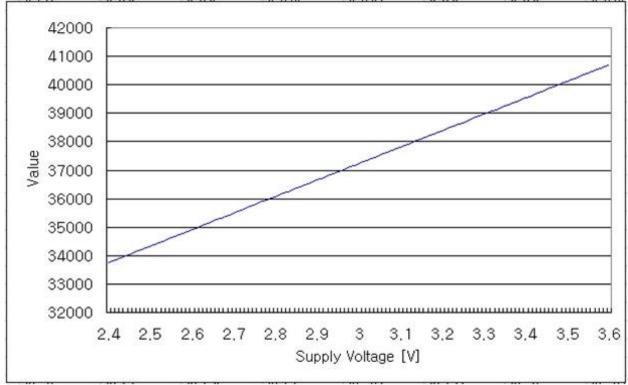

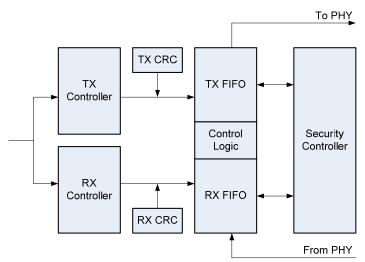

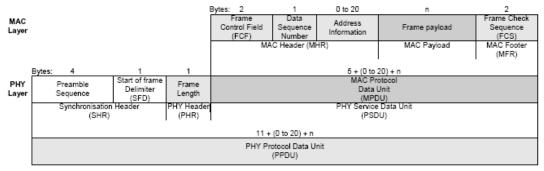

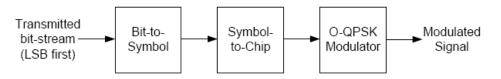

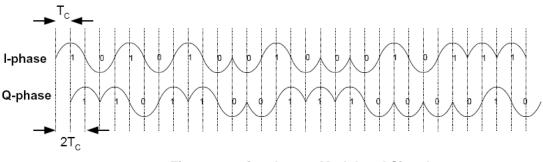

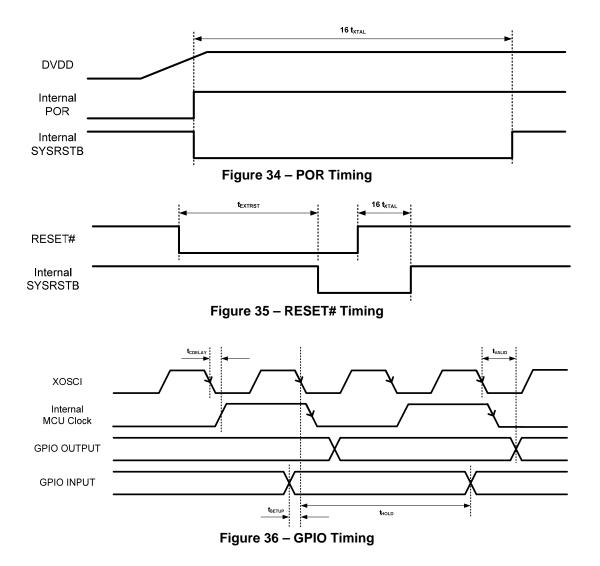

| 5                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reserved                                                                                                                                                                 |               | 0            |  |  |  |