# **Quad Channel Clock Translator**

#### **Features**

- Four independent OTN De-Synchronizers

- Excellent jitter performance of 180 fs rms in 12 kHz to 20 MHz band meets jitter requirements of 10G/40G and 100G PHYs

- Three programmable ultra-low jitter synthesizers generate frequencies from 1 Hz to 900 MHz.

- One programmable general purpose synthesizer generates any clock from 1 Hz to 180 MHz

- 6 differential (CML) or 12 single ended (CMOS) ultralow jitter outputs plus two general purpose CMOS outputs

- Accepts up to 10 LVPECL/LVDS/HCSL/LVCMOS inputs

#### **Ordering Information**

ZL30174LDG6\* 100 Pin aQFN Travs

\*Pb Free Tin/Silver/Copper

Package size: 10 x 10 mm -40°C to +85°C

- Up to four programmable digital PLLs/NCOs with loop bandwidth from 14 Hz to 470 Hz synchronize to any clock rate from 1 kHz to 900 MHz

- Automatic hitless reference switching and digital holdover on reference fail with initial holdover accuracy better than 10 ppb

# **Applications**

- OTN Transponders/Muxponeders

- **OTN Switches**

- **Test Equipment**

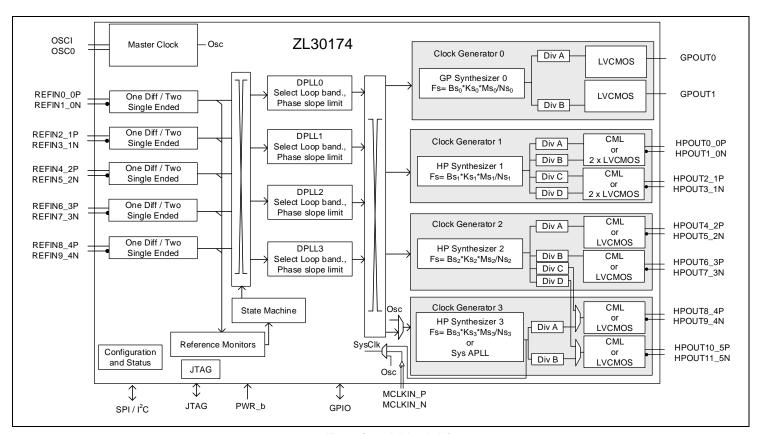

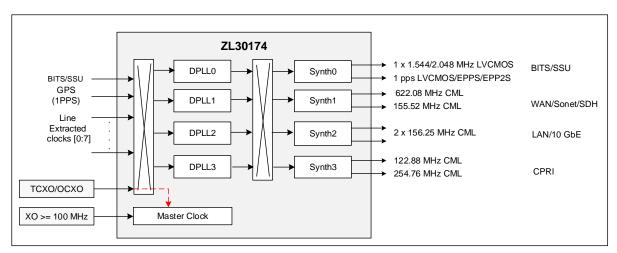

Figure 1. Functional Block Diagram

# **Table of Contents**

| 1    | Features         | 3                                      | 1         |

|------|------------------|----------------------------------------|-----------|

| 2    | <b>Applicat</b>  | ions                                   | 1         |

| Tab  | le of Cor        | ntents                                 | 2         |

| 3    | List of F        | igures                                 | 4         |

| 4    |                  | ables                                  |           |

| 5    |                  | List                                   |           |

| 5.1  |                  | eral features                          |           |

| 5.2  |                  | strical Clock Inputs                   |           |

| 5.3  |                  | ·                                      |           |

|      |                  | etrical Clock Engine                   |           |

| 5.4  |                  | etrical Clock Generation               |           |

| 6    |                  | nion Documentation                     |           |

| 7    |                  | ion Examples                           |           |

| 8    | _                | gram                                   |           |

| 9    | Pin Des          | criptions                              | 11        |

| 10   | Hard             | dware Functional Description           | 16        |

| 10.1 | 1 Inpu           | ıt References                          | 16        |

|      | 10.1.1           | Input Sources                          | 16        |

|      | 10.1.2           | 1                                      | 16        |

|      | 10.1.3           | 1 11                                   | 19        |

|      | 10.1.4           | '                                      | 19        |

| 10.2 |                  | , ,                                    | 24        |

|      | 10.2.1           | 1 ** * * * * * * * * * * * * * * * * * | 24        |

|      | 10.2.2<br>10.2.3 | - · · · · · · · · · · · · · · · · ·    | 24<br>24  |

|      | 10.2.3           | •                                      | 24<br>24  |

|      | 10.2.5           | ·                                      | 2-1<br>24 |

|      | 10.2.6           | ·                                      | <br>25    |

|      | 10.2.7           |                                        | 26        |

|      | 10.2.8           |                                        | 26        |

|      | 10.2.9           | ,                                      | 27        |

|      |                  | 3 - 1 3 - 1 3 - 1                      | 27        |

|      |                  |                                        | 28        |

|      | 10.2.12          | 3                                      | 28<br>29  |

|      | 10.2.13          | · · ·                                  | 29<br>31  |

|      | 10.2.15          | · · · · · · · · · · · · · · · · · · ·  | 32        |

| 10.3 |                  |                                        | 32        |

| 10.0 | 10.3.1           | •                                      | 32        |

|      | 10.3.2           |                                        | 33        |

| 10.4 |                  |                                        | 34        |

|      | 10.4.1           |                                        | 34        |

|      | 10.4.2           | , , , ,                                | 34        |

|      | 10.4.3           |                                        | 34        |

|      | 10.4.4           | · · · · · · · · · · · · · · · · · · ·  | 34        |

|      | 10.4.5           | · · · · · · · · · · · · · · · · · · ·  | 34        |

|      | 10.4.6           | ,                                      | 35        |

|      | 10.4.7<br>10.4.8 | · ·                                    | 36<br>36  |

| 10 ' |                  | ·                                      |           |

| 10.5 | 5 Sysi<br>10.5.1 |                                        | 39<br>39  |

|      | 10.0.1           | Master Clock Interface                 | J         |

|      | 10.5.2 Master Clock Frequency Selection 10.5.3 System PLL Bypass and Synthesizer 3 |                                                                                                                               |            |  |  |  |  |

|------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|

| 10.6 |                                                                                    | ver Supply                                                                                                                    | 41<br>42   |  |  |  |  |

|      | .6.1                                                                               | Power Up/Down Sequence                                                                                                        | 42         |  |  |  |  |

|      | .6.2                                                                               | Power Supply Filtering                                                                                                        | 43         |  |  |  |  |

| 10.  | .6.3                                                                               | Power Calculator                                                                                                              | 43         |  |  |  |  |

|      | .6.4                                                                               | Reset and Configuration Circuit                                                                                               | 44         |  |  |  |  |

|      |                                                                                    | VDD_DRI and VREG_OUT                                                                                                          | 44         |  |  |  |  |

| 11   |                                                                                    | figuration and Control                                                                                                        |            |  |  |  |  |

| 11.1 |                                                                                    | Configured Default Values on Power-Up                                                                                         |            |  |  |  |  |

| 11.2 | _                                                                                  | isters Configuration                                                                                                          |            |  |  |  |  |

|      | .2.1                                                                               | Input Reference Configuration DPLL Configuration                                                                              | 45         |  |  |  |  |

|      |                                                                                    | Output Multiplexer Configuration                                                                                              | 46<br>46   |  |  |  |  |

|      |                                                                                    | Synthesizer Configuration                                                                                                     | 46         |  |  |  |  |

|      | .2.5                                                                               | Output Dividers and Output Phase Offset (skew) Configuration                                                                  | 46         |  |  |  |  |

| 11.  | .2.6                                                                               | Output Drivers Configuration                                                                                                  | 46         |  |  |  |  |

| 11.3 | GPI                                                                                | O Configuration                                                                                                               | 47         |  |  |  |  |

| 11.4 | Rea                                                                                | dy Status                                                                                                                     | 47         |  |  |  |  |

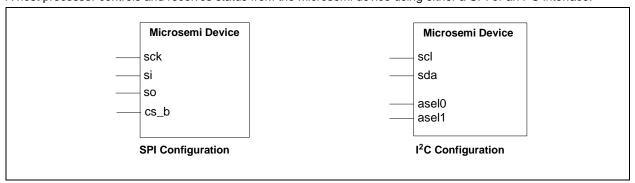

| 12   | Hos                                                                                | t Interface                                                                                                                   | 48         |  |  |  |  |

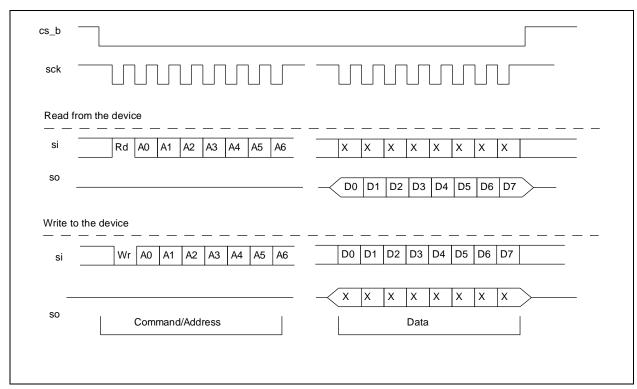

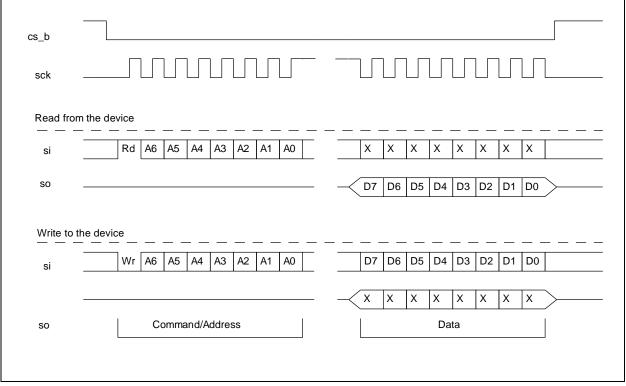

| 12.1 | Seri                                                                               | al Peripheral Interface                                                                                                       | 48         |  |  |  |  |

|      |                                                                                    | Least Significant Bit (LSb) First Transmission Mode                                                                           | 49         |  |  |  |  |

|      | .1.2                                                                               | Most Significant Bit (MSb) First Transmission Mode                                                                            | 50         |  |  |  |  |

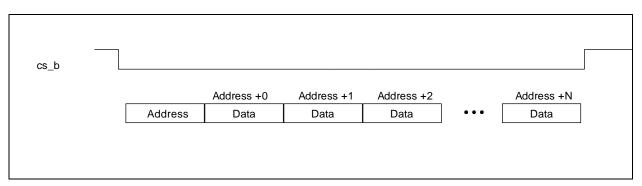

|      | .1.3                                                                               | SPI Burst Mode Operation                                                                                                      | 50         |  |  |  |  |

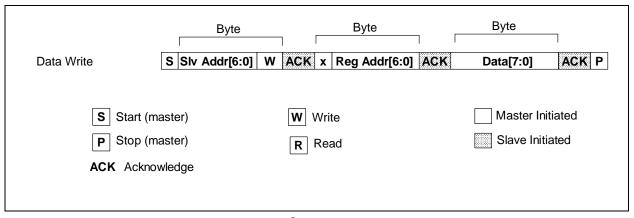

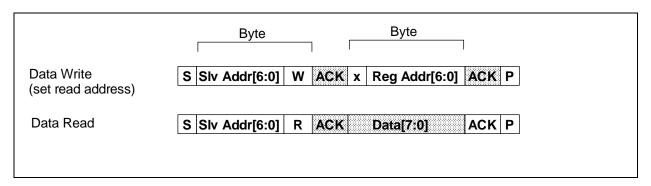

| 12.2 |                                                                                    | nterface                                                                                                                      |            |  |  |  |  |

| 13   | _                                                                                  | ister Map                                                                                                                     |            |  |  |  |  |

| 13.1 |                                                                                    | i-byte Register Values                                                                                                        |            |  |  |  |  |

| _    | .1.1                                                                               | Time between two write accesses to the same register Time after change to state machine or system-clock related configuration | 53<br>53   |  |  |  |  |

| 13.2 |                                                                                    | ky Read                                                                                                                       |            |  |  |  |  |

| _    |                                                                                    | ister Map List Summary                                                                                                        |            |  |  |  |  |

| 13.3 | -                                                                                  | ·                                                                                                                             |            |  |  |  |  |

| 13.4 | . кед<br>.4.1                                                                      | ister List                                                                                                                    | 62         |  |  |  |  |

|      |                                                                                    | Register List (Page 1)                                                                                                        | 64         |  |  |  |  |

|      |                                                                                    | Register List (Page 2)                                                                                                        | 77         |  |  |  |  |

|      | .4.4                                                                               | Register List (Page 3)                                                                                                        | 83         |  |  |  |  |

|      |                                                                                    | Register List (Page 4)                                                                                                        | 92         |  |  |  |  |

|      | .4.6                                                                               | Register List (Page 5)                                                                                                        | 100        |  |  |  |  |

|      | .4.7<br>.4.8                                                                       | Register List (Page 6) Register List (Page 10)                                                                                | 101<br>107 |  |  |  |  |

|      | .4.9                                                                               | Register List (Page 11)                                                                                                       | 109        |  |  |  |  |

|      |                                                                                    | Register List (Page 12                                                                                                        | 116        |  |  |  |  |

| 13.  | .4.11                                                                              | Register List (Page 13)                                                                                                       | 125        |  |  |  |  |

| 14   | AC a                                                                               | and DC Electrical Characteristics                                                                                             | 134        |  |  |  |  |

| 14.1 | Abs                                                                                | olute Maximum Ratings                                                                                                         | 134        |  |  |  |  |

| 14.2 | Rec                                                                                | Recommended Operating Conditions                                                                                              |            |  |  |  |  |

| 14.3 | DC                                                                                 | Electrical Characteristics                                                                                                    | 135        |  |  |  |  |

| 14.4 | AC I                                                                               | Electrical Characteristics                                                                                                    | 151        |  |  |  |  |

| 15   |                                                                                    | ormance Characteristics                                                                                                       |            |  |  |  |  |

| 15.1 | 15.1 Output Clocks Jitter Generation                                               |                                                                                                                               |            |  |  |  |  |

| 15.2 |                                                                                    | L Performance Characteristics                                                                                                 |            |  |  |  |  |

| 15.3 |                                                                                    | kage thermal characteristics                                                                                                  |            |  |  |  |  |

| 16   |                                                                                    | nge History                                                                                                                   |            |  |  |  |  |

| -    |                                                                                    | U                                                                                                                             |            |  |  |  |  |

17 18

| Acronyms        | 171 |

|-----------------|-----|

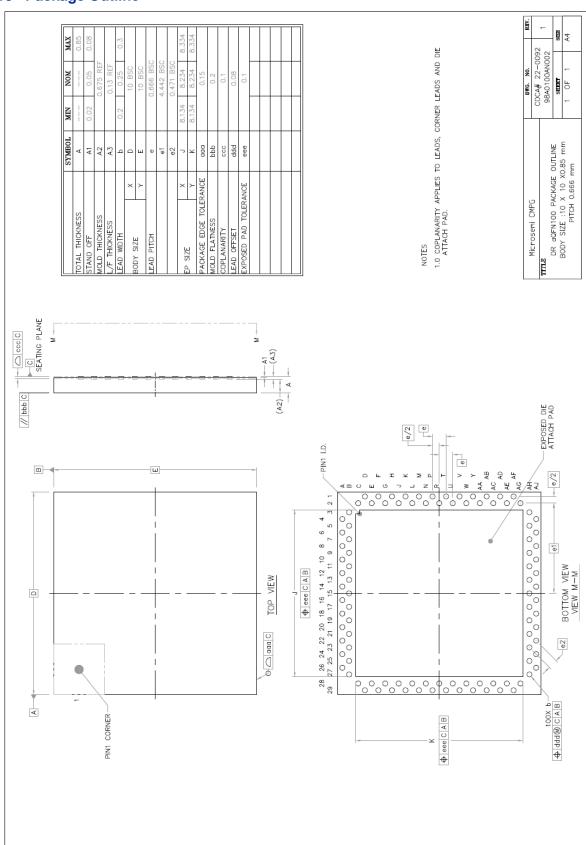

| Package Outline | 172 |

ZL30174

| 3 LIST OF F | gures                                                                                             |     |

|-------------|---------------------------------------------------------------------------------------------------|-----|

| Figure 1.   | Functional Block Diagram                                                                          | 1   |

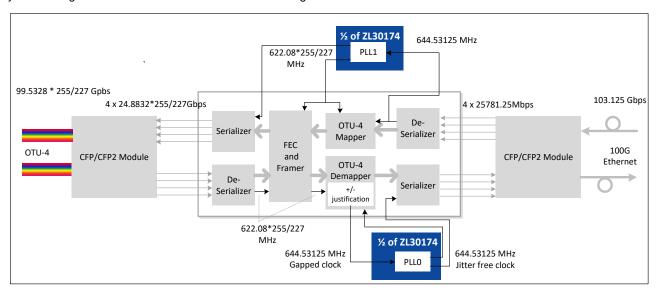

| Figure 2.   | OTU-4 Transponder                                                                                 | 9   |

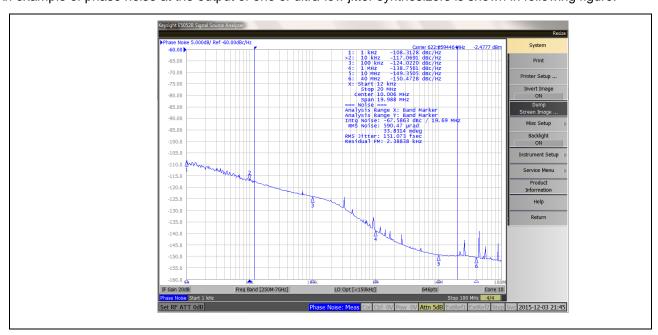

| Figure 3.   | Phase noise plot for 622.08MHz output clock with 200MHz XO ( 151fs jitter in 12kHz to 20MHz band) | 9   |

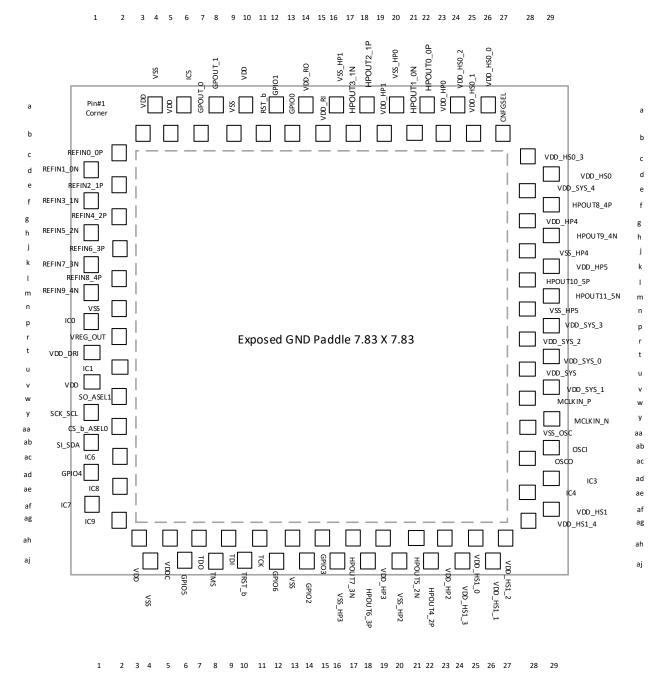

| Figure 4.   | Pin Diagram                                                                                       | 10  |

| Figure 5.   | Stratum 3/G.8262 Option I Frequency Acceptance and Rejection Ranges                               | 17  |

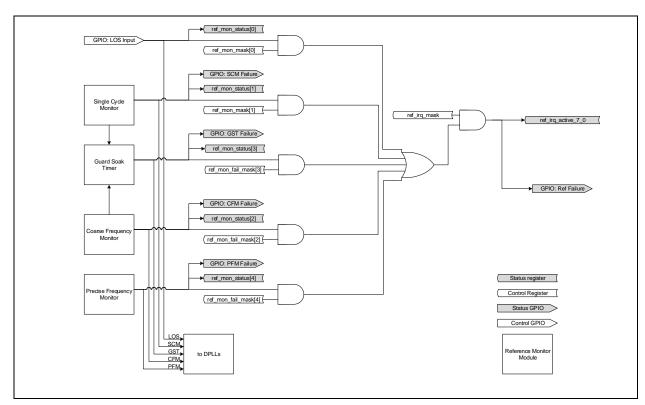

| Figure 6.   | Reference monitoring interrupt generation                                                         | 19  |

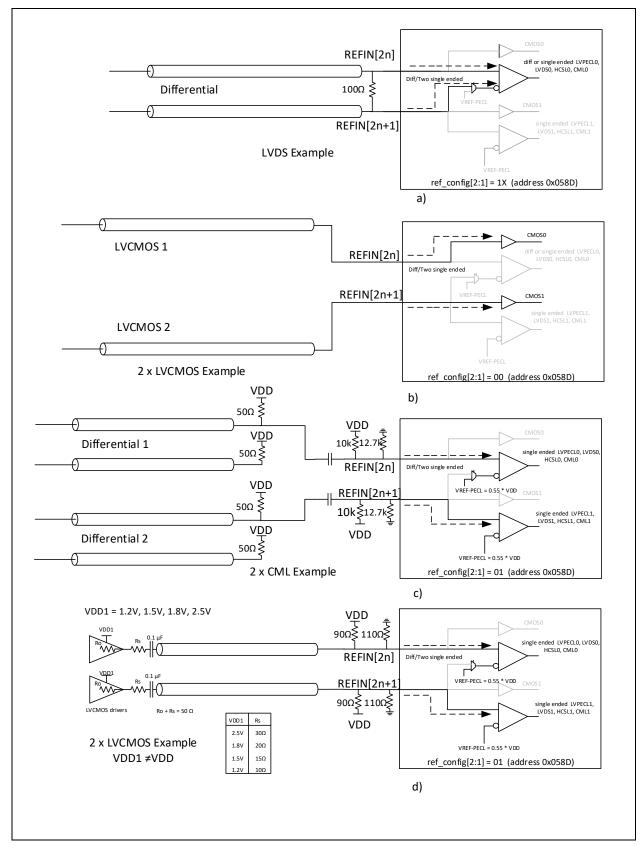

| Figure 7.   | Input buffers & termination                                                                       | 21  |

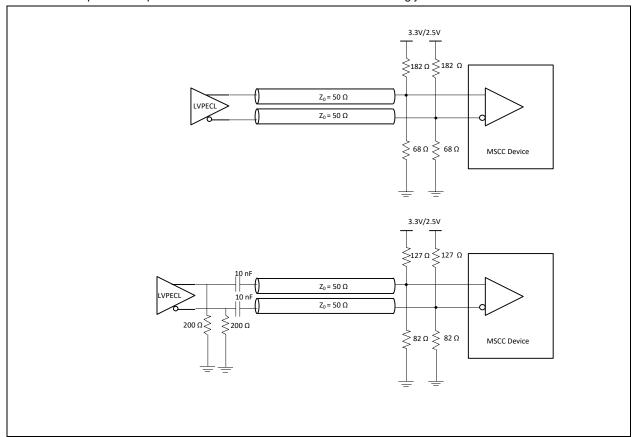

| Figure 8.   | Differential DC and AC Coupled LVPECL Termination                                                 | 22  |

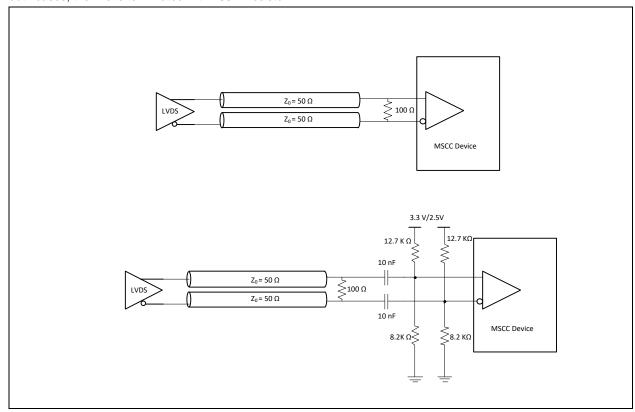

| Figure 9.   | Differential DC and AC Coupled LVDS Termination                                                   | 23  |

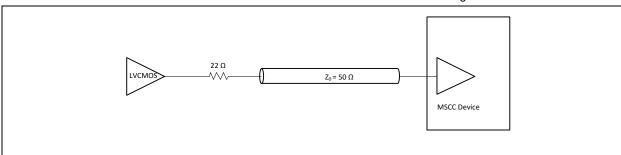

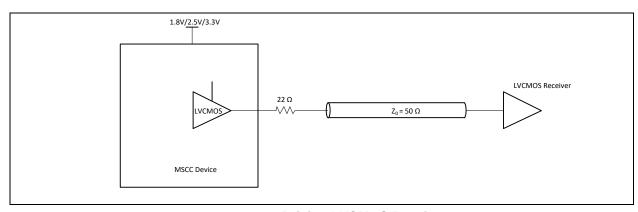

| Figure 10.  | Single Ended LVCMOS Termination                                                                   | 23  |

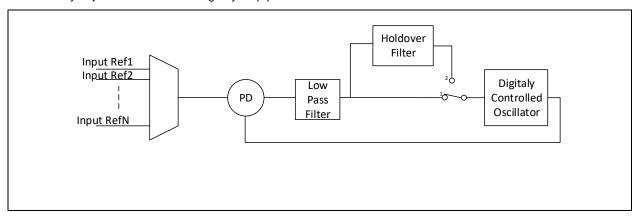

| Figure 11.  | Simplified block diagram of the holdover filter                                                   | 29  |

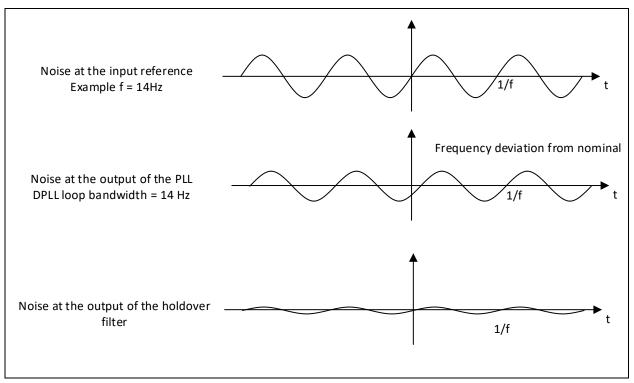

| Figure 12.  | Benefits of holdover filter                                                                       | 30  |

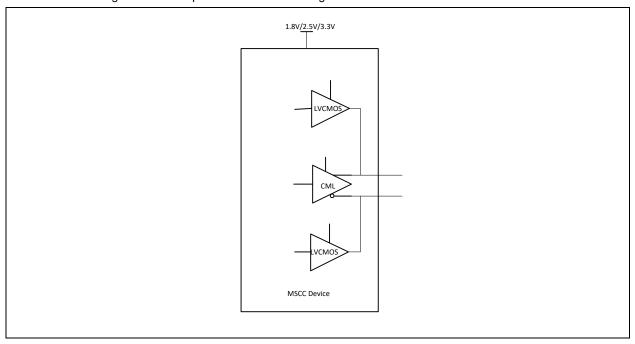

| Figure 13.  | Functional block diagram of the output buffer                                                     | 36  |

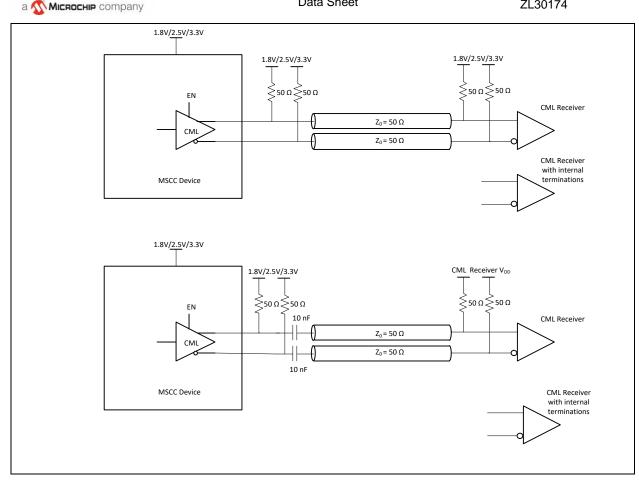

| Figure 14.  | Driving CML Recevier                                                                              | 37  |

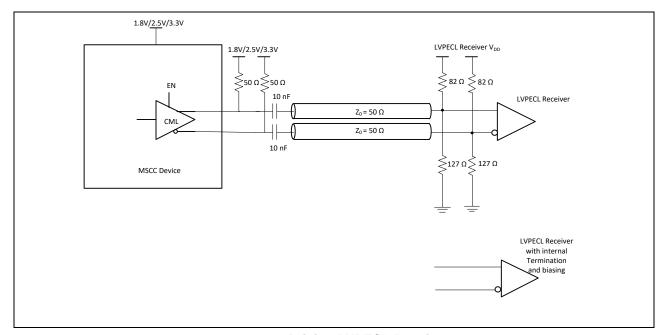

| Figure 15.  | Driving LVPECL Receiver                                                                           | 37  |

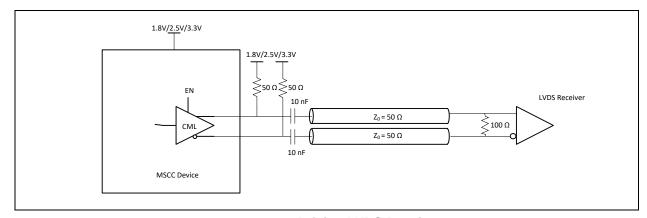

| Figure 16.  | Driving LVDS Receiver                                                                             | 38  |

| Figure 17.  | Driving LVCMOS Receiver                                                                           | 38  |

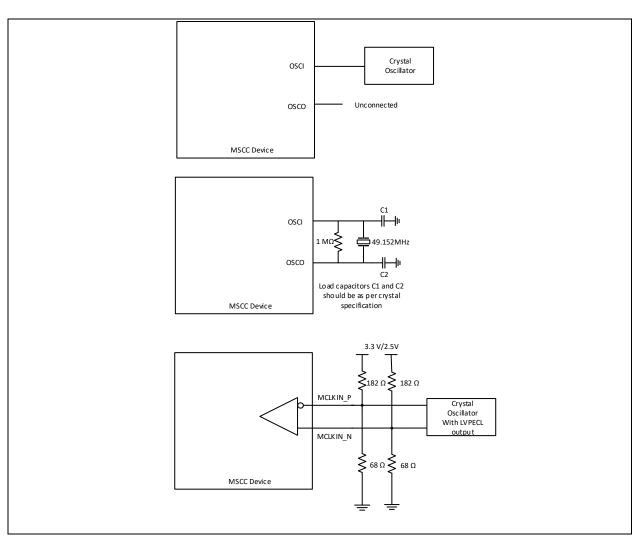

| Figure 18.  | Master Clock Oscillator                                                                           | 39  |

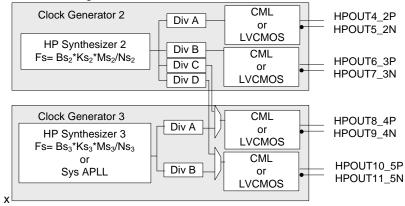

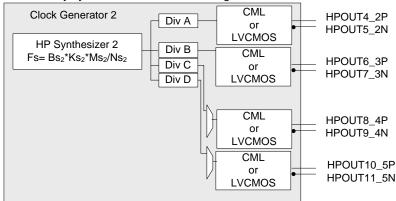

| Figure 19.  | HPOUT[8:9] MUX                                                                                    | 41  |

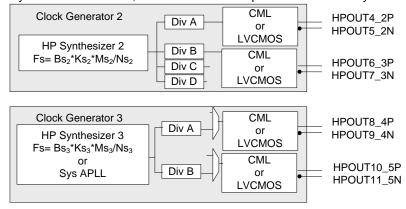

| Figure 20.  | HPOUT[8:9] Driven by Synthesizer 2 (System PLL Bypass FALSE)                                      | 41  |

| Figure 21.  | HPOUT[8:9] Driven by Synthesizer 3 (System PLL Bypass TRUE)                                       | 41  |

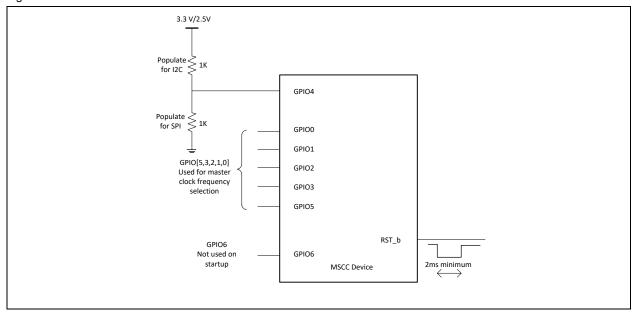

| Figure 22.  | Typical Configuration and Power-Up Reset Circuit                                                  | 44  |

| Figure 24.  | Selection of pre-configured values                                                                | 45  |

| Figure 25.  | Selection of pre-configured values with FPGA/CPU                                                  | 45  |

| Figure 26.  | Serial Interface Configuration                                                                    | 48  |

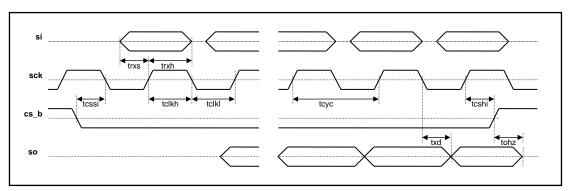

| Figure 27.  | Serial Peripheral Interface Functional Waveform – LSB First Mode                                  |     |

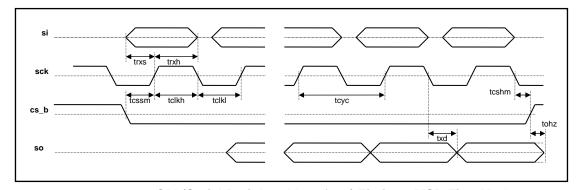

| Figure 28.  | Serial Peripheral Interface Functional Waveform – MSB First Mode                                  | 50  |

| Figure 29.  | Example of the Burst Mode Operation                                                               | 50  |

| Figure 30.  | I <sup>2</sup> C Data Write Protocol                                                              | 51  |

| Figure 31.  | I <sup>2</sup> C Data Read Protocol                                                               | 51  |

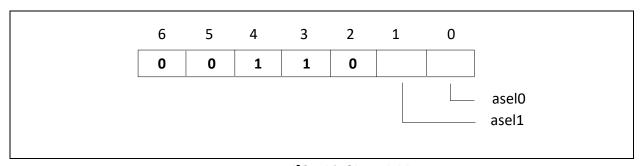

| Figure 32.  | I <sup>2</sup> C 7 bit Slave Address                                                              | 51  |

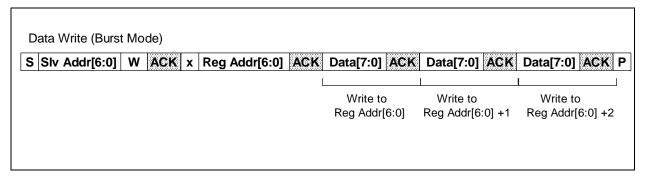

| Figure 33.  | I <sup>2</sup> C Data Write Burst Mode                                                            | 52  |

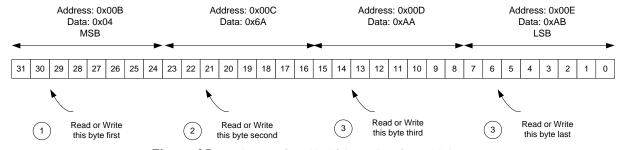

| Figure 34.  | Accessing Multi-byte Register Values                                                              | 53  |

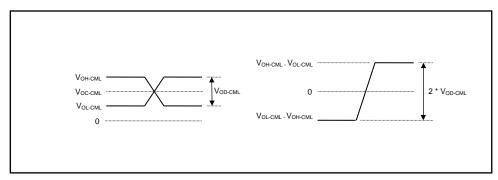

| Figure 35.  | HPOUT_DIFF (CML) Output                                                                           | 137 |

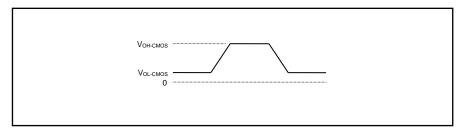

| Figure 36.  | HPOUT & GPOUT (CMOS) Output                                                                       | 141 |

| Figure 37.  | HPOUT_DIFF (CML) DC Output Level                                                                  | 148 |

| Figure 38.  | HPOUT and GPOUT (CMOS) Output Termination and DC Output Level                                     | 149 |

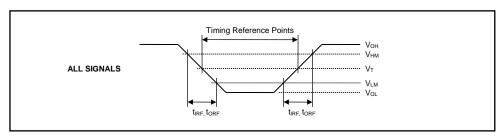

| Figure 39.  | Timing Parameter Measurement Voltage Levels                                                       |     |

| Figure 40.  | Reference Input Timing                                                                            | 152 |

| Figure 41.  | Reference Input to Output Clock Timing                                                            | 153 |

| Figure 42.  | Output to Output Clock Timing                                                                     |     |

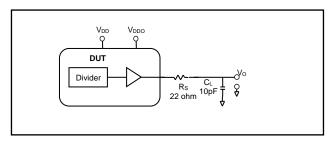

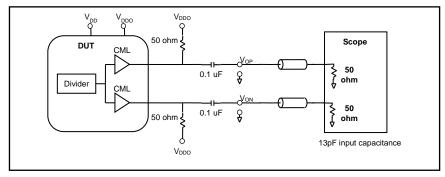

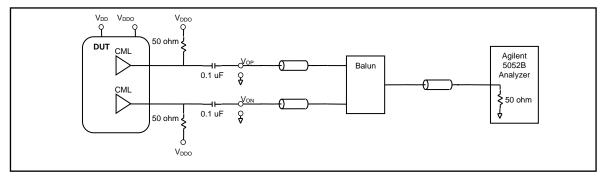

| Figure 43.  | HPOUT_DIFF Output tr and tf Measurement Setup                                                     | 154 |

| Figure 44.  | HPOUT_DIFF Output Duty Cycle Measurement Setup                                                    |     |

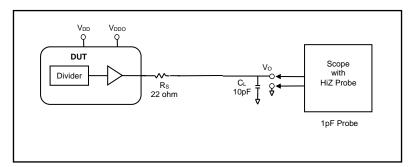

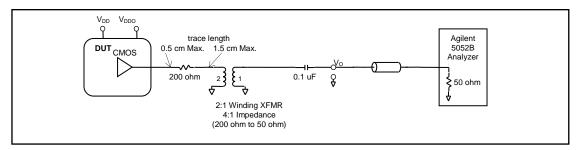

| Figure 45.  | HPOUT and GPOUT Output tr, tf & Duty Cycle Measurement Setup                                      |     |

| Figure 46.  | SPI (Serial Peripheral Interface) Timing - LSB First Mode                                         | 156 |

| Figure 47.  | SPI (Serial Peripheral Interface) Timing - MSB First Mode                                         | 156 |

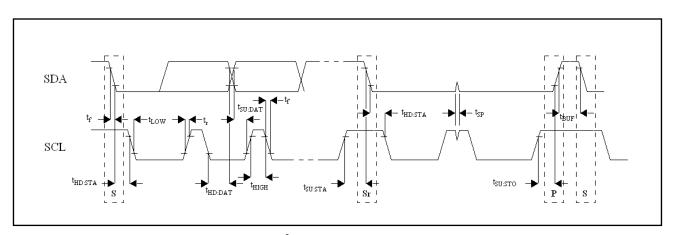

| Figure 48.  | I <sup>2</sup> C Serial Microport Timing                                                          |     |

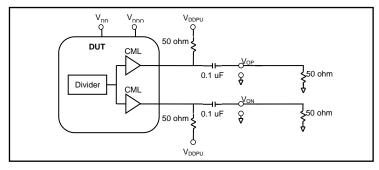

| Figure 49.  | HPOUT_DIFF (CML) Output Jitter Test Circuit                                                       |     |

| Figure 50.  | HPOUT (LVCMOS) and GPOUT (LVCMOS) Output Jitter Test Circuit                                      | 168 |

|             |                                                                                                   |     |

# 4 List of Tables

| Table $1 \cdot Pin$ Descriptions                                                                         | 11  |

|----------------------------------------------------------------------------------------------------------|-----|

| Table 2 · DPLL Status Indicators                                                                         | 26  |

| Table 3 · GPIO Master Clock Selection                                                                    | 40  |

| Table 4 · Serial Interface Selection                                                                     | 48  |

| Table 5 · Register Map (Page 0)                                                                          |     |

| Table 6 · Register Map (Page 1)                                                                          | 55  |

| Table 7 · Register Map (Page 2)                                                                          | 56  |

| Table 8 · Register Map (Page 3)                                                                          | 57  |

| Table 9 · Register Map (Page 4)                                                                          | 58  |

| Table 10 · Register Map (Page 5)                                                                         |     |

| Table 11 · Register Map (Page 6)                                                                         | 58  |

| Table 12 · Register Map (Page 10)                                                                        |     |

| Table 13 · Register Map (Page 11)                                                                        | 59  |

| Table 14 · Register Map (Page 12)                                                                        | 59  |

| Table 15 · Register Map (Page 13)                                                                        |     |

| Table 16 · Absolute Maximum Ratings*                                                                     |     |

| Table 17 · Recommended Operating Conditions*                                                             |     |

| Table 18 · DC Electrical Characteristics* - Current – Core                                               |     |

| Table 19 · DC Electrical Characteristics* - Current – Core + Synthesizers 3:1                            |     |

| Table 20 · DC Electrical Characteristics* - Current - Core + Synthesizer 1 + HPOUT DIFF[1:0] Outputs     |     |

| Table 21 · DC Electrical Characteristics* - Current - Core + Synthesizer 2 + HPOUT_DIFF[5:2] Outputs     |     |

| Table 22 · DC Electrical Characteristics* - Current - Core + Synthesizer 3 + HPOUT_DIFF[5:4] Outputs     |     |

| Table 23 · DC Electrical Characteristics* - Current - Core + Synthesizer 3:1 + HPOUT_DIFF[5:0] Outputs   |     |

| Table 24 · DC Electrical Characteristics* - Current - Core + Synthesizer 1 + HPOUT[3:0] Outputs          |     |

| Table 25 · DC Electrical Characteristics* - Current - Core + Synthesizer 2 + HPOUT[11:4] Outputs         |     |

| Table $26 \cdot DC$ Electrical Characteristics* - Current - Core + Synthesizer 3 + HPOUT[11:8] Outputs   |     |

| Table 27 · DC Electrical Characteristics* - Current - Core + Synthesizer 3:1 + HPOUT[11:0] Outputs       |     |

| Table 28 · DC Electrical Characteristics* - Current - Core + Synthesizer 0 + GPOUT[1:0] Outputs          |     |

| Table 29 · DC Electrical Characteristics* - Current - Core + Synthesizer 3:0 + HPOUT[11:0] + GPOUT[1:0]  |     |

| Table 30 · DC Electrical Characteristics* - Reference Inputs                                             |     |

| Table 31 · DC Electrical Characteristics* - Other Inputs and IO (Bi-directional)                         |     |

| Table 32 · DC Electrical Characteristics* - HPOUT DIFF Outputs                                           |     |

| Table 33 · DC Electrical Characteristics* - HPOUT and GPOUT Outputs                                      |     |

| Table 34 · DC Electrical Characteristics* - Other Outputs and IO (Bi-directional)                        |     |

| Table 35 · AC Electrical Characteristics* - Output Timing Parameters Measurement Voltage Levels          |     |

| Table 36 · AC Electrical Characteristics* - Input Timing                                                 |     |

| Table 37 · AC Electrical Characteristics* - REF Input to HPOUT_DIFF, HPOUT and GPOUT Output Clock Timing |     |

| Table 38 · AC Electrical Characteristics* - HPOUT DIFF Output Timing                                     |     |

| Table 39 · AC Electrical Characteristics* - HPOUT and GPOUT Output Timing                                |     |

| Table 40 · AC Electrical Characteristics* - SPI (Serial Peripheral Interface) Timing                     |     |

| Table 41 · AC Electrical Characteristics* - I <sup>2</sup> C Serial Microport Timing                     |     |

| Table 42 · Output Clocks Jitter Generation* - HPOUT_DIFF[0:1] (CML) with 114.285MHz XO                   |     |

| Table 43 · Output Clocks Jitter Generation* - HPOUT_DIFF[2:3] (CML) with 114.285MHz XO                   |     |

| Table 44 · Output Clocks Jitter Generation* - HPOUT_DIFF[4:5] (CML) with 114.285MHz XO                   |     |

| Table 45 · Output Clocks Jitter Generation* - HPOUT_DIFF[0:1] (CML) with 49.152MHz XO                    |     |

| Table 46 · Output Clocks Jitter Generation* - HPOUT_DIFF[2:3] (CML) with 49.152MHz XO                    |     |

| Table 47 · Output Clocks Jitter Generation* - HPOUT_DIFF[4:5] (CML) with 49.152MHz XO                    |     |

| Table 48 · Output Clocks Jitter Generation* - HPOUT_DIFF[0:1] (CML) with 49.152/MHz XO                   |     |

|                                                                                                          |     |

| Table 49 · Output Clocks Jitter Generation* - HPOUT_DIFF[2:3] (CML) with 24.576MHz XO                    |     |

| Table 50 · Output Clocks Jitter Generation* - HPOUT_DIFF[4:5] (CML) with 24.576MHz XO                    |     |

| Table 51 · Output Clocks Jitter Generation* - HPOUT (LVCMOS) Output Clock Timing                         |     |

| Table 52 · Output Clocks Jitter Generation* - GPOUT (LVCMOS) Output Clock Timing                         | 16/ |

| Table 53 · DPLL Performance Characteristics* | 168 |

|----------------------------------------------|-----|

| Table 54 · Package Thermal Characteristics   | 169 |

#### 5 Feature List

#### 5.1 General features

- Four independent clock channels

- Operates from a single crystal resonator or clock oscillator

- o Supports split XO mode for low-frequency stability TCXO/OCXO with ultra-low jitter clock outputs

- Configurable from SPI/I2C bus or from pre-configured flash memory

# 5.2 Electrical Clock Inputs

- Accepts up to 10 LVCMOS or 5 LVDS/HCSL/LVPECL/CML differential inputs

- Frequencies from 1 kHz to 180 MHz for LVCMOS

- Frequencies from 1 kHz to 900 MHz for LVDS/HCSL/LVPECL/CML

- Flexible input reference monitoring automatically disqualifies references based on frequency and phase irregularities.

- Each input reference has its own set of monitors which can be independently programmed.

- Loss of signal (LOS)

- Single Cycle Monitor (Triggers on glitches or variation in duty-cycle)

- Coarse Frequency Monitor

- Precise Frequency Monitor

- Programmable phase slope limiting down to 1 ns/s

- Locks to gapped clocks

#### 5.3 Electrical Clock Engine

- Digital PLLs filter jitter from 14Hz up to 470 Hz

- Multiple modes of operation

- Freerun

- Forced holdover

- o Forced reference

- Automatic

- NCO

- Internal state machine automatically controls state

- Locked

- Acquiring

- Holdover

- Automatic hitless reference switching and digital holdover on reference fail

- Programmable bandwidth

- Programmable damping & phase gain (gain peaking)

- Programmable lock and fast lock options

- Support for fast lock with lock times in seconds

- Support for hitless reference switching with typical performance 0.6 ns

- Holdover better than 1ppb with post holdover filter. Without the post holdover filter the initial holdover accuracy is better than 10ppb.

- Full rate conversion between input and output clock frequencies

#### 5.4 Electrical Clock Generation

- Four programmable synthesizers

- Precision Synthesizers

- Each ultra-low jitter output can be independently set to be differential (CML) or two CMOS

- Six CML outputs

- Generate clock rates from 1 Hz to 900 MHz

- Jitter performance of 180 fs rms (12 kHz 20 MHz)

- Meets OC-192, STM-64, 1 GbE & 10 GbE interface jitter requirements

- o Twelve LVCMOS outputs

- Generate clock rates from 1 Hz to 180 MHz

- Jitter performance of 290 fs rms (12 kHz 20 MHz)

- General Synthesizer

- o Two LVCMOS outputs

- Generate clock rates from 1 Hz to 180 MHz

- Jitter performance of 17 ps rms (12 kHz 20 MHz

- Programmable output advancement to accommodate trace delays or compensate for system routing paths

- Each output has its own power supply pin which can be hooked to 3.3V, 2.5V or 1.8V supplies. Outputs may be disabled to save power

#### 6 Companion Documentation

#### **Application Notes**

- ZLAN-442 Crystals and Oscillators for Next Generation Timing Solutions

- ZLAN-620 Precision Input-Output Alignment Process

- ZLAN-599 Jitter Measurements

- ZLAN-600 Cyle-to-Cycle & Periodic Jitter (PCle Applications)

- ZLAN-517 Power Supply Decoupling and Layout Guidelines

- ZLAN-527 Assembly and PCB Layout Guidelines for DR aQFN100 Package

### Evaluation & Demonstration Board (SyncE and clock input-output focused)

- ZLE30174 EVB (with schematic)

- ZLE30174 GUI

- o Windows register configuration tool

- o Generates Flash image configuration file

- o Generates raw register list configuration file

- Includes useful power calculator for desired PLL configuration

# 7 Application Examples

ZL30174 is multifunctional device which can be used in many OTN applications. It provides three independent PLL channels which can synchronize to any input frequency from 1KHz up to 900MHz. ZL30174 can generate frequencies from 1Hz up to 180MHz for LVCMOS and up to 900MHz for CML outputs. Each channel is comprised of a DPLL and a Synthesizer.

ZL30174 with its three ultra-low jitter channels can be used in OTN Transponder OTU-4 applications as shown in Figure 4. To simplify the block diagram ZL30174 is split into two blocks each containing one PLL. Each PLL here comprises of DPLL with sub 300Hz loop bandwidth as required by OTN specs and a Synthesizer used to generate required frequency with ultra-low jitter required by Serializers. The third ultra-low jitter synthesizer is used to generate system clock.

Figure 2 shows one channel (PLL0) used as De-Synchronizer to filter gapped OTN line clock. The gapped clock is generated in demapper justification block by removing pulses from the extracted OTN line clock. The gapped clock needs to be cleaned from jitter before it can be used to drive 100G Ethernet CAUI Serializers. The second PLL (PLL1) is used to drive OTN line. It can be set in a free run mode where the clock is synchronized to free run crystal oscillator used as ZL30174 master clock or the OTN line can be synchronized to 100G client by synchronizing PLL1 to the Ethernet clock as shown in Figure 2.

Figure 2. OTU-4 Transponder

An example of phase noise at the output of one of ultra-low jitter synthesizers is shown in following figure.

Figure 3. Phase noise plot for 622.08MHz output clock with 200MHz XO (151fs jitter in 12kHz to 20MHz band)

ZL30174

# **Pin Diagram**

Microsemi

MICROCHIP company

The device is packaged in a 10x10mm 100-pin aQFN.

Figure 4. Pin Diagram

ZL30174

# 9 Pin Descriptions

All device inputs and outputs are LVCMOS unless described otherwise. The Type column uses the following symbols: I-input,  $I_{PU}-input$  with  $50k\Omega$  internal pull-up resistor, O-output, A-analog, P-power supply pin. All GPIO and SPI/I<sup>2</sup>C interface pins have Schmitt-trigger inputs and have output drivers that can be disabled (high impedance).

Table 1 - Pin Descriptions

|                                                                                      | Table 1 - Pin Descriptions                                                                                                               |     |                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| #                                                                                    | Name                                                                                                                                     | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Input Refe                                                                           | nput Reference                                                                                                                           |     |                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| C2<br>D1<br>E2<br>F1<br>G2<br>H1<br>J2<br>K1<br>L2                                   | REFINO_0P<br>REFIN1_0N<br>REFIN2_1P<br>REFIN3_1N<br>REFIN4_2P<br>REFIN5_2N<br>REFIN6_3P<br>REFIN7_3N<br>REFIN8_4P<br>REFIN9_4N           | I   | Input References 0 to 9 (LVCMOS, LVDS, LVPECL, CML, HCSL). These input references can accept up to ten single ended or up to five differential input signal sources used for synchronization.  Each input pair can be programmed to be a differential input or two single ended inputs.  Input frequency range for LVPECL, LVDS, HCSL, CML is from 1 kHz to 900 MHz  Input frequency range for LVCMOS is from 1 kHz to 180 MHz. |  |  |  |  |

| Output Clo                                                                           | ocks                                                                                                                                     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| A22<br>B21<br>A18<br>B17<br>AJ22<br>AH21<br>AJ18<br>AH17<br>F29<br>H29<br>L28<br>M29 | HPOUT0_0P HPOUT1_0N HPOUT2_1P HPOUT3_1N HPOUT4_2P HPOUT5_2N HPOUT6_3P HPOUT7_3N HPOUT8_4P HPOUT9_4N HPOUT10_5P HPOUT11_5N  GPOUT0 GPOUT1 | 0   | High Performance (Ultra Low Jitter) Outputs 0 to 11 (CML or LVCMOS)  Each output pair can be configured to be CML differential output or two independent LVCMOS outputs.  CML output frequency range is from 1 Hz to 900 MHz.  LVCMOS output frequency range is from 1 Hz to 180 MHz  General Purpose Outputs 0 to 1 (LVCMOS).  LVCMOS output frequency range is from 1 Hz to 180 MHz                                           |  |  |  |  |

|                                                                                      |                                                                                                                                          |     |                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Control ar                                                                           | nd Status                                                                                                                                | T   |                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| B11                                                                                  | RST_b                                                                                                                                    | I   | <b>Power-on Reset.</b> A logic low at this input resets the device. To ensure proper operation, the device must be reset after power-up. The RST_b pin should be held low for 2 ms. This pin is internally pulled-up to V <sub>DD</sub> . User can access device registers either 500 ms after RST_b goes high, or after bit 7 in register at address 0x00 goes high which can be determined by polling address 0x00.           |  |  |  |  |

| 1                                                |                                                             |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                              |

|--------------------------------------------------|-------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B13<br>A12<br>AJ14<br>AH15<br>AD1<br>AJ6<br>AJ12 | GPIO0<br>GPIO1<br>GPIO2<br>GPIO3<br>GPIO4<br>GPIO5<br>GPIO6 | I/O | managed by the internal proce Recommended usage of GPIC DPLL lock indicators DPLL holdover indicators Reference fail indicators Reference select control or m Differential output clock enabled high performance LVCMOS (Host Interrupt Output: flags chread the enabled interrupt services 6:0 are internally pulled of If not used GPIO can be kept of After power on reset, device GPIO[4] sets SPI (low) or I2C master clock rate selection. The with an external 1KΩ resistor a must be driven low or high for GPIO functions. | nonitor le (per output or as a bank of 2 or 4 outputs) outputs enable anges of device status prompting the processor to vice registers (ISR).                                                                |

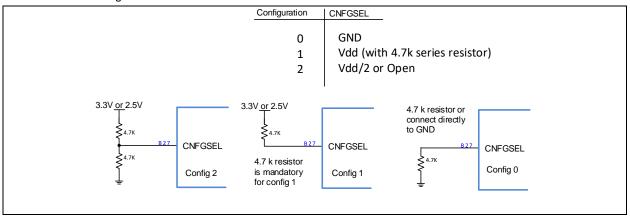

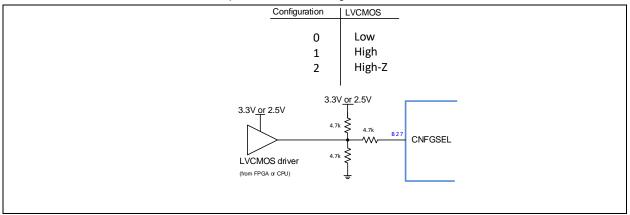

| B27                                              | CNFGSEL                                                     | I   | custom configurations on the ploaded by MSCC. If custom considering power up and the device registion                                                                                                                                                                                                                                                                                                                                                                                                                               | n is three level input which selects one of three cower up. Custom configurations have to be pre- infigurations are not loaded, this pin is ignored on the ters are loaded with default values.  CNFGSEL GND |

|                                                  |                                                             |     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GND $V_{DD}$ (has to be pulled up with 4.7kΩ resistor)                                                                                                                                                       |

|                                                  |                                                             |     | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | V <sub>DD</sub> (has to be pulled up with 4.7 kg2 resistor)                                                                                                                                                  |

|                                                  |                                                             |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 75572 of Opon                                                                                                                                                                                                |

| Host Inter                                       | face                                                        |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                              |

| Y1                                               | SCK_SCL                                                     | I/O | Clock for Serial Interface. Provides clock for serial micro-port interface. This pin is also the serial clock line (SCL) when the host interface is configured for I2C mode. As an input this pin is internally pulled up to $V_{DD}$ . In I2C mode this pin should be externally pulled high by $1K\Omega$ to $5K\Omega$ resistor.                                                                                                                                                                                                 |                                                                                                                                                                                                              |

| AB1                                              | SI_SDA                                                      | I/O | <b>Serial Interface Input.</b> Serial interface input stream. The serial data stream holds the access command, the address and the write data bits. This pin is also the serial data line (SDA) when host interface is configured for I2C mode. This pin is internally pulled up to $V_{DD}$ . In I2C mode this pin should be externally pulled high by $1K\Omega$ to $5K\Omega$ resistor.                                                                                                                                          |                                                                                                                                                                                                              |

| W2                                               | SO_ASEL1                                                    | I/O | $5K\Omega$ resistor.<br><b>Serial Interface Output.</b> Serial interface output stream. As an output the serial stream holds the read data bits. This pin is also the I2C address select when host interface is configured for I2C mode.                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                              |

| AA2                           | CS_b_ASEL0                      | 1     | Chip Select for Serial Interface. Serial interface chip select, this is an active low signal. This pin is also the I2C address select when host interface is configured for I2C mode. This pin is internally pulled up to V <sub>DD</sub> .                                                                                                                                                                                                                                                                          |  |

|-------------------------------|---------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| JTAG (IEE                     | EE 1149.1)                      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| AH7                           | TDO                             | 0     | <b>Test Serial Data Out.</b> JTAG serial data is output on this pin on the falling edge of TCK. This pin is held in high impedance state when JTAG scan is not enabled.                                                                                                                                                                                                                                                                                                                                              |  |

| AH9                           | TDI                             | I     | <b>Test Serial Data In.</b> JTAG serial test instructions and data are shifted in on this pin. This pin is internally pulled up to $V_{DD}$ . If this pin is not used then it should be left unconnected.                                                                                                                                                                                                                                                                                                            |  |

| AJ10                          | TRST_b                          | I     | <b>Test Reset.</b> Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-Reset state. This pin should be held low, or pulsed low on power-up, to ensure that the device is in the normal functional state. This pin is internally pulled up to $V_{DD}$ . If this pin is not used then it should be connected to GND.                                                                                                                                                                   |  |

| AH11                          | тск                             | I     | <b>Test Clock.</b> Provides the clock to the JTAG test logic. This pin is internally pulled up to $V_{DD}$ . This pin is internally pulled up to $V_{DD}$ . If this pin is not used then it should be connected to GND.                                                                                                                                                                                                                                                                                              |  |

| AJ8                           | TMS                             | I     | <b>Test Mode Select.</b> JTAG signal that controls the state transitions of the TAP controller. This pin is internally pulled up to V <sub>DD</sub> . If this pin is not used then it should be left unconnected.                                                                                                                                                                                                                                                                                                    |  |

| Master Cl                     | ock                             |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| AC28                          | osco                            | A-O   | Oscillator Master Clock. For crystal operation, a crystal is connected from this pin to OSCI. Not suitable for driving other devices. For clock oscillator operation, this pin is left unconnected. If OSCI is not used (MCLKIN is used) this pin is left unconnected.                                                                                                                                                                                                                                               |  |

| AB29                          | OSCI                            | I     | Oscillator Master Clock. For crystal operation, a crystal is connected from this pin to OSCO. For clock oscillator operation, this pin is connected to a clock source. Supported Crystal/Oscillator frequencies: 10 MHz, 20 MHz, 24.576 MHz, 25 MHz, 49.152 MHz, 50 MHz, 98.304 MHz, 100 MHz, 114.285 MHz, 125 MHz. If 98.304 MHz, 100 MHz, 114.285 MHz or 125 MHz is available then the system PLL can be used as a third synthesizer. If OSCI is not used (MCLKIN is used), it should be pulled-up or pulled-down. |  |

| W28<br>Y29                    | MCLKIN_P<br>MCLKIN_N            | I     | Differential Oscillator Master Clock This input is connected to a differential clock oscillator. Supported oscillator frequencies: 98.304 MHz, 100 MHz, 114.285 MHz, 125 MHz, 200 MHz.  If the differential master clock input is not used, MCLKIN_P and MCLK_N should be pulled low.                                                                                                                                                                                                                                |  |

| Miscelland                    | eous                            |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| P1<br>A6<br>AC2<br>AF1<br>AG2 | IC0<br>IC5<br>IC6<br>IC7<br>IC9 | A-I/O | Internal Connection Leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| AD29<br>AE28                 | IC3<br>IC4                                       | I | Internal Connection Connect to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|------------------------------|--------------------------------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| U2<br>AE2                    | IC1<br>IC8                                       | I | Internal Connection Pull-down with 1K $\Omega$ resistor or connect directly to ground.                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Power and                    | d Ground                                         |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

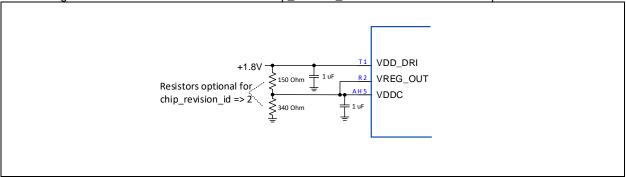

| T1                           | VDD_DRI                                          | Р | <b>Positive Supply Voltage.</b> Connect to +1.8V <sub>DC.</sub> Associated with core operation (internal regulator block). Refer to section 10.6.5 for more details.                                                                                                                                                                                                                                                                                                                          |  |

| R2                           | VREG_OUT                                         | Р | <b>Positive Supply Voltage</b> Connect to an external capacitor to ground. Connect to an external $340\Omega$ resistor to ground. Connect to an external $150\Omega$ resistor to VDD_DRI (pin T1). $340\Omega$ and $150\Omega$ resistors are required only for devices with chip_revision_id equal to 0 or 1. For devices with chip_revision_id equal to 2 these resistors are optional. Refer to section 10.6.5 for more details. Associated with core operation (internal regulator block). |  |

| AH5                          | VDDC                                             | Р | Positive Supply Voltage Connect to VREG_OUT (pin R2). Associated with core operation.                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| V1<br>AH3<br>A10<br>B5<br>B3 | VDD                                              | Р | <b>Positive Supply Voltage.</b> Connect to +2.5 V <sub>DC</sub> or +3.3V <sub>DC</sub> . Associated with Control & Status signals (GPIO[4:6]), Host Interface signals, JTAG signals, Input Reference signals, Output Clocks (GPOUT[0:1]) signals, and core operation.                                                                                                                                                                                                                         |  |

| A26<br>A24                   | VDD_HS0_0<br>VDD_HS0_2                           | Р | <b>Positive Supply Voltage.</b> Connect to +1.8V <sub>DC</sub> . Associated with core operation of synthesizer 1.                                                                                                                                                                                                                                                                                                                                                                             |  |

| B25<br>C28                   | VDD_HS0_1<br>VDD_HS0_3                           | Р | <b>Positive Supply Voltage.</b> Connect to +2.5 $V_{DC}$ or +3.3 $V_{DC}$ . Associated with core operation of synthesizer 1. The choice of +2.5 $V_{DC}$ or +3.3 $V_{DC}$ must be the same across all synthesizers.                                                                                                                                                                                                                                                                           |  |

| D29                          | VDD_HS0                                          | Р | <b>Positive Supply Voltage</b> Connect to $+2.5 \text{ V}_{DC}$ if the device is powered by $1.8 \text{V}_{DC}$ / $+2.5 \text{ V}_{DC}$ . Connect only to an external capacitor to ground if the device is powered by $1.8 \text{V}_{DC}$ / $+3.3 \text{ V}_{DC}$ . Associated with core operation of synthesizer 1.                                                                                                                                                                          |  |

| AH25<br>AJ26<br>AH27<br>AJ24 | VDD_HS1_0<br>VDD_HS1_1<br>VDD_HS1_2<br>VDD_HS1_3 | Р | <b>Positive Supply Voltage.</b> Connect to +1.8V <sub>DC</sub> . Associated with core operation of synthesizer 2.                                                                                                                                                                                                                                                                                                                                                                             |  |

| AG28                         | VDD_HS1_4                                        | Р | <b>Positive Supply Voltage.</b> Connect to +2.5 $V_{DC}$ or +3.3 $V_{DC}$ . Associated with core operation of synthesizer 2. The choice of +2.5 $V_{DC}$ or +3.3 $V_{DC}$ must be the same across all synthesizers.                                                                                                                                                                                                                                                                           |  |

| AF29                         | VDD_HS1                                          | Р | Positive Supply Voltage Connect to +2.5 V <sub>DC</sub> if the device is powered by 1.8V <sub>DC</sub> /+2.5 V <sub>DC</sub> . Connect only to an external capacitor to ground if the device is powered by 1.8V <sub>DC</sub> /+3.3 V <sub>DC</sub> . Associated with core operation of synthesizer 2.                                                                                                                                                                                        |  |

| T29<br>V29                   | VDD_SYS_0<br>VDD_SYS_1                           | Р | <b>Positive Supply Voltage.</b> Connect to +2.5 $V_{DC}$ or +3.3 $V_{DC}$ . Associated with core operation of synthesizer 3 (system PLL). The choice of +2.5 $V_{DC}$ or +3.3 $V_{DC}$ must be the same across all synthesizers.                                                                                                                                                                                                                                                              |  |

| R28<br>P29<br>E28            | VDD_SYS _2<br>VDD_SYS _3<br>VDD_SYS_4            | Р | <b>Positive Supply Voltage.</b> Connect to +1.8V <sub>DC</sub> . Associated with core operation of synthesizer 3 (system PLL)                                                                                                                                                                                                                                                                                                                                                                 |  |

| U28                                      | VDD_SYS                                                        | Р | <b>Positive Supply Voltage</b> Connect to +2.5 V <sub>DC</sub> if the device is powered by 1.8V <sub>DC</sub> /+2.5 V <sub>DC</sub> . Connect only to an external capacitor to ground if the device is powered by 1.8V <sub>DC</sub> /+3.3 V <sub>DC</sub> . Associated with core operation of synthesizer 3 (system PLL). |  |

|------------------------------------------|----------------------------------------------------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| B23<br>B19<br>AH23<br>AH19<br>G28<br>K29 | VDD_HP0<br>VDD_HP1<br>VDD_HP2<br>VDD_HP3<br>VDD_HP4<br>VDD_HP5 | Р | <b>Positive Supply Voltage</b> Connect to +1.8V <sub>DC</sub> or +2.5 V <sub>DC</sub> or +3.3 V <sub>DC</sub> These pins are used to power high performance outputs. Each pin can be connected to different supply voltage.                                                                                                |  |

| B15                                      | VDD_RI                                                         | Р | <b>Positive Supply Voltage</b> Connect to the highest supply voltage: +2.5 V <sub>DC</sub> or +3.3 V <sub>DC</sub> . Associated with Control & Status signals (RST_b, GPIO[0:3]) and core operation (internal regulator block).                                                                                            |  |

| A14                                      | VDD_RO                                                         | Р | <b>Positive Supply Voltage.</b> Connect to +1.8V <sub>DC</sub> . Associated with core operation (internal regulator block).                                                                                                                                                                                                |  |

| N2<br>AJ4<br>B9<br>A4<br>AH13            | VSS                                                            | Р | Ground. 0 Volts.                                                                                                                                                                                                                                                                                                           |  |

| A20<br>A16<br>AJ20<br>AJ16<br>J28<br>N28 | VSS_HP0<br>VSS_HP1<br>VSS_HP2<br>VSS_HP3<br>VSS_HP4<br>VSS_HP5 | Р | Ground. 0 Volts.                                                                                                                                                                                                                                                                                                           |  |

| AA28                                     | VSS_OSC                                                        | Р | Ground. 0 Volts.                                                                                                                                                                                                                                                                                                           |  |

| E-Pad                                    | VSS                                                            | Р | Analog Ground. 0 Volts.                                                                                                                                                                                                                                                                                                    |  |

ZL30174

### 10 Hardware Functional Description

#### 10.1 Input References

#### 10.1.1 Input Sources

The device has twelve input sources: ten input references (ten single ended or five differentials), and two oscillator clock sources (one single ended or one differential).

The device master clock frequency is configured on reset via external voltage levels on GPIO[5,3,2,1,0] pins as described in the pin description section.

The device synchronizes (locks) to any input reference which is a 1 kHz multiple, or it synchronizes (locks) to any input reference which is an  $M/N \times 1$  kHz multiple (FEC rate) where M and N are 16 bits wide. In some cases  $M/N \times 1$  Hz,  $M/N \times 10$  Hz and  $M/N \times 100$  Hz is supported.

The device input reference frequency is programmed during initialization. The input reference frequency can be changed when the input reference is not the active source for a DPLL.

The device accepts an input reference with a maximum frequency of 180 MHz through single ended LVCMOS input or 900 MHz frequency through differential inputs.

If the frequency of an input reference exceeds 400 MHz, the reference must be internally divided by 2 before being fed to DPLL (Refer to **ref config** registers).

#### 10.1.2 Input Reference Monitoring

The input references are monitored by reference monitor indicators which are independent for each reference. They indicate abnormal behavior of the reference signal, for example; drift from its nominal frequency or excessive jitter.

#### 10.1.2.1 Input Loss of Signal Monitor (LOS)

LOS is an external signal, fed to one of ZL30174 GPIO pins. LOS is typically generated by a PHY device whose recovered clock is fed to one of the reference inputs. The PHY device will generate a LOS signal when it cannot reliably extract the clock from the line. The user can set one of GPIO pins as a LOS input by programming corresponding GPIO register.

The GPIO inputs are read approximately every 10 ms, except with using system PLL bypass mode with 100 MHz oscillator where they are read approximately every 25 ms.

# 10.1.2.2 Input Coarse Frequency Monitor (CFM)

The CFM monitors the input reference frequency for 1.25 ms so that it can quickly detect large changes in frequency. CFM limit for each input reference can be selected in **ref\_cfm** mailbox register with range from 0.1% to 50%. If the CFM limit is exceeded, then CFM failure is declared for corresponding reference.

For frequencies below 16 kHz, the CFM and SCM limits should be set to the same value for proper operation.

#### 10.1.2.3 Input Precise Frequency Monitor (PFM)

The PFM block measures the frequency accuracy of the reference and updates the indicator bit. To prevent PFM from being false triggered by jitter/wander at the reference input, PFM averages frequency for more than 10 second period and indicate failure when the measured frequency exceeds limit specified in <code>ref\_pfm\_disqualify</code> register. To ensure an accurate frequency measurement, the PFM measurement interval is re-started if phase or frequency irregularities are detected by SCM or CFM. The PFM provides a level of hysteresis to prevent a failure indication from toggling between valid and invalid for input references that are on the edge of the acceptance range. PFM limit should be set as described in <code>ref\_pfm\_disqualify</code> and <code>ref\_pfm\_qualify</code> mailbox registers.

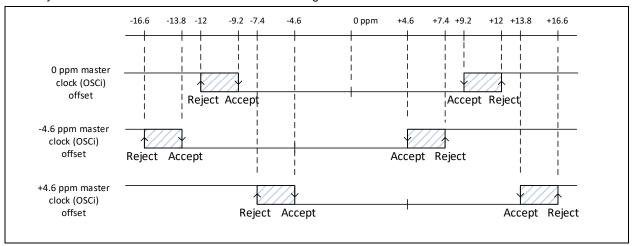

When determining the frequency accuracy of the reference input, the PFM uses the external master clock oscillator's frequency as its reference. As a result, the actual acceptance and rejection frequencies can be offset with respect to the external oscillator's output frequency. This is accounted for in the acceptance and rejection requirements as described in Telcordia GR-1244 section 3.4.1. An example of the acceptance and rejection ranges for Stratum 3 application (acceptance in the range of +/- 9.2 ppm, rejection at +/- 12 ppm) given a +/- 4.6 ppm freerun frequency accuracy of a Stratum 3 reference oscillator is shown in Figure 5.

Figure 5. Stratum 3/G.8262 Option I Frequency Acceptance and Rejection Ranges

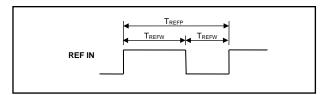

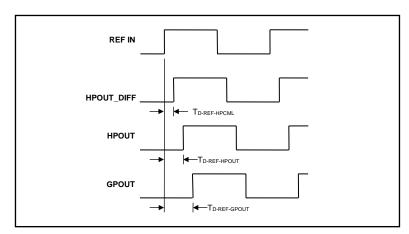

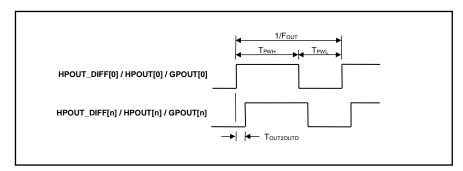

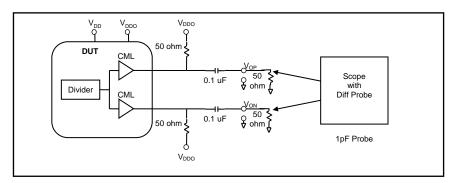

#### 10.1.2.4 Input Single Cycle Monitor (SCM)