## ZL30316

# Combined Synchronous Ethernet and IEEE1588 Timing over Packet Technology

**Data Sheet**

October 2012

#### Features

- Supports the combination of SyncE for frequency synchronization and IEEE 1588 for phase alignment (referred to as Hybrid Mode)

- Recovers and transmits network synchronization over Ethernet, IP and MPLS Networks

- Simultaneously supports both the Synchronous Ethernet (Option 1 and Option 2 and the IEEE 1588 industry standard timing protocols

- Capable of server, client repeater, and boundary clock operation

- Integrates two separate digital phase locked loops, with hitless switching between packet and electrical clock references

- Targeted for synchronization distribution to better than ITU-T G.8261, G.823, G.824 and ANSI T1.101 synchronization interface standards

- Average frequency accuracy better than ±10 ppb

- Aligns to a low frequency input signal at server (e.g., 1 Hz) with targeted accuracy better than ±1 μs

- Recovers clocks from two independent servers, with hitless switching between packet streams for redundancy

- Supports holdover if the server stream is lost

- Accepts eight input references, and up to three associated low frequency alignment or framing pulses

#### Ordering Information

ZL30316GKG 256 TEPBGA, 17 x 17 mm ZL30316GKG2\* 256 TEPBGA, 17 x 17 mm \* PB Free Tin/Silver/Copper

#### -40°C to +85°C

- Generates up to four separate output clocks at frequencies between 8 kHz and 100 MHz

- Generates two separate Synchronous Ethernet clocks to drive industry standard Ethernet PHY devices at either 25 MHz or 125 MHz

- Fully configurable solution, enabling performance to be tailored to application/network requirements

- Two independently configurable MAC interfaces, supporting MII, RMII, GMII and TBI standards

- Wire-speed Ethernet Bridge pass through function between the MAC interfaces

- Synchronous serial control interface

- Full demonstration & evaluation platform available

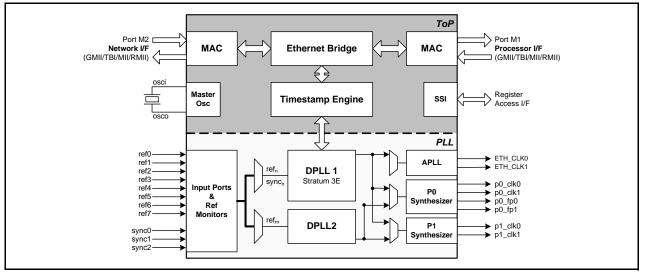

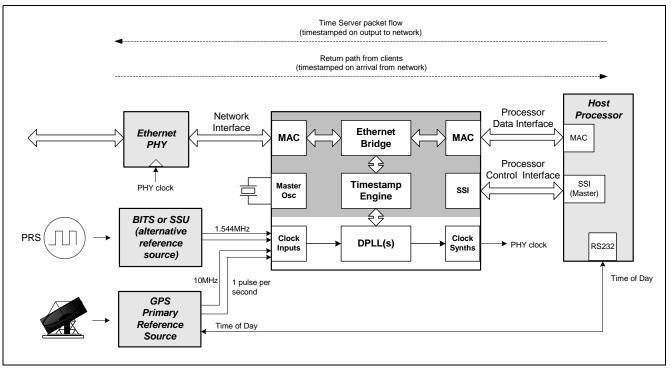

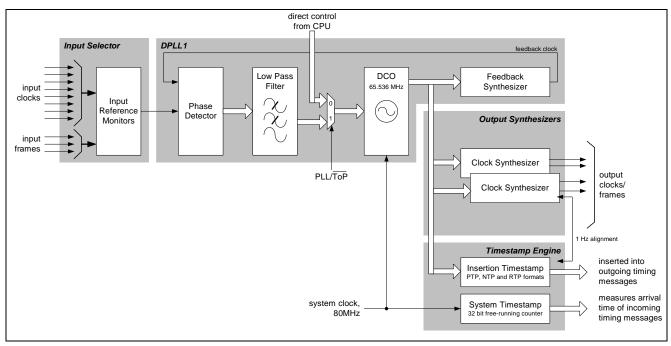

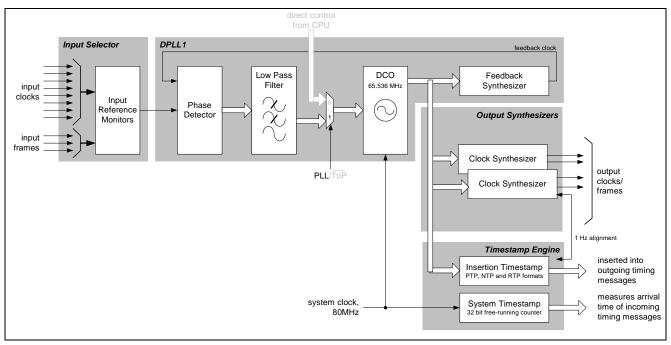

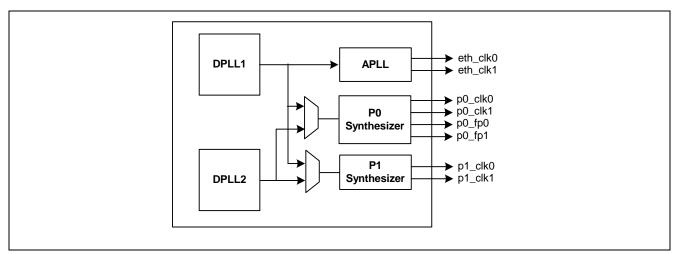

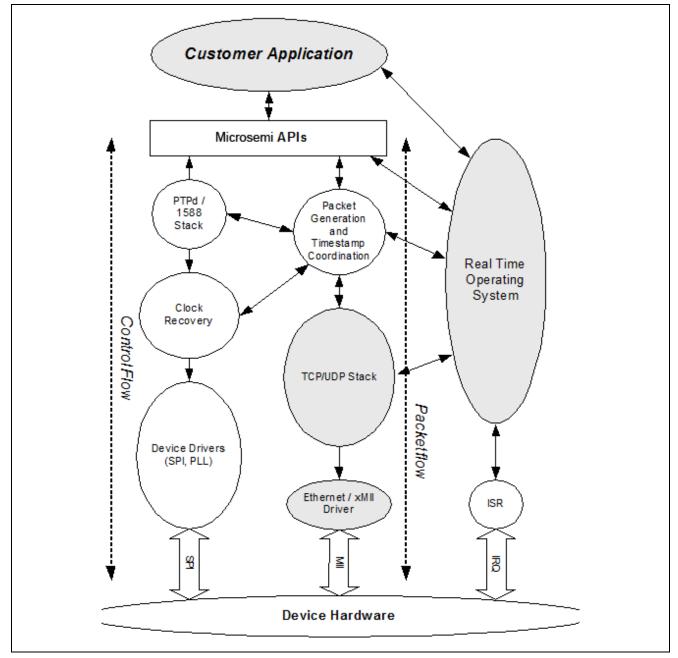

Figure 1 - ZL30316 Functional Block Diagram

### Applications

- IEEE 1588 and Synchronous Ethernet timing

- GSM and UMTS air interface synchronization over a packet network

- Circuit Emulation Services over Packets

- IP-PBX and VoIP Gateways

- Video Conferencing

- Broadband Video Distribution

### Change Summary

Changes from the September 2011 issue to the October 2012 issue.

| Page | Item                 | Description                                                                              |

|------|----------------------|------------------------------------------------------------------------------------------|

| 1    | Ordering Information | A note was added for the ZL30316GKG2 256<br>TEPBGA package: "Pb Free Tin/Silver/Copper." |

#### Description

Network infrastructures are gradually converging onto a packet-based architecture. With this convergence, there are a significant number of synchronous applications that require accurate timing to be distributed over the packet networks. Examples of precision timing sensitive applications that need the transport of synchronization over packet networks include transport of TDM over packet networks, connections to 2 G and 3 G cellular base stations, Voice over IP, IP PBXs, video-conferencing and broadband video.

There are two main ways to enable synchronization over a packet network, synchronizing the packet network itself, as in the Synchronous Ethernet approach, or distributing the timing using the packets as in Microsemi's Timing over Packet (ToP) technology. The two techniques can also be combined to provide a very powerful hybrid solution. Synchronous Ethernet delivers a very accurate frequency reference, but doesn't address phase and time synchronization. ToP can be used to supplement the excellent frequency distribution of Synchronous Ethernet with accurate phase and time information. Alternatively, ToP can be used to extend the reach of the Synchronous Ethernet reference across an asynchronous network, such as a LAN connected to a synchronous WAN.

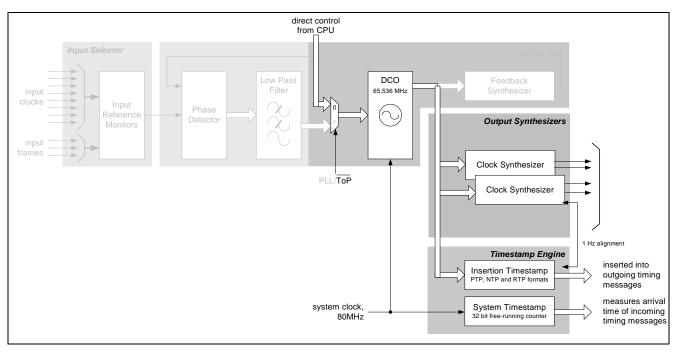

Microsemi has combined both methods into a single device. The ZL30316 incorporates an extremely low-jitter frequency synthesizer, capable of generating all the frequencies required for Synchronous Ethernet operation, together with Microsemi's patent-pending Timing over Packet (ToP) technology based on the industry-standard IEEE1588<sup>TM</sup> "PTP" (Precision Time Protocol). Not only can it function as a fully-featured Digital PLL, it also supports the distribution of time, phase and frequency across both layer 2 and layer 3 networks, using both Synchronous Ethernet and IEEE1588 protocols, either alone or in combination.

The ZL30316 is a member of a family of footprint-compatible devices offering the full range of features required for timing and synchronization across the packet network. These devices facilitate design of a flexible card that can be upgraded as required by simply placing another member of the same family.

The family members include:

| ZL30310 | ZL30310; Combined IEEE1588 <sup>TM</sup> ToP and Synchronous Ethernet, coupled with a GR-1244 Stratum 2/3E/3/4/4E GR-253 SONET, G.812 (types 2 and 3) G.813, and G.8262 quality phase locked loop for timing card applications, plus a second independent PLL for rate conversion or generation of additional derived clocks. |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ZL30312 | Combined IEEE1588 <sup>TM</sup> ToP and Synchronous Ethernet, coupled with a GR-1244 Stratum 3/4/4E and GR-253 SEONET and G.813 quality phase locked loop for timing card applications, plus a second independent PLL for rate conversion or generation of additional derived clocks.                                         |

| ZL30314 | Combined IEEE1588 <sup>TM</sup> ToP and Synchronous Ethernet, coupled with a GR1244 Stratum 3/4/4E and G.813 Option 1 quality phase locked loop for timing card applications, plus a second independent PLL for rate conversion or generation of additional derived clocks.                                                   |

| ZL30316 | Combined IEEE1588 <sup>TM</sup> ToP and Synchronous Ethernet, coupled with two independent, flexible phase locked loops for line card applications                                                                                                                                                                            |

| ZL30320 | Combined IEEE1588 <sup>TM</sup> ToP and Synchronous Ethernet for line card applications                                                                                                                                                                                                                                       |

| ZL30321 | Synchronous Ethernet line card device in a ToP compatible footprint, containing two independent DPLLs                                                                                                                                                                                                                         |

The Microsemi device offers the following clock routing options:

| Input                         | Output                     | Description                                                                                                                                                                             |  |  |  |  |

|-------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| clock reference               | clock                      | conventional PLL behaviour,<br>e.g., Synchronous Ethernet node                                                                                                                          |  |  |  |  |

| clock reference               | packet stream              | server behaviour,<br>e.g., IEEE1588 server                                                                                                                                              |  |  |  |  |

| clock reference               | clock and/or packet stream | conventional PLL behaviour coupled with packet time server, e.g., combined Synchronous Ethernet and IEEE1588 server                                                                     |  |  |  |  |

| packet reference              | clock                      | client behaviour,<br>e.g., IEEE1588 client                                                                                                                                              |  |  |  |  |

| clock and/or packet reference | clock                      | conventional PLL behaviour, coupled with packet time client,<br>either as fail-over from one to the other, or in combination<br>e.g., combined Synchronous Ethernet and IEEE1588 client |  |  |  |  |

| packet reference              | clock and/or packet stream | combination of client and boundary clock behaviour, e.g., IEEE1588 Boundary Clock                                                                                                       |  |  |  |  |

When operating as a server, the Microsemi device locks onto the incoming clock reference as a conventional PLL, filtering any jitter that may be present. It also synchronizes to any low-frequency alignment signal, e.g., an 8 kHz TDM frame pulse, or a 1 Hz alignment input. The device delivers streams of packets, each containing a timestamp indicating the precise time that the packet was launched into the network, relative to the acquired reference. It also receives packets from clients, and returns a message indicating the exact time that the client message was received at the server. Using this information, clients are able to align their own timebase with that of the server.

As a client, the Microsemi device can track two independent servers, and determine which one is providing the best time reference. If either the primary reference or the network between the server and client fails, the device can switch to the alternative reference without introducing a phase discontinuity. Alternatively, the client can switch to a conventional clock reference.

The solution timing recovery algorithm continuously tracks the frequency offset and phase drift between the clocks located at the server and the client nodes connected via the packet switched network. The algorithm is tolerant of lost packets, and of packet delay variation caused by packet queuing, route changes and other effects. In the event of a failure in the packet network, or the advent of severe congestion preventing or seriously delaying the delivery of timing packets, the device will put the recovered clocks into holdover until the flow of timing packets is restored. When the device is in holdover mode the drift of the local oscillator directly affects the accuracy of the output clocks.

When using ToP technology, the device is designed to meet ANSI standard T1.101 and ITU-T standards G.823 and G.824 for synchronization distribution. It maintains a mean frequency accuracy of better than  $\pm 10$  ppb and time alignment of better than  $\pm 1 \ \mu$ s when operated over a suitable network.

## **Table of Contents**

|     | Physical Specification                                               |      |

|-----|----------------------------------------------------------------------|------|

| 2.0 | External Interface Description                                       | . 15 |

|     | 2.1 Clock Interface.                                                 | . 15 |

|     | 2.1.1 Output Clock Impedance Matching                                | . 16 |

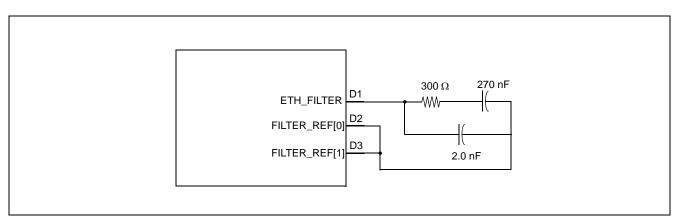

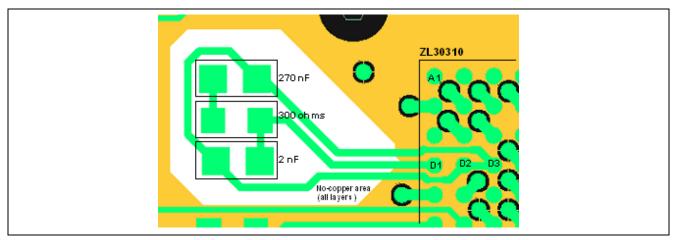

|     | 2.2 Ethernet Output Clock Loop Filter                                |      |

|     | 2.2.1 Ethernet Filter Components                                     | . 16 |

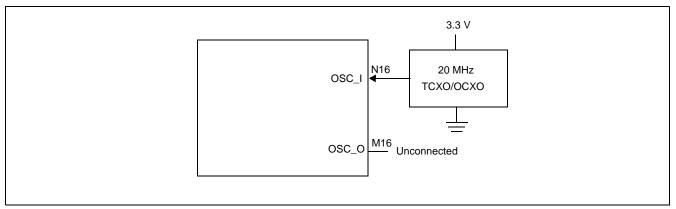

|     | 2.3 Local Oscillator                                                 | . 17 |

|     | 2.3.1 Use of a Clock Oscillator                                      |      |

|     | 2.4 Packet Interfaces                                                |      |

|     | 2.4.1 GMII and MII Signal Routing                                    |      |

|     | 2.5 CPU and Control Interface                                        |      |

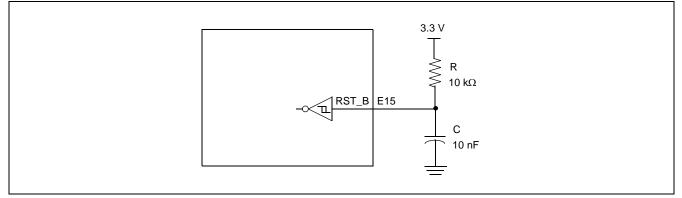

|     | 2.5.1 Reset Circuit                                                  |      |

|     | 2.6 JTAG and Test Interfaces                                         |      |

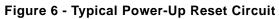

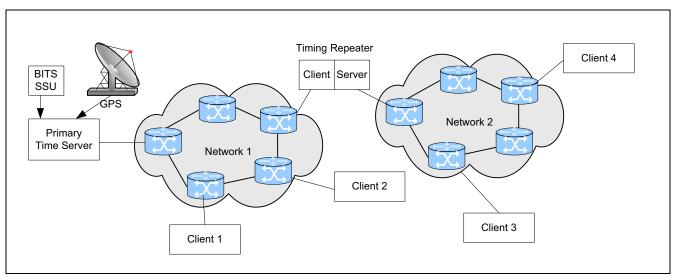

|     | 2.7 Power and Ground Connections                                     |      |

|     | 2.7.1 Power Up/Down Sequence                                         |      |

|     | 2.7.2 Power Supply Decoupling and Layout Practices                   |      |

|     | 2.8 Non-connects                                                     |      |

| 3.0 | Modes of Operation                                                   | . 27 |

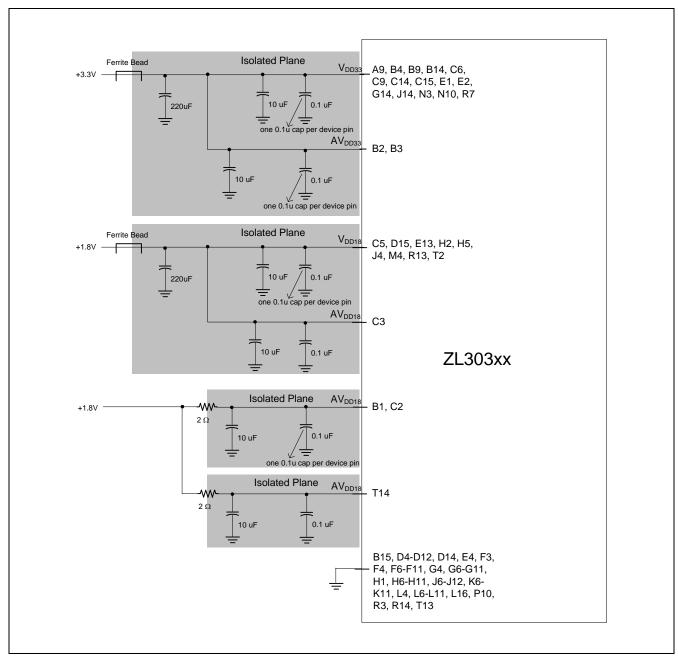

|     | 3.1 Time Server Operation                                            |      |

|     | 3.2 Client Operation                                                 |      |

|     | 3.3 Boundary Clock Mode of Operation                                 |      |

|     | 3.4 Timing Redundancy and Holdover                                   | . 30 |

| 4.0 | Functional Description                                               | . 31 |

|     | 4.1 Ethernet Bridge and MAC Interfaces.                              |      |

|     | 4.1.1 Overview of Bridge Operation                                   | . 31 |

|     | 4.1.2 Handling of Timing Packets                                     | . 32 |

|     | 4.1.2.1 Classification                                               | . 32 |

|     | 4.1.2.2 Timestamp Insertion                                          |      |

|     | 4.1.2.3 Timing Packet Scheduling                                     | . 33 |

|     | 4.1.3 Handling of Non-Timing Packets                                 |      |

|     | 4.1.3.1 Broadcast and ARP filtering                                  |      |

|     | 4.1.4 Queuing System and Buffer Management.                          |      |

|     | 4.1.4.1 Packet Dropping                                              |      |

|     | 4.1.4.2 Flow Control                                                 |      |

|     | 4.1.5 MAC Interfaces                                                 |      |

|     | 4.1.5.1 GMII/TBI/MII/RMII Connectivity                               |      |

|     | 4.1.5.2 MAC Configuration                                            |      |

|     | 4.1.5.3 Link Up/Down Status                                          |      |

|     | 4.1.5.4 Management Link.                                             |      |

|     | 4.1.5.5 Statistics                                                   |      |

|     | 4.1.5.6 Layout Guidelines.                                           |      |

|     | 4.2 Timestamp Engine.                                                |      |

|     | 4.2.1 Server Operation                                               |      |

|     | 4.2.2 Client Operation                                               |      |

|     | 4.2.3 Boundary Clock Operation                                       |      |

|     | 4.2.4 Combined Synchronous Ethernet and Timing over Packet Operation |      |

|     | 4.3 DPLL Functional Description.                                     |      |

|     | 4.3.1 DPLL Features                                                  |      |

|     | 4.3.2.1 DPLL1 Mode Of Operation                                      |      |

|     | 4.3.2.2 DPLL2 Mode of Operation                                      |      |

|     | 4.3.3 Loop Bandwidth                                                 |      |

|     | T.0.0 LOOP Dahuwiuun                                                 | . 40 |

## **Table of Contents**

|                                                                                          | 40             |

|------------------------------------------------------------------------------------------|----------------|

| 4.3.4 Pull-in/hold-in Range                                                              |                |

| 4.3.5 Phase slope Limiting                                                               |                |

| 4.3.6 Hitless Reference Switching                                                        |                |

| 4.3.7 Holdover.                                                                          |                |

| 4.3.8 Reference and Sync Inputs                                                          |                |

| 4.3.9 Reference Input Selection                                                          |                |

| 4.3.10 Reference Monitoring.                                                             |                |

| 4.3.11 Sync Monitoring                                                                   |                |

| 4.3.12 Reference Monitoring for Custom Configurations                                    |                |

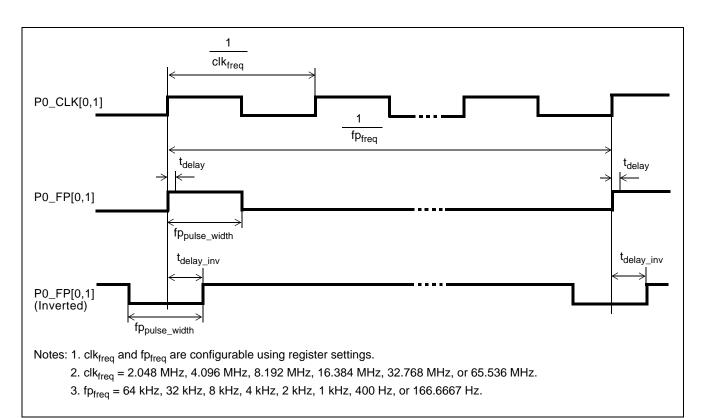

| 4.3.13 Output Clocks and Frame Pulses                                                    |                |

| 4.3.13.1 Output Clock and Frame Pulse Squelching                                         |                |

| 4.3.13.2 Disabling Output Clocks and Frame Pulses                                        |                |

| 4.3.13.3 Disabling Output Synthesizers                                                   | 61             |

| 4.3.14 Configurable Input-to-Output and Output-to-Output Delays.                         | 61             |

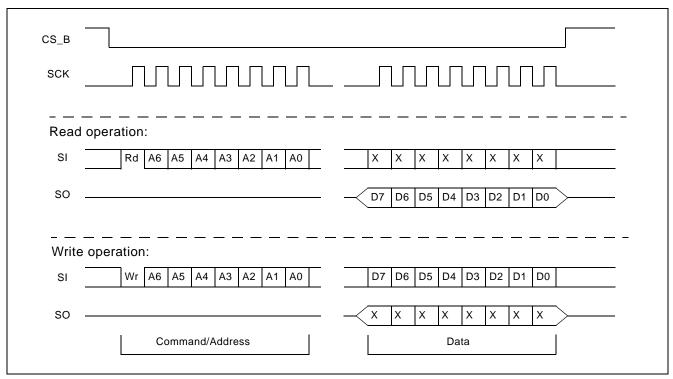

| 4.4 Synchronous Serial Interface                                                         | 63             |

| 4.4.1 Transmission Modes                                                                 | 63             |

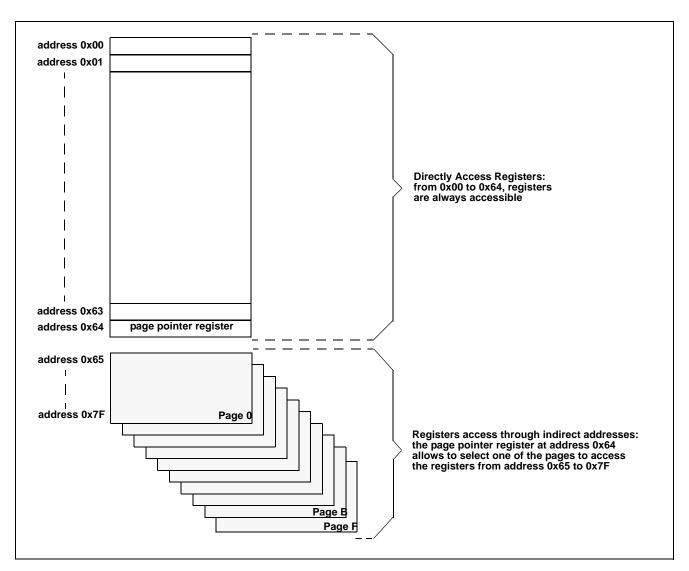

| 4.4.2 Page Addressing                                                                    | 64             |

| 4.4.3 Accessing Multi-byte Registers                                                     | 64             |

| 4.5 Timing Software                                                                      | 66             |

| 4.5.1 Hardware Requirements                                                              |                |

| 4.5.2 User Application                                                                   |                |

| 4.5.2.1 User-Provided Software Components                                                |                |

| 4.5.3 Microsemi-Provided Software Components.                                            |                |

| 4.5.3.1 Solution API                                                                     |                |

| 4.5.3.2 IEEE 1588 Stack                                                                  |                |

| 4.5.3.3 Other Software                                                                   |                |

| 4.5.4 Software Performance                                                               |                |

| 4.5.4.1 Use of Multicast vs. Unicast Packets                                             |                |

| 5.0 DC Characteristics                                                                   |                |

| 5.1 Absolute Maximum Ratings*                                                            |                |

| 5.2 Recommended Operating Conditions                                                     |                |

| 5.3 DC Electrical Characteristics                                                        |                |

| 6.0 AC Characteristics                                                                   |                |

|                                                                                          |                |

| 6.1 Clock Interface Timing.                                                              |                |

| 6.1.1 Input Timing For Sync References*                                                  |                |

| 6.1.2 Input To Output Timing For Ref <n> References*</n>                                 |                |

| 6.1.3 Output Clock Duty Cycle1                                                           |                |

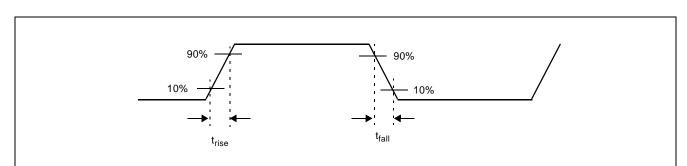

| 6.1.4 Output Clock and Frame Pulse Fall and Rise Times1                                  |                |

| 6.1.5 E1 Output Frame Pulse Timing*                                                      |                |

| 6.1.6 Measured Output Jitter On Ethernet Clock CMOS Outputs with Active MII Interface (E | : IH_CLK[0,1]) |

|                                                                                          |                |

| 6.1.7 Measured Output Jitter On Ethernet Clock CMOS Outputs with Active GMII Interface   | (ETH_          |

| CLK[0,1])75                                                                              |                |

| 6.1.8 Measured Output Jitter On Programmable CMOS Outputs (P0/1_CLK[0,1])                |                |

| 6.2 Packet Interface Timing.                                                             |                |

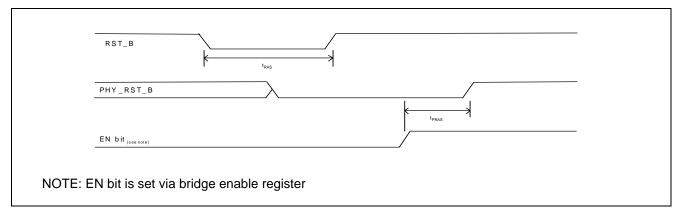

| 6.2.1 Typical Reset Timing Diagram.                                                      |                |

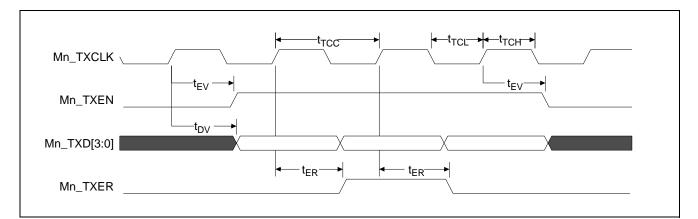

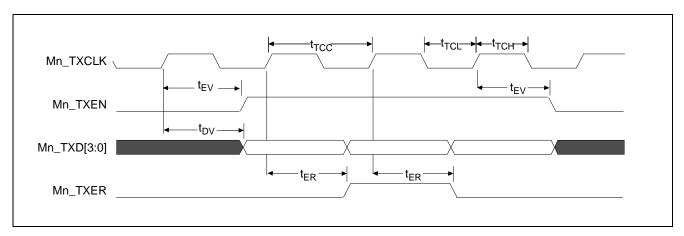

| 6.2.2 MII Transmit Timing: MAC to PHY Connections                                        |                |

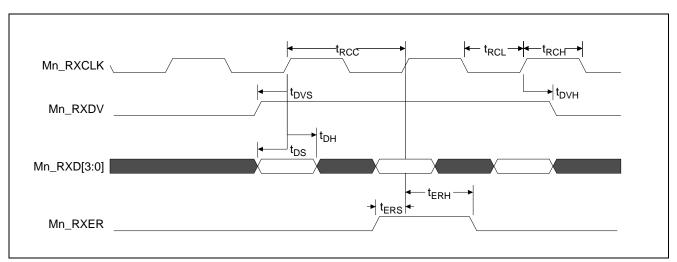

| 6.2.3 MII Receive Timing: MAC to PHY Connections                                         |                |

| 6.2.4 MII Transmit Timing: PHY Emulation Mode (MAC to MAC connections)                   |                |

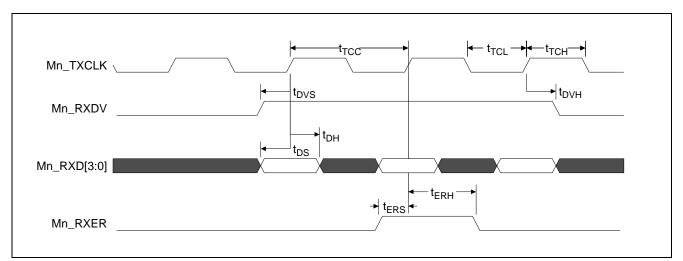

| 6.2.5 MII Receive Timing: PHY Emulation Mode (MAC to MAC connections)                    |                |

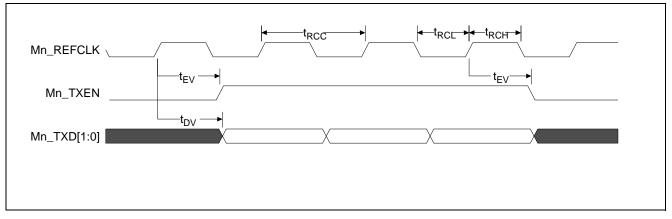

| 6.2.6 RMII Transmit Timing.                                                              |                |

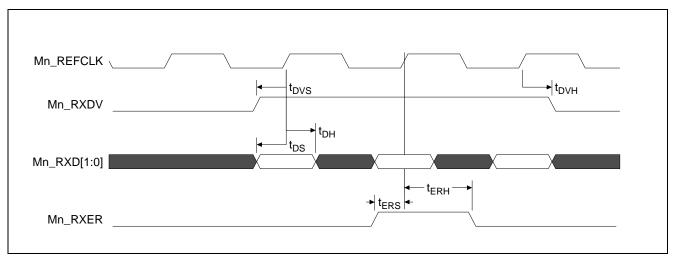

| 6.2.7 RMII Receive Timing                                                                | 82             |

## **Table of Contents**

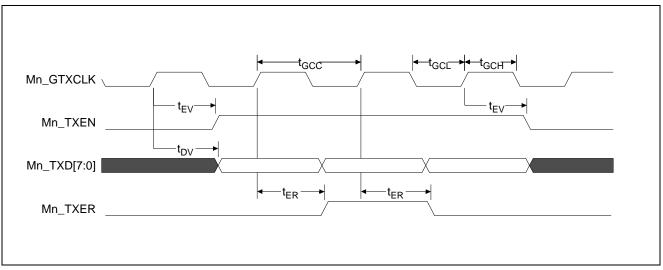

| 6.2.8 GMII Transmit Timing               | 83 |

|------------------------------------------|----|

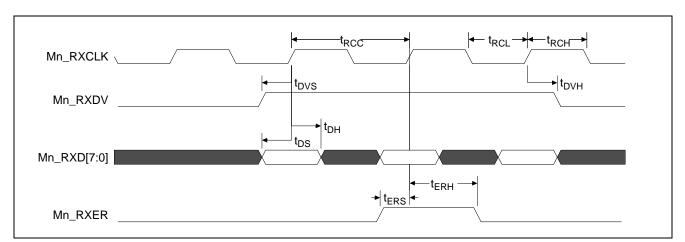

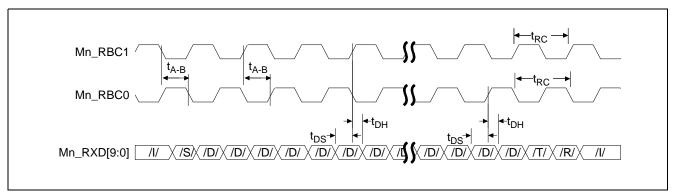

| 6.2.9 GMII Receive Timing                |    |

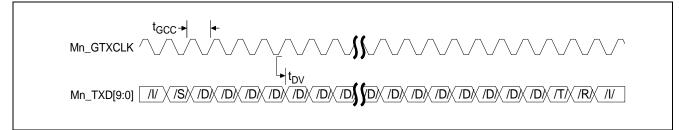

| 6.2.10 TBI Interface Timing.             |    |

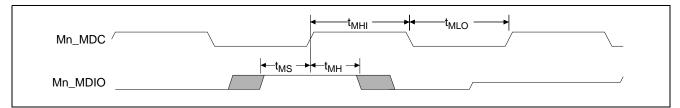

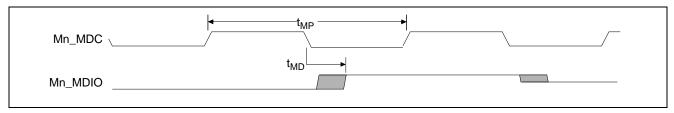

| 6.2.11 Management Interface Timing       | 86 |

| 6.3 Synchronous Serial Interface Timing. |    |

| 6.4 JTAG Interface Timing.               |    |

| 7.0 Package Dimensions                   | 89 |

## List of Figures

| Figure 1 - ZL30316 Functional Block Diagram                                    | . 1 |

|--------------------------------------------------------------------------------|-----|

| Figure 2 - ZL30316 Package View and Ball Positions                             | 12  |

| Figure 3 - Ethernet Loop Filter Component Values                               | 16  |

| Figure 4 - Ethernet Loop Filter Layout Example                                 | 17  |

| Figure 5 - Clock Oscillator Circuit.                                           |     |

| Figure 6 - Typical Power-Up Reset Circuit                                      | 22  |

| Figure 7 - Power Supply Decoupling for the ZL30316                             | 25  |

| Figure 8 - ZL30316 Operating Modes                                             |     |

| Figure 9 - Example ZL30316 Time Server driven from a GPS or BITS/SSU reference | 28  |

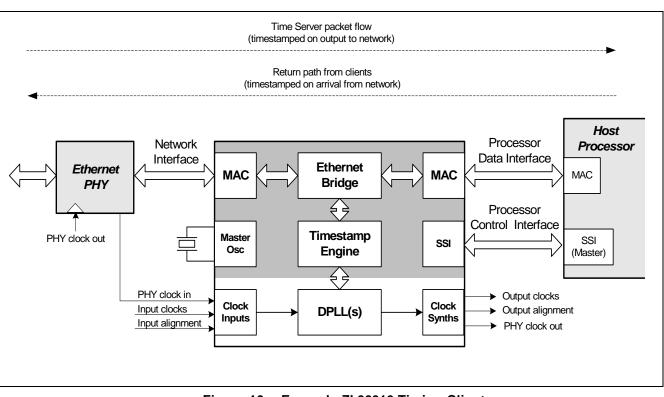

| Figure 10 - Example ZL30316 Timing Client.                                     |     |

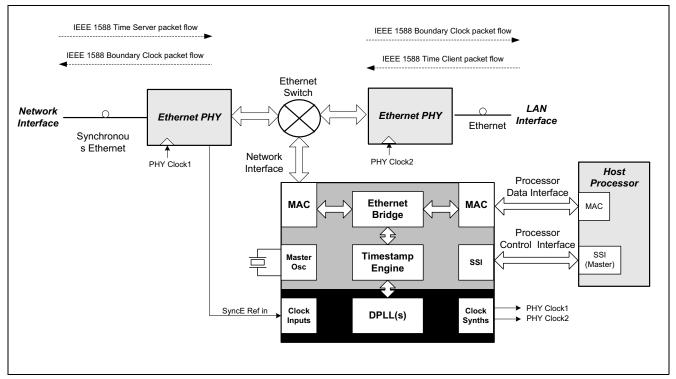

| Figure 11 - ZL30316 Boundary Clock                                             | 30  |

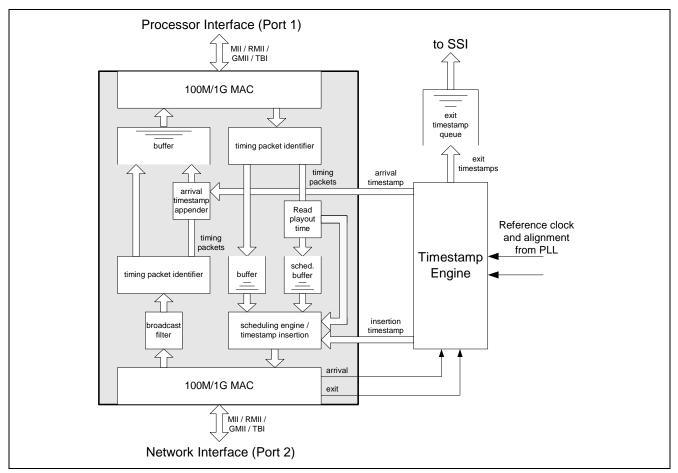

| Figure 12 - Ethernet Bridge Structure                                          | 31  |

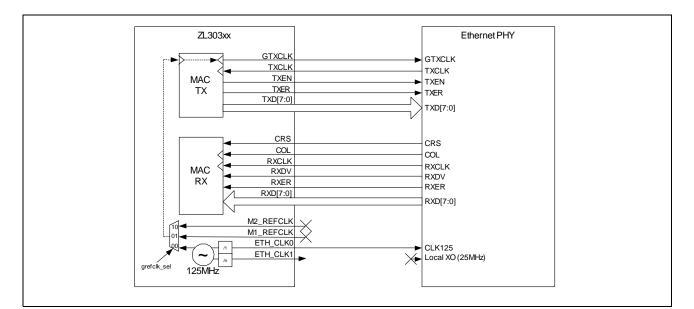

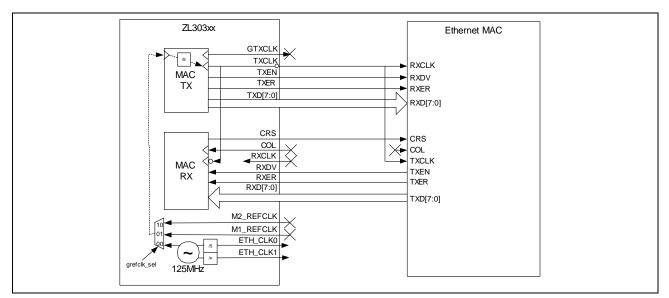

| Figure 13 - GMII Connection (MAC Mode)                                         | 36  |

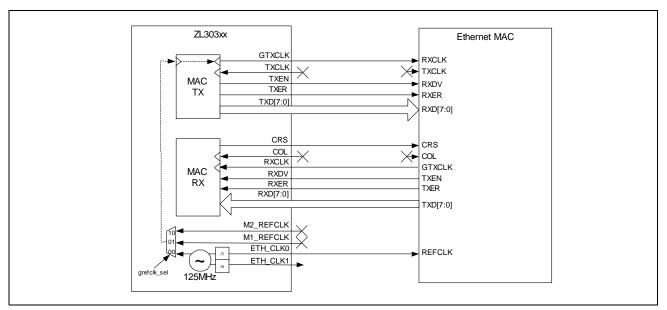

| Figure 14 - GMII Connection (PHY Mode)                                         | 37  |

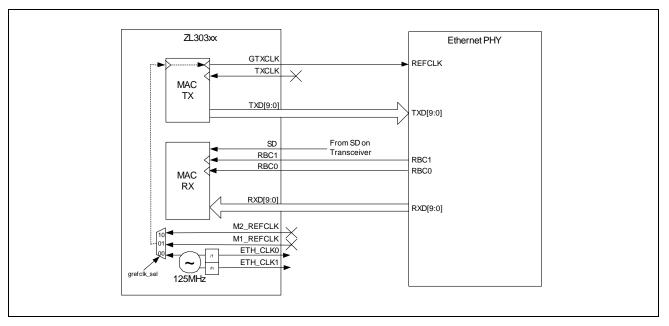

| Figure 15 - TBI Connection                                                     |     |

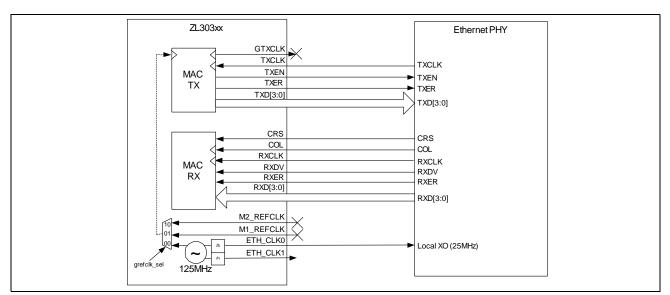

| Figure 16 - MII Connection (MAC Mode)                                          | 38  |

| Figure 17 - MII Connection (PHY Mode)                                          |     |

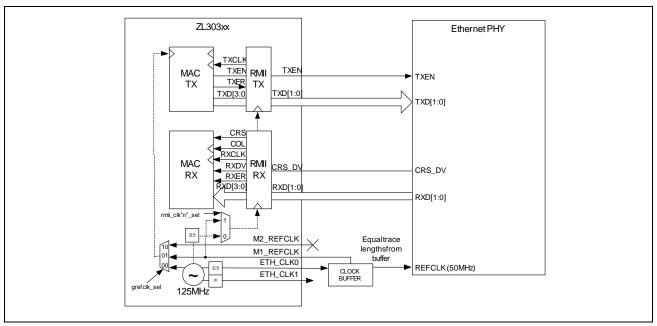

| Figure 18 - RMII Connection (MAC Mode).                                        | 39  |

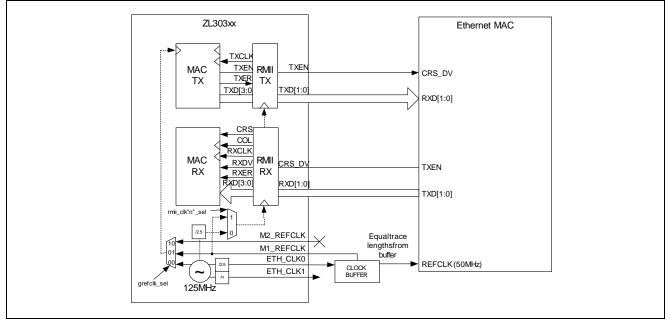

| Figure 19 - RMII Connection (PHY Mode)                                         | 39  |

| Figure 20 - Relationship of Timestamp Engine to DPLL                           | 43  |

| Figure 21 - Operation as a Timing over Packet Server                           | 44  |

| Figure 22 - Operation as a Timing over Packet Client                           | 45  |

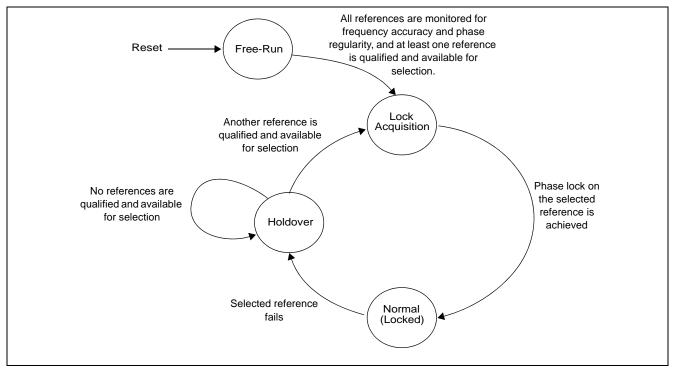

| Figure 23 - Automatic Mode State Machine                                       | 47  |

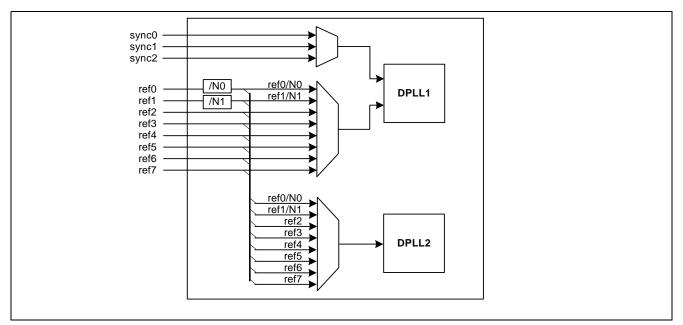

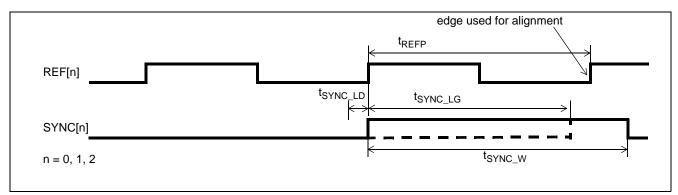

| Figure 24 - Reference and Sync Inputs                                          |     |

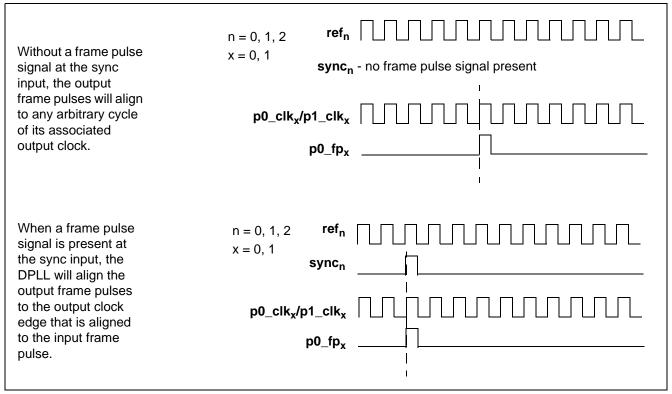

| Figure 25 - Output Frame Pulse Alignment                                       | 51  |

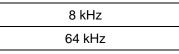

| Figure 26 - Behaviour of the Guard Soak Timer during CFM or SCM Failures       |     |

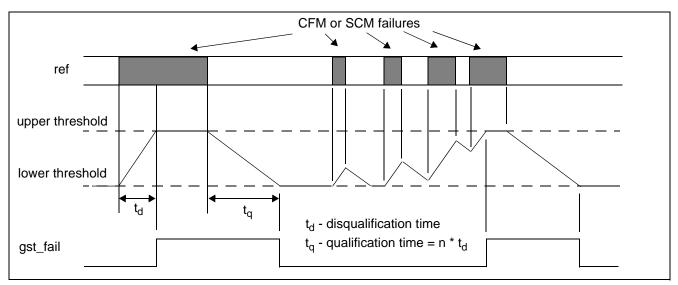

| Figure 27 - Frequency Acceptance and Rejection Ranges                          |     |

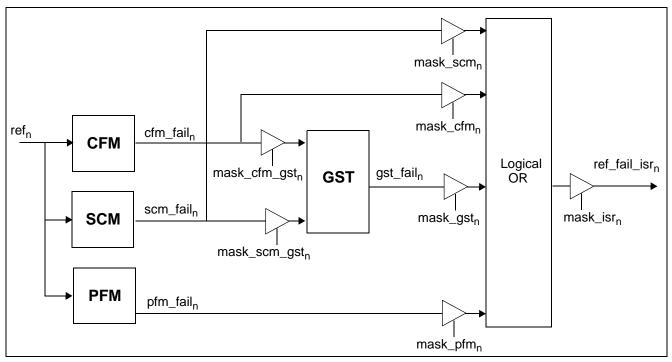

| Figure 28 - Reference Monitoring Block Diagram                                 | 55  |

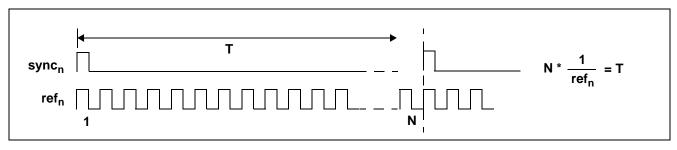

| Figure 29 - Sync Monitoring.                                                   | 55  |

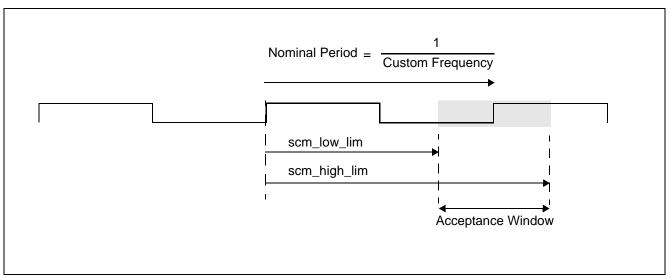

| Figure 30 - Defining SCM Limits for Custom Configurations                      |     |

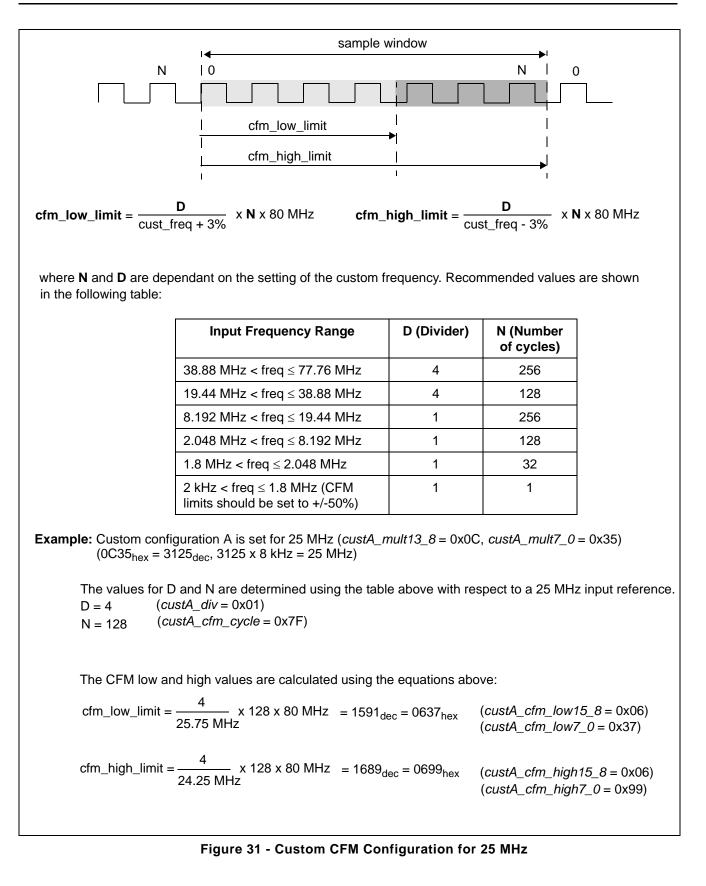

| Figure 31 - Custom CFM Configuration for 25 MHz.                               |     |

| Figure 32 - Output Clock Configuration                                         |     |

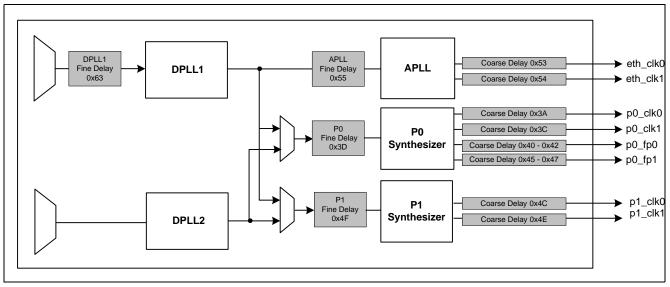

| Figure 33 - Phase Delay Adjustments                                            | 61  |

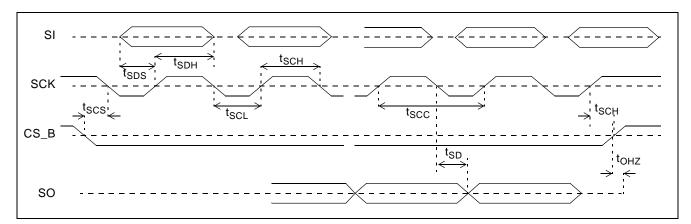

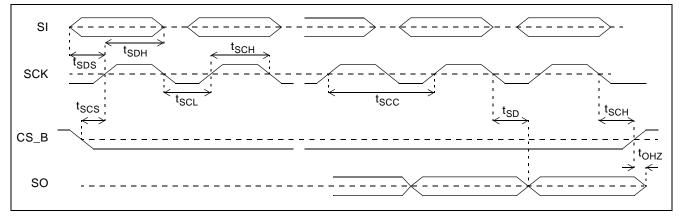

| Figure 34 - Serial Peripheral Interface Functional Waveforms - LSB First Mode  | 63  |

| Figure 35 - Serial Peripheral Interface Functional Waveforms - MSB First Mode  |     |

| Figure 36 - Page Addressing Scheme                                             |     |

| Figure 37 - High Level Software Architecture                                   |     |

| Figure 41 - Sync Input Timing                                                  | 72  |

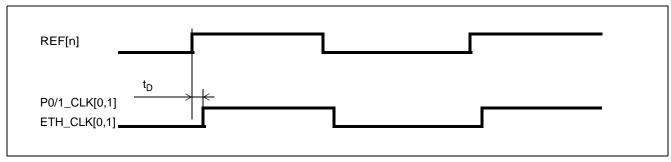

| Figure 42 - Input To Output Timing                                             |     |

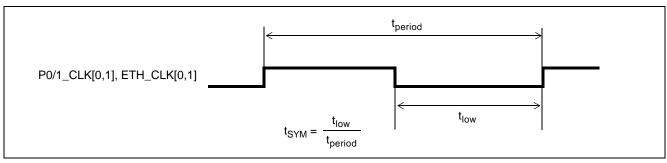

| Figure 43 - Output Duty Cycle                                                  |     |

| Figure 44 - Output Clock Fall and Rise Times                                   | 73  |

| Figure 45 - E1 Output Frame Pulse Timing                                       |     |

| Figure 46 - Typical Reset Timing Diagram.                                      |     |

| Figure 47 - MII Transmit Timing Diagram.                                       |     |

| Figure 48 - MII Receive Timing Diagram                                         |     |

| Figure 49 - MII Transmit Timing Diagram - PHY Emulation Mode                   |     |

| Figure 50 - MII Receive Timing Diagram                                         |     |

| Figure 51 - RMII Transmit Timing Diagram                                       |     |

|                                                                                |     |

## List of Figures

| Figure 52 - RMII Receive Timing Diagram                           | . 82 |

|-------------------------------------------------------------------|------|

| Figure 53 - GMII Transmit Timing Diagram                          | . 83 |

| Figure 54 - GMII Receive Timing Diagram                           | . 84 |

| Figure 55 - TBI Transmit Timing Diagram                           | . 85 |

| Figure 56 - TBI Receive Timing Diagram                            | . 85 |

| Figure 57 - Management Interface Timing for Ethernet Port - Read  | . 86 |

| Figure 58 - Management Interface Timing for Ethernet Port - Write | . 86 |

| Figure 59 - Serial Peripheral Interface Timing - LSB First Mode   | . 87 |

| Figure 60 - Serial Peripheral Interface Timing - MSB First Mode   | . 87 |

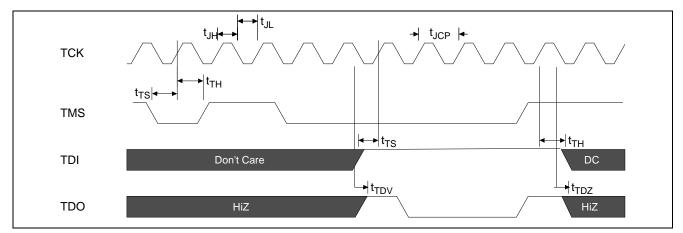

| Figure 61 - JTAG Signal Timing                                    | . 88 |

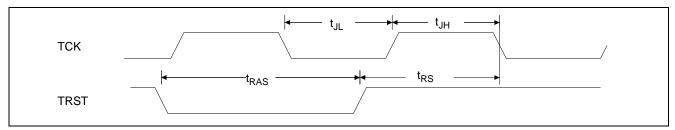

| Figure 62 - JTAG Clock and Reset Timing.                          | . 88 |

## List of Figures

| Table 1 - ZL30316 Ball Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 13 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 2 - Gigabit Ethernet Ports Signal Mapping in Different Operation Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 35 |

| Table 3 - MDIO Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 41 |

| Table 4 - DPLL Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 46 |

| Table 5 - DPLL1 Loop Bandwidth Settings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 48 |

| Table 6 - DPLL1 Pull-in Range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 49 |

| Table 7 - DPLL Phase Slope Limiting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 49 |

| Table 8 - Set of Pre-Defined Auto-Detect Clock Frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 50 |

| Table 9 - Set of Pre-Defined Auto-Detect Sync Frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 51 |

| Table 10 - Frequency Out of Range Limits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| Table 11 - Supported Output Frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 58 |

| Table 12 - APLL LVCMOS Output Clock Frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 59 |

| Table 13 - P0 Frame Pulse Frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 60 |

| Table 14 - P0 Frame Pulse Widths.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 60 |

| Table 15 - Reset Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 76 |

| Table 16 - MII Transmit Timing - 100 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 77 |

| Table 17 - MII Receive Timing - 100 Mbps.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 78 |

| Table 18 - MII Transmit Timing - 100 Mbps - PHY Emulation Mode         Comparison         Comparison <thcomparison< th=""> <thcomparison< t<="" td=""><td>. 79</td></thcomparison<></thcomparison<> | . 79 |

| Table 19 - MII Receive Timing - 100 Mbps.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 80 |

| Table 20 - RMII Transmit Timing - 100 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 81 |

| Table 21 - RMII Receive Timing - 100 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 82 |

| Table 22 - GMII Transmit Timing - 1000 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 83 |

| Table 23 - GMII Receive Timing - 1000 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 84 |

| Table 24 - TBI Timing - 1000 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 85 |

| Table 25 - MAC Management Timing Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 86 |

| Table 26 - JTAG Interface Timing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 88 |

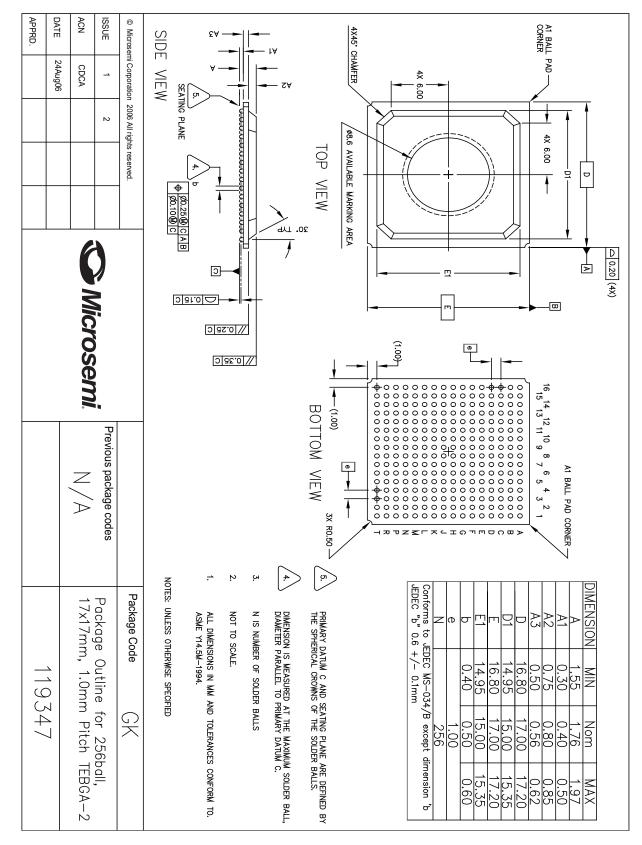

#### **1.0** Physical Specification

The package for the ZL30316 is a 256-ball TEBGA

#### Features:

- Body Size: 17 mm x 17 mm (typ.)

- Ball Count: 256

- Ball Pitch: 1.00 mm (typ.)

- Ball Matrix: 16 x 16

- Ball Diameter: 0.50 mm (typ.)

- Total Package Thickness: 1.76 mm (typ.)

|   | 1                  | 2                  | 3                  | 4                 | 5                 | 6                 | 7                 | 8               | 9                 | 10                | 11              | 12              | 13                | 14                 | 15                | 16              |   |

|---|--------------------|--------------------|--------------------|-------------------|-------------------|-------------------|-------------------|-----------------|-------------------|-------------------|-----------------|-----------------|-------------------|--------------------|-------------------|-----------------|---|

| A | NC                 | NC                 | NC                 | NC                | ETH_<br>CLK[0]    | Ю                 | IC                | ETH_<br>CLK[1]  | V <sub>DD33</sub> | IC                | P1_CLK<br>[0]   | P1_CLK<br>[1]   | NC                | P0_CLK<br>[0]      | P0_FP<br>[0]      | P0_FP<br>[1]    | A |

| в | AV <sub>DD18</sub> | AV <sub>DD33</sub> | AV <sub>DD33</sub> | V <sub>DD33</sub> | NC                | NC                | NC                | NC              | V <sub>DD33</sub> | NC                | NC              | NC              | NC                | V <sub>DD33</sub>  | V <sub>SS</sub>   | P0_CLK<br>[1]   | в |

| с | NC                 | AV <sub>DD18</sub> | AV <sub>DD18</sub> | NC                | V <sub>DD18</sub> | V <sub>DD33</sub> | NC                | NC              | V <sub>DD33</sub> | NC                | NC              | NC              | NC                | V <sub>DD33</sub>  | V <sub>DD33</sub> | ю               | с |

| D | ETH_<br>FILTER     | FILTER_<br>REF[0]  | FILTER_<br>REF[1]  | AV <sub>ss</sub>  | AV <sub>ss</sub>  | V <sub>ss</sub>   | V <sub>ss</sub>   | V <sub>ss</sub> | V <sub>ss</sub>   | V <sub>ss</sub>   | V <sub>ss</sub> | V <sub>ss</sub> | NC                | V <sub>ss</sub>    | V <sub>DD18</sub> | ю               | D |

| E | V <sub>DD33</sub>  | V <sub>DD33</sub>  | NC                 | AV <sub>ss</sub>  | NC                | NC                | NC                | NC              | NC                | NC                | NC              | NC              | V <sub>DD18</sub> | IC<br>(tie low)    | RST_B             | M1_<br>TXER     | E |

| F | M2_<br>MDC         | M2_<br>MDIO        | V <sub>ss</sub>    | AV <sub>ss</sub>  | NC                | V <sub>ss</sub>   | V <sub>ss</sub>   | V <sub>ss</sub> | V <sub>ss</sub>   | V <sub>ss</sub>   | V <sub>ss</sub> | NC              | M1_<br>TXEN       | M1_TXD<br>[6]      | M1_TXD<br>[7]     | M1_<br>GTXCLK   | F |

| G | M1_<br>MDC         | M1_<br>MDIO        | PHY_<br>RST_B      | AV <sub>ss</sub>  | NC                | V <sub>ss</sub>   | V <sub>ss</sub>   | V <sub>ss</sub> | V <sub>ss</sub>   | V <sub>ss</sub>   | V <sub>ss</sub> | M1_TXD<br>[5]   | M1_TXD<br>[4]     | V <sub>DD33</sub>  | M1_TXD<br>[3]     | M1_<br>TXCLK    | G |

| н | V <sub>ss</sub>    | V <sub>DD18</sub>  | NC                 | NC                | V <sub>DD18</sub> | V <sub>ss</sub>   | V <sub>ss</sub>   | V <sub>ss</sub> | V <sub>ss</sub>   | V <sub>ss</sub>   | V <sub>ss</sub> | M1_TXD<br>[0]   | M1_TXD<br>[1]     | M1_TXD<br>[2]      | M1_COL            | M1_<br>RXCLK    | н |

| J | IC                 | IC                 | NC                 | V <sub>DD18</sub> | NC                | V <sub>ss</sub>   | V <sub>ss</sub>   | V <sub>ss</sub> | V <sub>ss</sub>   | V <sub>ss</sub>   | V <sub>ss</sub> | V <sub>ss</sub> | M1_<br>RXER       | V <sub>DD33</sub>  | M1_CRS            | M1_<br>REFCLK   | J |

| к | REF[5]             | REF[6]             | REF[7]             | NC                | NC                | V <sub>ss</sub>   | V <sub>ss</sub>   | V <sub>ss</sub> | V <sub>ss</sub>   | V <sub>ss</sub>   | V <sub>ss</sub> | M1_RXD<br>[4]   | M1_RXD<br>[5]     | M1_RXD<br>[6]      | M1_RXD<br>[7]     | M1_RXDV         | к |

| L | REF[2]             | SYNC[2]            | REF[4]             | V <sub>ss</sub>   | NC                | V <sub>ss</sub>   | V <sub>ss</sub>   | V <sub>ss</sub> | V <sub>ss</sub>   | V <sub>ss</sub>   | V <sub>ss</sub> | M1_RXD<br>[0]   | M1_RXD<br>[1]     | M1_RXD<br>[2]      | M1_RXD<br>[3]     | V <sub>SS</sub> | L |

| м | REF[1]             | SYNC[1]            | REF[3]             | V <sub>DD18</sub> | NC                | IC                | IC                | M2_TXD<br>[3]   | M2_TXD<br>[7]     | IC                | IC              | NC              | TDI               | TDO                | NC                | OSC_O           | м |

| N | SYNC[0]            | NC                 | V <sub>DD33</sub>  | NC                | NC                | M2_RXD<br>[4]     | M2_<br>RXDV       | M2_TXD<br>[2]   | M2_TXD<br>[6]     | V <sub>DD33</sub> | INT0_B          | IC              | NC                | TMS                | NC                | OSC_I           | N |

| Ρ | REF[0]             | NC                 | NC                 | M2_RXD<br>[1]     | M2_RXD<br>[5]     | M2_<br>RXER       | M2_COL            | M2_TXD<br>[1]   | M2_TXD<br>[5]     | V <sub>ss</sub>   | IC              | INT1_B          | NC                | IC<br>(tie low)    | тск               | TRST_B          | Ρ |

| R | NC                 | NC                 | V <sub>ss</sub>    | M2_RXD<br>[2]     | M2_RXD<br>[6]     | M2_CRS            | V <sub>DD33</sub> | M2_TXD<br>[0]   | M2_TXD<br>[4]     | M2_<br>TXER       | CS_B            | so              | V <sub>DD18</sub> | AV <sub>ss</sub>   | NC                | NC              | R |

| т | DPLL2_<br>IN_REF   | V <sub>DD18</sub>  | M2_RXD<br>[0]      | M2_RXD<br>[3]     | M2_RXD<br>[7]     | M2_<br>REFCLK     | M2_<br>RXCLK      | M2_<br>TXCLK    | M2_<br>GTXCLK     | M2_<br>TXEN       | SCLK            | SI              | V <sub>ss</sub>   | AV <sub>DD18</sub> | NC                | NC              | т |

|   | 1                  | 2                  | 3                  | 4                 | 5                 | 6                 | 7                 | 8               | 9                 | 10                | 11              | 12              | 13                | 14                 | 15                | 16              | • |

#### Figure 2 - ZL30316 Package View and Ball Positions

## ZL30316

ZL30316 Signal

Name

$V_{SS}$

Ball #

F7

| ZL30316 Signal<br>Name       |  |  |  |  |

|------------------------------|--|--|--|--|

| NC                           |  |  |  |  |

| ETH_CLK[0]                   |  |  |  |  |

| IC                           |  |  |  |  |

| IC                           |  |  |  |  |

| ETH_CLK[1]                   |  |  |  |  |

| V <sub>DD33</sub>            |  |  |  |  |

| IC                           |  |  |  |  |

| P1_CLK[0]                    |  |  |  |  |

| P1_CLK[1]                    |  |  |  |  |

| NC                           |  |  |  |  |

| P0_CLK[0]                    |  |  |  |  |

| P0_FP[0]                     |  |  |  |  |

| P0_FP[1]                     |  |  |  |  |

| AV <sub>DD18</sub>           |  |  |  |  |

| AV <sub>DD33</sub>           |  |  |  |  |

| AV <sub>DD33</sub>           |  |  |  |  |

| V <sub>DD33</sub>            |  |  |  |  |

| NC                           |  |  |  |  |

| V <sub>DD33</sub>            |  |  |  |  |

| NC                           |  |  |  |  |

| NC                           |  |  |  |  |

| NC<br>NC                     |  |  |  |  |

|                              |  |  |  |  |

| V <sub>DD33</sub>            |  |  |  |  |

| V <sub>SS</sub><br>P0_CLK[1] |  |  |  |  |

| NC                           |  |  |  |  |

| AV <sub>DD18</sub>           |  |  |  |  |

| AV <sub>DD18</sub>           |  |  |  |  |

| NC                           |  |  |  |  |

| V <sub>DD18</sub>            |  |  |  |  |

| V <sub>DD33</sub>            |  |  |  |  |

| NC                           |  |  |  |  |

| NC                           |  |  |  |  |

| V <sub>DD33</sub>            |  |  |  |  |

| NC                           |  |  |  |  |

| NC                           |  |  |  |  |

|                              |  |  |  |  |

Table 1 - ZL30316 Ball Assignments

| Ball # | ZL30316 Signal<br>Name |

|--------|------------------------|

| C12    | NC                     |

| C13    | NC                     |

| C14    | V <sub>DD33</sub>      |

| C15    | V <sub>DD33</sub>      |

| C16    | IC                     |

| D1     | ETH_FILTER             |

| D2     | FILTER_REF[0]          |

| D3     | FILTER_REF[1]          |

| D4     | AV <sub>SS</sub>       |

| D5     | AV <sub>SS</sub>       |

| D6     | V <sub>SS</sub>        |

| D7     | V <sub>SS</sub>        |

| D8     | V <sub>SS</sub>        |

| D9     | V <sub>SS</sub>        |

| D10    | V <sub>SS</sub>        |

| D11    | V <sub>SS</sub>        |

| D12    | V <sub>SS</sub>        |

| D13    | NC                     |

| D14    | V <sub>SS</sub>        |

| D15    | V <sub>DD18</sub>      |

| D16    | IC                     |

| E1     | V <sub>DD33</sub>      |

| E2     | V <sub>DD33</sub>      |

| E3     | NC                     |

| E4     | AV <sub>SS</sub>       |

| E5     | NC                     |

| E6     | NC                     |

| E7     | NC                     |

| E8     | NC                     |

| E9     | NC                     |

| E10    | NC                     |

| E11    | NC                     |

| E12    | NC                     |

| E13    | V <sub>DD18</sub>      |

| E14    | IC (tie low)           |

| E15    | RST_B                  |

| E16    | M1_TXER                |

| F1     | M2_MDC                 |

| F2     | M2_MDIO                |

| F3     | V <sub>SS</sub>        |

| F4     | AV <sub>SS</sub>       |

| F5     | NC                     |

| F6     | V <sub>SS</sub>        |

| Tabl   | e 1 - ZL30316 Ball     |

|     | - 33                |

|-----|---------------------|

| F8  | V <sub>SS</sub>     |

| F9  | V <sub>SS</sub>     |

| F10 | V <sub>SS</sub>     |

| F11 | V <sub>SS</sub>     |

| F12 | NC                  |

| F13 | M1_TXEN             |

| F14 | M1_TXD[6]           |

| F15 | M1_TXD[7]           |

| F16 | M1_GTXCLK           |

| G1  | M1_MDC              |

| G2  | M1_MDIO             |

| G3  | PHY_RST_B           |

| G4  | AV <sub>SS</sub>    |

| G5  | NC                  |

| G6  | V <sub>SS</sub>     |

| G7  | V <sub>SS</sub>     |

| G8  | V <sub>SS</sub>     |

| G9  | V <sub>SS</sub>     |

| G10 | V <sub>SS</sub>     |

| G11 | V <sub>SS</sub>     |

| G12 | M1_TXD[5]           |

| G13 | M1_TXD[4]           |

| G14 | V <sub>DD33</sub>   |

| G15 | M1_TXD[3]           |

| G16 | M1_TXCLK            |

| H1  | V <sub>SS</sub>     |

| H2  | V <sub>DD18</sub>   |

| H3  | NC                  |

| H4  | NC                  |

| H5  | V <sub>DD18</sub>   |

| H6  | V <sub>SS</sub>     |

| H7  | V <sub>SS</sub>     |

| H8  | V <sub>SS</sub>     |

| H9  | V <sub>SS</sub>     |

| H10 | V <sub>SS</sub>     |

| H11 | V <sub>SS</sub>     |

| H12 | M1_TXD[0]           |

| H13 | M1_TXD[1]           |

| H14 | M1_TXD[2]           |