## ZL50405 Managed5-Port 10/100 M Ethernet Switch

Data Sheet

January 2005

## Features

- Integrated Single-Chip 10/100 Ethernet Switch

- Four 10/100 Mbps auto-negotiating Fast Ethernet (FE) ports with RMII, MII, GPSI, Reverse MII & Reverse GPSI interface options

- One 10/100 Mbps auto-negotiating port with MII interface option, that can be used as a WAN uplink or as a 9th port

- a 10/100 Mbps Fast Ethernet (FE) CPU port with Reverse MII interface option

- Embedded 2 Mbits (256 KBytes) internal memory

- supports up to 4 K byte frames

- L2 switching

- MAC address self learning, up to 4 K MAC addresses using internal table

- Supports IP Multicast with IGMP snooping, up to 4 K IP Multicast groups

- · Supports the following spanning standards

- IEEE 802.1D spanning tree

- IEEE 802.1w rapid spanning tree

- Supports Ethernet multicasting and broadcasting and flooding control

- VLAN Support

- Supports port-based VLAN and tagged-based

## Ordering Information

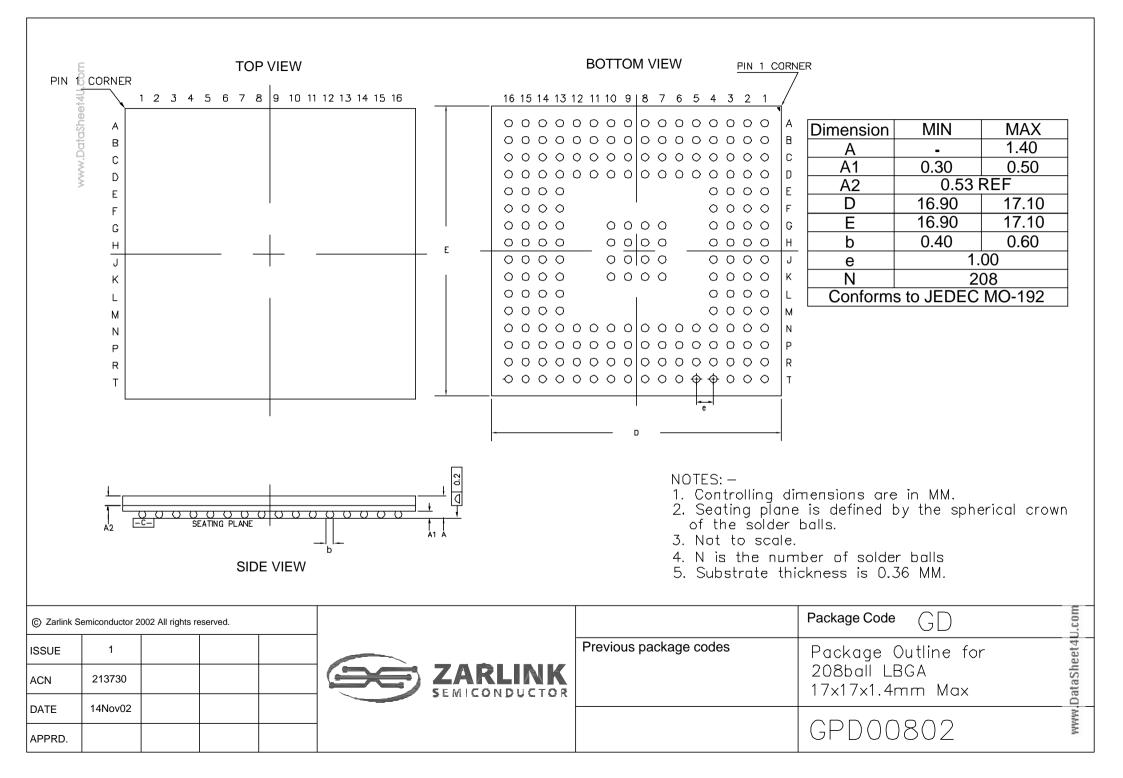

ZL50405GDC

208 Pin LBGA

-40°C to +85°C

VLAN (IEEE 802.1Q), up to 4 K VLANs

- Supports both shared VLAN learning (SVL) and independent VLAN learning (IVL)

- CPU access supports the following interface options:

- 8/16-bit parallel and Serial+MII interface in managed mode

- Serial interface in lightly managed mode, or in unmanaged mode with optional I<sup>2</sup>C EEPROM interface

- Failover Features

- Rapid link failure detection using hardware-generated heartbeat packets

- link failover in less than 50 ms

- Rate Control (both ingress and egress)

- · Bandwidth rationing, Bandwidth on demand,

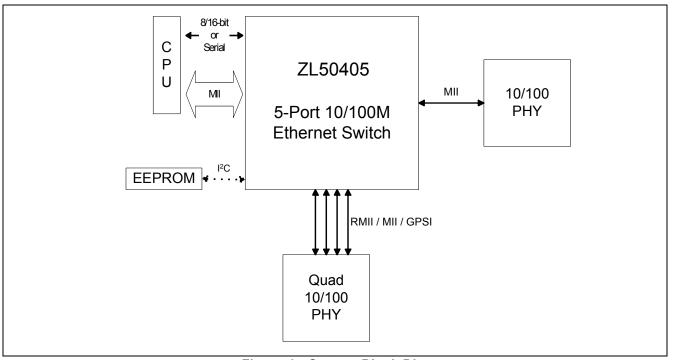

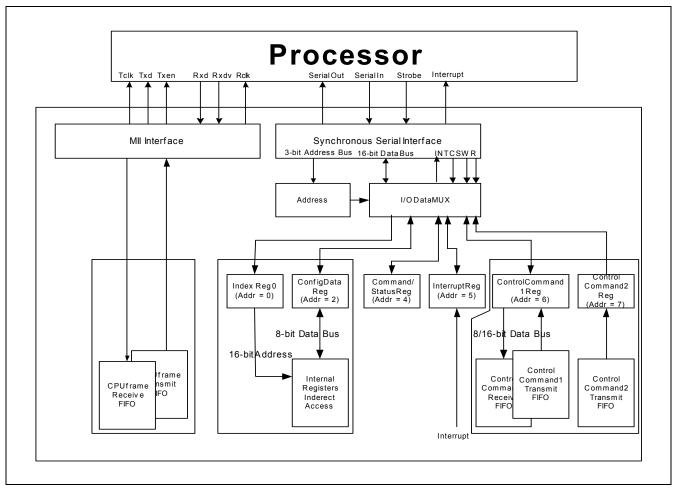

#### Figure 1 - System Block Diagram

Zarlink Semiconductor Inc. Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2003-2005, Zarlink Semiconductor Inc. All Rights Reserved.

- SLA (Service Level Agreement)

- Smooth out traffic to uplink port

- Ingress Rate Control

- Back pressure

- Flow Control

- WRED (Weighted Random Early Discard)

- Egress Rate Control

- Down to 16 kbps Rate Control granularity

- Per queue traffic shaper on uplink port

- Packet Filtering and Port Security

- Static address filtering for source and/or destination MAC

- Static MAC address not subject to aging

- Secure mode freezes MAC address learning (each port may independently use this mode)

- Supports port authentication (IEEE 802.1x)

- QoS Support

- Supports IEEE 802.1p/Q Quality of Service with 2 transmission priority queues (4 for uplink port), with strict priority and/or WFQ service disciplines

- Provides 2 levels of dropping precedence with WRED mechanism

- User controls the WRED thresholds.

- Buffer management: per class and per port buffer reservations

- Port-based priority: VLAN priority in a tagged frame can be overwritten by the priority of Port VLAN ID

- Supports per-system option to enable flow control for best effort frames even on QoS enabled ports

- Classification based on:

- · Port based priority

- VLAN Priority field in VLAN tagged frame

- DS/TOS field in IP packet

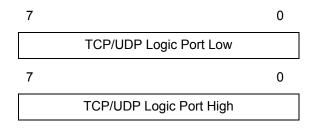

- UDP/TCP logical ports: 8 hard-wired and 8 programmable ports, including one programmable range

- The precedence of the above classifications is programmable

- Supports IEEE 802.3ad link aggregation

- Up to 8 trunk groups, with up to 4 ports per group

- Supports load sharing among trunk ports based on:

- Source port

- Source and/or destination MAC address

- Supports module hot swap on all ports

- MIB Statistics counters for all ports

- Full Duplex Ethernet IEEE 802.3x Flow Control

- Backpressure flow control for Half Duplex ports

- Hardware auto-negotiation through MII management interface (MDIO) for Ethernet ports

- · Built-in reset logic triggered by system malfunction

- Built-In Self Test for internal SRAM

- IEEE-1149.1 (JTAG) test port

## Description

The ZL50405 is a low density, low cost, high performance, non-blocking Ethernet switch chip. A single chip provides 4 ports at 10/100 Mbps, 1 uplink port at 10/100 Mbps, and a CPU interface for managed, lightly managed and unmanaged switch applications. The chip supports up to 4 K MAC addresses and up to 4 K tagged-based Virtual LANs (VLANs).

With strict priority and/or WFQ transmission scheduling and WRED dropping schemes, the ZL50405 provides powerful QoS functions for various multimedia and mission-critical applications. The chip provides 2 transmission priorities (4 priorities for uplink port) and 2 levels of dropping precedence. Each packet is assigned a transmission priority and dropping precedence based on the VLAN priority field in a VLAN tagged frame, or the DS/TOS field, or the UDP/TCP logical port fields in IP packets. The ZL50405 recognizes a total of 16 UDP/TCP logical ports, 8 hard-wired and 8 programmable (including one programmable range).

The ZL50405 provides the ability to monitor a link, detect a simple link failure, and provide notification of the failure to the CPU. The CPU can then failover that link to an alternate link.

The ZL50405 supports up to 8 groups of port trunking/load sharing. Each group can contain up to 4 ports. Port trunking/load sharing can be used to group ports between interlinked switches to increase the effective network bandwidth.

In half-duplex mode, all ports support backpressure flow control, to minimize the risk of losing data during long activity bursts. In full-duplex mode, IEEE 802.3x flow control is provided. The ZL50405 also supports a per-system option to enable flow control for best effort frames, even on QoS-enabled ports.

Statistical information for SNMP and the Remote Monitoring Management Information Base (RMON MIB) are collected independently for all ports. Access to these statistical counters/registers is provided via the CPU interface. SNMP Management frames can be received and transmitted via the CPU interface, creating a complete network management solution.

The ZL50405 is fabricated using 0.18 micron technology. The ZL50405 is packaged in a 208-pin Ball Grid Array package.

|        | GA and Ball Signal Descriptions                                   |    |

|--------|-------------------------------------------------------------------|----|

| 1.     | 1 BGA Views (Top-View)                                            | 11 |

| 1.     | 2 Power and Ground Distribution                                   | 11 |

| 1.     | 3 Ball Signal Descriptions.                                       | 12 |

|        | 4 Signal Mapping and Internal pull-up/Down Configuration          |    |

| 1      | 5 Bootstrap Options                                               | 19 |

|        | 1.5.1 Recommended Default Boostrap Settings.                      |    |

| 1      | 6 Default Switch Configuration and Initialization Sequence        |    |

|        |                                                                   |    |

|        | lock Functionality                                                |    |

|        | 1 Internal Memory.                                                |    |

| 2.     | 2 MAC Modules                                                     |    |

|        | 2.2.1 RMII MAC Module (RMAC)                                      | 22 |

|        | 2.2.1.1 GPSI (7WS) Interface                                      | 23 |

|        | 2.2.2 CPU MAC Module (CMAC)                                       | 23 |

|        | 2.2.3 MII MAC Module (MMAC)                                       |    |

|        | 2.2.4 PHY Addresses                                               |    |

| 2      | 3 Management Module                                               |    |

|        |                                                                   |    |

|        | 4 Frame Engine                                                    |    |

|        | 5 Search Engine                                                   |    |

|        | 6 Heartbeat Packet Generation and Response                        |    |

|        | 7 Timeout Reset Monitor                                           |    |

| 2.     | 8 JTAG                                                            | 24 |

| 3.0 M  | anagement and Configuration                                       | 25 |

|        | 1 Register Configuration, Frame Transmission, and Frame Reception |    |

| •••    | 3.1.1 Register Configuration                                      |    |

|        | 3.1.2 Rx/Tx of Standard Ethernet Frames                           |    |

|        |                                                                   |    |

| ~      | 3.1.3 Control Frames                                              |    |

| 3.     | 2 I2C Interface                                                   |    |

|        | 3.2.1 Start Condition                                             |    |

|        | 3.2.2 Address                                                     |    |

|        | 3.2.3 Data Direction                                              |    |

|        | 3.2.4 Acknowledgment                                              | 29 |

|        | 3.2.5 Data                                                        | 29 |

|        | 3.2.6 Stop Condition                                              | 29 |

| 3.     | 3 Synchronous Serial Interface                                    |    |

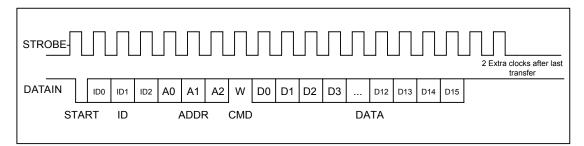

| •••    | 3.3.1 Write Command                                               |    |

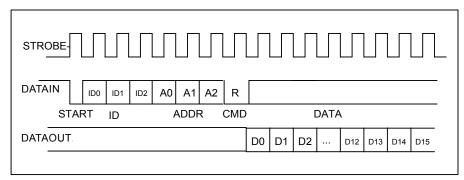

|        | 3.3.2 Read Command                                                |    |

|        |                                                                   |    |

|        | ata Forwarding Protocol.                                          |    |

|        | 1 Unicast Data Frame Forwarding                                   |    |

|        | 2 Multicast Data Frame Forwarding                                 |    |

| 4.     | 3 Frame Forwarding To and From CPU                                | 32 |

| 5.0 Se | earch Engine                                                      | 33 |

|        | 1 Search Engine Overview                                          |    |

|        | 2 Basic Flow                                                      |    |

|        | 3 Search, Learning, and Aging.                                    |    |

| 5.     |                                                                   |    |

|        | 5.3.1 MAC Search.                                                 |    |

|        | 5.3.2 Learning                                                    |    |

|        | 5.3.3 Aging                                                       |    |

|        | 4 MAC Address Filtering                                           |    |

|        | 5 Protocol Filtering                                              |    |

| 5.     | 6 Logical Port Filtering                                          | 34 |

|        | 7 Quality of Service                                              |    |

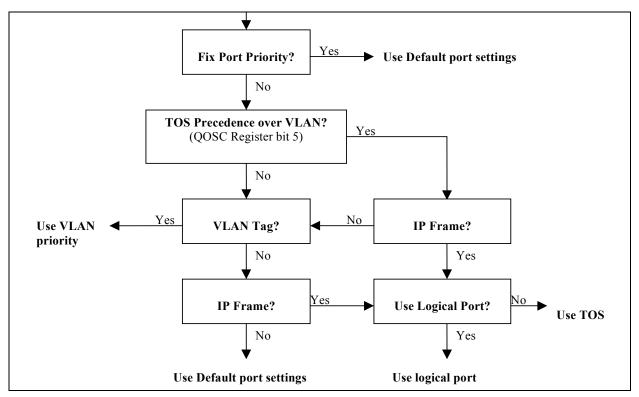

| 5.8 Priority Classification Rule                        | . 35 |

|---------------------------------------------------------|------|

| 6.0 Frame Engine                                        | . 37 |

| 6.1 Data Forwarding Summary                             | . 37 |

| 6.2 Frame Engine Details                                | . 37 |

| 6.2.1 FCB Manager.                                      | . 37 |

| 6.2.2 Rx Interface                                      |      |

| 6.2.3 RxDMA.                                            |      |

| 6.2.4 TxQ Manager                                       |      |

| 6.2.5 Port Control                                      |      |

| 6.2.6 TxDMA                                             |      |

| 7.0 Quality of Service and Flow Control                 |      |

| 7.1 Model                                               |      |

| 7.2 Two QoS Configurations                              |      |

|                                                         |      |

| 7.2.1 Strict Priority.                                  |      |

| 7.2.2 Weighted Fair Queuing                             |      |

| 7.3 WRED Drop Threshold Management Support              |      |

| 7.4 Shaper                                              |      |

| 7.5 Rate Control                                        |      |

| 7.6 Buffer Management.                                  |      |

| 7.6.1 Dropping When Buffers Are Scarce                  |      |

| 7.7 Flow Control Basics.                                |      |

| 7.7.1 Unicast Flow Control                              |      |

| 7.7.2 Multicast Flow Control                            |      |

| 7.8 Mapping to IETF Diffserv Classes                    | . 43 |

| 7.9 Failover Backplane Feature.                         | . 44 |

| 8.0 Port Trunking                                       | . 45 |

| 8.1 Features and Restrictions                           |      |

| 8.2 Unicast Packet Forwarding                           | . 45 |

| 8.3 Multicast Packet Forwarding                         |      |

| 9.0 Traffic Mirroring                                   |      |

| 9.1 Mirroring Features                                  |      |

| 9.2 Using port mirroring for loop back                  |      |

|                                                         |      |

| 10.0 Clocks                                             |      |

|                                                         |      |

| 10.1.1 System Clock (SCLK) speed requirement            |      |

| 10.1.2 RMAC Reference Clock (M_CLK) speed requirement.  |      |

| 10.1.3 MMAC Reference Clock (REF_CLK) speed requirement |      |

| 10.1.4 JTAG Test Clock (TCK) speed requirements.        |      |

| 10.2 Clock Generation.                                  |      |

| 10.2.1 MDC                                              |      |

| 10.2.2 SCL                                              |      |

| 10.2.3 Ethernet Interface Clocks.                       |      |

| 11.0 Hardware Statistics Counters                       |      |

| 11.1 Hardware Statistics Counters List                  |      |

| 11.2 IEEE 802.3 HUB Management (RFC 1516)               | . 50 |

| 11.2.1 Event Counters                                   |      |

| 11.2.1.1 ReadableOctet                                  | . 50 |

| 11.2.1.2 ReadableFrame                                  | . 51 |

| 11.2.1.3 FCSErrors.                                     | . 51 |

| 11.2.1.4 AlignmentErrors                                |      |

|                                                      | - 4 |

|------------------------------------------------------|-----|

| 11.2.1.5 FrameTooLongs                               |     |

| 11.2.1.6 ShortEvents                                 |     |

| 11.2.1.7 Runts                                       |     |

| 11.2.1.8 Collisions                                  |     |

| 11.2.1.9 LateEvents                                  |     |

| 11.2.1.10 VeryLongEvents                             |     |

| 11.2.1.11 DataRateMisatches                          |     |

| 11.2.1.12 AutoPartitions                             |     |

| 11.2.1.13 TotalErrors                                |     |

| 11.3 IEEE 802.1 Bridge Management (RFC 1286)         | 53  |

| 11.3.1 Event Counters                                | 53  |

| 11.3.1.1 InFrames                                    | 53  |

| 11.3.1.2 OutFrames                                   | 53  |

| 11.3.1.3 InDiscards.                                 | 53  |

| 11.3.1.4 DelayExceededDiscards                       |     |

| 11.3.1.5 MtuExceededDiscards                         |     |

| 11.4 RMON – Ethernet Statistic Group (RFC 1757)      |     |

| 11.4.1 Event Counters                                |     |

| 11.4.1.1 Drop Events                                 |     |

| 11.4.1.2 Octets                                      |     |

|                                                      |     |

| 11.4.1.3 BroadcastPkts                               |     |

| 11.4.1.4 MulticastPkts                               |     |

| 11.4.1.5 CRCAlignErrors                              |     |

| 11.4.1.6 UndersizePkts                               |     |

| 11.4.1.7 OversizePkts                                |     |

| 11.4.1.8 Fragments                                   |     |

| 11.4.1.9 Jabbers.                                    |     |

| 11.4.1.10 Collisions                                 |     |

| 11.4.1.11 Packet Count for Different Size Groups     |     |

| 11.5 Miscellaneous Counters                          | 55  |

| 12.0 Register Definition                             | 56  |

| 12.1 ZL50400 Register Description                    |     |

| 12.2 Directly Accessed Registers                     |     |

| 12.2.1 INDEX REG0                                    |     |

| 12.2.2 DATA_FRAME_REG                                |     |

| 12.2.3 CONTROL_FRAME_REG                             |     |

| 12.2.4 COMMAND&STATUS Register                       |     |

| 12.2.5 Interrupt Register                            |     |

|                                                      |     |

| 12.2.6 Control Command Frame Buffer1 Access Register |     |

| 12.2.7 Control Command Frame Buffer2 Access Register |     |

| 12.3 Indirectly Accessed Registers                   |     |

| 12.3.1 (Group 0 Address) MAC Ports Group             |     |

| 12.3.1.1 ECR1Pn: Port n Control Register             |     |

| 12.3.1.2 ECR2Pn: Port n Control Register             |     |

| 12.3.1.3 ECR3Pn: Port n Control Register             |     |

| 12.3.1.4 ECR4Pn: Port n Control Register             |     |

| 12.3.1.5 BUF_LIMIT – Frame Buffer Limit              |     |

| 12.3.1.6 FCC – Flow Control Grant Period             |     |

| 12.3.2 (Group 1 Address) VLAN Group                  |     |

| 12.3.2.1 AVTCL – VLAN Type Code Register Low         | 72  |

| 12.3.2.2 AVTCH – VLAN Type Code Register High        |     |

| 12.3.2.3 PVMAP00_0 – Port 0 Configuration Register 0 | 72  |

|                                                      |     |

| 12.3.2.4 PVMAP00_1 – Port 0 Configuration Register 1                           | 72  |

|--------------------------------------------------------------------------------|-----|

| 12.3.2.5 PVMAP00_3 – Port 0 Configuration Register 3                           |     |

| 12.3.2.6 PVMAPnn_0,1,3 – Ports 1~9 Configuration Registers                     | 73  |

| 12.3.2.7 PVMODE                                                                |     |

| 12.3.3 (Group 2 Address) Port Trunking Groups                                  |     |

| 12.3.3.1 TRUNKn– Trunk Group 0~7.                                              |     |

|                                                                                |     |

| 12.3.3.2 TRUNKn_HASH10 – Trunk group n hash result 1/0 destination port number |     |

| 12.3.3.3 TRUNKn_HASH32 – Trunk group n hash result 3/2 destination port number |     |

| 12.3.3.4 TRUNKn_HASH54 – Trunk group n hash result 5/4 destination port number |     |

| 12.3.3.5 TRUNKn_HASH76 – Trunk group n hash result 7/6 destination port number |     |

| Multicast Hash Registers                                                       | 75  |

| 12.3.3.6 MULTICAST HASHn-0 – Multicast hash result 0~7 mask byte 0             | 76  |

| 12.3.3.7 MULTICAST_HASHn-1 – Multicast hash result 0~7 mask byte 1             | 76  |

| 12.3.4 (Group 3 Address) CPU Port Configuration Group                          |     |

| 12.3.4.1 MAC0 – CPU MAC address byte 0                                         |     |

| 12.3.4.2 MAC1 – CPU MAC address byte 1                                         |     |

| 12.3.4.3 MAC2 – CPU MAC address byte 2                                         |     |

|                                                                                |     |

| 12.3.4.4 MAC3 – CPU MAC address byte 3                                         |     |

| 12.3.4.5 MAC4 – CPU MAC address byte 4                                         |     |

| 12.3.4.6 MAC5 – CPU MAC address byte 5                                         |     |

| 12.3.4.7 INT_MASK0 – Interrupt Mask                                            |     |

| 12.3.4.8 INTP_MASK0 – Interrupt Mask for MAC Port 0,1                          |     |

| 12.3.4.9 INTP_MASKn – Interrupt Mask for MAC Ports 2~9 Registers               | 78  |

| 12.3.4.10 RQS – Receive Queue Select                                           | 78  |

| 12.3.4.11 RQSS – Receive Queue Status                                          | .79 |

| 12.3.4.12 MAC01 – Increment MAC port 0,1 address                               |     |

| 12.3.4.13 MAC23 – Increment MAC port 2,3 address                               |     |

| 12.3.4.14 MAC45 – Increment MAC port 4,5 address                               |     |

| 12.3.4.15 MAC67 – Increment MAC port 6,7 address                               |     |

| 12.3.4.16 MAC9 – Increment MAC port 9 address                                  |     |

| 12.3.4.17 CPUQINS0 - CPUQINS6 – CPU Queue Insertion Command                    |     |

| 12.3.4.18 CPUQINSRPT – CPU Queue Insertion Report                              |     |

|                                                                                |     |

| 12.3.4.19 CPUGRNHDL0 - CPUGRNHDL1 – CPU Allocated Granule Pointer              |     |

| 12.3.4.20 CPURLSINFO0 - CPURLSINFO4 – Receive Queue Status                     |     |

| 12.3.4.21 CPUGRNCTR – CPU Granule Control.                                     |     |

| 12.3.5 (Group 4 Address) Search Engine Group                                   |     |

| 12.3.5.1 AGETIME_LOW – MAC address aging time Low                              |     |

| 12.3.5.2 AGETIME_HIGH –MAC address aging time High                             |     |

| 12.3.5.3 SE_OPMODE – Search Engine Operation Mode                              | 82  |

| 12.3.6 (Group 5 Address) Buffer Control/QOS Group                              | 83  |

| 12.3.6.1 QOSC – QOS Control                                                    | 83  |

| 12.3.6.2 UCC – Unicast Congestion Control                                      | .84 |

| 12.3.6.3 MCC – Multicast Congestion Control                                    |     |

| 12.3.6.4 MCCTH – Multicast Threshold Control.                                  |     |

| 12.3.6.5 RDRC0 – WRED Rate Control 0                                           |     |

| 12.3.6.6 RDRC1 – WRED Rate Control 1                                           |     |

| 12.3.6.7 RDRC2 – WRED Rate Control 2                                           |     |

|                                                                                |     |

| 12.3.6.8 SFCB – Share FCB Size                                                 |     |

| 12.3.6.9 C1RS – Class 1 Reserve Size                                           |     |

| 12.3.6.10 C2RS – Class 2 Reserve Size                                          |     |

| 12.3.6.11 C3RS – Class 3 Reserve Size                                          |     |

| 12.3.6.12 AVPML – VLAN Tag Priority Map                                        | 86  |

| 12.3.6.13 AVPMM – VLAN Priority Map                                               |      |

|-----------------------------------------------------------------------------------|------|

| 12.3.6.14 AVPMH – VLAN Priority Map                                               |      |

| 12.3.6.15 AVDM – VLAN Discard Map                                                 |      |

| 12.3.6.16 TOSPML – TOS Priority Map                                               |      |

| 12.3.6.17 TOSPMM – TOS Priority Map                                               |      |

| 12.3.6.18 TOSPMH – TOS Priority Map                                               | . 88 |

| 12.3.6.19 TOSDML – TOS Discard Map                                                | . 88 |

| 12.3.6.20 USER PROTOCOL n – User Define Protocol 0~7                              |      |

| 12.3.6.21 USER_PROTOCOL_FORCE_DISCARD – User Define Protocol 0~7 Force Discard    | . 89 |

| User Defined Logical Ports and Well Known Ports                                   |      |

| 12.3.6.22 WELL_KNOWN_PORT[1:0]_PRIORITY- Well Known Logic Port 1 and 0 Priority   |      |

| 12.3.6.23 WELL KNOWN PORT 3:2] PRIORITY- Well Known Logic Port 3 and 2 Priority   |      |

| 12.3.6.24 WELL KNOWN PORT[5:4] PRIORITY- Well Known Logic Port 5 and 4 Priority   |      |

| 12.3.6.25 WELL_KNOWN_PORT[7:6]_PRIORITY- Well Known Logic Port 7 and 6 Priority   |      |

| 12.3.6.26 WELL KNOWN PORT ENABLE – Well Known Logic Port 0 to 7 Enables           |      |

| 12.3.6.27 WELL KNOWN PORT FORCE DISCARD – Well Known Logic Port 0~7 Force Discard |      |

| 12.3.6.28 USER_PORT[7:0] [LOwithHIGH] – User Define Logical Port 0~7              |      |

| 12.3.6.29 USER_PORT_[1:0]_PRIORITY - User Define Logic Port 1 and 0 Priority      |      |

| 12.3.6.30 USER_PORT_[3:2]_PRIORITY - User Define Logic Port 3 and 2 Priority      |      |

|                                                                                   |      |

| 12.3.6.31 USER_PORT_[5:4]_PRIORITY - User Define Logic Port 5 and 4 Priority      |      |

| 12.3.6.32 USER_PORT_[7:6]_PRIORITY - User Define Logic Port 7 and 6 Priority      |      |

| 12.3.6.33 USER_PORT_ENABLE[7:0] – User Define Logic Port 0 to 7 Enables           |      |

| 12.3.6.34 USER_PORT_FORCE_DISCARD[7:0] – User Define Logic Port 0~7 Force Discard |      |

| 12.3.6.35 RLOWL – User Define Range Low Bit 7:0                                   |      |

| 12.3.6.36 RLOWH – User Define Range Low Bit 15:8.                                 |      |

| 12.3.6.37 RHIGHL – User Define Range High Bit 7:0                                 |      |

| 12.3.6.38 RHIGHH – User Define Range High Bit 15:8                                |      |

| 12.3.6.39 RPRIORITY – User Define Range Priority                                  |      |

| 12.3.7 (Group 6 Address) MISC Group                                               |      |

| 12.3.7.1 MII_OP0 – MII Register Option 0                                          |      |

| 12.3.7.2 MII_OP1 – MII Register Option 1                                          |      |

| 12.3.7.3 FEN – Feature Register                                                   |      |

| 12.3.7.4 MIIC0 – MII Command Register 0                                           |      |

| 12.3.7.5 MIIC1 – MII Command Register 1                                           | . 96 |

| 12.3.7.6 MIIC2 – MII Command Register 2                                           | . 97 |

| 12.3.7.7 MIIC3 – MII Command Register 3                                           | . 97 |

| 12.3.7.8 MIID0 – MII Data Register 0.                                             | . 97 |

| 12.3.7.9 MIID1 – MII Data Register 1                                              |      |

| 12.3.7.10 USD – One Micro Second Divider                                          |      |

| 12.3.7.11 DEVICE Mode                                                             | . 98 |

| 12.3.7.12 CHECKSUM - EEPROM Checksum                                              |      |

| 12.3.7.13 LHBTimer – Link Heart Beat Timeout Timer                                |      |

| 12.3.7.14 LHBReg0, LHBReg1 - Link Heart Beat OpCode                               |      |

| 12.3.7.15 fMACCReg0, fMACCReg1 - MAC Control Frame OpCode                         |      |

| 12.3.7.16 FCB Base Address Register 0                                             |      |

| 12.3.7.17 FCB Base Address Register 1                                             |      |

| 12.3.7.18 FCB Base Address Register 2                                             |      |

| 12.3.8 (Group 7 Address) Port Mirroring Group                                     |      |

| 12.3.8.1 MIRROR CONTROL – Port Mirror Control Register                            |      |

| 12.3.8.2 MIRROR_DEST_MAC[5:0] – Mirror Destination MAC Address 0~5                |      |

| 12.3.8.3 MIRROR_SRC _MAC[5:0] – Mirror Source MAC Address 0~5                     |      |

| 12.3.8.4 RMAC_MIRROR0 – RMAC Mirror 0                                             |      |

|                                                                                   | 100  |

# **Table of Contents**

| 12.3.8.5 RMAC_MIRROR1 – RMAC Mirror 1                       | 101   |

|-------------------------------------------------------------|-------|

| 12.3.9 (Group 8 Address) Per Port QOS Control               |       |

| 12.3.9.1 FCRn – Port 0~9 Flooding Control Register.         |       |

| 12.3.9.2 BMRCn - Port 0~9 Broadcast/Multicast Rate Control. |       |

| 12.3.9.3 PR100_n – Port 0~7 Reservation.                    |       |

| 12.3.9.4 PR100_CPU – Port CPU Reservation                   |       |

| 12.3.9.5 PRM – Port MMAC Reservation.                       |       |

| 12.3.9.6 PTH100_n – Port 0~7 Threshold                      |       |

| 12.3.9.7 PTH100_CPU – Port CPU Threshold.                   |       |

| 12.3.9.8 PTHG – Port MMAC Threshold                         | 102   |

| 12.3.9.9 QOSC00, QOSC01 - Classes Byte Limit port 0         | 102   |

| 12.3.9.10 QOSC02, QOSC15 - Classes Byte Limit port 1-7      | 103   |

| 12.3.9.11 QOSC16 - QOSC21 - Classes Byte Limit CPO port     | 103   |

| 12.3.9.12 QOSC22 - QOSC27 - Classes Byte Linit MMAC port    |       |

| 12.3.9.14 QOSC36 - QOSC39 - Shaper Control Port MMAC        |       |

| 12.3.10 (Group E Address) System Diagnostic                 |       |

| 12.3.10.1 DTSRL – Test Output Selection                     |       |

| 12.3.10.2 DTSRM – Test Output Selection                     |       |

| 12.3.10.3 TESTOUT0, TESTOUT1 – Testmux Output [7:0], [15:8] |       |

| 12.3.10.4 MASK0-MASK4 – Timeout Reset Mask.                 |       |

| 12.3.10.5 BOOTSTRAP0 – BOOTSTRAP3                           |       |

| 12.3.10.6 PRTFSMST0~9                                       |       |

| 12.3.10.7 PRTQOSST0-PRTQOSST7                               |       |

| 12.3.10.8 PRTQOSST8A, PRTQOSST8B (CPU port).                |       |

| 12.3.10.9 PRTQOSST9A, PRTQOSST9B (MMAC port)                |       |

| 12.3.10.10 CLASSQOSST                                       | . 107 |

| 12.3.10.11 PRTINTCTR                                        |       |

| 12.3.10.12 QMCTRL0~9                                        | 108   |

| 12.3.10.13 QCTRL                                            | 108   |

| 12.3.10.14 BMBISTR0, BMBISTR1                               |       |

| 12.3.10.15 BMControl                                        | . 109 |

| 12.3.10.16 BUFF_RST                                         |       |

| 12.3.10.17 FCB_HEAD_PTR0, FCB_HEAD_PTR1                     |       |

| 12.3.10.18 FCB_TAIL_PTR0, FCB_TAIL_PTR1                     |       |

| 12.3.10.19 FCB_NUM0, FCB_NUM1                               |       |

| 12.3.10.20 BM_RLSFF_CTRL                                    |       |

| 12.3.10.21 BM_RSLFF_INFO[5:0]                               |       |

| 12.3.11 (Group F Address) CPU Access Group                  |       |

| 12.3.11.1 GCR - Global Control Register                     |       |

| 12.3.11.2 DCR - Device Status and Signature Register.       |       |

| 12.3.11.3 DCR1 - Device Status Register 1.                  |       |

| 12.3.11.4 DPST – Device Port Status Register                |       |

| 12.3.11.5 DTST – Data read back register.                   |       |

| 12.3.11.6 DA – Dead or Alive Register.                      |       |

| 0 Characteristics and Timing.                               |       |

| 13.1 Absolute Maximum Ratings.                              |       |

| 13.2 DC Electrical Characteristics                          |       |

| 13.3 Recommended Operating Conditions                       |       |

| 13.4 AC Characteristics and Timing                          |       |

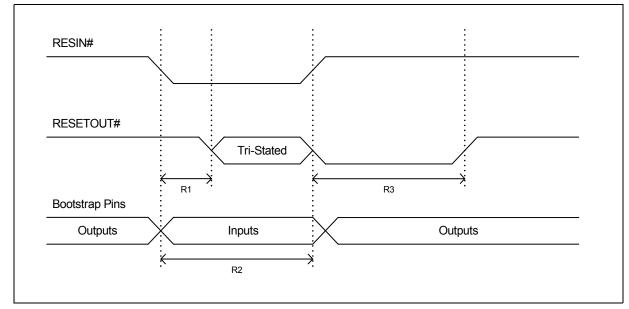

| 13.4.1 Typical Reset & Bootstrap Timing Diagram             |       |

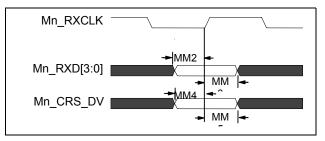

| 13.4.2 Reduced Media Independent Interface                  | ΝÖ    |

13.0

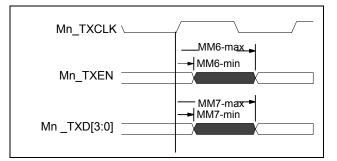

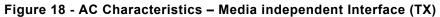

| 13.4.3 Media Independent Interface               | 119 |

|--------------------------------------------------|-----|

| 13.4.4 General Purpose Serial Interface (7-wire) |     |

| 13.4.5 MDIO Input Setup and Hold Timing          | 121 |

| 13.4.6 I <sup>2</sup> C Input Setup Timing       | 122 |

| 13.4.7 Serial Interface Setup Timing.            | 123 |

| 13.4.8 JTAG (IEEE 1149.1-2001)                   | 124 |

| 14.0 Document History                            | 125 |

| 14.1 July 2003                                   | 125 |

| 14.2 November 2003                               | 125 |

| 14.3 February 2004                               | 125 |

| 14.4 August 2004                                 | 125 |

| 14.5 November 2004                               | 125 |

## 1.0 BGA and Ball Signal Descriptions

## 1.1 BGA Views (Top-View)

|   | 1             | 2           | 3           | 4           | 5           | 6           | 7           | 8            | 9            | 10           | 11           | 12           | 13          | 14          | 15            | 16          |   |

|---|---------------|-------------|-------------|-------------|-------------|-------------|-------------|--------------|--------------|--------------|--------------|--------------|-------------|-------------|---------------|-------------|---|

| A | SCLK          | P_CS#       | P_RD#       | P_WE<br>#   | P_DAT<br>A1 | P_DAT<br>A3 | P_DAT<br>A5 | P_DAT<br>A7  | P_DAT<br>A9  | P_DAT<br>A11 | P_DAT<br>A13 | P_DAT<br>A15 | REF_C<br>LK | RSVD        | M9_M<br>TXCLK | M9_TX<br>EN | A |

| В | P_INT<br>#    | P_A0        | P_A1        | P_A2        | P_DAT<br>A0 | P_DAT<br>A2 | P_DAT<br>A4 | P_DAT<br>A6  | P_DAT<br>A8  | P_DAT<br>A10 | P_DAT<br>A12 | P_DAT<br>A14 | тск         | TMS         | RSVD          | M9_RX<br>CK | в |

| С | RESET<br>OUT# | TSTO<br>UT1 | TSTO<br>UT3 | TSTO<br>UT5 | TSTO<br>UT6 | TSTO<br>UT7 | TSTO<br>UT9 | TSTO<br>UT11 | TSTO<br>UT12 | TSTO<br>UT14 | TSTO<br>UT15 | TRST#        | TDI         | RSVD        | M9_C<br>RS    | M9_C<br>OL  | С |

| D | RESIN<br>#    | TSTO<br>UT0 | TSTO<br>UT2 | TSTO<br>UT4 | 3.3V        | SCAN_<br>EN | TSTO<br>UT8 | TSTO<br>UT10 | 1.8V         | TSTO<br>UT13 | TDO          | 3.3V         | RSVD        | RSVD        | M9_RX<br>DV   | RSVD        | D |

| Е | M2_C<br>OL    | M0_C<br>OL  | M1_C<br>OL  | 3.3V        |             |             |             |              |              |              |              |              | 3.3V        | RSVD        | RSVD          | RSVD        | E |

| F | M_MD<br>C     | M_MDI<br>O  | M0_RX<br>D2 | M0_RX<br>D3 |             |             |             |              |              |              |              |              | M9_RX<br>D2 | M9_RX<br>D3 | RSVD          | RSVD        | F |

| G | M0_RX<br>D0   | M0_RX<br>D1 | M0_RX<br>CK | M0_TX<br>D3 |             |             | GND         | GND          | GND          | GND          |              |              | M9_RX<br>D0 | M9_RX<br>D1 | M9_TX<br>D2   | M9_TX<br>D3 | G |

| н | M0_C<br>RS    | M0_TX<br>EN | M0_TX<br>D2 | 1.8V        |             |             | GND         | GND          | GND          | GND          |              |              | 1.8V        | RSVD        | M9_TX<br>D0   | M9_TX<br>D1 | н |

| J | M0_TX<br>D0   | M0_TX<br>D1 | M0_TX<br>CK | M1_RX<br>D3 |             |             | GND         | GND          | GND          | GND          |              |              | RSVD        | RSVD        | RSVD          | RSVD        | J |

| к | M1_RX<br>D0   | M1_RX<br>D1 | M1_RX<br>D2 | M1_RX<br>CK |             |             | GND         | GND          | GND          | GND          |              |              | RSVD        | RSVD        | RSVD          | RSVD        | к |

| L | M1_C<br>RS    | M1_TX<br>EN | M1_TX<br>D2 | M1_TX<br>D3 |             |             |             |              | 1            |              | 1            |              | RSVD        | RSVD        | RSVD          | RSVD        | L |

| М | M1_TX<br>D0   | M1_TX<br>D1 | M1_TX<br>CK | 3.3V        |             |             |             |              |              |              |              |              | 3.3V        | RSVD        | RSVD          | RSVD        | М |

| N | M2_RX<br>D3   | M2_TX<br>CK | M2_TX<br>D3 | M3_RX<br>D3 | 3.3V        | M3_TX<br>D3 | 1.8V        | RSVD         | RSVD         | RSVD         | RSVD         | RSVD         | RSVD        | RSVD        | RSVD          | RSVD        | N |

| Ρ | M2_RX<br>D2   | M2_RX<br>CK | M2_TX<br>D2 | M3_RX<br>D2 | M3_RX<br>CK | M3_TX<br>D2 | M3_C<br>OL  | RSVD         | RSVD         | RSVD         | RSVD         | RSVD         | RSVD        | RSVD        | RSVD          | RSVD        | Ρ |

| R | M2_RX<br>D1   | M2_TX<br>EN | M2_TX<br>D1 | M3_RX<br>D1 | M3_TX<br>EN | M3_TX<br>D1 | M_CLK       | RSVD         | RSVD         | RSVD         | RSVD         | RSVD         | RSVD        | RSVD        | RSVD          | RSVD        | R |

| т | M2_RX<br>D0   | M2_C<br>RS  | M2_TX<br>D0 | M3_RX<br>D0 | M3_C<br>RS  | M3_TX<br>D0 | M3_TX<br>CK | RSVD         | RSVD         | RSVD         | RSVD         | RSVD         | RSVD        | RSVD        | RSVD          | RSVD        | т |

|   | 1             | 2           | 3           | 4           | 5           | 6           | 7           | 8            | 9            | 10           | 11           | 12           | 13          | 14          | 15            | 16          |   |

## 1.2 Power and Ground Distribution

| G7-10, H7-10, J7-10, K7-10       | GND  | V <sub>SS</sub> | Ground     |

|----------------------------------|------|-----------------|------------|

| D5, D12, E4, E13, M4, M13,<br>N5 | 3.3V | V <sub>CC</sub> | I/O Power  |

| D9, H4, H13, N7                  | 1.8V | V <sub>DD</sub> | Core Power |

## 1.3 Ball Signal Descriptions

All pins are CMOS type; all Input Pins are 5 Volt tolerance; and all Output Pins are 3.3 CMOS drive. Notes

| # =         | Active low signal                                                                                       |

|-------------|---------------------------------------------------------------------------------------------------------|

| Input =     | Input signal                                                                                            |

| Input-ST =  | Input signal with Schmitt-Trigger                                                                       |

| Output =    | Output signal (Tri-State driver)                                                                        |

| I/O-TS =    | Input & Output signal with Tri-State driver                                                             |

| pull-up =   | Weak internal pull-up (nominal 100K ohm)                                                                |

|             | (refer to Section 1.4 on page 17 as some internal pull-ups are not enabled in certain configurations)   |

| pull-down = | Weak internal pull-down (nominal 100K ohm)                                                              |

|             | (refer to Section 1.4 on page 17 as some internal pull-downs are not enabled in certain configurations) |

#### **Ball Signal Description Table**

| Ball No(s)                                                                    | Symbol          | I/O                    | Description                                                       |  |  |  |

|-------------------------------------------------------------------------------|-----------------|------------------------|-------------------------------------------------------------------|--|--|--|

| 16-Bit CPU Bus Interfa                                                        | ace             |                        |                                                                   |  |  |  |

| A12, B12, A11, B11,<br>A10, B10, A9, B9, A8,<br>B8, A7, B7, A6, B6,<br>A5, B5 | P_DATA[15:0]    | I/O-TS<br>with pull-up | Processor Bus Data Bit [15:0]. P_DATA[7:0] is used in 8-bit mode. |  |  |  |

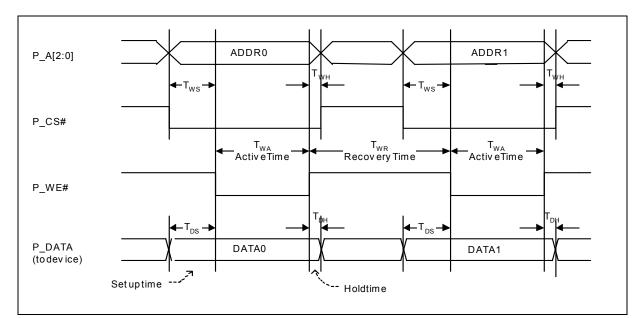

| B4, B3, B2                                                                    | P_A[2:0]        | Input<br>with pull-up  | Processor Bus Address Bit [2:0]                                   |  |  |  |

| A4                                                                            | P_WE#           | Input<br>with pull-up  | CPU Bus-Write Enable                                              |  |  |  |

| A3                                                                            | P_RD#           | Input                  | CPU Bus-Read Enable                                               |  |  |  |

| A2                                                                            | P_CS#           | Input<br>with pull-up  | Chip Select                                                       |  |  |  |

| B1                                                                            | P_INT#          | Output                 | CPU Interrupt                                                     |  |  |  |

| Fast Ethernet Access                                                          | Ports [3:0] MII |                        |                                                                   |  |  |  |

| N4, P4, R4, T4, N1,<br>P1, R1, T1, J4, K3,<br>K2, K1, F4, F3, G2,<br>G1       | M[3:0]_RXD[3:0] | Input<br>with pull-up  | Ports [3:0] – Receive Data Bit [3:0]                              |  |  |  |

| T5, T2, L1, H1                                                                | M[3:0]_CRS_DV   | Input<br>with pull-up  | Ports [3:0] – Carrier Sense and Receive Data Valid                |  |  |  |

### Ball Signal Description Table (continued)

| Ball No(s)                                                                 | Symbol          | I/O                             | Description                                                                                                                                                                                  |

|----------------------------------------------------------------------------|-----------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R5, R2, L2, H2                                                             | M[3:0]_TXEN     | Output, slew                    | Ports [3:0] – Transmit Enable                                                                                                                                                                |

|                                                                            |                 |                                 | This pin also serves as a bootstrap pin.                                                                                                                                                     |

| N6, P6, R6, T6, N3,<br>P3, R3, T3, L4, L3,<br>M2, M1, G4, H3, J2,<br>J1    | M[3:0]_TXD[3:0] | Output, slew                    | Ports [3:0] – Transmit Data Bit [3:0]                                                                                                                                                        |

| P7, E1, E3, E2                                                             | M[3:0]_COL      | Input<br>with pull-down         | Ports[3:0] – Collision                                                                                                                                                                       |

| T7, N2, M3, J3                                                             | M[3:0]_TXCLK    | Input or Output                 | Ports[3:0] – Transmit Clock                                                                                                                                                                  |

|                                                                            |                 | with pull-up                    | This pin in an output if ECR4Pn[0]='1'                                                                                                                                                       |

| P5, P2, K4, G3                                                             | M[3:0]_RXCLK    | Input or Output<br>with pull-up | Ports[3:0] – Receive Clock                                                                                                                                                                   |

|                                                                            |                 |                                 | This pin in an output if ECR4Pn[1]='1'                                                                                                                                                       |

| Fast Ethernet Uplink                                                       | Port MII        |                                 |                                                                                                                                                                                              |

| G16, G15, H16, H15                                                         | M9_TXD[3:0]     | Output                          | Transmit Data Bit [3:0]                                                                                                                                                                      |

| D15                                                                        | M9_RXDV         | Input<br>with pull-up           | Receive Data Valid                                                                                                                                                                           |

| C15                                                                        | M9_CRS          | Input<br>with pull-down         | Carrier Sense                                                                                                                                                                                |

| C16                                                                        | M9_COL          | Input<br>with pull-down         | Collision Detected                                                                                                                                                                           |

| B16                                                                        | M9_RXCLK        | Input or Output                 | Receive Clock                                                                                                                                                                                |

|                                                                            |                 | with pull-up                    | This pin in an output if ECR4P9[1]='1'                                                                                                                                                       |

| F14, F13, G14, G13                                                         | M9_RXD[3:0]     | Input<br>with pull-up           | Receive Data Bit [3:0]                                                                                                                                                                       |

| A16                                                                        | M9_TXEN         | Output<br>with pull-up          | Transmit Data Enable                                                                                                                                                                         |

| A15                                                                        | M9_MTXCLK       | Input<br>with pull-up           | Transmit Clock                                                                                                                                                                               |

| Test Interface                                                             | •               |                                 | · · ·                                                                                                                                                                                        |

| C11, C10, D10, C9,<br>C8, D8, C7, D7, C6,<br>C5, C4, D4, C3, D3,<br>C2, D2 | TSTOUT[15:0]    | Output                          | <ul> <li>[15:4] Reserved</li> <li>[3] EEPROM checksum is good</li> <li>[2] Initialization Completed</li> <li>[1] Memory Self Test in progress</li> <li>[0] Initialization started</li> </ul> |

|                                                                            |                 |                                 | These pins also serve as bootstrap pins.                                                                                                                                                     |

Ball Signal Description Table (continued)

| Ball No(s)                        | Symbol          | I/O                            | Description                                                                                                                               |

|-----------------------------------|-----------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Test Facility                     | 1               | •                              | -                                                                                                                                         |

| C13 TDI                           |                 | Input<br>with pull-up          | JTAG - Test Data In                                                                                                                       |

| C12                               | TRST#           | Input<br>with pull-up          | JTAG - Test Reset                                                                                                                         |

| B13                               | тск             | Input<br>with pull-up          | JTAG - Test Clock                                                                                                                         |

| B14                               | TMS             | Input<br>with pull-up          | JTAG - Test Mode State                                                                                                                    |

| D11                               | TDO             | Output                         | JTAG - Test Data Out                                                                                                                      |

| D6 SCAN_EN                        |                 | Input                          | Scan Enable. Manufacturing test option.                                                                                                   |

|                                   |                 | Must be externally pulled-down | Should be externally pulled-down for proper operation.                                                                                    |

| System Clock, Power,              | and Ground Pins |                                |                                                                                                                                           |

| A1 SCLK                           |                 | Input                          | System Clock. Based on system requirement,<br>SCLK needs to operate at difference<br>frequency.<br>SCLK requires 40/60% duty cycle clock. |

| D9, H4, H13, N7,                  | V <sub>DD</sub> | Power                          | +1.8 Volt DC Supply                                                                                                                       |

| D5, D12, E4, E13, M4,<br>M13, N5, | V <sub>CC</sub> | Power                          | +3.3 Volt DC Supply                                                                                                                       |

| G7-10, H7-10, J7-10,<br>K7-10     | V <sub>SS</sub> | Power Ground                   | Ground                                                                                                                                    |

| Misc.                             | ·               | •                              |                                                                                                                                           |

| D1                                | RESIN#          | Input                          | Reset Input                                                                                                                               |

| C1                                | RESETOUT#       | Output                         | Reset PHY                                                                                                                                 |

| F1                                | M_MDC           | Output                         | MII Management Data Clock                                                                                                                 |

| F2                                | M_MDIO          | I/O-TS<br>with pull-up         | MII Management Data I/O                                                                                                                   |

| R7                                | M_CLK           | Input                          | RMAC Reference Clock                                                                                                                      |

| A13                               | REF_CLK         | Input<br>with pull-up          | MMAC Reference Clock                                                                                                                      |

### Ball Signal Description Table (continued)

| Ball No(s)                                                                                                                                                                                                                                                                                                                                | Symbol      | I/O                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| , L13, K14, L15, L16,<br>N14, P14, R14, T14,<br>N11, P11, R11, T11,<br>N8, P8, R8, T8, K16,<br>T15, T12, T9, K15,<br>R15, R12, R9, J13,<br>K13, J15, J16, N16,<br>P16, R16, T16, N13,<br>P13, R13, T13, N10,<br>P10, R10, T10, H14,<br>M14, M15, M16, J14,<br>N15, N12, N9, L14,<br>P15, P12, P9, E16,<br>E15, F16, F15, D16,<br>B15, A14 | RSVD        | N/A                | Reserved. Leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Bootstrap Pins (1= pu<br>(See "Bootstrap Option                                                                                                                                                                                                                                                                                           | • • • •     |                    | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D2                                                                                                                                                                                                                                                                                                                                        | TSTOUT[0]   | Input (Reset Only) | Enable Debounce of STROBE signal<br>Pullup – Enabled<br>Pulldown - Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| C3, D3, C2                                                                                                                                                                                                                                                                                                                                | TSTOUT[3:1] | Input (Reset Only) | Management interface operation mode:<br>000 – 16-bit parallel interface<br>001 – 8-bit parallel interface<br>010 – Serial with MII as Ethernet frame<br>transfer interface.<br>011 – Serial only. CPU can transmit/receive<br>frames with the serial interface.<br>111 – Unmanaged Serial. No CPU packet can<br>be transmit or received with the serial<br>interface. EEPROM can be used to configure<br>the device at bootup.<br>A one (1) indicates pullup. A zero (0)<br>indicates pulldown. TSTOUT[1] is the Least<br>Significant Bit (LSB). |

| C5, C4, D4                                                                                                                                                                                                                                                                                                                                | TSTOUT[6:4] | Input (Reset Only) | <ul> <li>Device ID. Default address of the device for serial interface. Up to 8 device can be sharing the serial management bus with different device ID.</li> <li>A one (1) indicates pullup. A zero (0) indicates pulldown. TSTOUT[4] is the Least Significant Bit (LSB).</li> </ul>                                                                                                                                                                                                                                                           |

| C6                                                                                                                                                                                                                                                                                                                                        | TSTOUT[7]   | Input (Reset Only) | EEPROM not installed.<br>Pullup: Not installed<br>Pulldown: Installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### Ball Signal Description Table (continued)

| Ball No(s)     | Symbol        | I/O                                                     | Description                                                                                                                                                                        |

|----------------|---------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7             | TSTOUT[8]     | Input (Reset Only)<br>Must be externally<br>pulled-up   | Manufacturing Option. Must be pulled up.                                                                                                                                           |

| C7             | TSTOUT[9]     | Input (Reset Only)                                      | Module Detect<br>Pullup: Enable. In this mode, the device will<br>detect the existence of a PHY (for hot swap<br>purpose).<br>Pulldown: Disable                                    |

| D8             | TSTOUT[10]    | Input (Reset Only)<br>Must be externally<br>pulled-down | Manufacturing Option. Must be pulled down.                                                                                                                                         |

| C8             | TSTOUT[11]    | Input (Reset Only)                                      | Power Saving<br>Pullup: Enable MAC power saving mode<br>Pulldown: Disable MAC power saving mode                                                                                    |

| С9             | TSTOUT[12]    | Input (Reset Only)                                      | Timeout Reset Enable<br>Pullup: Enable<br>Pulldown: Disable                                                                                                                        |

| C11, C10, D10  | TSTOUT[15:13] | Input (Reset Only)<br>Must be externally<br>pulled-up   | Manufacturing Options. Must be pulled-up.                                                                                                                                          |

| R5, R2, L2, H2 | M[3:0]_TXEN   | Input (Reset Only)                                      | User Defined Bootstrap:<br>Usually used in conjuction with Module Detect<br>to determine what interface to use for the<br>inserted module. Can be read from<br>BOOTSTRAP2 register |

1. External pull-up/down resistors are required on all bootstrap pins for proper operation. Recommend 10 K for pull-ups and 1 K for pull-downs.

#### **1.4** Signal Mapping and Internal pull-up/Down Configuration

The ZL50405 Fast Ethernet access ports (0-3) support 3 interface options: RMII, MII & GPSI. The table below summarizes the interface signals required for each interface and how they relate back to the Pin Symbol name shown in the "Ball Signal Description Table" on page 12. It also specifies whether the internal pull-up/down resistor is present for each pin in the specific operating mode.

Notes:

- I Input

- O Output

- U Pullup D - Pulldown

| Fast Ethernet<br>Access Ports<br>Pin Symbol | No<br>Module<br>(Bootstrap<br>TSTOUT9='1') | <b>RMII Mode</b><br>(ECR4Pn[4:3]='11') | <b>MII Mode</b><br>(ECR4Pn[4:3]='01') | GPSI Mode<br>(ECR4Pn[4:3]='00') |  |

|---------------------------------------------|--------------------------------------------|----------------------------------------|---------------------------------------|---------------------------------|--|

| M[3:0]_RXD0                                 | (U)                                        | M[3:0]_RXD0 (I)                        | M[3:0]_RXD0 (I)                       | M[3:0]_RXD (I)                  |  |

| M[3:0]_RXD1                                 | (U)                                        | M[3:0]_RXD1 (I)                        | M[3:0]_RXD1 (I)                       | NC (U)                          |  |

| M[3:0]_RXD2                                 | (U)                                        | NC (U)                                 | M[3:0]_RXD2 (I)                       | NC (U)                          |  |

| M[3:0]_RXD3                                 | (U)                                        | NC (U)                                 | M[3:0]_RXD3 (I)                       | NC (U)                          |  |

| M[3:0]_TXEN                                 | (O)                                        | M[3:0]_TXEN (O)                        | M[3:0]_TXEN (O)                       | M[3:0]_TXEN (O)                 |  |

| M[3:0]_CRS_DV                               | (U)                                        | M[3:0]_CRS_DV (I)                      | M[3:0]_DV (I)                         | M[3:0]_CRS (I)                  |  |

| M[3:0]_TXD0                                 | (O)                                        | M[3:0]_TXD0 (O)                        | M[3:0]_TXD0 (O)                       | M[3:0]_TXD (O)                  |  |

| M[3:0]_TXD1                                 | (O)                                        | M[3:0]_TXD1 (O)                        | M[3:0]_TXD1 (O)                       | NC (O)                          |  |

| M[3:0]_TXD2                                 | (O)                                        | NC (O)                                 | M[3:0]_TXD2 (O)                       | NC (O)                          |  |

| M[3:0]_TXD3                                 | (O)                                        | NC (O)                                 | M[3:0]_TXD3 (O)                       | NC (O)                          |  |

| M[3:0]_COL                                  | (D)                                        | NC (D)                                 | M[3:0]_COL (I)                        | M[3:0]_COL (I)                  |  |

| M[3:0]_TXCLK                                | (U)                                        | NC (U)                                 | M[3:0]_TXCLK (IO)                     | M[3:0]_TXCLK (IO)               |  |

| M[3:0]_RXCLK                                | (U)                                        | NC (U)                                 | M[3:0]_RXCLK (IO)                     | M[3:0]_RXCLK (IO)               |  |

Table 1 - Signal Mapping In Different Operation Mode

The ZL50405 Fast Ethernet uplink port (port 9) supports 1 interface option: MII. The table below summarizes the interface signals required for each interface, and how they relate back to the Pin Symbol name shown in "Ball Signal Description Table" on page 12.

| Fast Ethernet<br>Uplink Port<br>Pin Symbol | No<br>Module<br>(Bootstrap<br>TSTOUT9='1') | MII Mode<br>(ECR4P9[4:3]='11') |

|--------------------------------------------|--------------------------------------------|--------------------------------|

| M9_RXD0                                    | (U)                                        | M9_RXD0 (I)                    |

| M9_RXD1                                    | (U)                                        | M9_RXD1 (I)                    |

| M9_RXD2                                    | (U)                                        | M9_RXD2 (I)                    |

| M9_RXD3                                    | (U)                                        | M9_RXD3 (I)                    |

| M9_RXDV                                    | (U)                                        | M9_RXDV (I)                    |

| M9_CRS                                     | (D)                                        | M9_CRS (I)                     |

| M9_COL                                     | (D)                                        | M9_COL (I)                     |

| M9_RXCLK                                   | (U)                                        | M9_RXCLK (IO)                  |

| M9_TXD0                                    | (O)                                        | M9_TXD0 (O)                    |

| M9_TXD1                                    | (O)                                        | M9_TXD1 (O)                    |

| M9_TXD2                                    | (O)                                        | M9_TXD2 (O)                    |

| M9_TXD3                                    | (O)                                        | M9_TXD3 (O)                    |

| M9_TXEN                                    | (U)                                        | M9_TXEN (O)                    |

| REF_CLK                                    | (U)                                        | REF_CLK (I)                    |

| M9_MTXCLK                                  | (U)                                        | M9_MTXCLK (I)                  |

Table 2 - Signal Mapping In Different Operation Mode

The ZL50405 CPU access support 5 interface options: 8 or 16-bit parallel, serial+MII (port 8), serial only, and unmanaged serial (with optional EEPROM). The table below summarizes the interface signals required for each interface, and how they relate back to the Pin Symbol name shown in "Ball Signal Description Table" on page 12.

| Management<br>Interface<br>Pin Symbol | <b>16-bit CPU</b><br>(TSTOUT[3:1]='000') | 8-bit CPU         Serial with MII           (TSTOUT[3:1]='001')         (TSTOUT[3:1]='010') |                   | Serial Only<br>(TSTOUT[3:1]='011' or '111') |  |

|---------------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------|-------------------|---------------------------------------------|--|

| P_A[0]                                | P_A[0] (I)                               | P_A[0] (I)                                                                                  | NC (U)            | SDA (IOU) (111 only)                        |  |

| P_A[1]                                | P_A[1] (I)                               | P_A[1] (I)                                                                                  | NC (U)            | SCL (OU) (111 only)                         |  |

| P_A[2]                                | P_A[2] (I)                               | P_A[2] (I)                                                                                  | NC (U)            | NC (U)                                      |  |

| P_WE#                                 | P_WE# (I)                                | P_WE# (I)                                                                                   | STROBE (IU)       | STROBE (IU)                                 |  |

| P_RD#                                 | P_RD# (I)                                | P_RD# (I)                                                                                   | DATAOUT (O)       | DATAOUT (O)                                 |  |

| P_CS#                                 | P_CS# (I)                                | P_CS# (I)                                                                                   | DATAIN (IU)       | DATAIN (IU)                                 |  |

| P_INT#                                | P_INT# (O)                               | P_INT# (O)                                                                                  | P_INT# (O)        | P_INT# (O)                                  |  |

| P_DATA0                               | P_DATA0 (IOU)                            | P_DATA0 (IOU)                                                                               | CPU_MII_TXD0 (O)  | NC (U)                                      |  |

| P_DATA1                               | P_DATA1 (IOU)                            | P_DATA1 (IOU)                                                                               | CPU_MII_TXD1 (O)  | NC (U)                                      |  |

| P_DATA2                               | P_DATA2 (IOU)                            | P_DATA2 (IOU)                                                                               | CPU_MII_TXD2 (O)  | NC (U)                                      |  |

| P_DATA3                               | P_DATA3 (IOU)                            | P_DATA3 (IOU)                                                                               | CPU_MII_TXD3 (O)  | NC (U)                                      |  |

| P_DATA4                               | P_DATA4 (IOU)                            | P_DATA4 (IOU)                                                                               | CPU_MII_TXCLK (O) | NC (U)                                      |  |

| P_DATA5                               | P_DATA5 (IOU)                            | P_DATA5 (IOU)                                                                               | CPU_MII_TXEN (O)  | NC (U)                                      |  |

| P_DATA6                               | P_DATA6 (IOU)                            | P_DATA6 (IOU)                                                                               | NC (U)            | NC (U)                                      |  |

| P_DATA7                               | P_DATA7 (IOU)                            | P_DATA7 (IOU)                                                                               | NC (U)            | NC (U)                                      |  |

| P_DATA8                               | P_DATA8 (IOU)                            | NC (U)                                                                                      | CPU_MII_RXD0 (I)  | NC (U)                                      |  |

| P_DATA9                               | P_DATA9 (IOU)                            | NC (U)                                                                                      | CPU_MII_RXD1 (I)  | NC (U)                                      |  |

| P_DATA10                              | P_DATA10 (IOU)                           | NC (U)                                                                                      | CPU_MII_RXD2 (I)  | NC (U)                                      |  |

| P_DATA11                              | P_DATA11 (IOU)                           | NC (U)                                                                                      | CPU_MII_RXD3 (I)  | NC (U)                                      |  |

| P_DATA12                              | P_DATA12 (IOU)                           | NC (U)                                                                                      | CPU_MII_RXCLK (O) | NC (U)                                      |  |

| P_DATA13                              | P_DATA13 (IOU)                           | NC (U)                                                                                      | CPU_MII_RXDV (I)  | NC (U)                                      |  |

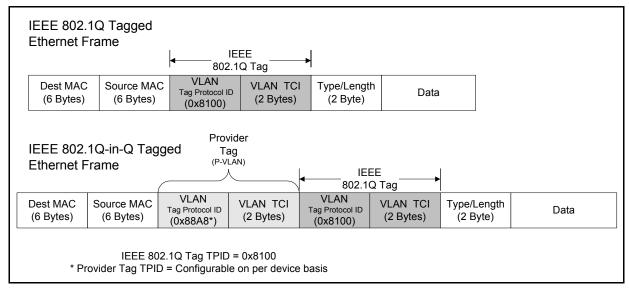

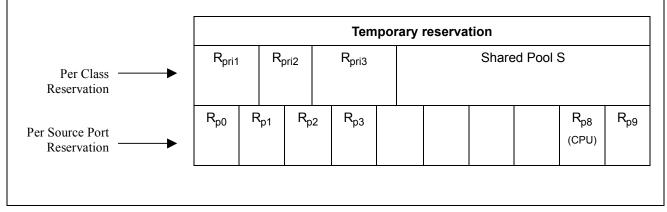

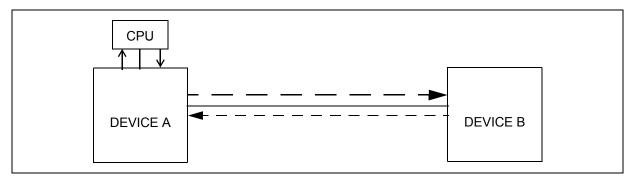

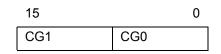

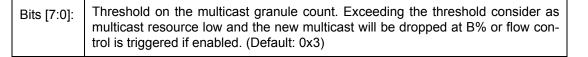

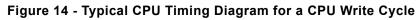

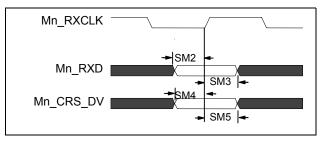

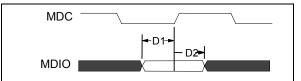

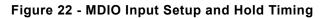

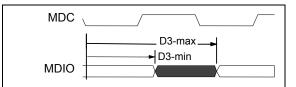

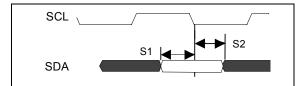

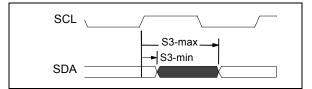

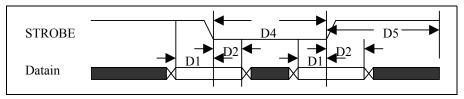

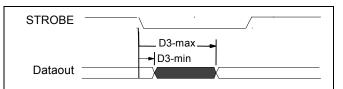

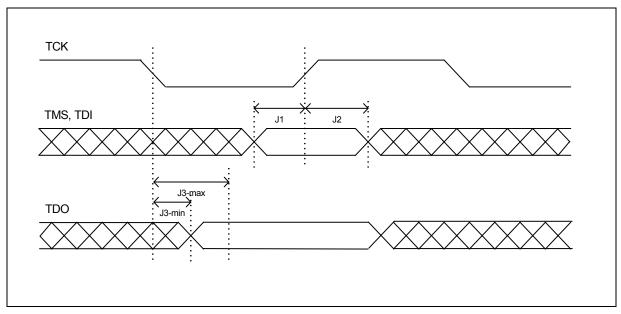

| P_DATA14                              | P_DATA14 (IOU)                           | NC (U)                                                                                      | NC (U)            | NC (U)                                      |  |