## **Advanced Differential Sensor Signal Conditioner**

Datasheet PRELIMINARY

#### **Features**

- Digital compensation of sensor offset, sensitivity, temperature drift and non-linearity

- Accommodates nearly all bridge sensor types (signal spans from 1 up to 275mV/V processable)

- · Digital one-shot calibration: quick and precise

- Selectable compensation temperature T1 source: bridge, thermistor, internal diode or external diode

- Output options: voltage (0...5V), current (4...20mA), PWM, I<sup>2</sup>C, SPI, ZACwire<sup>™</sup> (one-wire-interface), alarm

- Adjustable output resolution (up to 15 bits) versus sampling rate (up to 3.9kHz)

- Selectable bridge excitation: ratiometric voltage, constant voltage or constant current

- Input channel for separate temperature sensor

- Sensor connection and common mode check (Sensor aging detection)

- operation temperature, depending on product version, up to -40...+125℃ (-40...+150℃ derated)

- Supply voltage +2.7V...+5.5V

- Available in SSOP16 or as die

#### **Benefits**

- No external trimming components required

- PC-controlled configuration and calibration via digital bus interface - simple, low cost

- High accuracy (±0.1% FSO @ -25...85℃; ±0.25% FSO @ -40...125℃)

## **Application Circuit (Examples)**

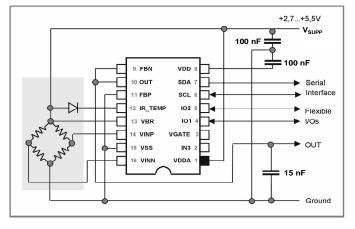

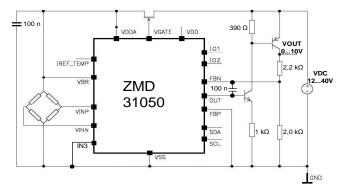

Fig.1: Ratiometric measurement with voltage output, temperature compensation via external diode

#### **Brief Description**

ZMD31050 is a CMOS integrated circuit for highly-accurate amplification and sensor-specific correction of bridge sensor signals. The device provides digital compensation of sensor offset, sensitivity, temperature drift and non-linearity by a 16-bit RISC micro controller running a correction algorithm with correction coefficients stored in non-volatile EEPROM.

The ZMD31050 accommodates virtually any bridge sensor (e.g. piezo-resistive, ceramic-thickfilm or steel membrane based). In addition, the IC can interface a separate temperature sensor.

The bi-directional digital interfaces (I<sup>2</sup>C, SPI, ZACwire<sup>TM</sup>) can be used for a simple PC-controlled one-shot calibration procedure, in order to program a set of calibration coefficients into an on-chip EEPROM. Thus a specific sensor and a ZMD31050 are mated digitally: fast, precise and without the cost overhead associated with laser trimming, or mechanical potentiometer methods.

- S Application kit available (SSOP16 samples, calibration PCB, calibration software, technical documentation)

- Support for industrial mass calibration available

- S Quick circuit customization possible for large production volumes

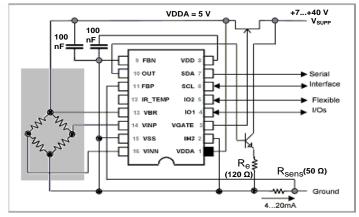

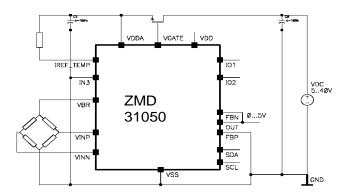

Fig.2: Two-wire-(4 to 20) mA configuration [(7 to 40) V], temperature compensation via internal diode

## Refer also chapter 2 for additional application circuits and details

# **Advanced Differential Sensor Signal Conditioner**

Datasheet PRELIMINARY

## **Contents**

| 1.         | CIRCUIT DESCRIPTION                                                      | 3   |

|------------|--------------------------------------------------------------------------|-----|

| 1.1<br>1.2 |                                                                          |     |

| 1.3        |                                                                          |     |

|            | 1.3.1. Programmable Gain Amplifier                                       |     |

|            | 1.3.2. Analog Sensor Offset Compensation - Analog Zero Point Shift (AZS) |     |

|            | 1.3.3. Measurement Cycle realized by Multiplexer                         |     |

|            | 1.3.4. Analog-to-Digital Converter                                       | 7   |

| 1.4        | 4 SYSTEM CONTROL                                                         | 8   |

|            | 5 OUTPUT STAGE                                                           |     |

|            | 1.5.1. Analog Output                                                     |     |

|            | 1.5.2. Comparator Module (ALARM Output)                                  |     |

|            | 1.5.3. Serial Digital Interface                                          |     |

| 1.6        |                                                                          |     |

| 1.7        | 7 WATCHDOG AND ERROR DETECTION                                           | 11  |

| 2.         | APPLICATION CIRCUIT EXAMPLES                                             | 12  |

|            |                                                                          |     |

| 3.         | ESD/LATCH-UP-PROTECTION                                                  | 13  |

| 4.         | PIN CONFIGURATION AND PACKAGE                                            | 13  |

| 5.         | IC CHARACTERISTICS                                                       | 14  |

| 5.1        | 1 ABSOLUTE MAXIMUM RATINGS                                               | 1.1 |

| 5.2        |                                                                          |     |

| 5.3        |                                                                          |     |

| 5.4        |                                                                          |     |

| 5.5        |                                                                          |     |

| 6.         | TEST                                                                     |     |

| ٠.         |                                                                          | 10  |

| 7.         | RELIABILITY                                                              | 19  |

| 8.         | CUSTOMIZATION                                                            | 19  |

|            |                                                                          |     |

| 9.         | RELATED DOCUMENTS                                                        | 19  |

## **Advanced Differential Sensor Signal Conditioner**

Datasheet PRELIMINARY

#### 1. CIRCUIT DESCRIPTION

#### 1.1 Signal Flow

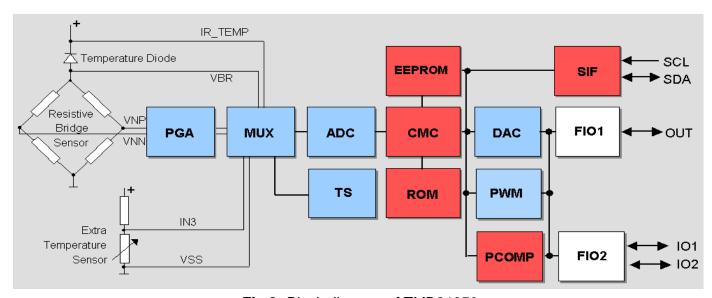

Fig.3: Block diagram of ZMD31050

| PGA    | programmable gain amplifier                                             |

|--------|-------------------------------------------------------------------------|

| MUX    | multiplexer                                                             |

| ADC    | analog-to-digital converter                                             |

| CMC    | calibration microcontroller                                             |

| DAC    | digital-to-analog converter                                             |

| FIO1   | flexible I/O 1: analog out (voltage/current), PWM2,                     |

|        | ZACwire <sup>TM</sup> (one-wire-interface)                              |

| FIO2   | flexible I/O 2: PWM1, SPI data out, SPI slave select, Alarm1, Alarm2SIF |

|        | serial interface: I2C data I/O, SPI data in, clock                      |

| PCOMP  | programmable comparator                                                 |

| EEPROM | for calibration parameters and configuration                            |

| TS     | on-chip temperature sensor (pn-junction)                                |

| ROM    | for correction formula and –algorithm                                   |

| PWM    | PWM module                                                              |

The ZMD31050's signal path is partly analog (blue) and partly digital (red). The analog part is realized differential – this means internal is the differential bridge sensor signal also handled via two signal lines, which are rejected symmetrically around a common mode potential (analog ground = VDDA/2). Consequently it is possible to amplify positive and negative input signals, which are located in the common mode range of the signal input.

The differential signal from the bridge sensor is pre-amplified by the programmable gain amplifier (PGA). The Multiplexer (MUX) transmits the signals from bridge sensor, external diode or separate temperature sensor to the ADC in a certain sequence (instead of the temperature diode the internal pn-junction (TS) can be used optionally). Afterwards the ADC converts these signals into digital values.

## **Advanced Differential Sensor Signal Conditioner**

Datasheet PRELIMINARY

The digital signal correction takes place in the calibration micro-controller (CMC). It is based on a special correction formula located in the ROM and on sensor-specific coefficients (stored into the EEPROM during calibration). Dependent on the programmed output configuration the corrected sensor signal is output as analog value, as PWM signal or in digital format (SPI, I²C, ZACwire™). The output signal is provided at 2 flexible I/O modules (FIO) and at the serial interface (SIF). The configuration data and the correction parameters can be programmed into the EEPROM via the digital interfaces. The modular circuit concept enables fast custom designs varying these blocks and, as a result, functionality and die size.

#### 1.2 Application Modes

For each application a configuration set has to be established (generally prior to calibration) by programming the on-chip EEPROM regarding to the following modes:

- Sensor channel

- Sensor mode: ratiometric voltage or current supply mode.

- Input range: The gain of the analog front end has to be chosen with respect to the maximum sensor signal span and to this has also adjusted the zero point of the ADC

- Additional offset compensation: The extended analog offset compensation has to be enabled if required, e.g. if the sensor offset voltage is near to or larger than the sensor span.

- Resolution/response time: The A/D converter has to be configured for resolution and converting scheme (first or second order). These settings influence the sampling rate, signal integration time and this way the noise immunity. The Sample Order influences the response time too.

- Ability to invert the sensor bridge inputs

- **S** Analog output

- Choice of output method (voltage value, current loop, PWM) for output register 1.

- Optional choice of additional output register 2: PWM via IO1 or alarm out module via IO1/2.

- S Digital communication: The preferred protocol and its parameter have to be set.

- **S** Temperature

- The temperature measure source for the temperature correction has to be chosen.

- The temperature measure source T1 sensor type for the temperature correction has to be chosen (only T1 is usable for correction!!!)

- Optional: the temperature measure channel as the second output has to be chosen.

- S Supply voltage: For non-ratiometric output the voltage regulation has to be configured.

**Note:** Not all possible combinations of settings are allowed (see section 1.5).

The calibration procedure must include

- the set of coefficients of calibration calculation

- and, depending on configuration,

- the adjustment of the extended offset compensation,

- the zero compensation of temperature measurement,

- the adjustment of the bridge current

- and, if necessary,

- the set of thresholds and delays for the alarms and the reference voltage.

## **Advanced Differential Sensor Signal Conditioner**

Datasheet PRELIMINARY

#### 1.3 Analog Front End (AFE)

The analog front end consists of the programmable gain amplifier (PGA), the multiplexer (MUX) and the analog-to-digital converter (ADC).

#### 1.3.1. <u>Programmable Gain Amplifier</u>

The following tables show the adjustable gains, the processable sensor signal spans and the allowed common mode range.

| No. | PGA<br>Gain a <sub>IN</sub> | Gain<br>Amp1 | Gain<br>Amp2 | Gain<br>Amp3 | Max. span<br>V <sub>IN_SP</sub> in mV/V | Input range<br>V <sub>IN_CM</sub> in % VDDA * |

|-----|-----------------------------|--------------|--------------|--------------|-----------------------------------------|-----------------------------------------------|

| 1   | 420                         | 30           | 7            | 2            | 2                                       | 43 - 57                                       |

| 2   | 280                         | 30           | 4,66         | 2            | 3                                       | 40 - 59                                       |

| 3   | 210                         | 15           | 7            | 2            | 4                                       | 43 - 57                                       |

| 4   | 140                         | 15           | 4,66         | 2            | 6                                       | 40 - 59                                       |

| 5   | 105                         | 15           | 3,5          | 2            | 8                                       | 38 - 62                                       |

| 6   | 70                          | 7,5          | 4,66         | 2            | 12                                      | 40 - 59                                       |

| 7   | 52,5                        | 7,5          | 3,5          | 2            | 16                                      | 38 - 62                                       |

| 8   | 35                          | 3,75         | 4,66         | 2            | 24                                      | 40 - 59                                       |

| 9   | 26,3                        | 3,75         | 3,5          | 2            | 32                                      | 38 - 62                                       |

| 10  | 14                          | 1            | 7            | 2            | 50                                      | 43 - 57                                       |

| 11  | 9,3                         | 1            | 4,66         | 2            | 80                                      | 40 - 59                                       |

| 12  | 7                           | 1            | 3,5          | 2            | 100                                     | 38 - 62                                       |

| 13  | 2,8                         | 1            | 1,4          | 2            | 280                                     | 21 - 76                                       |

Table 1: Adjustable gains, resulting sensor signal spans and common mode ranges

#### 1.3.2. Analog Sensor Offset Compensation - Analog Zero Point Shift (AZS)

The ZMD31050 supports two methods of sensor offset cancellation (zero shift):

- digital offset correction

- analog cancellation for large offset values (up to approx 300% of span)

Digital sensor offset correction will be processed at the digital signal correction/conditioning by the CMC. Analog sensor offset pre-compensation will be needed for compensation of large offset values, which would be overdrive the analog signal path by uncompensated gaining. For analog sensor offset pre-compensation a compensation voltage will be added in the analog pre-gaining signal path (coarse offset removal). The analog offset compensation in the AFE can be adjusted by 6 EEPROM bits. It allows an Analog Zero Point Shift up to 300% of the processable signal span.

The zero point shift of the temperature measurements can also be adjusted by 6 EEPROM bits  $(Z_{AZS} = -25...+25)$  and is calculated by:

$$V_{AZS} / VDD_{BR} = k * Z_{AZS} / (20 * a_{IN})$$

<sup>\*</sup> Bridge in voltage mode, refer "ZMD31050 Functional description" for usable input signal/common mode range at bridge in current mode

## **Advanced Differential Sensor Signal Conditioner**

Datasheet PRELIMINARY

| PGA gain<br>a <sub>IN</sub> | Max. span<br>V <sub>IN SP</sub><br>in mV/V | Calculation factor k | Offset shift per step<br>in % full span | Approx. maximum offset shift in mV/V | Approx. maximum shift in [% V <sub>IN SP</sub> ] (@ ± 25) |

|-----------------------------|--------------------------------------------|----------------------|-----------------------------------------|--------------------------------------|-----------------------------------------------------------|

| 420                         | 2                                          | 3,0                  | 15%                                     | +/- 9                                | 450                                                       |

| 280                         | 3                                          | 1,833                | 9%                                      | +/- 8                                | 266                                                       |

| 210                         | 4                                          | 3,0                  | 15%                                     | +/- 18                               | 450                                                       |

| 140                         | 6                                          | 1,833                | 9%                                      | +/- 18                               | 300                                                       |

| 105                         | 8                                          | 1,25                 | 6%                                      | +/- 15                               | 187                                                       |

| 70                          | 12                                         | 1,833                | 9%                                      | +/- 33                               | 275                                                       |

| 52,5                        | 16                                         | 1,25                 | 6%                                      | +/- 44                               | 275                                                       |

| 35                          | 24                                         | 1,833                | 9%                                      | +/-66                                | 275                                                       |

| 26,3                        | 32                                         | 1,25                 | 6%                                      | +/- 87                               | 272                                                       |

| 14                          | 50                                         | 3,0                  | 15%                                     | +/- 270                              | 540                                                       |

| 9,3                         | 80                                         | 1,833                | 9%                                      | +/- 250                              | 312                                                       |

| 7                           | 100                                        | 1,25                 | 6%                                      | +/- 225                              | 225                                                       |

| 2,8                         | 280                                        | 0,2                  | 1%                                      | +/- 90                               | 32                                                        |

Table 2: Analog Zero Point Shift Ranges

## 1.3.3. Measurement Cycle realized by Multiplexer

The Multiplexer selects, depending on EEPROM settings, the following inputs in a certain sequence.

- S Bridge temperature signal measured by external diode

- § Bridge temperature signal measured by internal pn-junction

- S Bridge temperature signal measured by bridge resistors

- S Separate temperature signal measured by external thermistor

- § Internal offset of the input channel measured by input short circuiting

- Pre-amplified bridge sensor signal Start routine The complete measurement cycle is Pressure measurement n controlled by the CMC. The cycle diagram at the right shows its principle structure. 1 Temp 1 auto zero n Pressure measurement The EEPROM adjustable parameters are: Temp 1 measurement Pressure measurement count, n Pressure measurement n=<1,2,4,8,16,32,64,128> 1 Pressure auto zero Enable temperature measurement 2, n + e2 Pressure measurement e2 = <0,1>e2 Temp 2 auto zero After Power ON the start routine is called. It n + e2 + Pressure measurement contains the pressure and auto zero e2 \* Temp 2 measurement measurement. When enabled it measures the temperature and its auto zeros.

Fig. 4: Measurement cycle ZMD31050

## **Advanced Differential Sensor Signal Conditioner**

**PRELIMINARY Datasheet**

#### 1.3.4. Analog-to-Digital Converter

The ADC is a charge balancing converter in full differential switched capacitor technique. It can be used as first or second order converter:

In the **first order** mode it is inherently monotone and insensitive against short and long term instability of the clock frequency. The conversion cycle time depends on the desired resolution and can be roughly calculated by:

$$t_{CYC}$$

1 =  $2^{r_{ADC}} \mu s$

The available ADC-resolutions are  $r_{ADC} = \langle 9, 10, 11, 12, 13, 14, 15 \rangle$ .

In the second order mode two conversions are stacked with the advantage of much shorter conversion cycle time and the drawback of a lower noise immunity caused by the shorter signal integration period. The conversion cycle time at this mode is roughly calculated by:

$$t_{CYC}_{2} = 2^{(r_{ADC} + 3)/2} \mu s$$

The available ADC-resolutions are  $r_{ADC} = <10,11,12,13,14,15>$ .

The result of the AD conversion is a relative counter result corresponding to the following equation:

$$Z_{ADC} = 2^{r_{ADC}} * [(V_{ADC})_{DIFF}/V_{ADC}] + (1 - RS_{ADC})]$$

number of counts (result of the conversion) Z<sub>ADC</sub>: V<sub>ADC DIFF</sub>:

$V_{ADC\_REF}$ :

differential input voltage of ADC (=  $a_{IN} * V_{IN\_DIFF}$ ) reference voltage of ADC (= VDD<sub>BR</sub> at ratiometric measurement) digital ADC Range Shift (RS<sub>ADC</sub> =  $^{15}/_{16}$ ,  $^{7}/_{8}$ ,  $^{3}/_{4}$ ,  $^{1}/_{2}$ , controlled by the EEPROM content)  $RS_{ADC}$ :

With the RS<sub>ADC</sub> value a sensor input signal can be shifted in the optimal input range of the ADC.

**Note:** The AD conversion time is only a part of a whole sample cycle. Thus the sample rate is lower then the AD conversion rate.

| ADC              | N                  | laximum Out        | Sample     | e Rate f <sub>con</sub> |                        |                           |

|------------------|--------------------|--------------------|------------|-------------------------|------------------------|---------------------------|

| Order            | r <sub>ADC</sub> * | <b>Digital-OUT</b> | Analog-OUT | r <sub>PWM</sub>        | f <sub>CLK</sub> =2MHz | f <sub>CLK</sub> =2.25MHz |

| O <sub>ADC</sub> | Bit                | Bit                | Bit        | Bit                     | Hz                     | Hz                        |

| 1                | 9                  | 9                  | 9          | 9                       | 1302                   | 1465                      |

| 1                | 10                 | 10                 | 10         | 10                      | 781                    | 879                       |

| 1                | 11                 | 11                 | 11         | 11                      | 434                    | 488                       |

| 1                | 12                 | 12                 | 11         | 12                      | 230                    | 259                       |

| 1                | 13                 | 13                 | 11         | 12                      | 115                    | 129                       |

| 1                | 14                 | 14                 | 11         | 12                      | 59                     | 67                        |

| 1                | 15                 | 15                 | 11         | 12                      | 30                     | 34                        |

| 2                | 10                 | 10                 | 10         | 10                      | 3906                   | 4395                      |

| 2                | 11                 | 11                 | 11         | 11                      | 3906                   | 4395                      |

| 2                | 12                 | 12                 | 11         | 12                      | 3906                   | 4395                      |

| 2                | 13                 | 13                 | 11         | 12                      | 1953                   | 2197                      |

| 2                | 14                 | 14                 | 11         | 12                      | 1953                   | 2197                      |

| 2                | 15                 | 15                 | 11         | 12                      | 977                    | 1099                      |

Table 3: Output resolution versus sample rate

\*ADC Resolution should be 1 or 2 Bits higher then applied Output Resolution

## **Advanced Differential Sensor Signal Conditioner**

Datasheet PRELIMINARY

#### 1.4 System Control

The system control has the following features:

- S Control of the I/O relations and of the measurement cycle regarding to the EEPROM-stored configuration data

- § 16 bit correction calculation for each measurement signal using the EEPROM stored calibration coefficients and ROM-based algorithms

- Started by internal POC, internal clock generator or external clock

- § For safety improvement the EEPROM data are proved with a signature within initialization procedure, the registers of the CMC are steadily observed with a parity check. Once an error is detected, the error flag of the CMC is set and the outputs are driven to a diagnostic value

Note: The conditioning includes up to third order sensor input correction. The available adjustment ranges depend on the specific calibration parameters, a detailed description will be issued later. To give a rough idea: Offset compensation and linear correction are only limited by the loose of resolution it will cause, the second order correction is possible up to about 30% full scale difference to straight line, third order up to about 20% (ADC resolution = 13bit). The temperature calibration includes first and second order correction and should be fairly sufficient in all relevant cases. ADC resolution influences also calibration possibilities – 1 bit more resolution reduces calibration range by approximately 50%.

## **Advanced Differential Sensor Signal Conditioner**

Datasheet PRELIMINARY

## 1.5 Output Stage

|     | Used so          | erial IF | Used I/O pins |                    |                      |              |  |  |  |  |

|-----|------------------|----------|---------------|--------------------|----------------------|--------------|--|--|--|--|

| No. | I <sup>2</sup> C | SPI      | OUT           | IO1                | IO2                  | SDA          |  |  |  |  |

| 1   | Х                |          |               |                    |                      | Data I/O     |  |  |  |  |

| 2   | Х                |          |               | ALARM1             |                      | Data I/O     |  |  |  |  |

| 3   | Х                |          |               |                    | ALARM2               | Data I/O     |  |  |  |  |

| 4   | Х                |          |               | ALARM1             | ALARM2               | Data I/O     |  |  |  |  |

| 5   | Х                |          |               | PWM1               |                      | Data I/O     |  |  |  |  |

| 6   | Х                |          |               | PWM1               | ALARM2               | Data I/O     |  |  |  |  |

| 7   | Х                |          | Analog        |                    |                      | Data I/O     |  |  |  |  |

| 8   | Х                |          | Analog        | ALARM1             |                      | Data I/O     |  |  |  |  |

| 9   | Х                |          | Analog        |                    | ALARM2               | Data I/O     |  |  |  |  |

| 10  | Х                |          | Analog        | ALARM1             | ALARM2               | Data I/O     |  |  |  |  |

| 11  | Х                |          | Analog        | PWM1               |                      | Data I/O     |  |  |  |  |

| 12  | Х                |          | Analog        | PWM1               | ALARM2               | Data I/O     |  |  |  |  |

| 13  | Х                |          | PWM2          |                    |                      | Data I/O     |  |  |  |  |

| 14  | Х                |          | PWM2          | ALARM1             |                      | Data I/O     |  |  |  |  |

| 15  | Х                |          | PWM2          |                    | ALARM2               | Data I/O     |  |  |  |  |

| 16  | Х                |          | PWM2          | ALARM1             | ALARM2               | Data I/O     |  |  |  |  |

| 17  | Х                |          | PWM2          | PWM1               |                      | Data I/O     |  |  |  |  |

| 18  | Х                |          | PWM2          | PWM1               | ALARM2               | Data I/O     |  |  |  |  |

| 19  |                  | Х        |               | Data out           | Slave<br>select      | Data in      |  |  |  |  |

| 20  |                  | Х        |               | Data out<br>ALARM1 | Slave<br>select<br>- | Data in<br>- |  |  |  |  |

| 21  |                  | Х        |               | Data out<br>PWM1   | Slave<br>select      | Data in<br>- |  |  |  |  |

| 22  |                  | Х        | Analog        | Data out           | Slave<br>select      | Data in      |  |  |  |  |

| 23  |                  | Х        | Analog        | Data out<br>ALARM1 | Slave<br>select<br>- | Data in<br>- |  |  |  |  |

| 24  |                  | Х        | Analog        | Data out<br>PWM1   | Slave<br>select      | Data in<br>- |  |  |  |  |

| 25  |                  | Х        | PWM2          | Data out           | Slave<br>select      | Data in      |  |  |  |  |

| 26  |                  | Х        | PWM2          | Data out<br>ALARM1 | Slave<br>select<br>- | Data in<br>- |  |  |  |  |

| 27  |                  | Х        | PWM2          | Data out<br>PWM1   | Slave<br>select<br>- | Data in<br>- |  |  |  |  |

**Table 4:** Output configurations overview

The ZMD31050 provides the following I/O pins: OUT, IO1, IO2 and SDA.

Via these pins the following signal formats can be output: Analog (voltage/current), PWM, Data (SPI/I<sup>2</sup>C), Alarm.

The following values can be provided at the O/I pins: bridge sensor signal, temperature signal 1, temperature signal 2, alarm.

#### Note:

The Alarm signal only refers to the bridge sensor signal, but never to a temperature signal.

Due to the necessary pin sharing there are restrictions to the possible combinations of outputs and interface connections.

The table beside gives an overview about possible combinations.

#### Note:

In the SPI mode the pin IO2 is used as Slave select. Thus no Alarm 2 can be output in this mode.

## **Advanced Differential Sensor Signal Conditioner**

Datasheet PRELIMINARY

#### 1.5.1. Analog Output

For the analog output 3 registers of 15 bit depth are available, which can store the actual pressure and the results of temperature measurement 1 and 2. Each register can be independently switched to one of two output slots connected to the Pin OUT and IO1 respectively. In these output slots different output modules are available according to the following table:

| Output slot: | OUT | IO1 |

|--------------|-----|-----|

| Voltage      | Х   |     |

| PWM          | Х   | Х   |

Table 5: Analog output configuration

The Voltage module consists of an 11bit resistor string – DAC with buffered output and a subsequent inverting amplifier with class AB rail-to-rail OPAMP. The two feedback nets are connected to the Pins FBN and FBP. This structure offers wide flexibility for the output configuration, for example voltage output and 4 mA to 20 mA current loop output. To short circuit the analog output against VSS or VDDA does not damage the ZMD31050.

The PWM module provides pulse streams with signal dependent duty cycle. The PWM – frequency depends on resolution and clock divider. The maximum resolution is 12 bit, the maximum PWM – frequency is 4 kHz (9 bit). If both, second PWM and SPI protocol are activated, the output pin IO1 is shared between the PWM output and the SPI\_SDO output of the serial interface (Interface communication interrupts the PWM output).

#### 1.5.2. Comparator Module (ALARM Output)

The comparator module consists of two comparator channels connectable to IO1 and IO2 respectively. Each of them can be independently programmed referring to the parameters threshold, hysteresis, switching direction and on/off – delay, additional a window comparator mode is available.

#### 1.5.3. Serial Digital Interface

The ZMD31050 includes a serial digital interface which is able to communicate in three different communication protocols –  $I^2C^{TM}$ , SPI $^{TM}$  and ZACwire $^{TM}$  (one wire communication). In the SPI mode the pin IO2 operates as slave select input, the pin IO1 as data output.

#### Initializing Communication

After power-on the interface is for about 20ms (start window) in the state ZACwire. During the start window it is possible to communicate via the one wire interface (pin OUT).

Detecting a proper request inside the start window the interface stays in the state ZACwire. This state can be left by certain commands or a new power-on.

If no request happens during the start window then the serial interface switches to I<sup>2</sup>C or SPI mode (depending on EEPROM settings) and the OUT pin is used as analog output or as PWM output (also depending on EEPROM settings. The start window can generally be disabled (or enabled) by a special EEPROM setting.

For detailed description of the serial interfaces see "ZMD31050 Functional Description".

## **Advanced Differential Sensor Signal Conditioner**

Datasheet PRELIMINARY

## 1.6 Voltage Regulator

For ratiometric applications 3V to 5V ( $\pm 10\%$ ) the external supply voltage can be used for sensor element biasing. If an absolute analog output is desired then the internal voltage regulator with external power regulation element (FET) can be used. It is bandgap reference based and designed for an external supply range  $V_{SUPP} = (7 \text{ to } 40) \text{ VDC}$ . With the voltage regulator the internal supply and sensor bridge voltage can be varied between 3V and 5V.

## 1.7 Watchdog and Error Detection

The ZMD31050 detects various possible errors. A detected error is signalized by changing in a diagnostic mode. In this case the analog output is set to High or Low (maximum or minimum possible output value) and the output registers of the digital serial interface are set to a significant error code.

A watchdog oversees the continuous working of the CMC and the running measurement loop.

A check of the sensor bridge for broken wires is done permanently by two comparators watching the input voltage of each input [(VSSA + 0.5V) to (VDDA - 0.5V)]. Add on the common mode voltage of the sensor is watched permanently (sensor aging).

Different functions and blocks in digital part are watched like RAM-, ROM,- EEPROM- and Register content continuously, the document "ZMD31050 Functional Description" contains in chapter 1.3.4 a detailed description of all watched blocks and methods of messaging of errors.

## **Advanced Differential Sensor Signal Conditioner**

**PRELIMINARY Datasheet**

#### 2. **Application Circuit Examples**

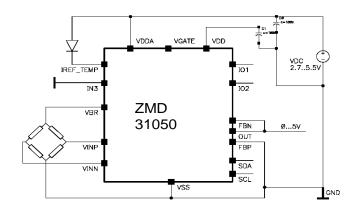

## Example 1

Typical ratiometric measurement with voltage 0V to 10V output configuration, supply regulator output, temperature compensation via external (external JFET), temperature compensation via diode, internal VDD regulator and active sensor internal diode and bridge in voltage mode connection check (bridge must not be at VDDA)

## **Example 2**

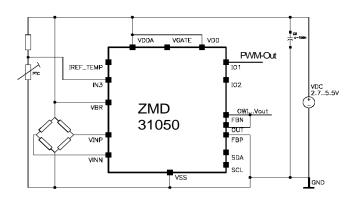

## Example 3

Absolute voltage output, supply (external JFET), constant current excitation of the measurement, 3-wire connection for end of line sensor bridge, temperature compensation by calibration at pin OUT (ZACwire™), additional bridge voltage drop measurement, internal VDD temperature regulator without ext. capacitor

#### Example 4

regulator Ratiometric bridge differential signal measurement external thermistor and PWM-output at pin IO1

#### Hint:

It is possible to combine or split connectivity of different application examples. For VDD generation ZMD recommends to use internal supply voltage regulator with external capacitor (refer example 1).

## **Advanced Differential Sensor Signal Conditioner**

Datasheet PRELIMINARY

## 3. ESD/Latch-Up-Protection

All pins have an ESD Protection of >2000V (except the pins INN, INP and FBP with > 1200V) and a Latch-up protection of  $\pm 100$ mA or of  $\pm 8$ V/  $\pm 4$ V (to VSS/VSSA) – refer chapter 4 for details and restrictions. ESD Protection referred to the human body model is tested with devices in SSOP16 packages during product qualification. The ESD test follows the human body model with 1.5kOhm/100pF based on MIL 883, Method 3015.7.

## 4. Pin Configuration and Package

| Pin | Name    | Description                                          | Remarks              | Latch-Up related Application Circuit<br>Restrictions and/or Remarks                   |

|-----|---------|------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------|

| 1   | VDDA    | Positive analog supply voltage                       | Supply               |                                                                                       |

| 2   | IN3     | Resistive temp sensor IN & external clock IN         | Analog IN            | free accessible (latch-up related)                                                    |

| 3   | VGATE   | Gate voltage for external regulator FET              | Analog OUT           | only connection to external FET                                                       |

| 4   | IO1     | SPI data out & ALARM1 & PWM1 Output                  | Digital IO           | free accessibility                                                                    |

| 5   | IO2     | SPI chip select & ALARM2                             | Digital IO           | free accessibility                                                                    |

| 6   | SCL     | I <sup>2</sup> C clock & SPI clock                   | Digital IN, pull-up  | free accessibility                                                                    |

| 7   | SDA     | Data IO for I <sup>2</sup> C & data IN for SPI       | Digital IO, pull-up  | free accessibility                                                                    |

| 8   | VDD     | Positive digital supply voltage                      | Supply               | only short to VDDA or capacitor to VSS allowed, otherwise no application access       |

| 9   | FBN     | Negative feedback connection output stage            | Analog IO            | free accessibility                                                                    |

| 10  | OUT     | Analog output & PWM2 Output & one wire interface i/o | Analog OUT & dig. IO | free accessibility                                                                    |

| 11  | FBP     | Positive feedback connection output stage            | Analog IO            | free accessibility                                                                    |

| 12  | IR_TEMP | Current source resistor i/o & temp. diode in         | Analog IO            | circuitry secures potential inside of VSS-VDDA range, otherwise no application access |

| 13  | VBR     | Bridge top sensing in bridge current out             | Analog IO            | only short to VDDA or connection to sensor bridge, otherwise no application access    |

| 14  | VINP    | Positive input sensor bridge                         | Analog IN            | free accessibility                                                                    |

| 15  | VSS     | Negative supply voltage                              | Ground               |                                                                                       |

| 16  | VINN    | Negative input sensor bridge                         | Analog IN            | free accessibility                                                                    |

Table 6: Pin configuration

The standard package of the ZMD31050 is a SSOP16 (5.3mm body width) with lead-pitch 0.65mm:

| Pin-Nr<br>9<br>10<br>11<br>12<br>13<br>14 | Pin-Name<br>FBN<br>OUT<br>FBP<br>IR_TEMP<br>VBR<br>VINP | ZMD U23456 abcd xxxx YYWW | Pin-Name<br>VDD<br>SDA<br>SCL<br>IO2<br>IO1<br>VGATE | Pin-Nr<br>8<br>7<br>6<br>5<br>4<br>3 |

|-------------------------------------------|---------------------------------------------------------|---------------------------|------------------------------------------------------|--------------------------------------|

| 15                                        | VSS                                                     |                           | VGATE<br>IN3                                         | 3<br>2                               |

| 16                                        | VINN                                                    | 5 5                       | VDDA                                                 | 1                                    |

# **Advanced Differential Sensor Signal Conditioner**

Datasheet PRELIMINARY

## 5. IC Characteristics

## 5.1 Absolute Maximum Ratings

| No.   | Parameter                                       | Symbol                                     | min  | typ | max          | Unit | Conditions                  |

|-------|-------------------------------------------------|--------------------------------------------|------|-----|--------------|------|-----------------------------|

| 5.1.1 | Digital Supply Voltage                          | $VDD_{AMR}$                                | -0.3 |     | 6.5          | V DC | to VSS                      |

| 5.1.2 | Analog Supply Voltage                           | VDDA <sub>AMR</sub>                        | -0.3 |     | 6.5          | V DC | to VSS                      |

| 5.1.3 | Voltage at all analog<br>and digital I/O – Pins | V <sub>A_I/O</sub> ,<br>V <sub>D_I/O</sub> | -0.3 |     | VDDA<br>+0.3 | V DC | Exception s. 5.1.4          |

| 5.1.4 | Voltage at Pin FBP                              | $V_{FBP\_AMR}$                             | -1.2 |     | VDDA<br>+0.3 | V DC | 4 mA to 20mA –<br>Interface |

| 5.1.5 | Storage temperature                             | T <sub>STG</sub>                           | -45  |     | 150          | °C   |                             |

## 5.2 Operating Conditions

## (Voltages related to VSS)

| No.    | Parameter                                  | Symbol              | min          | typ | max       | Unit                 | Conditions                                             |

|--------|--------------------------------------------|---------------------|--------------|-----|-----------|----------------------|--------------------------------------------------------|

| 5.2.1  | Ambient temperature                        | $T_{AMB}$           | -40          |     | 125       | °C                   |                                                        |

| 5.2.2  | Ambient temperature advanced performance   | $T_{AMB\_ADV}$      | -25          |     | 85        | °C                   |                                                        |

| 5.2.3  | Ambient temperature EEPROM programming     | $T_{AMB_{EEP}}$     | -25          |     | 85        | °C                   |                                                        |

| 5.2.4  | EEPROM programming cycles                  |                     |              |     | 100       |                      |                                                        |

| 5.2.5  | Data retention<br>(EEPROM)                 |                     |              |     | 15        | а                    | avg. temp < 85grd                                      |

| 5.2.6  | Analog Supply Voltage                      | VDDA                | 2.7          |     | 5.5       | V DC                 | ratiometric mode                                       |

| 5.2.7  | Analog Supply Voltage advanced performance | VDDA <sub>ADV</sub> | 4.5          |     | 5.5       | V DC                 | ratiometric mode                                       |

| 5.2.8  | Digital Supply Voltage                     | VDD                 | -<br>2.7     |     | 1.05<br>- | VDDA<br>V DC         | external powered                                       |

| 5.2.9  | External Supply<br>Voltage                 | $V_{SUPP}$          | VDDA<br>+ 2V |     | 40        | V DC                 | voltage regulator mode with ext. JFET                  |

| 5.2.10 | Common mode input range                    | $V_{IN\_CM}$        | 0.21         |     | 0.76      | V <sub>ADC_REF</sub> | depends on gain<br>adjustment -<br>refer chapter 1.3.1 |

# **Advanced Differential Sensor Signal Conditioner**

**PRELIMINARY Datasheet**

| No.    | Parameter                                            | Symbol               | min                     | typ | max          | Unit     | Conditions                                           |

|--------|------------------------------------------------------|----------------------|-------------------------|-----|--------------|----------|------------------------------------------------------|

| 5.2.11 | Input Voltage Pin FBP                                | $V_{IN\_FBP}$        | -1                      |     | VDDA         | V DC     |                                                      |

| 5.2.12 | Sensor Bridge<br>Resistance *                        | $R_{BR}$             | 3.0 <sup>1</sup><br>5.0 |     | 25.0<br>25.0 | kΩ<br>kΩ | full temperature range<br>4mA to 20mA –<br>Interface |

| 5.2.13 | Reference Resistor for Bridge Current Source *       | $R_{BR\_REF}$        | 0.07                    |     |              | $R_{BR}$ | leads to $I_{BR} = V_{DDA} / (16.R_{BR\_REF})$       |

| 5.2.14 | Stabilization Capacitor *                            | $C_{VDDA}$           | 50                      | 100 | 470          | nF       | between VDDA and VSS, external                       |

| 5.2.15 | Optional Stabilization Capacitor *                   | $C_{VDD}$            | 0 2                     | 100 | 470          | nF       | between VDD and VSS, external                        |

| 5.2.16 | Maximum allowed load capacitance at OUT <sup>3</sup> | C <sub>L_OUT</sub>   |                         |     | 50           | nF       | Output Voltage mode                                  |

| 5.2.17 | Minimum allowed load resistance                      | R <sub>L_OUT</sub>   | 2                       |     |              | kΩ       | Output Voltage mode                                  |

| 5.2.18 | Maximum allowed load capacitance at VGATE            | C <sub>L_VGATE</sub> |                         |     | 10           | nF       | summarized to all potentials                         |

#### **Build In Characteristics** 5.3

| No.    | Parameter                                              | Symbol             | min               | typ  | max            | Unit          | Conditions                        |

|--------|--------------------------------------------------------|--------------------|-------------------|------|----------------|---------------|-----------------------------------|

| 5.3.1. | Selectable Input Span,<br>Pressure Measurement         | $V_{IN\_SP}$       | 1                 |      | 275            | mV/V          | 4 Bit setting s. 3.3.1            |

| 5.3.2  | Analog Offset<br>Compensation Range<br>(6 Bit setting) |                    | -20<br>-25<br>-31 |      | 20<br>25<br>31 | count         | ADJREF:BCUR>3<br>ADJREF:BCUR=7    |

| 5.3.3  | A/D Resolution                                         | r <sub>ADC</sub>   | 9                 |      | 15             | Bit           | 3 Bit setting                     |

| 5.3.4  | D/A Resolution                                         | r <sub>DAC</sub>   |                   | 11   |                | Bit           | @ analogue output                 |

| 5.3.5  | PWM - Resolution                                       | r <sub>PWM</sub>   | 9                 |      | 12             | Bit           |                                   |

| 5.3.6  | Reference current for external temperature diodes      | I <sub>TS</sub>    | 8                 | 18   | 40             | μΑ            |                                   |

| 5.3.7  | Sensitivity internal temperature diode                 | ST <sub>T_SI</sub> | 2800              | 3200 | 3600           | ppm<br>f.s./K | Raw values - without conditioning |

no measurement in mass production, parameter is guarantied by design and/or quality observation no limitations with an external connection between VDDA and VBR

lower stabilization capacitors can increase noise level at the output

if used, consider special requirements of ZACwire™ single wire interface stated in "Functional Description" chapter 4.3

## **Advanced Differential Sensor Signal Conditioner**

Datasheet PRELIMINARY

## 5.3.8 Cycle Rate versus A/D-Resolution \*

(linear related to master clock frequency<sup>1</sup> - values calculated at exact 2 MHz)

| <b>ADC Order</b> | Resolution       | Conversion             | n Cycle f <sub>cyc</sub>  |  |

|------------------|------------------|------------------------|---------------------------|--|

| O <sub>ADC</sub> | r <sub>ADC</sub> | f <sub>CLK</sub> =2MHz | f <sub>CLK</sub> =2.25MHz |  |

|                  | Bit              | Hz                     | Hz                        |  |

| 1                | 9                | 1302                   | 1465                      |  |

|                  | 10               | 781                    | 879                       |  |

|                  | 11               | 434                    | 488                       |  |

|                  | 12               | 230                    | 259                       |  |

|                  | 13               | 115                    | 129                       |  |

|                  | 14               | 59                     | 67                        |  |

|                  | 15               | 30                     | 34                        |  |

| 2                | 11               | 3906                   | 4395                      |  |

|                  | 12               | 3906                   | 4395                      |  |

|                  | 13               | 1953                   | 2197                      |  |

|                  | 14               | 1953                   | 2197                      |  |

|                  | 15               | 977                    | 1099                      |  |

## 5.3.9 PWM Frequency \*

| PWM                    | PWM F | req./Hz a | at 2 MHz | Clock <sup>1</sup> | PWM Freq./Hz at 2.25 MHz Clock <sup>2</sup> |      |      |       |  |

|------------------------|-------|-----------|----------|--------------------|---------------------------------------------|------|------|-------|--|

| Resolution             |       | Clock I   | Divider  | _                  | Clock Divider                               |      |      |       |  |

| r <sub>PWM</sub> [Bit] | 1     | 0,5       | 0,25     | 0,125              | 1                                           | 0,5  | 0,25 | 0,125 |  |

| 9                      | 3906  | 1953      | 977      | 488                | 4395                                        | 2197 | 1099 | 549   |  |

| 10                     | 1953  | 977       | 488      | 244                | 2197                                        | 1099 | 549  | 275   |  |

| 11                     | 977   | 488       | 244      | 122                | 1099                                        | 549  | 275  | 137   |  |

| 12                     | 488   | 244       | 122      | 61                 | 549                                         | 275  | 137  | 69    |  |

<sup>\*</sup> no measurement in mass production, parameter is guarantied by design and/or quality observation

<sup>1</sup> Internal RC – Oscillator: coarse adjustment to1, 2 and 4 MHz, fine tuning +/- 25%, external clock is also possible

<sup>&</sup>lt;sup>2</sup> Internal RC – Oscillator: coarse adjustment to1.125, 2.25 and 4.5 MHz, fine tuning +/- 25%, external clock is also possible

# **Advanced Differential Sensor Signal Conditioner**

Datasheet PRELIMINARY

## 5.4 Electrical Parameters

## (Voltages related to VSS)

| No.                       | Parameter                                             | Symbol                | min           | typ       | max      | Unit        | Conditions                                                                        |  |  |  |  |

|---------------------------|-------------------------------------------------------|-----------------------|---------------|-----------|----------|-------------|-----------------------------------------------------------------------------------|--|--|--|--|

| 5.4.1 Supply / Regulation |                                                       |                       |               |           |          |             |                                                                                   |  |  |  |  |

| 5.4.1.1                   | Supply current                                        | I <sub>SUPP</sub>     |               | 2.5       | 4        | mA          | without bridge current<br>and without load<br>current, f <sub>CLK</sub> ≤ 2.25MHz |  |  |  |  |

| 5.4.1.2                   | Supply current for current loop                       | I <sub>SUPP_CL</sub>  |               | 2.0       | 2.75     |             | without bridge current, $f_{CLK} \le 1.2 MHz$ , Bias-Adjustment $\le 1$           |  |  |  |  |

| 5.4.1.2                   | Temperature Coeff.<br>Voltage Reference               | TC <sub>REF</sub>     | -200          | +/- 50    | 200      | ppm/K       |                                                                                   |  |  |  |  |

|                           |                                                       | 5.4.                  | 2 Analo       | g Front   | End      |             |                                                                                   |  |  |  |  |

| 5.4.2.1                   | Parasitic differential input offset current *         | I <sub>IN_OFF</sub>   | -2 to -<br>10 |           | 2 to 10  | nA          | temp. range 5.2.2., T <sub>ADV</sub>                                              |  |  |  |  |

|                           | 5.4                                                   | 4.3 DAC 8             | & Analo       | g Outpu   | t (Pin C | OUT)        |                                                                                   |  |  |  |  |

| 5.4.3.1                   | Output signal range                                   | $V_{\text{OUT\_SR}}$  | 0.025         |           | 0.975    | VDDA        | Voltage mode, assuming maximum load of 2k                                         |  |  |  |  |

| 5.4.3.2                   | Output slew rate *                                    | SR <sub>OUT</sub>     | 0.1           |           |          | V/μs        | Voltage mode, C <sub>L</sub> <20nF<br>@ V <sub>OUT_SR</sub> : 5.4.2.1             |  |  |  |  |

| 5.4.3.3                   | Short circuit current *                               | I <sub>OUT_max</sub>  | 5             | 10        | 20       | mA          |                                                                                   |  |  |  |  |

| 5.4.3.4                   | addressable output signal range *                     | $V_{\text{OUT\_ADR}}$ | 0             |           | 1        | VDDA        | 2048 steps                                                                        |  |  |  |  |

|                           |                                                       | 5.4.4 PW              | M Outp        | ut (Pin ( | OUT, IO  | 1)          |                                                                                   |  |  |  |  |

| 5.4.4.1                   | PWM high voltage                                      | $V_{PWM\_H}$          | 0.9           |           |          | VDDA        | $R_L > 10 \text{ k}\Omega$                                                        |  |  |  |  |

| 5.4.4.2                   | PWM low voltage                                       | $V_{PWM\_L}$          |               |           | 0.1      | VDDA        | $R_L > 10 \text{ k}\Omega$                                                        |  |  |  |  |

| 5.4.4.3                   | PWM output slew rate*                                 | SR <sub>PWM</sub>     | 15            |           |          | V/μs        | C <sub>L</sub> < 1nF                                                              |  |  |  |  |

|                           | 5.4.5                                                 | Tempera               | ature Se      | ensors (  | Pin IR_  | ГЕМР)       |                                                                                   |  |  |  |  |

| 5.4.5.1                   | Sensitivity external diode / resistor meas.           | ST <sub>TS_E</sub>    | 75            |           | 210      | μV /<br>LSB | at r <sub>ADC</sub> = 13 Bit                                                      |  |  |  |  |

|                           | 5.4.6 Digital Outputs (IO1, IO2, OUT in digital mode) |                       |               |           |          |             |                                                                                   |  |  |  |  |

| 5.4.6.1                   | Output-High-Level                                     | $V_{DOUT\_H}$         | 0.9           |           |          | VDDA        | $R_L > 1 k\Omega$                                                                 |  |  |  |  |

| 5.4.6.2                   | Output-Low-Level                                      | $V_{DOUT\_L}$         |               |           | 0.1      | VDDA        | $R_L > 1 k\Omega$                                                                 |  |  |  |  |

| 5.4.6.3                   | Output Current *                                      | I <sub>DOUT</sub>     | 4             |           |          | mA          |                                                                                   |  |  |  |  |

<sup>\*</sup> no measurement in mass production, parameter is guarantied by design and/or quality observation

# **Advanced Differential Sensor Signal Conditioner**

Datasheet PRELIMINARY

| No.     | Parameter                                                 | Symbol             | min              | typ | max                | Unit       | Conditions                                                              |  |  |  |  |

|---------|-----------------------------------------------------------|--------------------|------------------|-----|--------------------|------------|-------------------------------------------------------------------------|--|--|--|--|

|         | 5.4.7 System Response                                     |                    |                  |     |                    |            |                                                                         |  |  |  |  |

| 5.4.7.1 | Startup time <sup>1</sup>                                 | t <sub>STA</sub>   | 2                | 2   | 5                  | ms         | Power up to first measure result at output, OWI – start window disabled |  |  |  |  |

| 5.4.7.2 | Response time                                             | t <sub>RESI</sub>  | 2/f <sub>0</sub> | CON | 3/f <sub>CON</sub> |            | refer chapter 1.3.4 for f <sub>CON</sub>                                |  |  |  |  |

| 5.4.7.3 | Overall accuracy (deviation from ideal line including INL | AC <sub>OL</sub>   | JT               |     | 0.1                | %          | T <sub>ADV</sub> , V <sub>ADV</sub><br>(-25 to +85)°C, (4.5 to 5.5)V    |  |  |  |  |

|         | gain and offset errors)                                   |                    |                  |     | 0.25               | %          | For decreased current consumption ADJREF:BCUR>3                         |  |  |  |  |

| 5.4.7.4 | Peak-to-Peak-<br>Noise@output *                           | V <sub>OUT_</sub>  | NS               |     | 5                  | mV         | shorted inputs,<br>bandwidth ≤ 2kHz                                     |  |  |  |  |

| 5.4.7.5 | Ratiometricity Error                                      | RE <sub>OU</sub> · |                  |     | 500<br>1000        | ppm<br>ppm | 4.5 – 5.0V & 5.0 – 5.5V<br>2.7 – 3.0V & 3.0 – 3.3V                      |  |  |  |  |

#### 5.5 Interface Characteristics

| No.     | Parameter                                                 | Symbol                | min     | typ   | max     | Unit                                       | Conditions                          |  |  |  |

|---------|-----------------------------------------------------------|-----------------------|---------|-------|---------|--------------------------------------------|-------------------------------------|--|--|--|

|         | 5.5.1 Multiport Serial Interfaces (I <sup>2</sup> C, SPI) |                       |         |       |         |                                            |                                     |  |  |  |

| 5.5.1.1 | Input-High-Level                                          | $V_{I2C\_IN\_H}$      | 0.7     |       | 1       | VDDA                                       |                                     |  |  |  |

| 5.5.1.2 | Input-Low-Level                                           | $V_{I2C\_IN\_L}$      | 0       |       | 0.3     | VDDA                                       |                                     |  |  |  |

| 5.5.1.3 | Output-Low-Level                                          | $V_{I2C\_OUT\_L}$     |         |       | 0.1     | VDDA                                       |                                     |  |  |  |

| 5.5.1.4 | load capacitance @ SDA                                    | $C_{SDA}$             |         |       | 400     | pF                                         |                                     |  |  |  |

| 5.5.1.5 | Clock frequency SCL                                       | $f_{SCL}$             |         |       | 400     | kHz                                        |                                     |  |  |  |

| 5.5.1.6 | Pull-up Resistor                                          | $R_{I2C\_PU}$         | 500     |       |         | Ω                                          |                                     |  |  |  |

|         | 5.5.2 On                                                  | e Wire Ser            | ial Int | erfac | e (ZAC) | wire™)                                     |                                     |  |  |  |

| 5.5.2.1 | Pull-up resistance master                                 | R <sub>OWI_PU</sub>   | 330     |       |         | Ω                                          |                                     |  |  |  |

| 5.5.2.2 | OWI line resistance                                       | R <sub>OWI_LINE</sub> |         |       | 0.05    | R <sub>OWI_PU</sub>                        |                                     |  |  |  |

| 5.5.2.3 | OWI load capacitance                                      | C <sub>OWI_LOA</sub>  |         |       | 0.08    | t <sub>OWI_BIT</sub> / R <sub>OWI_PU</sub> | 20μs < t <sub>OWI_BIT</sub> < 100μs |  |  |  |

| 5.5.2.4 | Voltage level Low                                         | V <sub>OWI_L</sub>    |         |       | 0.2     | VDDA                                       |                                     |  |  |  |

| 5.5.2.5 | Voltage level High                                        | V <sub>OWI_H</sub>    | 0.75    |       |         | VDDA                                       |                                     |  |  |  |

<sup>\*</sup> no measurement in mass production, parameter is guarantied by design and/or quality observation

<sup>&</sup>lt;sup>1</sup> Depends on resolution and configuration - start routine begins approximately 0.8ms after power on

## **Advanced Differential Sensor Signal Conditioner**

Datasheet PRELIMINARY

#### 6. Test

Refer "ZMD31050 Test Flow Description" for a detailed test flow and test conditions.

#### 7. Reliability

A reliability investigation according to the in-house non-automotive standard will be performed.

#### 8. Customization

For high-volume applications, which require an up- or downgraded functionality compared to the ZM31050, ZMD can customize the circuit design by adding or removing certain functional blocks. For it ZMD has a considerable library of sensor-dedicated circuitry blocks.

Thus ZMD can provide a custom solution quickly. Please contact ZMD for further information.

#### 9. Related Documents

- ZMD31050 Feature Sheet

- ZMD31050 Functional Description

- ZMD31050 Evaluation Kit Description

- ZMD31050 Development Status Report (including parts identification table)

- ZMD31050 Test Flow Description

- ZMD31050 Application Notes

## **Advanced Differential Sensor Signal Conditioner**

Datasheet PRELIMINARY

**NOTES:**

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. ZMD assumes no obligation regarding future manufacture unless otherwise agreed in writing. The information furnished hereby is believed to be correct and accurate. However, ZMD shall not be liable to any customer, licensee or any other third party for any damages in connection with or arising out of the furnishing, performance or use of this technical data. No obligation or liability to any customer, licensee or any other third party shall result from ZMD's rendering of technical or other services.

For further information:

ZMD AG Grenzstrasse 28 01109 Dresden, Germany Phone +49 (0)351-8822-366 Fax +49 (0)351-8822-337

sales@zmd.de www.zmd.biz ZMD America, Inc. 201 Old Country Road, Suite 204 Melville, NY 11747, USA Phone +01 (631) 549-2666 Fax +01 (631) 549-2882 sales@zmda.com www.zmd.biz ZMD America, Inc. 15373 Innovation Drive, Suite 110 San Diego, CA 92128, USA Phone +01 (858) 674-8070 Fax +01 (858) 674-8071 sales@zmda.com www.zmd.biz