### 8 Bit D to A/A to D Converter

#### **FEATURES**

- Туре

- Accuracy

- Operating Ranges

- Compatibility

- Power Supply

- Settling Time (D-A) : 1 μs typ.

- Conversion Time (A-D) : 1 ms typ., using ramp and

- 16 Lead D.I.L.

**D-A/A-D CONVERTER**

**ZN425E**

ZN425.J

- Extra Components Required

- D-A

A-D

: Reference capacitor (direct voltage output through 10 kΩ typ.)

: Monolithic, contains D-A with counter and reference

: 0.2% FSR at 25°C (±1 LSB

: 0°C to 70°C (ZN425E) -55°C to +125°C (ZN425J)

linearity)

: Single +5V

compare

: TTL and CMOS

: Comparator, gate, clock and reference capacitor

#### DESCRIPTION

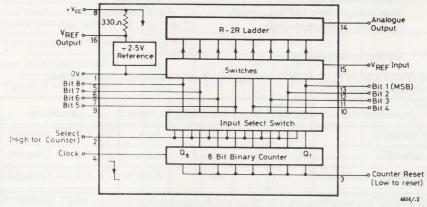

The ZN425E (or ZN425J) is a monolithic S.I.C. 8-bit digital to analogue converter containing an R-2R ladder network of diffused resistors with precision bipolar switches, and in addition a counter and a 2.5V precision voltage reference. The counter is a powerful addition which allows a precision staircase to be generated very simply merely by clocking the counter.

Fig. 1 - Block Diagram

Ferranti Electronic Components Division

#### INTRODUCTION

The ZN425E (or ZN425J) is an 8-bit dual mode digital to analogue/analogue to digital converter. It contains an 8-bit D to A converter using an advanced design of R-2R ladder network and an array of precision bipolar switches plus an 8-bit binary counter and a 2.5 volt precision voltage reference all on a single monolithic chip.

The special design of ladder network results in full 8-bit accuracy using normal diffused resistors.

The use of the on-chip reference voltage is pin optional to retain flexibility. An external fixed or varying reference may therefore be substituted.

By including on the chip an 8-bit binary counter, analogue to digital conversion can be obtained simply by adding an external comparator (ZN424P) and clock inhibit gating (ZN7400E).

By simply clocking the counter the ZN425E can be used as a self-contained precision ramp generator.

A logic input select switch is incorporated which determines whether the precision switches accept the outputs from the binary counter or external digital inputs depending upon whether the control signal is respectively high or low.

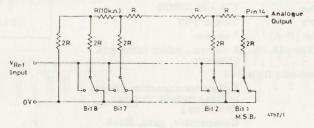

The converter is of the voltage switching type and uses an R-2R resistor ladder network as shown in Fig. 2.

Fig. 2 - The R-2R Ladder Network

Each 2R element is connected either to 0V or V<sub>REF</sub> by transistor switches specially designed for low offset voltage (typically 1 millivolt).

Binary weighted voltages are produced at the output of the R-2R ladder, the value depending on the digital number applied to the bit inputs.

#### ABSOLUTE MAXIMUM RATINGS

| Supply voltage V <sub>CC</sub>      | +7.0 volts               |

|-------------------------------------|--------------------------|

| Max. voltage, logic and VREF inputs | +5.5 volts See note 3    |

| Operating temperature range         | 0°C to +70°C (ZN425E)    |

|                                     | -55°C to +125°C (ZN425J) |

| Storage temperature range           | -55°C to +125°C          |

|                                     |                          |

CHARACTERISTICS (at  $T_{amb}=25\,^{*}C$  and  $V_{CC}=+5$  volts unless otherwise specified). Internal voltage reference

| Parameter                                | Symbol | Min.  | Тур. | Max. | Units  | Conditions              |

|------------------------------------------|--------|-------|------|------|--------|-------------------------|

| Output voltage                           | VREF   | 2.4   | 2.55 | 2.7  | volts  | I = 7.5  mA  (internal) |

| Slope resistance                         | Rs     | 01969 | 2    | 4    | ohms   | I = 7 · 5 mA (internal) |

| V <sub>REF</sub> Temperature coefficient |        |       | 40   |      | ppm/°C | I = 7.5  mA  (internal) |

Note: The internal reference requires a  $0.22 \,\mu\text{F}$  stabilising capacitor between pins 1 and 16.

#### CHARACTERISTICS (continued). 8-Bit D to A Converter and Counter

| Parameter                                          | Symbol          | Min.  | Тур.       | Max.        | Units    | Conditions                                              |

|----------------------------------------------------|-----------------|-------|------------|-------------|----------|---------------------------------------------------------|

| Linearity error                                    | ton or se       | -     |            | ±0.5        | L.S.B.   | See Note 3                                              |

| Settling time                                      |                 | -     | 1.0        | -           | μs       | 1 L.S.B. step                                           |

| Settling time to 0 · 5 L.S.B.                      | 1000            | -     | 2.0        |             | 'ns      | All bits ON toOFF<br>or OFF to ON                       |

| Offset voltage, ZN425E<br>ZN425J                   | Vos             | =     | 3·0<br>8·0 | 8·0<br>12·0 | mV<br>mV | All bits OFF<br>See Note 3                              |

| V <sub>OS</sub> Temperature coefficient            | i persente de   | -     | 5          | -           | μV/°C    |                                                         |

| F.S.R. Temperature coefficient                     | - Anton         | -     | 3          | -           | ppm/°C   | Ext. $V_{REF} = 2.5$                                    |

| Linearity Error Temp. coeff.                       | es sint dat     | -     | 7.5        | -           | ppm/°C   | Relative to F.S.R.                                      |

| Analogue output resistance                         | Ro              |       | 10         | -           | kΩ       | 1                                                       |

| External reference voltage                         | 122.5           | 0     | -          | 3.0         | volts    |                                                         |

| Supply voltage                                     | V <sub>cc</sub> | 4.5   | -          | 5.5         | volts    | See Note 3                                              |

| Supply current                                     | ls              | -     | 25         | 35          | mA       | 199                                                     |

| High level input voltage                           | VIH             | 2.0   | -          | -           | volts    | See Notes 1 and 2                                       |

| Low level input voltage                            | VIL             | _     | -          | 0.7         | volts    |                                                         |

| High level input current                           | Іін             | -     | -          | 10          | μΑ       | $V_{CC} = \max_{V_1}$ $V_1 = 2 \cdot 4V$                |

|                                                    |                 |       | -          | 100         | μΑ       | $V_{CC} = \max_{i}, V_{i} = 5.5V$                       |

| Low level input current                            | I <sub>IL</sub> |       | -          | -0.68       | mA       | $V_{CC} = \max_{i}, V_{i} = 0.3V$                       |

| Low level input current bit inputs clock and reset |                 | -     | -          | -0.18       | mA       | find) and still net                                     |

| High level output current                          | I <sub>OH</sub> | (T-0) |            | -40         | μА       |                                                         |

| Low level output current                           | IOL             |       | -          | 1.6         | mA       |                                                         |

| High level output voltage                          | V <sub>OH</sub> | 2.4   | -          |             | volts    | $V_{CC} = min.,$<br>Q = 1,<br>$I_{load} = -40 \mu A$    |

| Low level output voltage                           | V <sub>OL</sub> | _     | -          | 0.4         | volts    | $V_{CC} = min.,$<br>Q = 0,<br>$I_{load} = 1 \cdot 6 mA$ |

| Maximum counter clock<br>frequency                 | f <sub>c</sub>  | 3     | 5          | 1           | MHz      |                                                         |

| Reset pulse width                                  | t <sub>R</sub>  | 200   | -          | -           | ns       | See Note 4                                              |

#### Notes:

- 1. The Logic Select pin (2) must be held low when the bit pins (5, 6, 7, 9, 10, 11, 12 and 13) are driven externally.

- To obtain counter outputs on bit pins the Logic Select pin (2) should be taken to +V<sub>CC</sub> via a 1 kΩ resistor.

- 3. The ZN425J differs from the ZN425E in the following respects :

- (a) For the ZN425J, the maximum linearity error may increase to  $\pm 1$  LSB over the temperature ranges –55 °C to 0 °C and +70 °C to +125 °C.

- (b) Maximum operating voltage. Between 70°C and 125°C the maximum supply voltage is reduced to 5.0V.

- (c) Offset voltage. The difference is due to package lead resistance. This offset will normally be removed by the setting up procedure, and because the offset temperature coefficient is low, the specified accuracy will be maintained.

- 4. The device may be reset by gating from its own counter.

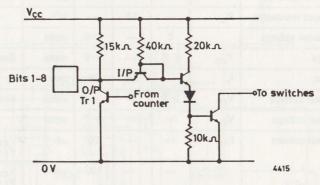

If Pin 2 is high then the output equals the  $\Omega$  output of the corresponding counter. If Pin 2 is low then the output transistor, Tr1 is held off.

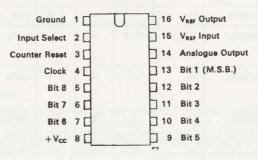

#### **PIN CONNECTIONS**

#### APPLICATIONS

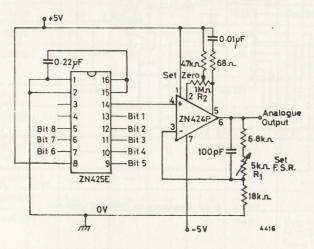

#### 1. 8-bit D to A Converter

The ZN425E gives an analogue voltage output directly from pin 14 therefore the usual current to voltage converting amplifier is not required. The output voltage drift, due to the temperature coefficient of the Analogue Output Resistance  $R_o$ , will be less than 0.004% per °C (or 1 L.S.B./ 100°C) if  $R_1$  is chosen to be  $\ge 650 \text{ k}\Omega$ .

In order to remove the offset voltage and to calibrate the converter a buffer amplifier is necessary. Fig. 4 shows a typical scheme using the internal reference voltage. To minimise temperature drift in this and similar applications the source resistance to the inverting input of the operational amplifier should be approximately  $6 \ k\Omega$ . The calibration procedure is as follows:

*i.* Set all bits to OFF (low) and adjust  $R_2$  until  $V_{out} = 0.000V$ .

ii. Set all bits to ON (high) and adjust  $R_1$  until  $V_{out} = Nominal full scale reading - 1 L.S.B.$

iii. Repeat i. and ii.

(

e.g. Set F.S.R. to +3.840 volts - 1 L.S.B.

# = 3.825 volts(1 L.S.B. $= \frac{3.84}{256} = 15.0 \text{ millivolts.}$

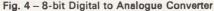

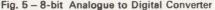

#### 2. 8-bit Analogue to Digital Converter

A counter type analogue to digital converter can be constructed by adding a voltage comparator as in Fig. 5. On the negative edge of the CONVERT COMMAND Pulse the counter is set to zero and the STATUS output to logical 1. On the positive edge the counter starts to count up from zero. The analogue output ramps until it equals the analogue voltage applied to the other input of the comparator. At this point, any further clock pulses are inhibited and STATUS goes low to indicate that the output data is valid.

The conversion time depends upon the value of the analogue input and for full scale reading is given by the clock frequency divided into the maximum number of counts.

For example if  $F_{clock} = 256 \text{ kHz}$ conversion (for F.S.R.) =  $\frac{2^8}{256,000}$  seconds = 1 millisecond

#### 3. Precision Ramp Generator

The inclusion of an 8-bit binary counter on the chip gives the ZN425E a useful ramp generator function. The circuit, Fig. 6 uses the same buffer stages as the D to A converter. The calibration procedure is also the same. Holding pin 2 low will set all bits to ON and if RESET is taken low with pin 2 high all the bits are turned OFF. If the end voltages of the ramp are not required to be set accurately then the buffer stage could be omitted and the voltage ramp will appear directly at pin 14

Fig. 6 - Precision Ramp Generator

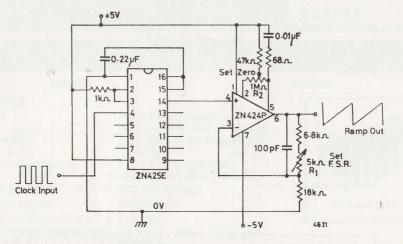

#### 4. Alternative Output Buffer using the ZLD741

The following circuit, employing the ZLD741 operational amplifier, may be used as the output buffer for both the 8-bit Digital to Analogue Converter (Fig. 4) and the Precision Ramp Generator (Fig. 6).

Fig. 7 - The ZLD741 as Output Buffer

#### 5. Further Applications

Details of a wide range of additional applications, described in the Ferranti publication 'Application Report-ZN425E 8-bit A-D/D-A Converter', are also available.

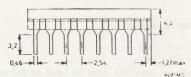

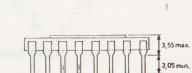

#### **PACKAGE DETAILS**

**ZN425E**

ZN425.J

254

16 Lead Moulded D.I.L.

16 Lead Ceramic D.I.L.

**Dimensions in millimetres**

0 46

#### © FERRANTI LTD. 1977

The copyright in this work is vested in Ferranti Limited and this document is issued for the purpose only for which it is supplied. No licence is implied for the use of any patented feature. It must not be reproduced in whole or in part, or used for tendering or manufacturing purposes except under an agreement or with the consent in writing of Ferranti Ltd. and then only on the condition that this notice is included in any such reproduction. Information furnished is believed to be accurate but no liability in respect of any use of it is accepted by Ferranti Ltd.

FERRANTI LIMITED, ELECTRONIC COMPONENTS DIVISION GEM MILL, CHADDERTON, OLDHAM OL9 8NP. Tel: 061-624 0515 Telex: 668038 Ferranti GmbH, Widenmayerstrasse 5, D8000-Munich-22, West Germany Tel: (089) 293871 Telex: 523980

Ferranti Electric Inc., East Bethpage Road, Plainview, N.Y. 11803, U.S.A. Tel: 516-293 8383 Telex: 510 224 6483

Issue 2, July 1977 8M

Printed in England HK&R

5365C