# ZT2046

## 4-WIRE RESISTIVE TOUCH SCREEN CONTROLLER

5F, No.2, Industry E. 9<sup>th</sup> Rd., Science-Based Industrial Park, Hsinchu 30075 Taiwan

Tel: (886) 3577 7509 Fax: (886) 3577 7390 Email: sales@zilltek.com

**Rev. 0.9**

Apr. 08, 2009

■ This data sheet is subject to change without notice.

## **REVISION HISTORY**

| Rev. | Date     |

|------|----------|

| 0.5  | 08.02.28 |

| 0.6  | 08.04.28 |

| 0.7  | 08.04.29 |

| 0.8  | 09.04.02 |

| 0.9  | 09.04.08 |

|      |          |

#### **FEATURES**

4-wire resistive touch screen interface

Digital I/O: 1.5V to 5.25V

One auxiliary analog input

Touch pressure measurement

On-chip reference voltage: 2.5V

Operation voltage: 2.2V to 5.25V

Specified throughput rate: 125 KSPS

Battery voltage measurement: 0 to 6V

• Internal temperature sensor: -40 to 85°C

Programmable 8-bit or 12-bit resolution

Available In QFN package

RoHS compliant and 100% lead (Pb) free

#### **APPLICATIONS**

- Pagers

- Cellular Phones

- Portable Instruments

- Point-of-Sale Terminals

- Touch Screen Monitors

- Personal Digital Assistants

#### **ORDERING INFORMATION**

| PART    | PACKAGE     | PACKAGE RoHS Shi |                     |

|---------|-------------|------------------|---------------------|

| ZT2046Q | QFN-16L 4x4 | Yes              | Tape and Reel, 5000 |

#### **DESCRIPTION**

The ZT2046 is a 4-wire touch screen controller with programmable 8-bit or 12-bit successive approximation converter, synchronous serial interface and low on-resistance switches. The ZT2046 operates from 2.2V to 5.25V and features touch pressure measurement, battery measurement, and temperature measurement. The ZT2046 also has an internal 2.5V reference that can be used for the auxiliary analog input, battery voltage detection, and temperature measurement modes. The internal reference can be shut down to save power if not in use. An external reference can also be applied and ranges between 1V and VCC. The auxiliary analog input varies from 0V to reference.

The ZT2046 features low power and high speed operation. The power consumption is less than 0.8mW at 2.7V, internal reference off, and 125kHz sample rate, which makes the device ideal for battery powered systems such as cellular phones with resistive touch screens and other portable instruments. The ZT2046 is available in 16-lead QFN green packages.

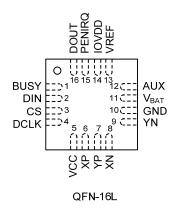

#### **Pin Configuration**

#### **Absolute Maximum Rating**

| Power Dissipation                | 250mW                |

|----------------------------------|----------------------|

| Digital Inputs to GND            | 0.3V to IOVDD + 0.3V |

| Analog Inputs to GND             | 0.3V to VCC + 0.3V   |

| VCC and IOVDD to GND             | 0.3V to +6V          |

| Storage Temperature Range        | 65°C to +150°C       |

| Operating Temperature Range      | 40°C to +85°C        |

| Maximum Junction Temperature     | +150°C               |

| Lead Temperature (soldering, 10s | s)+300°C             |

**CAUTION**: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **Electro-Static Discharge Sensitivity**

This integrated circuit can be damaged by ESD. It is recommended that all integrated circuits be handled with proper precautions. Failure to observe proper handling and in-

stallation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure.

#### **Pin Description**

| QFN | NAME      | Description                                                                                                                                  |

|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | vcc       | Power supply input                                                                                                                           |

| 6   | XP        | X+ position input                                                                                                                            |

| 7   | YP        | Y+ position input                                                                                                                            |

| 8   | XN        | X- position input                                                                                                                            |

| 9   | YN        | Y- position input                                                                                                                            |

| 10  | GND       | Ground                                                                                                                                       |

| 11  | $V_{BAT}$ | Battery monitor input                                                                                                                        |

| 12  | AUX       | Auxiliary analog input                                                                                                                       |

| 13  | VREF      | Reference input/output                                                                                                                       |

| 14  | IOVDD     | Digital I/O power supply                                                                                                                     |

| 15  | PENIRQ    | Pen interrupt                                                                                                                                |

| 16  | DOUT      | Serial data output; The bits are clocked out on the falling edge of DCLK. This output is high impedance when CS is high.                     |

| 1   | BUSY      | Busy logic output; This output is high impedance when CS is high.                                                                            |

| 2   | DIN       | Serial data input; If CS is low, data is clocked into the register on the rising edge of DCLK.                                               |

| 3   | cs        | Chip select input; This input controls conversion timing and enables the serial input/output register. CS high = power-down mode (ADC only). |

| 4   | DCLK      | External clock input; This clock runs the SAR conversion process and synchronizes serial data I/O.                                           |

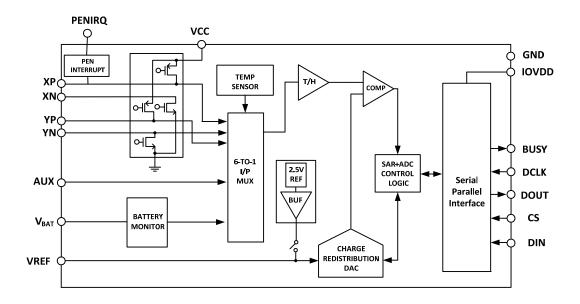

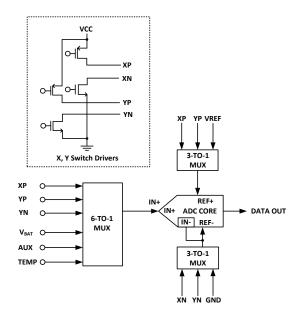

#### **Block Diagram**

## **Electrical Specifications**

VCC = 2.7V to 3.6V,  $T_A = -40^{\circ}\text{C}$  to +85°C, VREF = 2.5V internal reference,  $f_{DCLK} = 2\text{MHz}$ , 12-bit mode, digital inputs = GND or IOVDD, unless otherwise noted.

| PARAMETER                      | TEST CONDITIONS                                           | MIN  | TYP  | MAX     | UNIT             |

|--------------------------------|-----------------------------------------------------------|------|------|---------|------------------|

| POWER-SUPPLY REQUIREMENTS      |                                                           |      |      |         |                  |

| VCC <sup>1</sup>               | Specified Performance                                     | 2.7  |      | 3.6     | V                |

|                                | Operating Range                                           | 2.2  |      | 5.25    | V                |

| IOVDD <sup>2</sup>             |                                                           | 1.5  |      | VCC     | V                |

| Quiescent Current <sup>3</sup> | VCC = 3.6V, Internal VREF Off, f <sub>DCLK</sub> = 2MHz   |      | 380  |         | μΑ               |

|                                | VCC = 3.6V, Internal VREF On, f <sub>DCLK</sub> = 2MHz    |      | 670  |         | μA               |

|                                | VCC = 2.7V, Internal VREF Off, f <sub>DCLK</sub> = 200kHz |      | 170  |         | μA               |

|                                | Power-Down Mode with                                      |      |      | 3       | μA               |

|                                | CS = DCLK = DIN = IOVDD                                   |      |      |         | ·                |

| Power Dissipation              | VCC = +2.7V                                               |      |      | 1.8     | mW               |

| ANALOG INPUT                   |                                                           |      |      |         |                  |

| Input Voltage Range            |                                                           | 0    |      | VREF    | V                |

| Absolute Input Range           | Positive Input                                            | -0.2 |      | VCC+0.2 | V                |

| ,                              | Negative Input                                            | -0.2 |      | 0.2     | V                |

| Input Capacitance              | .0.1                                                      |      | 25   |         | pF               |

| Leakage Current                |                                                           |      | 0.1  |         | μA               |

| REFERENCE INPUT                |                                                           |      |      |         |                  |

| Range                          |                                                           | 1.0  |      | VCC     | V                |

| Input Impedance                | SER/DFR = 0, PD1 = 0                                      |      | 1    |         | GΩ               |

|                                | Internal VREF Off                                         |      | _    |         |                  |

|                                | Internal VREF On                                          |      | 250  |         | Ω                |

| REFERENCE OUTPUT               |                                                           |      |      |         |                  |

| Internal Reference Voltage In- |                                                           | 2.45 | 2.50 | 2.55    | V                |

| ternal Reference Drift         |                                                           |      | 15   |         | ppm/°C           |

| Quiescent Current              |                                                           |      | 500  |         | μΑ               |

| SYSTEM PERFORMANCE             |                                                           |      |      |         | F                |

| Resolution                     |                                                           |      | 12   |         | Bits             |

| No Missing Codes               |                                                           | 11   |      |         | Bits             |

| Integral Linearity Error       |                                                           |      |      | ±2      | LSB <sup>4</sup> |

| Offset Error                   |                                                           |      |      | ±6      | LSB              |

| Gain Error                     | External VREF                                             |      |      | ±4      | LSB              |

| Noise                          | Including Internal VREF                                   |      | 70   |         | μVrms            |

| Power-Supply Rejection         |                                                           |      | 70   |         | dB               |

| SAMPLING DYNAMICS              |                                                           |      |      |         |                  |

| Conversion Time                |                                                           |      |      | 12      | CLK Cycles       |

| Acquisition Time               |                                                           | 3    |      |         | CLK Cycles       |

| Throughput Rate                |                                                           |      |      | 125     | kHz              |

| SWITCH DRIVERS                 |                                                           |      |      |         |                  |

| On-Resistance                  |                                                           |      |      |         |                  |

| Y+, X+                         |                                                           |      | 5    |         | Ω                |

| Y-, X-                         |                                                           |      | 6    |         | Ω                |

| BATTERY MONITOR                |                                                           |      |      |         |                  |

| Input Voltage Range            |                                                           | 0.5  |      | 6.0     | V                |

| Input Impedance                |                                                           | 0.5  |      | 0.0     | •                |

| Sampling Battery               |                                                           |      | 10   |         | ΚΩ               |

| Battery Monitor Off            |                                                           |      | 1    |         | GΩ               |

| Accuracy                       | V <sub>BAT</sub> = 0.5V to 5.5V, External VREF            | -2   | _    | +2      | %                |

| , would do                     | $V_{BAT} = 0.5V \text{ to } 5.5V, \text{ External VREF}$  | -3   | I    | +3      | %                |

## **Electrical Specifications (continued)**

| PARAMETER               | TEST CONDITIONS                       | MIN         | TYP               | MAX         | UNIT |

|-------------------------|---------------------------------------|-------------|-------------------|-------------|------|

| DIGITAL I/O             |                                       |             |                   |             |      |

| Capacitance             | All Digital Control Input Pins        |             | 5                 | 15          | pF   |

| $V_{IH}$                | IIH   ≤ +5μA                          | IOVDD • 0.7 |                   | IOVDD + 0.3 | V    |

| $V_{IL}$                | IIL   ≤ +5μA                          | -0.3        |                   | 0.3 • IOVDD | V    |

| V <sub>OH</sub>         | IOH = −250μA                          | IOVDD • 0.8 |                   |             | V    |

| V <sub>OL</sub>         | IOL = 250μA                           |             |                   | 0.4         | V    |

| Output Format           |                                       | St          | l<br>traight Bina | ry          |      |

| TEMPERATURE MEASUREMENT |                                       |             |                   |             |      |

| Temperature Range       |                                       | -40         |                   | +85         | °C   |

| Resolution              | Differential Method⁵                  |             | 1.6               |             | °C   |

|                         | Single Conversion Method <sup>6</sup> |             | 0.3               |             | °C   |

| Accuracy                | Differential Method⁵                  |             | ±2                |             | °C   |

|                         | Single Conversion Method <sup>6</sup> |             | ±3                |             | °C   |

| TEMPERATURE RANGE       |                                       |             |                   |             |      |

| Specified Performance   |                                       | -40         |                   | +85         | °C   |

- 1. ZT2046 operates down to 2.2V.

- 2. IOVDD must be (+VCC).

- 3. Combined supply current from +VCC and IOVDD. Typical values obtained from conversions on AUX input with PD0 = 0.

- 4. LSB means Least Significant Bit. With VREF = +2.5V, 1 LSB is  $610\mu V$ .

- 5. Difference between TEMP0 and TEMP1 measurement. No calibration necessary.

- 6. Temperature drift is −2.1mV/°C.

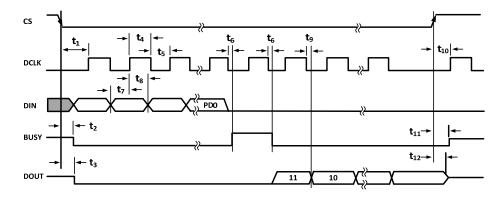

### **Timing Specifications**

| Symbol           | Description                         | Min | MAX | Units |

|------------------|-------------------------------------|-----|-----|-------|

| t <sub>ACQ</sub> | Acquisition time                    | 1.5 |     | μs    |

| t <sub>1</sub>   | CS falling to first DCLK rising     | 100 |     | ns    |

| t <sub>2</sub>   | CS falling to BUSY enabled          |     | 200 | ns    |

| t <sub>3</sub>   | CS falling to DOUT enabled          |     | 200 | ns    |

| t <sub>4</sub>   | DCLK high                           | 200 |     | ns    |

| t <sub>5</sub>   | DCLK low                            | 200 |     | ns    |

| t <sub>6</sub>   | DCLK falling to BUSY rising/falling |     | 200 | ns    |

| t <sub>7</sub>   | DIN valid prior to DCLK rising      | 100 |     | ns    |

| t <sub>8</sub>   | DIN hold after DCLK high            | 50  |     | ns    |

| t <sub>9</sub>   | DCLK falling to DOUT valid          |     | 200 | ns    |

| t <sub>10</sub>  | CS rising to DCLK ignored           | 10  |     | ns    |

| t <sub>11</sub>  | CS rising to BUSY disabled          |     | 200 | ns    |

| t <sub>12</sub> CS rising to DOUT |  | 200 | ns |

|-----------------------------------|--|-----|----|

|-----------------------------------|--|-----|----|

Table 1. Configuration of analog input, reference and touch screen in single-ended / differential reference mode

| A2 | A1 | A0 | SER/DFR | Analog In | Measure   | X Driver | Y Driver | +REF | -REF  |        |      |      |

|----|----|----|---------|-----------|-----------|----------|----------|------|-------|--------|------|------|

| 0  | 0  | 0  | 1       | TEMP0     | TEMP      | Off      | Off      | VREF | GND   |        |      |      |

| 0  | 0  | 1  | 1       | XP        | Υ         | Off      | On       | VREF | GND   |        |      |      |

| 0  | 1  | 0  | 1       | $V_{BAT}$ | $V_{BAT}$ | Off      | Off      | VREF | GND   |        |      |      |

|    | 1  | 1  | 1       | XP        | 71        | XP Off   | YP On    | VDEE | CND   |        |      |      |

| 0  | 1  | 1  | 1       | XP Z1     | XN On     | YN Off   | VREF     | GND  |       |        |      |      |

| 1  | 0  | 0  | 1       | VNI       | 72        | XP Off   | YP On    | VREF | GND   |        |      |      |

|    | U  | U  | U       | U         | 1         | TIN      | YN       | Z2   | XN On | YN Off | VILE | טווט |

| 1  | 0  | 1  | 1       | YP        | X         | On       | Off      | VREF | GND   |        |      |      |

| 1  | 1  | 0  | 1       | AUX       | AUX       | Off      | Off      | VREF | GND   |        |      |      |

| 1  | 1  | 1  | 1       | TEMP1     | TEMP      | Off      | Off      | VREF | GND   |        |      |      |

| 0  | 0  | 1  | 0       | XP        | Υ         | Off      | On       | YP   | YN    |        |      |      |

| 0  | 1  | 1  | 0       | XP        | 71        | XP Off   | YP On    | YP   | VNI   |        |      |      |

| 0  | 1  | 1  | 0       | XP        | Z1        | XN On    | YN Off   | I IP | XN    |        |      |      |

| 1  | 0  | 0  | 0       | VNI       | 72        | XP Off   | YP On    | VD   | VNI   |        |      |      |

| 1  | 0  | 0  | 0       | YN        | Z2        | XN On    | YN Off   | YP   | XN    |        |      |      |

| 1  | 0  | 1  | 0       | YP        | Х         | On       | Off      | XP   | XN    |        |      |      |

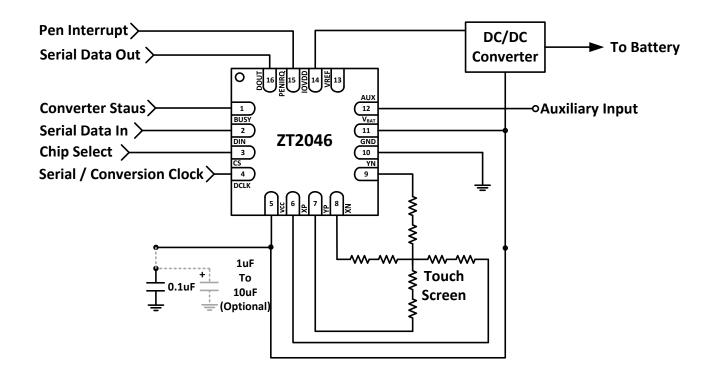

Figure 1. Typical application circuit of the ZT2046

#### **FUNCTIONAL DESCRIPTION**

#### **Theory of Operation**

The ZT2046 is a fast, low power, 12-bit successive approximation register (SAR) analog-to-digital converter (ADC). The ZT2046 can be operated from 2.2V to 5.25V. The throughput rate of the ZT2046 reaches 125 KSPS when 2MHz clock is provided. The sample and hold function comes from the architecture of capacitive redistribution. The ZT2046 integrates functions of 12-bit ADC, reference, temperature sensor and battery voltage monitor into a single chip.

The typical application circuit of the ZT2046 is shown in Figure 1. The device features an internal 2.5V reference (VREF) and uses an external clock. The serial clock input (DCLK) accesses data from the part and also provides the clock source for ADC. The VREF can be replaced with an external, low-impedance voltage source between 1V and VCC. The value of the reference voltage directly determines the input range of the converter.

The analog input to the ADC is applied via an internal multiplexer. This analog input can be any one of X-, Y-, and Z-Position coordinates, auxiliary input, battery voltage, or chip temperature. The ZT2046 is configured with low on-resistance switch drivers that allow an unselected ADC input channel to provide power and the accompanying pin to provide ground for a touch screen. In some cases, the on-resistance may be a source of error. However, this error can be negated with a differential input to the converter and a differential reference architecture.

#### **Analog Input**

Figure 2 shows a simplified diagram of the analog input of the ZT2046 incluing the differential input of the ADC, the multiplexer and the differential reference. Table 1 shows the relationship between the A2, A1, A0, and SER/DFR control bits and the configuration of the ZT2046. The control bits are provided serially via the DIN pin. For more information, see the *Digital Interface* section of this data sheet.

When the converter enters the hold mode, the voltage difference between the +IN and -IN inputs (shown in Figure 2) is captured on the internal capacitor array. The input current into the analog inputs depends on the

conversion rate of the device. During the sample period, the source must charge the internal sampling capacitor (typically 25pF). Once the capacitor is fully charged, there is no further input current. The rate of charge transfer from the analog source to the converter is a function of conversion rate.

Figure 2. Simplified diagram of analog input

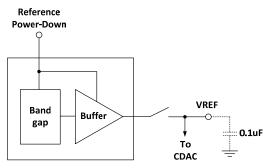

#### **Internal Reference**

The ZT2046 has an internal reference voltage of 2.5V that can be turned on or off with the power-down address, PD1 (see Table 4 and Figure 3). Typically, the internal reference voltage is only used in the single-ended mode for battery monitoring, temperature measurement, and for using the auxiliary input. Optimal touch screen performance is achieved when using the differential mode. The turn-on time of the internal reference is typically 50us without a load. However, a 0.1uF capacitor on the VREF pin is recommended for optimum performance. For the compatibility with the UH7843, the internal reference voltage must be commanded to be off.

Figure 3. Simplified diagram of the internal reference

#### **Reference Input**

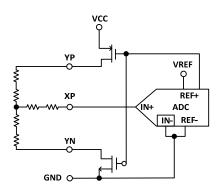

The voltage difference between +REF and -REF (see Figure 2) sets the analog input range. The ZT2046 operates with a reference in the range of 1V to VCC. The internal reference can be replaced with an external reference. For best performance, the internal reference should be disable when an external reference is applied. The reference input can be made in single-ended mode or differential mode depending on the control bit of SER/DFR. If SER/DFR is set to 1, then a single-ended conversion is performed. Figure 4 shows the configuration of singled-ended reference. +REF conncets to either internal reference or external reference. -REF is set to ground. The YP and YN switch drivers are turned on and the voltage on XP, the selected input channel to the ADC, is digitized and converted with the reference. There are several critical items concerning the reference input and its wide voltage range. As the reference voltage is reduced, the analog voltage weight of each digital output code (referred to as LSB size) is also reduced. The LSB (least significant bit) size is equal to the reference voltage divided by 4096 in 12-bit mode. Any offset or gain error inherent in the ADC appears to increase, in terms of LSB size, as the reference voltage is reduced. For example, if the offset of a given converter is 2LSBs with a 2.5V reference, it is typically 5LSBs with a 1V reference. In each case, the actual offset of the device is the same, 1.22mV. With a lower reference voltage, more care must be taken to provide a clean layout including adequate bypassing, a clean (low-noise, low- ripple) power supply, a low-noise reference (if an external reference is used), and a low-noise input signal.

The voltage into the VREF input directly drives the capacitor digital-to-analog converter (CDAC) portion of the ZT2046. Therefore, the input current is very low (typically  $< 13\mu$ A).

There is also a critical item regarding the reference

when making measurements while the switch drivers are ON. For this discussion, it is useful to consider the basic operation of the ZT2046 (see Figure 1). This particular application shows the device being used to digitize a resistive touch screen. A measurement of the current Y-Position of the pointing device is made by connecting the X+ input to the ADC, turning on the Y+ and Y- drivers, and digitizing the voltage on X+ (Figure 4 shows a block diagram). For this measurement, the resistance in the X+ lead does not affect the conversion (it does affect the settling time, but the resistance is usually small enough that this is not a concern). However, because the resistance between Y+ and Y- is fairly low, the on-resistance of the Y drivers does make a small difference. Under the situation outlined so far, it is not possible to achieve a OV input or a full-scale input regardless of where the pointing device is on the touch screen because some voltage is lost across the internal switches. In addition, the internal switch resistance is unlikely to track the resistance of the touch screen, providing an additional source of error.

Figure 4. Simplified diagram of single-ended reference (SER/DFR high, Y switches enabled, XP is analog input)

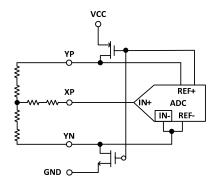

This situation can be remedied as shown in Figure 5. By setting the SER/DFR bit low, the +REF and -REF inputs are connected directly to Y+ and Y-, respectively, making the analog-to-digital conversion ratiometric. The result of the conversion is always a percentage of the external resistance, regardless of how it changes in relation to the on-resistance of the internal switches. Note that there is an important consideration regarding power dissipation when using the ratiometric mode of operation (see the Power Dissipation section for more details).

Figure 5. Simplified diagram of differential reference (SER/DFR low, Y switches enabled, XP is analog input)

As a final note about the differential reference mode, it must be used with +VCC as the source of the +REF voltage and cannot be used with VREF. It is possible to use a high-precision reference on VREF and single-ended reference mode for measurements that do not need to be ratiometric. In some cases, it is possible to power the converter directly from a precision reference. Most references can provide enough power for the ZT2046, but might not be able to supply enough current for the external load (such as a resistive touch screen).

#### **Touch Screen Settling Issue**

There are two key touch-screen characteristics that can degrade accuracy. First, the parasitic capacitance between the top and bottom layers of the touch screen can result in electrical ringing. Second, vibration of the top layer of the touch screen can cause mechanical contact bouncing.

External capacitors may be used across the touch screen to eliminate noise generated by the LCD panel or backlight circuitry. These capacitors need a settling time requirement and can result in a gain error when the input signal, reference, or both have not settled to the final steady-state value before the ADC samples the inputs. Three methods used to alleviate or avoid this issue are described below.

The first method is to stop or slow down the DCLK for the required touch screen settling time. This allows the input and reference to stablize during the acquisition time (DCLK 6 to 8 of the ZT2046; see Figure 9). This method can be applied in both the single-ended and the differential modes. Another method is to operate the ZT2046 in the differential mode only for the touch screen measurements and program the ZT2046 to keep the touch screen drivers on and not go into power-down (PD0 = 1). Additional conversions with the same address

are necessary until the input signal settles. Once the required conversions have been made, the MCU commands the ZT2046 to go into its power-down mode on the last measurement. The last method is to operate in the 15-DCLK mode, keeping the touch screen drivers on until commanded to stop by the processor.

#### **Internal Temperature Sensor**

The ZT2046 offers two temperature measurement options: single-ended conversion and differential conversion. Both options rely on the temperature characteristics of diode junction. The diode forward bias voltage ( $V_{BE}$ ) vs. temperature is a well-defined characteristic. The ambient temperature can be predicted by knowing the value of the  $V_{BE}$  at a fixed temperature and then monitoring the change of  $V_{BE}$  as the temperature changes. The single conversion mode requires calibration at a known temperature, but only needs a single reading to calculate the ambient temperature. This assumes a diode temperature drift of -2.1mV/°C. This method achieves a resolution of 0.3°C/LSB and a typical accuracy of  $\pm 3^{\circ}$ C.

The differential conversion mode measures the temperature twice. The first time (Temp0) is measured with a constant current into the diode. The second time (Temp1) is measured with a fixed multiple of the constant current into the same diode. The voltage difference between the first and second conversion is proportional to the absolute temperature and is expressed by the following formula:

$$T (^{\circ}C) = 2.573 * \Delta V (mV) - 273$$

where  $\Delta V$  is the voltage difference between Temp0 and Temp1. This method can provide more accurate absolute temperature measurement and higher resolution (1.6°C/LSB).

#### **Battery Voltage Monitor**

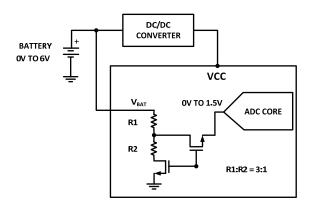

The ZT2046 can monitor the battery voltage from 0V to 6V as shown in Figure 6. The voltage to the VCC of ZT2046 is supplied at the desired level with a DC/DC converter (ex: ZT7103). The voltage on  $V_{BAT}$  is divided by an internal resistor network of 4. If a 6.0V battery voltage is applied on  $V_{BAT}$ , there is 1.5V at the ADC input. Table 1 shows the control bit settings required to perform a battery measurement.

Figure 6. Block diagram of battery measurement

#### **Touch-Pressure Measurement**

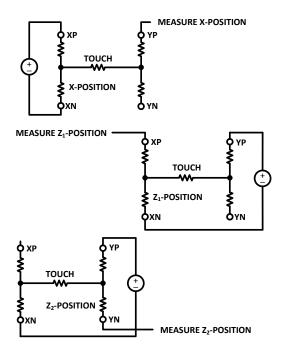

The ZT2046 offers two methods for measuring the pressure applied to the touch screen as shown in Figure 7. The 8-bit resolution mode would be recommended for this measurement but the following calculations use 12-bit resolution mode demonstrating its maximum accuracy. The first method performs pressure measurements using a known X-plate resistance. After completing three conversions of X-position, Z1-position and Z2-position, calculate the touch resistance with the following equation:

$$R_{touch} = R_{Nplate} \times \frac{X_{position}}{4096} \left( \frac{z_k}{z_k} - 1 \right)$$

The second method requires knowing both the X-plate and Y-plate resistance. Three conversions are required in this method: X-position, Y-position and Z1-position. Using the following equation calculates the touch resistance:

$$R_{touch} \equiv \frac{R_{Vplate} \cdot X_{position}}{4096} \left(\frac{4096}{z_1} - 1\right) - R_{Vplate} \left(1 - \frac{Y_{position}}{4096}\right)$$

Figure 7. Block diagram of pressure measurement

#### Serial Interface

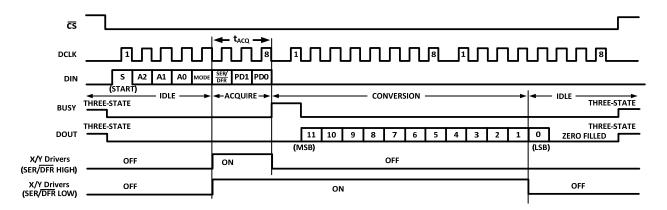

The typical operation of the serial interface consists of three inputs: DIN, DCLK, CS, and two outputs: DOUT, BUSY shown in figure 8. One complete conversion can be accomplished with 24 DCLK cycles. Logic high on CS disables the ZT2046 and makes DOUT in high impedance state. Pulling CS low enables the ZT2046 and takes the BUSY and DOUT out of three-state. The first eight DCLK cycles are used to provide the control byte via the DIN pin. Once the converter receives the first five control bits for the following conversion, it sets the input multiplexer and switches, and then enters the acquisition mode. During the acquisition mode, the X/Y switches are turned on except for battery and temperature measurement, single-ended or differential mode is determined, power-down and reference on/off are set. After 3 DCLK cycles of acquisition mode, the converter enters the conversion mode. The BUSY pin outputs high and returns low on the next falling edge of DCLK to inform the processor receiving the conversion data via the DOUT pin. There are 12 clock cycles to complete the A/D conversion. The X/Y switches are turned off during this period if in single-ended mode. A 13<sup>th</sup> clock cycle is needed for the last bit of conversion result. Three more low DCLK cycles are needed to complete the 24 DCLK transfer.

#### Input Control Bits

The ZT2046 needs 8-bit instructions via the DIN pin to perform the conversion as shown in Table 2. Table 3 describes the functions of the control bits. The first bit (S) has to be set to high to initiate the start of the conversion. If the start bit is set to low, the following input command is ignored. The next three bits (A2, A1, A0) after the S bit decide one input channel of the internal multiplexer. The input channel may be touch screen drivers (XP, YP) or touch pressure (XP, YN) or temperature input or battery input or auxiliary input, depending on the settings of A2, A1 and A0. More detailed information can be referred to the Table 1. Bit 3 (MODE) controls the resolution of the conversion. If the MODE is set to low, 12-bit conversion is performed. Otherwise, the resolution is reduced to 8-bit. Bit 2 (SER/DFR) specifies single-ended (high) or differential (low) reference mode. The differential mode, also called ratiometric mode, has better accuracy than single-ended mode when measuring the X-position, Y-position and touch pressure. If X-position, Y-position and touch pressure are measured in the single-ended mode, an external reference voltage is needed. SER/DFR along with A2, A1 and A0 controls the input channel of the internal multiplexer. Please note that the differential mode can only be used in touch screen and touch pressure measurements. Other measurements are set in single-ended mode. The last two bits (PD1, PD0) are power-down bits. Table 4 lists four available operations for ZT2046. The internal reference can be turned on or off independent of the ADC.

Table 2. Order and symbols of the 8 control bits

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|---------|-------|-------|

| S     | A2    | A1    | A0    | MODE  | SER/DFR | PD1   | PD0   |

Table 3. Description of the control bits

| Bit No. | Symbol   | Content                                          |

|---------|----------|--------------------------------------------------|

| 7       | S        | Start bit; This bit must be high to initiate the |

|         |          | control bits.                                    |

| 6 – 4   | A2 – A0  | Channel select bits; These three address bits    |

|         |          | along with SER/DFR determine the active          |

|         |          | analog input to the A/D converter. Further       |

|         |          | information can be referred to Table 1.          |

| 3       | MODE     | ADC resolution select bit; High is 8-bit con-    |

|         |          | version and low is 12-bit conversion.            |

| 2       | SER/DFR  | Single-ended (high) / Differential (low) ref-    |

|         |          | erence select bit; Please note that DFR is       |

|         |          | only used in the touch screen measurement.       |

| 1, 0    | PD1, PD0 | Power-down select bits; Please see the Table     |

|         |          | 4 for detailed operation.                        |

Table 4. Power-down and internal reference options

| PD1 | PD0 | PENIRQ   | Content                                 |

|-----|-----|----------|-----------------------------------------|

| 0   | 0   | Enabled  | Power-down between conversions; The     |

|     |     |          | YN switch is on and PENIRQ is enable in |

|     |     |          | this mode.                              |

| 0   | 1   | Disabled | Reference is off and ADC is on.         |

| 1   | 0   | Enabled  | Reference is on and ADC is off.         |

| 1   | 1   | Disabled | Reference and ADC are always on.        |

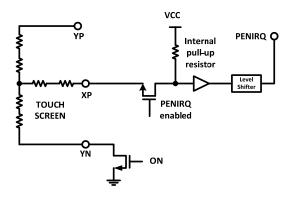

#### **Pen Interrupt Request**

The PENIRQ function is shown in Figure 9. An internal pull-up resistor is designed. When the ZT2046 is operated in the power-down mode, the PENIRQ is enable and the YN switch is on so that YN connects to GND. Before pressing the touch screen, there is no connection between XP and the internal pull-up resistor. Therefore the PENIRQ outputs high. Once the touch screen is pressed by a pen or finger, the PENIRQ outputs low due to the circuit path to GND. Besides, the PENIRQ is disabled and keeps low during the measurement of X-, Y- and Z-positions. The PENIRQ is disabled and keeps high during the measurement cycle of temperature, battery voltage and auxiliary input. If PD0 is set to high, the PENIRQ is disabled and can not detect the action of the touch screen. To recover the detection ability during the

measurement cycle, PD0 should be written to low again.

Figure 9. Block diagram of PENIRQ

Figure 8. Timing chart with 24 DCLKS per cycle and 8-bit bus interface

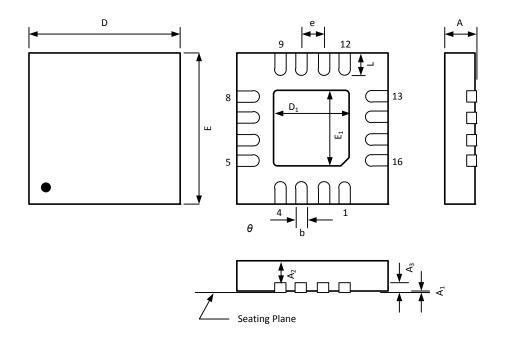

## PACKAGE DIMENSION (QFN-16L)

| SYMBOLS        | DIMENSION (MM) |      |      | DIMENSION (MIL) |       |       |

|----------------|----------------|------|------|-----------------|-------|-------|

|                | MIN            | NOM  | MAX  | MIN             | NOM   | MAX   |

| Α              | 0.76           | 0.8  | 0.84 | 30              | 31    | 33    |

| $A_1$          | 0              | 0.02 | 0.04 | 0               | 0.8   | 1.5   |

| A <sub>2</sub> | 0.57           | 0.6  | 0.63 | 22              | 24    | 25    |

| A <sub>3</sub> | 0.20 REF.      |      |      | 8.0 REF.        |       |       |

| b              | 0.25           | 0.30 | 0.35 | 9.84            | 11.81 | 13.78 |

| D              | 3.90           | 4.00 | 4.10 | 154             | 157   | 161   |

| $D_1$          | 2.05           | 2.10 | 2.15 | 80.70           | 82.68 | 84.65 |

| E              | 3.90           | 4.00 | 4.10 | 154             | 157   | 161   |

| E <sub>1</sub> | 2.05           | 2.10 | 2.15 | 80.70           | 82.68 | 84.65 |

| е              | 0.650 BSC      |      |      | 25.59 BSC       |       |       |

| L              | 0.50           | 0.55 | 0.60 | 19.69           | 21.65 | 23.62 |