# Li+ Charger Protection IC with Integrated P-MOSFET

**FEATURES**

Input over-voltage protection

Input over-current protection

Battery over-voltage protection

High immunity of false triggering

High accuracy protection threshold

RoHS Compliant and 100% Lead (Pb) Free

8 OUT

<u><\_7</u>]out

<\_6 CHRIN

6 ACIN

5 GND

4 VBAT

5

GATDRV

Thermal shutdown protection

Top View

TDFN 2x2-8L

Exposed

Pad (EP)

Top View

SOT23-6L

0

A built-in P-MOSFET

APPLICATIONS

**Pins Configuration**

Cell phones

ACIN

ACIN

VBAT

Γī

GND 3

4

OUT 1

CHRIN 2

GATDRV 3

#### DESCRIPTION

The ZT2306/A provides complete Li+ charger protection against input over-voltage, input over-current, and battery over-voltage. When any of the monitored parameters are over the threshold, the IC removes the power from the charging system by turning off an internal switch. All protections also have deglitch time against false triggering due to voltage spikes or current transients.

The ZT2306/A integrates a P-MOSFET with the body diode reverse protection to replace the external P-MOSFET and Schottky diode for charger function of cell phone's PMIC. When the CHRIN voltage drops below  $V_{BAT}$ +20mV, the internal power select circuit will reverse the body diode's terminal to prevent a reverse current flowing from the battery back to CHRIN pin.

The ZT2306/A is available in the TDFN 2x2-8L (EP) and SOT23-6L packages, and it is RoHS compliant and 100% lead (Pb) free.

#### ORDERING INFORMATION

| PART     | PACKAGE                    | RoHS | Ship, Quantity |

|----------|----------------------------|------|----------------|

| ZT2306D  | TDFN 2x <mark>2-8</mark> L | Yes  | Tape and Reel  |

| ZT2306AD | TDFN 2x2-8L                | Yes  | Tape and Real  |

| ZT2306S  | SOT23-6L                   | Yes  | Tape and Real  |

| ZT2306AS | SOT23-6L                   | Yes  | Tape and Real  |

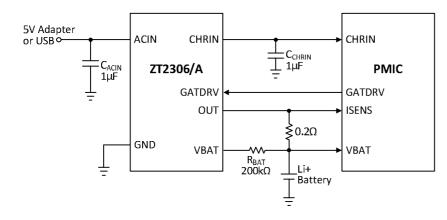

# Typical Application Circuit

#### Absolute Maximum Ratings

| ACIN Input Voltage to GND (V <sub>ACIN</sub> ) –0.3V to +30V  |

|---------------------------------------------------------------|

| CHRIN to GND Voltage (V <sub>CHRIN</sub> ) –0.3V to +7V       |

| GATDRV to GND Voltage (V_GATDRV) –0.3V to $V_{\text{CHRIN}}$  |

| VBAT to GND Voltage (V <sub>BAT</sub> ) –0.3V to +7V          |

| OUT to GND Voltage (V <sub>OUT</sub> ) –0.3V to +7V           |

| OUT Output Current (I <sub>OUT</sub> ) 1.5A                   |

| Junction Temperature (T <sub>J</sub> ) +150°C                 |

| Lead Temperature (T <sub>SDR</sub> , Soldering, 10sec) +260°C |

| Operating Temperature Range (T <sub>A</sub> )40°C to +85°C    |

| Storage Temperature Range (T <sub>STG</sub> ) –65°C to +150°C |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **Electro-Static Discharge Sensitivity**

This integrated circuit can be damaged by ESD. It is recommended that all integrated circuits be handled with proper precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure.

## Package Thermal Characteristics

| TDFN 2x2-8L                         |         |

|-------------------------------------|---------|

| Thermal Resistance, θ <sub>JA</sub> | 80°C/W  |

| SOT23-6L                            |         |

| Thermal Resistance, θ <sub>JA</sub> | 220°C/W |

#### **Pins Description**

| TDFN | SOT | Symbol         | Description                                              |

|------|-----|----------------|----------------------------------------------------------|

| 1    | 6   | ACIN           | Power supply input.                                      |

| 2    | 0   | ACIN           | rower supply input.                                      |

| 3    | 5   | GND            | Ground.                                                  |

| 4    | 4   | VBAT           | Battery voltage sense input.                             |

| 5    | 3   | GATDRV         | Internal P-MOSFET gate input.                            |

| 6    | 2   | CHRIN          | Output pin.<br>Provide supply voltage to PMIC.           |

| 7    | 1   | OUT            | Output pin. Supply source current                        |

| 8    | 1   | OUT            | for charging Li+ battery.                                |

| EP   |     | Exposed<br>pad | To be soldered to ground to promote thermal performance. |

N.

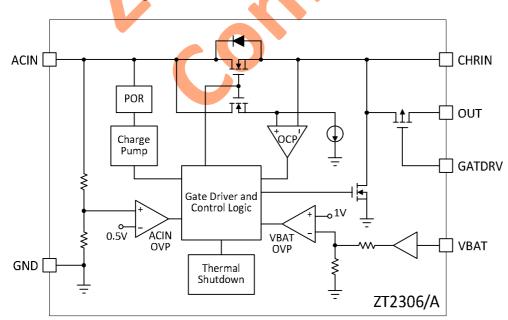

# Functional Block Diagram

# **Recommended Operating Conditions**

| PARAMETER          | Symbol            | MIN | MAX | UNIT |

|--------------------|-------------------|-----|-----|------|

| ACIN Input Voltage | V <sub>ACIN</sub> | 4.5 | 5.5 | V    |

| Output Current     | I <sub>OUT</sub>  | 0   | 700 | mA   |

# **Electrical Specifications**

( $V_{ACIN} = +5V$ ,  $V_{BAT} = +3.8V$ ,  $-40^{\circ}C < T_A < +85^{\circ}C$ , typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                              | Symbol                   | TEST CON                                                                 | MIN                            | ТҮР  | MAX  | UNIT       |          |

|--------------------------------------------------------|--------------------------|--------------------------------------------------------------------------|--------------------------------|------|------|------------|----------|

| ACIN Input Current and Power-0                         | Dn-Reset                 | (POR)                                                                    |                                |      | •    |            |          |

| ACIN Supply Current                                    | <b>I</b> <sub>ACIN</sub> | I <sub>OUT</sub> = 0A,                                                   | I <sub>CHRIN</sub> = <b>OA</b> |      | 250  | 350        | μA       |

| ACIN POR Threshold                                     | V <sub>ACIN</sub>        | V <sub>ACIN</sub> I                                                      | rising                         | 2.4  |      | 2.8        | V        |

| ACIN POR Hysteresis                                    |                          |                                                                          |                                | 200  | 250  | 300        | mV       |

| ACIN Power-On-Blanking Time                            | T <sub>B(ACIN)</sub>     |                                                                          |                                |      | 8    |            | ms       |

| Internal Switch On Resistance                          |                          |                                                                          |                                |      |      |            |          |

| ACIN to OUT On Resistance                              |                          | I <sub>OUT</sub> =                                                       | 0.7A                           |      | 0.5  |            | Ω        |

| CHRIN Discharge On Resistance                          |                          |                                                                          |                                |      | 500  |            | Ω        |

| Input Over-Voltage Protection (                        | OVP)                     |                                                                          |                                |      |      | •          |          |

|                                                        | V                        | M side s                                                                 | ZT2306                         | 6    | 6.17 | 6.35       | v        |

| Input OVP Threshold                                    | V <sub>OVP</sub>         | V <sub>ACIN</sub> rising                                                 | ZT2306A                        | 6.6  | 6.8  | 7          |          |

| Input OVP Hysteresis                                   |                          |                                                                          |                                | 200  | 300  | 400        | mV       |

| Input OVP Propagation Delay                            |                          |                                                                          |                                |      |      | 1          | μs       |

| Input OVP Recovery Time                                | T <sub>ON(OVP)</sub>     |                                                                          |                                |      | 8    |            | ms       |

| Over Current Protection (OCP)                          |                          |                                                                          |                                |      |      |            |          |

| OCP Threshold                                          | I <sub>OCP</sub>         |                                                                          |                                | 1    | 1.15 | 1.3        | Α        |

| OCP Blanking Time                                      | T <sub>B(OCP)</sub>      |                                                                          |                                |      | 176  |            | μs       |

| OCP Recovery Time                                      | T <sub>ON(OCP)</sub>     |                                                                          |                                |      | 64   |            | ms       |

| Battery Over Voltage Protection                        |                          |                                                                          |                                |      |      |            |          |

| Battery OVP Threshold                                  | V <sub>BOVP</sub>        | V <sub>BAT</sub> r                                                       | ising                          | 4.32 | 4.35 | 4.38       | V        |

| Battery OVP Hysteresis                                 |                          |                                                                          |                                | 220  | 270  | 320        | mV       |

| VBAT Pin Leakage Current                               | IVBAT                    | $V_{BAT} = +4.4V$                                                        |                                |      |      | 20         | nA       |

| Battery OVP Blanking Time                              | T <sub>B(BOVP)</sub>     |                                                                          |                                |      | 176  |            | μs       |

| Internal P-MOSFET (CHRIN, OUT                          | and GAT                  | DRV Pins)                                                                |                                |      |      |            |          |

|                                                        |                          | V <sub>CHRIN</sub> from low to high,<br>P-MOSFET is controlled by GATDRV |                                |      | 150  |            |          |

| V <sub>CHRIN</sub> -V <sub>BAT</sub> Lockout Threshold |                          |                                                                          |                                |      |      |            | mV       |

|                                                        |                          | V <sub>CHRIN</sub> from high to low, P-MOSFET is off                     |                                |      | 20   |            | <u> </u> |

| OUT Input Current                                      |                          | $V_{CHRIN} = 0V, V_{OUT} = +4.2V, GATDRV = GND$                          |                                |      |      | 1          | μA       |

| GATDRV Leakage Current                                 |                          | $V_{ACIN} = V_{CHRIN} = V_{OUT}$                                         |                                |      | 1    | μA         |          |

| OUT Leakage Current                                    |                          | $V_{ACIN} = V_{CHRIN} = V_{GATE}$                                        |                                |      | 1    | μ <b>A</b> |          |

| P-MOSFET Input Capacitance                             |                          |                                                                          |                                | 200  |      | pF         |          |

| GATDRV Input Resistance                                |                          |                                                                          |                                |      |      |            | Ω        |

| Over-Temperature Protection (C                         |                          | _ ·                                                                      |                                |      |      |            |          |

| Over-Temperature Threshold                             | T <sub>OTP</sub>         | T <sub>J</sub> ris                                                       |                                | 160  |      | °C         |          |

| Over-Temperature Hysteresis                            |                          |                                                                          |                                | 40   |      | °C         |          |

# FUNCTION DESCRIPTION

## **Pins Description**

| Symbol | Description                                                                                                                 |

|--------|-----------------------------------------------------------------------------------------------------------------------------|

| ACIN   | Power Supply Input. Connect this pin to<br>external DC supply. Bypass to GND with a 1µF<br>(minimum) ceramic capacitor.     |

| GND    | Ground terminal.                                                                                                            |

| VBAT   | Battery Voltage Sense Input. Connect this pin to pack positive terminal through a resistor.                                 |

| GATDRV | Internal P-MOSFET Gate Input.                                                                                               |

| CHRIN  | Output Pin. This pin provides supply voltage<br>to the PMIC input. Bypass to GND with a 1µF<br>(minimum) ceramic capacitor. |

| OUT    | Output Pins. These pins provide supply<br>source current in series with a resistor to<br>battery.                           |

| EP     | Exposed Thermal Pad. This pad must be electrically connected to the GND pin.                                                |

## ACIN Power-On-Reset (POR)

The ZT2306/A has a built-in power-on-reset circuit to keep the output shutting off until internal circuitry is operating properly. The POR circuit has hysteresis and a deglitch feature so that it will typically ignore undershoot transients on the input. When input voltage exceeds the POR threshold and after 8ms blanking time, the output voltage starts a soft-start to reduce the inrush current.

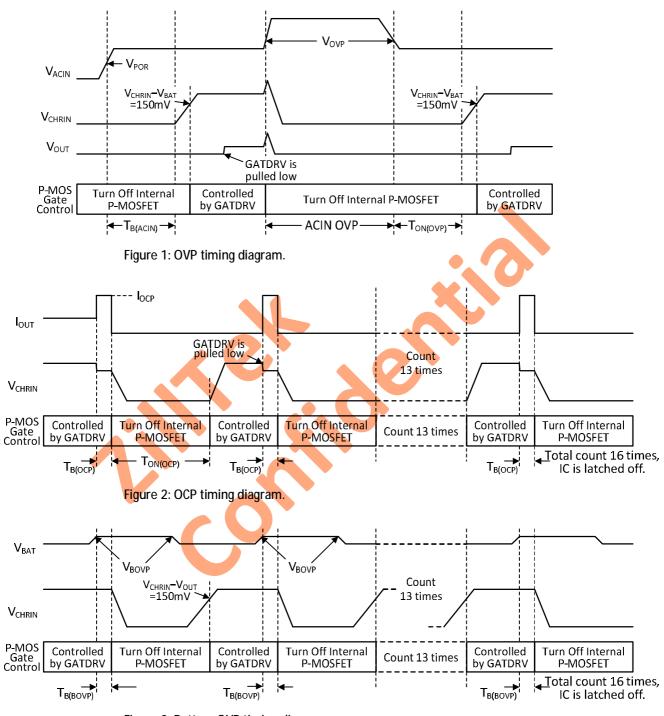

#### ACIN Over-Voltage Protection (OVP)

The input voltage is monitored by the internal OVP circuit. When the input voltage rises above the input OVP threshold, the internal FET will be turned off within 1ms to protect connected system on OUT pin. When the input voltage returns below the input OVP threshold minus the hysteresis, the FET is turned on again after 8ms recovery time. The input OVP circuit has a 300mV hysteresis and a recovery time of  $T_{ON(OVP)}$  to provide noise immunity against transient conditions.

## **Over-Current Protection (OCP)**

The output current is monitored by the internal OCP circuit. When the output current reaches the OCP threshold, the device limits the output current at OCP threshold level. If the OCP condition continues for a blanking time of  $T_{B(OCP)}$ , the internal power FET is turned off. After the recovery time of  $T_{ON(OCP)}$ , the FET will be turned on again. The ZT2306/A has a built-in counter. When the total count of OCP fault reaches 16, the FET is turned off permanently, requiring a V<sub>ACIN</sub> POR again to restart.

#### **Battery Over-Voltage Protection**

The ZT2306/A monitors the VBAT pin voltage for battery over-voltage protection. The battery OVP threshold is internally set to 4.35V. When the VBAT pin voltage exceeds the battery OVP threshold for a blanking time of  $T_{B(BOVP)}$ , the internal power FET is turned off. When the VBAT voltage returns below the battery OVP threshold minus the hysteresis, the FET is turned on again. The ZT2306/A has a built-in counter. When the total count of battery OVP fault reaches 16, the FET is turned off permanently, requiring a V<sub>ACIN</sub> POR again to restart.

# **Over-Temperature Protection**

When the junction temperature exceeds 160°C, the internal thermal sense circuit turns off the power FET and allows the device to cool down. When the device's junction temperature cools by 40°C, the internal thermal sense circuit will enable the device, resulting in a pulsed output during continuous thermal protection. Thermal protection is designed to protect the IC in the event of over temperature conditions. For normal operation, the junction temperature cannot exceed  $T_J = +125$ °C.

## Internal P-MOSFET

The ZT2306/A integrates a P-channel MOSFET with the body diode reverse protection to replace the external P-MOSFET and Schottky diode for cell phone's PMIC. The body diode reverse protection prevents a reverse current flowing from the battery back to CHRIN pin. During power-on, when CHRIN voltage rises above the

VBAT voltage by more than 150mV, the body diode of the P-channel MOSFET is forward biased from OUT to CHRIN, and P-MOSFET is controlled by the external GATDRV voltage. When the CHRIN voltage drops below  $V_{BAT}$ +20mV, the body diode of the P-channel MOSFET is forward biased from CHRIN to OUT and P-channel MOSFET is turned off. When any of input OVP, OCP, battery OVP, is detected, the internal P-channel MOSFET is also turned off.

Figure 3: Battery OVP timing diagram.

# APPLICATION INFORMATION

## **R**<sub>BAT</sub> Selection

Connect the VBAT pin to the positive terminal of battery through a resistor  $R_{BAT}$  for battery OVP function. The  $R_{BAT}$  limits the current flowing from VBAT to battery in case of VBAT pin is shorted to ACIN pin under a failure mode. The recommended value of  $R_{BAT}$  is 200k $\Omega$ . In the worse case of an IC failure, the current flowing from the VBAT pin to the battery is:

$(30V - 3V) / 200k\Omega = 135\mu A$

Where the 30V is the maximum ACIN voltage and the 3V is the minimum battery voltage. The current is so small and can be absorbed by the charger system.

#### **Capacitor Selection**

The input capacitor is for decoupling and prevents the input voltage from overshooting to dangerous levels. In the AC adapter hot plug-in applications or load current step-down transient, the input voltage has a transient spike due to the parasitic inductance of the input cable. A 25V, X5R, dielectric ceramic capacitor with a value between  $1\mu$ F and  $4.7\mu$ F placed close to the ACIN pin is recommended.

The output capacitor of CHRIN is for CHRIN voltage decoupling. And also can be as the input capacitor of the charging circuit. At least, a  $1\mu$ F, 10V, X5R capacitor is recommended.

## Layout Consideration

In some failure modes, a high voltage may be applied to the device. Make sure the clearance constraint of the PCB layout must satisfy the design rule for high voltage. The exposed pad of the TDFN 2x2-8L performs the function of channeling heat away. It is recommended that connect the exposed pad to a large copper ground plane on the backside of the circuit board through several thermal vias to improve heat dissipation. The input and output capacitors should be placed close to the IC. The high current traces like input trace and output trace must be wide and short.

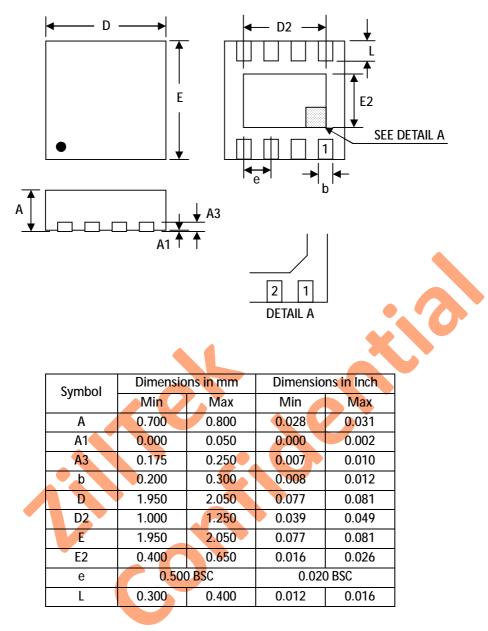

ZT2306/A

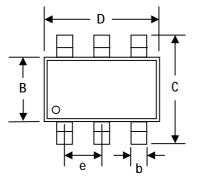

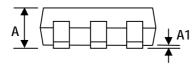

PACKAGE DIMENSION SOT23-6L

|  | Symbol | Dimensio | ns in mm | Dimensions in Inch |       |  |

|--|--------|----------|----------|--------------------|-------|--|

|  | Symbol | Min      | Max      | Min                | Max   |  |

|  | А      | 1.050    | 1.250    | 0.041              | 0.049 |  |

|  | A1     | 0.013    | 0.100    | 0.001              | 0.004 |  |

|  | В      | 1.525    | 1.675    | 0.060              | 0.066 |  |

|  | b      | 0.300    | 0.559    | 0.012              | 0.022 |  |

|  | С      | 2.700    | 2.900    | 0.106              | 0.114 |  |

|  | D      | 2.900    | 2.975    | 0.114              | 0.117 |  |

|  | е      | 0.950    | ) BSC    | 0.037 BSC          |       |  |

|  | Н      | 0.250    | ) BSC    | 0.010 BSC          |       |  |

|  | L      | 0.300    | 0.600    | 0.012              | 0.024 |  |

|  |        |          |          |                    |       |  |

ZT2306/A