# SMBus-Controlled Level 2 Multi-Chemistry Battery Charger With Input

# **Current Detect Comparator and Charge Enable Pin**

Check for Samples :bq24747

#### **FEATURES**

www.ti.com

- NMOS-NMOS Synchronous Buck Converter with 300 kHz Frequency and >95% Efficiency

- 30-ns Minimum Driver Dead-time and 99.5%

Maximum Effective Duty Cycle

- High-Accuracy Voltage and Current Regulation

- ±0.5% Charge Voltage Accuracy

- ±3% Charge Current Accuracy

- ±3% Adapter Current Accuracy

- ±2% Input Current Sense Amp Accuracy

- Integration

- Input Current Comparator, With Adjustable Threshold and Hysteresis

- Internal Soft-Start

- Safety

- Input Overvoltage Protection (OVP)

- Dynamic Power Management (DPM)

- Up to 19.2 V Battery Voltage

- 7 V–24 V AC/DC-Adapter Operating Range

- Simplified SMBus Control Interface

- Charge Voltage DAC (1.024 V-19.2 V)

- Charge Current DAC (128 mA–8.064 A)

- Adapter Current Limit DPM DAC (256 mA-11.008 A)

- Status and Monitoring Outputs

- AC/DC Adapter Present with Adjustable Voltage Threshold

- Input Current Comparator, With Adjustable Threshold and Hysteresis

- Current Sense Amplifier for Current Drawn From Input Source

- Charge Any Battery Chemistry: Li+, NiCd, NiMH, Lead Acid, etc.

- Charge Enable Pin

- < 10-µBattery Current with Adapter Removed

- < 1 mA Input DCIN Current with Adapter Present and Charge Disabled

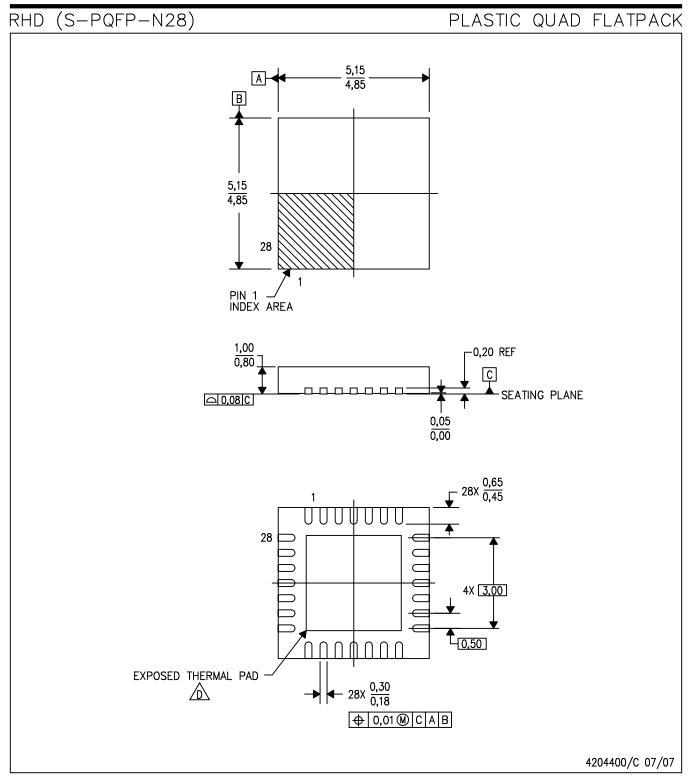

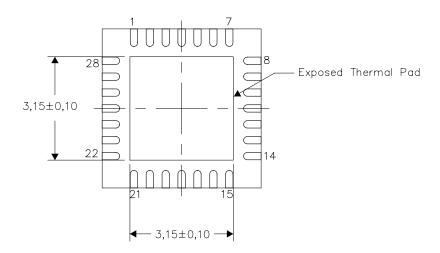

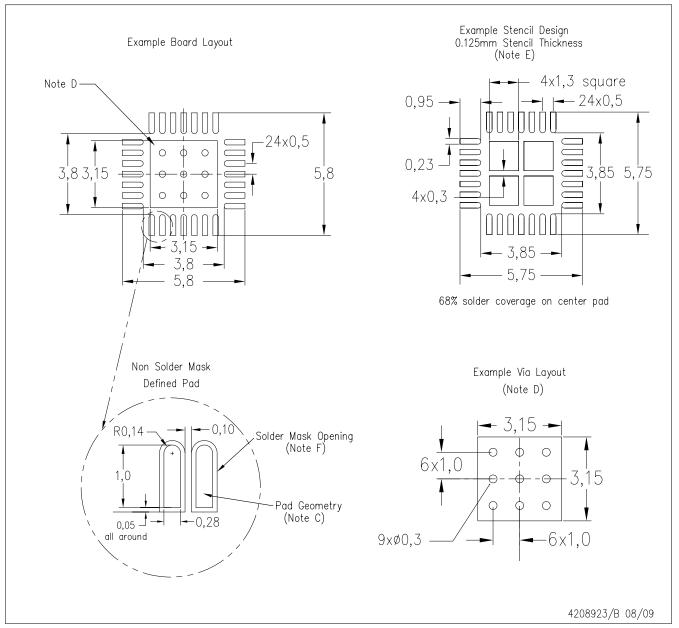

- 28-pin, 5x5-mm<sup>2</sup> QFN Package

#### **APPLICATIONS**

- Notebook and Ultra-Mobile Computers

- Portable Data-Capture Terminals

- Portable Printers

- Medical Diagnostics Equipment

- Battery Bay Chargers

- Battery Back-up Systems

#### DESCRIPTION

The bq24747 is a high-efficiency, synchronous battery charger with an integrated input-current comparator, offering low component count for space-constrained, multi-chemistry battery-charging applications. The input-current, charge-current, and charge-voltage DACs allow very high regulation accuracies that can be easily programmed by the system power-management microcontroller using the SMBus interface. The bq24747 charges two, three, or four series Li+ cells, and is available in a 28-pin, 5x5 mm² QFN package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **DESCRIPTION (CONTINUED)**

The bq24747 features Dynamic Power Management (DPM) and input power limiting. These features reduce battery-charge current when the input power limit is reached to avoid overloading the AC adaptor when supplying the load and the battery charger simultaneously. A highly accurate current-sense amplifier enables precise measurement of input current from the AC adapter, allowing monitoring the overall system power. If the adapter current is above the programmed low-power threshold, a signal is sent to host so that the system optimizes its performance to the power available from the adapter. An integrated comparator monitors the input current through the current-sense amplifier, and indicates when the input current exceeds a programmable threshold limit

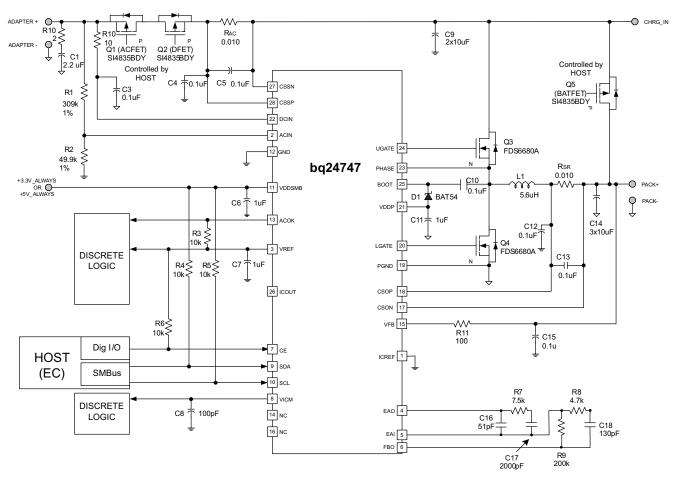

#### TYPICAL APPLICATIONS

$V_{IN} = 20 \text{ V}, V_{BAT} = 4\text{-cell Li-lon}, I_{CHARGE} = 4.5 \text{ A}$

Pull-up rail could be either VREF or other system rail.

Figure 1. Typical System Schematic: Using External Input Current Comparator (discrete logic) Instead of Internal Comparator

Submit Documentation Feedback

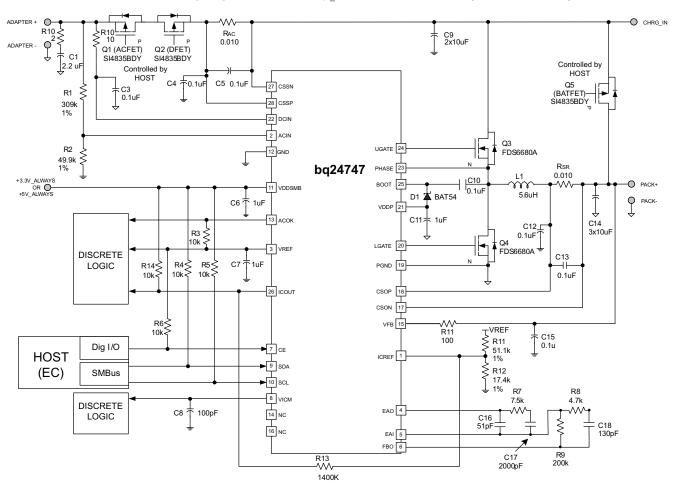

$V_{IN}$  = 20 V,  $V_{BAT}$  = 4-cell Li-Ion,  $I_{CHARGE}$  = 4.5 A,  $VICM_{er\_limit}$  = 6 A, for ICOUT Input Current comparator.

Pull-up rail could be either VREF or other system rail.

Figure 2. Typical System Schematic, Using Internal Input Current Comparator

#### ORDERING INFORMATION(1)

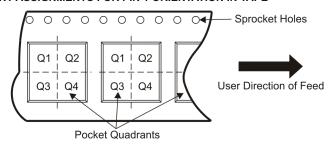

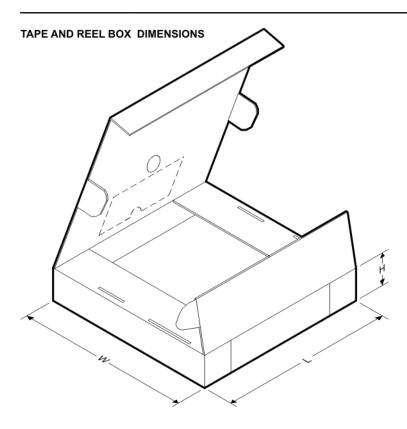

| PART NUMBER | PACKAGE                          | ORDERING NUMBER (Tape and Reel) | QUANTITY |

|-------------|----------------------------------|---------------------------------|----------|

| ba24747     | 28-PIN 5 x 5 mm <sup>2</sup> QFN | bq24747RHDR                     | 3000     |

| bq24747     | 28-FIN 5 X 5 IIIIII QFN          | bq24747RHDT                     | 250      |

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

#### PACKAGE THERMAL DATA

Copyright © 2009, Texas Instruments Incorporated

| PACKAGE                  | $\theta_{JA}$ | T <sub>A</sub> = 70°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C |  |  |

|--------------------------|---------------|---------------------------------------|------------------------------------------------|--|--|

| QFN – RHD <sup>(1)</sup> | 39°C/W        | 2.36 W                                | 0.028 W/°C                                     |  |  |

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

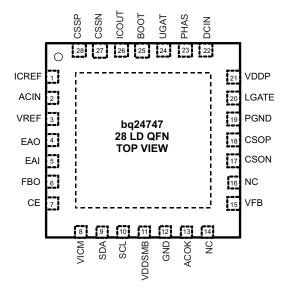

#### Table 1. TERMINAL FUNCTIONS - 28-PIN QFN

| TEI | RMINAL | FUNCTION                                                                                                                                                                                                                                                                                                                                                                              |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. |        |                                                                                                                                                                                                                                                                                                                                                                                       |

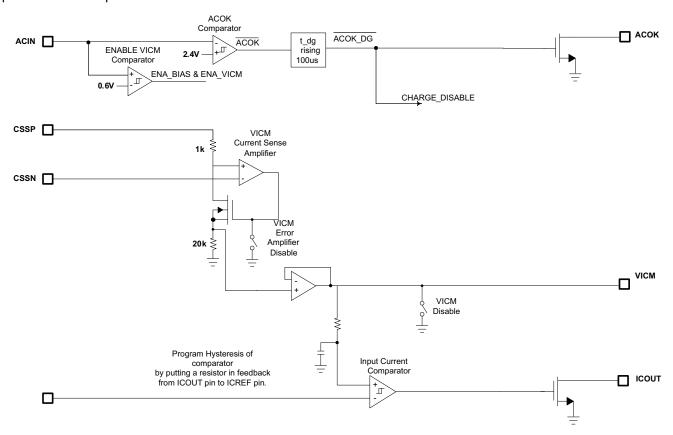

| 1   | ICREF  | Input current comparator voltage reference input. Connect a resistor-divider from VREF to ICREF, and GND to program the reference for the ICOUT comparator. The ICREF pin voltage is compared to the VICM pin voltage and the logic output is given on the ICOUT open-drain pin. Connecting a positive feedback resistor from the ICREF pin to the ICOUT pin programs the hysteresis. |

| 2   | ACIN   | Adapter detected voltage set input. Program the adapter detect threshold by connecting a resistor divider from adapter input to ACIN pin to GND pin. Adapter voltage is detected if ACIN pin voltage is greater than 2.4 V. VICM current sense amplifier, ICOUT comparator, ICREF input, and ACOK output are active when ACIN pin voltage is greater than 0.6 V.                      |

| 3   | VREF   | 3.3 V regulated voltage output. Place a 1 µF ceramic capacitor from VREF to GND pin close to the IC. This voltage could be used for ratio metric programming of voltage and current regulation and for programming the ICREF threshold.                                                                                                                                               |

| 4   | EAO    | Error Amplifier Output for compensation. Connect the feedback-compensation components from EAO to EAI. Typically, a capacitor in parallel with a series resistor and capacitor. This node is internally compared to the PWM saw-tooth oscillator signal.                                                                                                                              |

| 5   | EAI    | Error Amplifier Input for compensation. Connect the feedback compensation components from EAI to EAO. Connect the input compensation from FBO to EAI.                                                                                                                                                                                                                                 |

| 6   | FBO    | Feedback Output for compensation. Connect the input compensation from FBO to EAI. Typically, a resistor in parallel with a series resistor and capacitor.                                                                                                                                                                                                                             |

| 7   | CE     | Charge enable active-high logic input. HI enables charge. LO disables charge.                                                                                                                                                                                                                                                                                                         |

| 8   | VICM   | Adapter current sense amplifier output. VICM voltage is 20 times the differential voltage across CSSP-CSSN. Place a 100pF (max) or less ceramic decoupling capacitor from VICM to GND.                                                                                                                                                                                                |

| 9   | SDA    | SMBus Data input. Connect to SMBus data line from the host controller. A 10-k $\Omega$ pull-up resistor to the host controller power rail is needed.                                                                                                                                                                                                                                  |

| 10  | SCL    | SMBus Clock input. Connect to SMBus clock line from the host controller. A 10-k $\Omega$ pull-up resistor to the host controller power rail is needed.                                                                                                                                                                                                                                |

| 11  | VDDSMB | Input voltage for SMBus logic. Connect a 3.3 V always supply rail, or 5 V always rail to VDDSMB pin. Connect a 0.1µF ceramic capacitor from VDDSMB to GND for decoupling.                                                                                                                                                                                                             |

| 12  | GND    | Analog Ground. On PCB layout, connect to the analog ground plane, and only connect to PGND through the power-pad underneath the IC.                                                                                                                                                                                                                                                   |

| 13  | ACOK   | Valid adapter active-high detect logic open-drain output. Pulled HI when Input voltage is above ACIN programmed threshold. Connect a $10$ -k $\Omega$ pull-up resistor from ACOK pin to pull-up supply rail.                                                                                                                                                                          |

| 14  | NC     | No Connect. Pin floating internally.                                                                                                                                                                                                                                                                                                                                                  |

| 15  | VFB    | Battery-voltage remote sense. Directly connect a Kelvin sense trace from the battery-pack positive terminal to the VFB pin to accurately sense the battery pack voltage. Place a 0.1-µF capacitor from VFB to GND close to the IC to filter high-frequency noise.                                                                                                                     |

| 16  | NC     | No Connect. Pin floating internally.                                                                                                                                                                                                                                                                                                                                                  |

| 17  | CSON   | Charge-current sense resistor, negative input. An optional 0.1-µF ceramic capacitor is placed from CSON pin to GND for common-mode filtering. An optional 0.1-µF ceramic capacitor is placed from CSON to CSOP to provide differential-mode filtering.                                                                                                                                |

| 18  | CSOP   | Charge-current sense resistor, positive input. An optional 0.1-µF ceramic capacitor is placed from CSOP pin to GND for common mode filtering. An optional 0.1-µF ceramic capacitor is placed from CSON to CSOP to provide differential-mode filtering.                                                                                                                                |

| 19  | PGND   | Power ground. On PCB layout, connect directly to source of low-side power MOSFET, to ground connection of input and output capacitors of the charger. Only connect to GND through the power-pad underneath the IC.                                                                                                                                                                    |

| 20  | LGATE  | PWM low-side driver output. Connect to the gate of the low-side power MOSFET with a short trace.                                                                                                                                                                                                                                                                                      |

| 21  | VDDP   | PWM low-side driver positive 6-V supply output. Connect a 1-µF ceramic capacitor from VDDP to PGND pin, close to the IC. Use for high-side driver bootstrap voltage by connecting a small signal Schottky diode from VDDP to BOOT.                                                                                                                                                    |

| 22  | DCIN   | IC-power positive supply. Connect to the common-source (diode-OR) point: source of high-side P-channel MOSFET and source of reverse blocking power P-channel MOSFET. Place a 1μF ceramic capacitor from DCIN to PGND pin close to the IC.                                                                                                                                             |

| 23  | PHASE  | PWM high-side driver negative supply. Connect to the phase switching node (junction of the low-side power MOSFET drain, high-side power MOSFET source, and output inductor). Connect the 0.1µF bootstrap capacitor from PHASE to BOOT.                                                                                                                                                |

| 24  | UGATE  | PWM high-side driver output. Connect to the gate of the high-side power MOSFET with a short trace.                                                                                                                                                                                                                                                                                    |

| 25  | BOOT   | PWM high-side driver positive supply. Connect a 0.1µF bootstrap ceramic capacitor from BOOT to PHASE. Connect a small bootstrap Schottky diode from VDDP to BOOT.                                                                                                                                                                                                                     |

www.ti.com SLUS988 - OCTOBER 2009

#### Table 1. TERMINAL FUNCTIONS – 28-PIN QFN (continued)

| TE  | RMINAL | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. |        |                                                                                                                                                                                                                                                                                                                                                                                              |

| 26  | ICOUT  | Input current comparator active-high open-drain logic output. Place a 10 k $\Omega$ pull-up resistor from ICOUT pin to the pull-up voltage rail. Place a positive feedback resistor from ICOUT pin to ICREF pin for programming hysteresis. The output is HI when VICM pin voltage is lower than ICREF pin voltage. The output is LO when VICM pin voltage is higher than ICREF pin voltage. |

| 27  | CSSN   | Adapter current-sense resistor, negative input. An optional 0.1-µF ceramic capacitor is placed from CSSN pin to GND for common-mode filtering. An optional 0.1-µF ceramic capacitor is placed from CSSN to CSSP to provide differential-mode filtering.                                                                                                                                      |

| 28  | CSSP   | Adapter current-sense resistor, positive input. An optional 0.1-µF ceramic capacitor is placed from CSSP pin to GND for common-mode filtering. An optional 0.1-µF ceramic capacitor is placed from CSSN to CSSP to provide differential-mode filtering.                                                                                                                                      |

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1) (2)

|                |                                                                    | VALUE       | UNIT |

|----------------|--------------------------------------------------------------------|-------------|------|

|                | DCIN, CSOP, CSON, CSSP, CSSN, VFB, ACOK                            | -0.3 to 30  |      |

|                | PHASE                                                              | -1 to 30    |      |

|                | EAI, EAO, FBO, VDDP, LGATE, ACIN, VICM, ICOUT, ICREF, CE, SDA, SCL | -0.3 to 7   |      |

| Voltage range  | VDDSMB                                                             | -0.3 to 5.5 | V    |

|                | VREF                                                               | -0.3 to 3.6 | V    |

|                | BOOT, UGATE with respect to GND and PGND                           | -0.3 to 36  |      |

|                | GND, PGND                                                          | -1 to 1     |      |

| Maximum differ | ence voltage: CSOP-CSON, CSSP-CSSN                                 | -0.5 to 0.5 |      |

| Junction tempe | inction temperature range                                          |             | 00   |

| Storage temper | rage temperature range                                             |             | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                  |                                                               | MIN  | NOM MAX | UNIT |

|------------------|---------------------------------------------------------------|------|---------|------|

|                  | PHASE                                                         | -0.7 | 24      |      |

|                  | DCIN, CSOP, CSON, CSSP, CSSN, VFB, ACOK                       | 0    | 24      |      |

|                  | VDDP, LGATE                                                   | 0    | 6.5     |      |

| Voltage range    | VREF                                                          |      | 3.3     | V    |

|                  | EAI, EAO, FBO, ACIN, VICM, ICOUT, ICREF, CE, VDDSMB, SDA, SCL | 0    | 5.5     |      |

|                  | BOOT, UGATE with respect to GND and PGND                      | 0    | 30      |      |

|                  | GND, PGND                                                     | -0.3 | 0.3     |      |

| Maximum differe  | ence voltage: CSOP-CSON, CSSP-CSSN                            | -0.3 | 0.3     |      |

| Junction tempera | ature range                                                   | -40  | 125     | °C   |

| Storage tempera  | ature range                                                   | -55  | 150     | C    |

<sup>(2)</sup> All voltages are with respect to GND if not specified. Currents are positive into, and negative out of the specified terminal. Consult Packaging Section of the data book for thermal limitations and considerations of packages.

#### **ELECTRICAL CHARACTERISTICS**

$7.0 \text{ V} \leq \text{V(DCIN)} \leq 24 \text{ V}, \ 0^{\circ}\text{C} < \text{T}_{\text{J}} < +125^{\circ}\text{C}, \ \text{typical values are at T}_{\text{A}} = 25^{\circ}\text{C}, \ \text{with respect to AGND (unless otherwise noted)}$

|                           | PARAMETER                                             | TEST CONDITIONS                                                                             | MIN    | TYP    | MAX    | UNIT |

|---------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------|--------|--------|--------|------|

| OPERATING C               | ONDITIONS                                             | <u>'</u>                                                                                    |        |        |        |      |

| V <sub>DCIN_OP</sub>      | DCIN input voltage operating range                    |                                                                                             | 7      |        | 24     | V    |

|                           | AGE REGULATION                                        |                                                                                             |        |        |        |      |

| V <sub>VFB OP</sub>       | VFB input voltage range                               |                                                                                             | 0      |        | DCIN   | V    |

|                           |                                                       |                                                                                             | 16.716 | 16.8   | 16.884 | ٧    |

|                           |                                                       | ChargeVoltage() = 0x41A0                                                                    | -0.5%  |        | 0.5%   |      |

|                           |                                                       |                                                                                             | 12.529 | 12.592 | 12.655 | V    |

| / <sub>VFB_REG _ACC</sub> |                                                       | ChargeVoltage() = 0x3130                                                                    | -0.5%  |        | 0.5%   |      |

| V <sub>VFB_REG</sub> _ACC | VFB charge voltage regulation accuracy                |                                                                                             | 8.350  | 8.4    | 8.450  | V    |

|                           |                                                       | ChargeVoltage() = 0x20D0                                                                    | -0.6%  |        | 0.6%   |      |

|                           |                                                       |                                                                                             | 4.154  | 4.192  | 4.230  | V    |

|                           |                                                       | ChargeVoltage() = 0x1060                                                                    | -0.9%  |        | 0.9%   |      |

| V <sub>VFB_REG_</sub> RNG | Charge voltage regulation range                       | T <sub>J</sub> = 0 to 125°C, 1.024 V–19.2 V, Max DAC value is 19.2 V                        | 1.024  |        | 19.2   | ٧    |

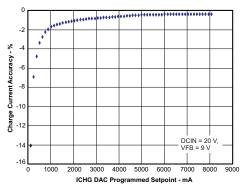

| CHARGE CURF               | RENT REGULATION                                       |                                                                                             |        |        | l      |      |

| V <sub>IREG_CHG_RNG</sub> | Charge current regulation differential voltage range  | $V_{IREG\_CHG} = V_{CSOP} - V_{CSON}$ , Max DAC value is 80.64 mV                           | 0      |        | 80.64  | mV   |

|                           |                                                       | 0 0 0 0                                                                                     |        | 3968   |        | mA   |

|                           |                                                       | ChargeCurrent() = 0x0F80                                                                    | -3%    |        | 3%     |      |

|                           |                                                       |                                                                                             |        | 2048   |        | mA   |

| CHRG_REG_ACC              |                                                       | ChargeCurrent() = 0x0800                                                                    | -5%    |        | 5%     |      |

|                           | Charge current regulation accuracy                    |                                                                                             |        | 512    |        | mA   |

|                           |                                                       | ChargeCurrent() = 0x0200                                                                    | -25%   |        | 25%    |      |

|                           |                                                       | 01 0 10 0 0000                                                                              |        | 128    |        | mA   |

|                           |                                                       | ChargeCurrent() = 0x0080                                                                    | -33%   |        | 33%    |      |

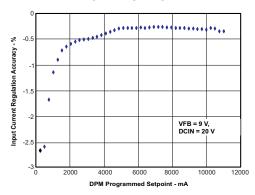

| INPUT CURREI              | NT REGULATION                                         |                                                                                             |        |        | l      |      |

| V <sub>IREG_DPM_RNG</sub> | Adapter current regulation differential voltage range | V <sub>IREG_DPM</sub> = V <sub>CSSP</sub> - V <sub>CSSN</sub> , Max DAC value is 110.084 mV | 0      |        | 110.1  | mV   |

|                           |                                                       | 1 10 10 10 10 10 10 10 10 10 10 10 10 10                                                    |        | 4096   |        | mA   |

| NPUT CURRE                |                                                       | InputCurrent() ≥ 0x0800                                                                     | -3%    |        | 3%     |      |

|                           |                                                       |                                                                                             |        | 2048   |        | mA   |

|                           |                                                       | InputCurrent() = 0x0400                                                                     | -5%    |        | 5%     |      |

| INPUT_REG_ACC             | Input current regulation accuracy                     |                                                                                             |        | 512    |        | mA   |

|                           |                                                       | InputCurrent() = 0x0100                                                                     | -25%   |        | 25%    |      |

|                           |                                                       |                                                                                             |        | 256    |        | mA   |

|                           |                                                       | InputCurrent() = 0x0080                                                                     | -33%   |        | 33%    |      |

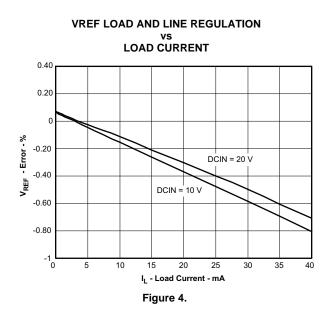

| VREF REGULA               | TOR                                                   |                                                                                             |        |        | -      |      |

| $V_{VREF\_REG}$           | VREF regulator voltage                                | V <sub>ACIN</sub> > 0.6 V, 0 - 30 mA                                                        | 3.267  | 3.3    | 3.333  | V    |

| VREF_LIM                  | VREF current limit                                    | V <sub>VREF</sub> = 0 V, V <sub>ACIN</sub> > 0.6 V                                          | 35     |        | 80     | mA   |

| VDDP REGULA               |                                                       | THE PROPERTY OF                                                                             |        |        |        |      |

| $V_{VDDP\_REG}$           | VDDP regulator voltage                                | V <sub>ACIN</sub> > 0.6 V, 0 - 50 mA                                                        | 5.7    | 6.0    | 6.3    | V    |

| VDDF_INEG                 |                                                       | V <sub>VDDP</sub> = 0 V, V <sub>ACIN</sub> > 0.6 V                                          | 90     |        | 135    |      |

| I <sub>VDDP_LIM</sub>     | VDDP current limit                                    | ADDI - / VOIM                                                                               |        |        |        | mA   |

Submit Documentation Feedback

#### **ELECTRICAL CHARACTERISTICS (continued)**

$7.0 \text{ V} \leq \text{V(DCIN)} \leq 24 \text{ V}, \ 0^{\circ}\text{C} < \text{T}_{J} < +125^{\circ}\text{C}, \ \text{typical values are at T}_{A} = 25^{\circ}\text{C}, \ \text{with respect to AGND (unless otherwise noted)}$

|                                                  | PARAMETER                                                    | TEST CONDITIONS                                                                       | MIN   | TYP      | MAX      | UNIT    |

|--------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------|-------|----------|----------|---------|

| ADAPTER CUR                                      | RENT SENSE AMPLIFIER                                         |                                                                                       |       |          |          |         |

| V <sub>CSSP/N_OP</sub>                           | Input common mode range                                      | Voltage on CSSP/CSSN                                                                  | 0     |          | 24       | V       |

| V <sub>VICM</sub>                                | VICM output voltage range                                    |                                                                                       | 0     |          | 2.25     | V       |

| A <sub>VICM</sub>                                | Current sense amplifier voltage gain                         | A <sub>VICM</sub> = V <sub>VICM</sub> / V <sub>IREG_DPM</sub>                         |       | 20       |          | V/V     |

| -                                                |                                                              | V <sub>IREG DPM</sub> = V(CSSP-CSSN) ≥ 40 mV                                          | -2%   |          | 2%       |         |

|                                                  |                                                              | V <sub>IREG DPM</sub> = V(CSSP-CSSN) =20 mV                                           | -3%   |          | 3%       |         |

|                                                  | Adapter current sense accuracy                               | V <sub>IREG_DPM</sub> = V(CSSP-CSSN) =5 mV                                            | -25%  |          | 25%      |         |

|                                                  |                                                              | V <sub>IREG_DPM</sub> = V(CSSP-CSSN) =1.5 mV                                          | -33%  |          | 33%      |         |

| I <sub>VICM_LIM</sub>                            | Output current limit                                         | V <sub>VICM</sub> = 0 V                                                               | 1     |          |          | mA      |

| C <sub>VICM MAX</sub>                            | Maximum output load capacitance                              | For stability with 0 mA to 1 mA load                                                  |       |          | 100      | pF      |

|                                                  | ATOR INPUT UNDERVOLTAGE)                                     | . c. stability illim c martie i martied                                               |       |          | .00      | ۲۰.     |

| V <sub>DCIN VFB OP</sub>                         | Differential voltage from DCIN to VFB                        |                                                                                       | -20   |          | 24       | V       |

| V <sub>ACIN_CHG</sub>                            | ACIN rising threshold                                        | Min voltage to enable charging, V <sub>ACIN</sub> rising                              | 2.376 | 2.40     | 2.424    | V       |

| Vacin_chg<br>Vacin_chg_hys                       | ACIN falling hysteresis                                      | V <sub>ACIN</sub> falling                                                             |       | 40       |          | mV      |

| - ACIN_CHG_HYS                                   | ACIN rising dealitch <sup>(1)</sup>                          | V <sub>ACIN</sub> rising                                                              | 50    | 100      | 150      | μs      |

|                                                  | ACIN falling deglitch                                        | V <sub>ACIN</sub> falling                                                             |       | 1        | 100      | μs      |

| V. a.v. a.v                                      | Adapter present rising threshold                             | Min voltage to enable all bias, V <sub>ACIN</sub> rising                              | 0.56  | 0.62     | 0.68     | μs<br>V |

| V <sub>ACIN_BIAS</sub>                           |                                                              |                                                                                       | 0.50  | 20       | 0.00     | mV      |

| V <sub>ACIN_BIAS_HYS</sub>                       | Adapter present falling hysteresis  ACIN rising deglitch (1) | V <sub>ACIN</sub> falling V <sub>ACIN</sub> rising                                    |       | 200      |          | IIIV    |

|                                                  | ACIN fishing deglitch  ACIN falling deglitch                 |                                                                                       |       | 1        |          | μs      |

| DOIN / VED COI                                   | <u> </u>                                                     | V <sub>ACIN</sub> falling                                                             |       | <u>'</u> |          |         |

|                                                  | MPARATOR (REVERSE DISCHARGING PROT                           | · · · · · · · · · · · · · · · · · · ·                                                 | 4.40  | 405      | 040      | \       |

| V <sub>DCIN-VFB_FALL</sub>                       | DCIN to VFB falling threshold                                | V <sub>DCIN</sub> – V <sub>VFB</sub> to turn off ACFET                                | 140   | 185      | 240      | mV      |

| VDCIN-VFB_HYS                                    | DCIN to VFB hysteresis                                       | V V                                                                                   |       | 50       |          | mV      |

|                                                  | DCIN to VFB rising deglitch                                  | V <sub>DCIN</sub> - V <sub>VFB</sub> > V <sub>DCIN-VFB_RISE</sub>                     |       | 1        |          | ms      |

|                                                  | DCIN to VFB falling deglitch                                 | V <sub>DCIN</sub> - V <sub>VFB</sub> < V <sub>DCIN-VFB_FALL</sub>                     |       | 3.3      |          | μs      |

|                                                  | TAGE COMPARATOR                                              |                                                                                       |       |          |          |         |

| V <sub>OV_RISE</sub>                             | Over-voltage rising threshold                                | As percentage of V <sub>VFB_REG</sub>                                                 |       | 104      |          | %       |

| V <sub>OV_FALL</sub>                             | Over-voltage falling threshold                               | As percentage of V <sub>VFB_REG</sub>                                                 |       | 102      |          |         |

| VFB SHORT (UI                                    | NDERVOLTAGE and TRICKLE CHARGE) COM                          | IPARATOR                                                                              |       |          |          |         |

| V <sub>VFB_SHORT_RISE</sub>                      |                                                              |                                                                                       | 2.4   | 2.7      | 2.9      | V       |

| V <sub>VFB_SHORT_HYS</sub>                       | VFB short rising hysteresis                                  |                                                                                       |       | 215      |          | mV      |

| OV_RISE OV_FALL OV_FB SHORT (UN OV_FB_SHORT_RISE | VFB short rising deglitch                                    | V <sub>VFB</sub> > V <sub>VFB_SHORT</sub> +V <sub>VFB_SHORT_HYS</sub> Detection delay |       | 1.5      |          | μs      |

|                                                  | VFB short falling deglitch                                   | V <sub>VFB</sub> < V <sub>VFB_SHORT</sub>                                             |       | 3.3      |          | μs      |

| I <sub>TRKL_REG_ACC</sub>                        | Trickle Charge current regulation accuracy in BATSHORT       | V <sub>VFB</sub> < V <sub>VFB_SHORT</sub>                                             | 60    | 220      | 300      | mA      |

| I <sub>LOW_MAX_REG</sub>                         | Maximum Charge current regulation at Low Voltage (<4V)       | V <sub>VFB_SHORT</sub> < V <sub>VFB</sub> < 4                                         |       | 3        |          | Α       |

| CHARGE OVER                                      | CURRENT COMPARATOR                                           |                                                                                       |       |          |          |         |

| V <sub>oc</sub>                                  | Charge overcurrent falling threshold                         | As percentage of I <sub>REG_CHG</sub>                                                 |       | 145%     |          |         |

|                                                  | Minimum Current Limit (CSOP-CSON)                            |                                                                                       |       | 50       |          | mV      |

|                                                  | Internal Filter Pole Frequency                               |                                                                                       |       | 160      |          | kHz     |

| INPUT UNDERV                                     | OLTAGE LOCK-OUT COMPARATOR (UVLO)                            |                                                                                       |       |          |          |         |

| UVLO                                             | AC undervoltage rising threshold                             | Measure on DCIN pin                                                                   | 3.5   | 4        | 4.5      | V       |

| V <sub>UVLO_HYS</sub>                            | AC undervoltage hysteresis, falling                          |                                                                                       |       | 260      |          | mV      |

| INPUT CURREN                                     | IT COMPARATOR                                                |                                                                                       |       |          | <u> </u> |         |

| 0. 00                                            |                                                              |                                                                                       |       |          |          |         |

<sup>(1)</sup> Verified by design.

#### **ELECTRICAL CHARACTERISTICS (continued)**

$7.0 \text{ V} \leq \text{V(DCIN)} \leq 24 \text{ V}, \ 0^{\circ}\text{C} < \text{T}_{\text{J}} < +125^{\circ}\text{C}, \ \text{typical values are at T}_{\text{A}} = 25^{\circ}\text{C}, \ \text{with respect to AGND (unless otherwise noted)}$

|                           | PARAMETER                                                                    | TEST CONDITIONS                                                                                                                  | MIN | TYP  | MAX | UNIT  |

|---------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| THERMAL SHU               | TDOWN COMPARATOR                                                             |                                                                                                                                  |     |      |     |       |

|                           | VLOWV_VFB comparator                                                         |                                                                                                                                  |     | 4    |     | V     |

|                           | Reset time CE after falling-edge on-shot                                     |                                                                                                                                  |     | 2    |     | ms    |

| T <sub>SHUT</sub>         | Thermal shutdown rising temperature                                          | Temperature Increasing                                                                                                           |     | 155  |     | °C    |

| T <sub>SHUT_HYS</sub>     | Thermal shutdown hysteresis, falling                                         |                                                                                                                                  |     | 20   |     | C     |

| PWM HIGH SID              | E DRIVER (UGATE)                                                             |                                                                                                                                  |     |      |     |       |

| R <sub>DS_HI_ON</sub>     | High side driver (HSD) turn-on resistance                                    | V <sub>BOOT</sub> - V <sub>PHASE</sub> = 5.5 V                                                                                   |     |      | 6   | Ω     |

| R <sub>DS_HI_OFF</sub>    | High side driver turn-off resistance                                         | V <sub>BOOT</sub> - V <sub>PHASE</sub> = 5.5 V                                                                                   |     |      | 1   | Ω     |

| V <sub>BOOT_REFRESH</sub> | Bootstrap refresh comparator threshold voltage                               | V <sub>BOOT</sub> – V <sub>PHASE</sub> when low side refresh pulse is requested                                                  | 4   |      |     | V     |

| I <sub>BOOT_LEAK</sub>    | BOOT leakage current when charge enabled                                     | High Side is on; Charge enabled                                                                                                  |     |      | 200 | μA    |

| PWM LOW SID               | E DRIVER (LGATE)                                                             |                                                                                                                                  |     |      |     |       |

| R <sub>DS_LO_ON</sub>     | Low side driver (LSD) turn-on resistance                                     |                                                                                                                                  |     |      | 6   | Ω     |

| R <sub>DS LO OFF</sub>    | Low side driver turn-off resistance                                          |                                                                                                                                  |     |      | 1   | Ω     |

| PWM DRIVERS               | TIMING                                                                       |                                                                                                                                  |     |      |     |       |

|                           | Driver Dead Time                                                             | Dead time when switching between LGATE and UGATE , no load at LGATE and UGATE                                                    | 30  |      |     | ns    |

| PWM OSCILLA               | TOR                                                                          |                                                                                                                                  |     |      |     |       |

| F <sub>SW</sub>           | PWM switching frequency                                                      |                                                                                                                                  | 240 |      | 360 | kHz   |

| V <sub>RAMP_HEIGHT</sub>  | PWM ramp height                                                              | As percentage of DCIN                                                                                                            |     | 6.67 |     | %DCIN |

| QUIESCENT C               | JRRENT                                                                       |                                                                                                                                  |     |      |     |       |

| I <sub>OFF_STATE</sub>    | Total off-state battery current from CSOP, CSON, VFB, DCIN, BOOT, PHASE, etc | $V_{VFB} = 16.8 \text{ V}, V_{ACIN} < 0.6 \text{ V}, V_{DCIN} > 5 \text{ V}, 0^{\circ}\text{C} \le T_{J} \le 85^{\circ}\text{C}$ |     | 7    | 10  | μΑ    |

| I <sub>BAT_ON</sub>       | Battery on-state quiescent current                                           | $V_{VFB}$ = 16.8 V, 0.6V < $V_{ACIN}$ < 2.4 V, $V_{DCIN}$ > 5 V                                                                  |     | 0.7  | 1   | mA    |

| I <sub>BAT_LOAD_CD</sub>  | Internal battery load current, charge disabled                               | Charge is disabled: $V_{VFB}$ = 16.8 V, $V_{ACIN}$ > 2.4 V, $V_{DCIN}$ > 5 V                                                     |     | 0.7  | 1   | mA    |

| I <sub>BAT_LOAD_CE</sub>  | Internal battery load current, charge enabled                                | Charge is enabled: $V_{VFB}$ = 16.8 V, $V_{ACIN}$ > 2.4 V, $V_{DCIN}$ > 5 V                                                      | 6   | 10   | 12  | mA    |

| I <sub>AC</sub>           | Adapter quiescent current                                                    | Charge disabled, V <sub>DCIN</sub> = 20 V                                                                                        |     | 0.7  | 1   | mA    |

| I <sub>AC_SWITCH</sub>    | Adapter switching quiescent current                                          | Charge enabled, V <sub>DCIN</sub> = 20 V, converter running                                                                      |     | 25   |     | mA    |

| INTERNAL SOF              | T START (8 steps to regulation current ICHG)                                 |                                                                                                                                  |     |      |     |       |

|                           | Soft start steps                                                             |                                                                                                                                  |     | 8    |     | step  |

|                           | Soft start step time                                                         |                                                                                                                                  |     | 1.5  |     | ms    |

| CHARGER SEC               | CTION POWER-UP SEQUENCING                                                    |                                                                                                                                  |     |      |     |       |

|                           | Charge-Enable Delay after Power-up                                           | Delay from when adapter is detected to when the charger is allowed to turn on                                                    |     | 1.5  |     | ms    |

| CHARGE UND                | RCURRENT COMPARATOR (CYCLE-BY-CYC                                            | LE SYNCHRONOUS TO NON-SYNCHRONOUS)                                                                                               |     |      |     |       |

| V <sub>UCP</sub>          | Cycle-by-cycle Synchronous to Non-Synchronous Transition Threshold           | Cycle-by-cycle, (CSOP-CSON) voltage, falling, LGATE turns-off and latches off until next cycle                                   | 5   | 10   | 15  | mV    |

|                           | Blankout Time after LGATE turns-on                                           | Blankout comparator after LGATE turns-on                                                                                         |     | 100  |     | ns    |

| LOGIC INPUT F             | PIN CHARACTERISTICS (CE)(2) Pull-up CE with                                  | n ≥2.2 kΩ resistor or directly to VREF.                                                                                          |     |      |     |       |

| V <sub>IN_LO</sub>        | Input low threshold voltage                                                  |                                                                                                                                  |     |      | 0.8 | V     |

| V <sub>IN_HI</sub>        | Input high threshold voltage                                                 |                                                                                                                                  | 2.1 |      |     |       |

| V <sub>BIAS</sub>         | Input bias current                                                           | V = 0 TO V <sub>VDDP</sub>                                                                                                       |     |      | 1   | μA    |

|                           | OGIC OUTPUT PIN CHARACTERISTICS (ACOI                                        |                                                                                                                                  |     |      | "   |       |

|                           |                                                                              |                                                                                                                                  |     |      |     |       |

<sup>(2)</sup> Pull up CE with  $\geq$  2 k $\Omega$  resistor, or connect directly to VREF.

#### **ELECTRICAL CHARACTERISTICS (continued)**

$7.0 \text{ V} \le \text{V(DCIN)} \le 24 \text{ V}, 0^{\circ}\text{C} < \text{T}_{\text{J}} < +125^{\circ}\text{C}, \text{ typical values are at T}_{\text{A}} = 25^{\circ}\text{C}, \text{ with respect to AGND (unless otherwise noted)}$

|                                               | PARAMETER                                               | TEST CONDITIONS                                                                       | MIN | TYP | MAX  | UNIT |  |  |  |

|-----------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------|-----|-----|------|------|--|--|--|

| VDDSMB INPUT SUPPLY FOR SMBus                 |                                                         |                                                                                       |     |     |      |      |  |  |  |

| V <sub>VDDSMB_RANGE</sub>                     | VDDSMB input voltage range                              |                                                                                       | 2.7 |     | 5.5  | V    |  |  |  |

| V <sub>VDDSMB_UVLO_</sub><br>Threshold_Rising | VDDSMB undervoltage lockout threshold voltage, rising   | V <sub>VDDSMB</sub> Rising                                                            | 2.4 | 2.5 | 2.65 | V    |  |  |  |

| V <sub>VDDSMB_UVLO_</sub><br>Hyst_Rising      | VDDSMB undervoltage lockout hysteresis voltage, falling | V <sub>VDDSMB</sub> Falling                                                           | 100 | 150 | 200  | mV   |  |  |  |

| IVDDSMB_lq                                    | VDDSMB quiescent current                                | $V_{VDDSMB} = SCL = SDA = 5.5 \text{ V},$<br>$0^{\circ}C \leq T_{J} \leq 85^{\circ}C$ |     | 20  | 27   | μA   |  |  |  |

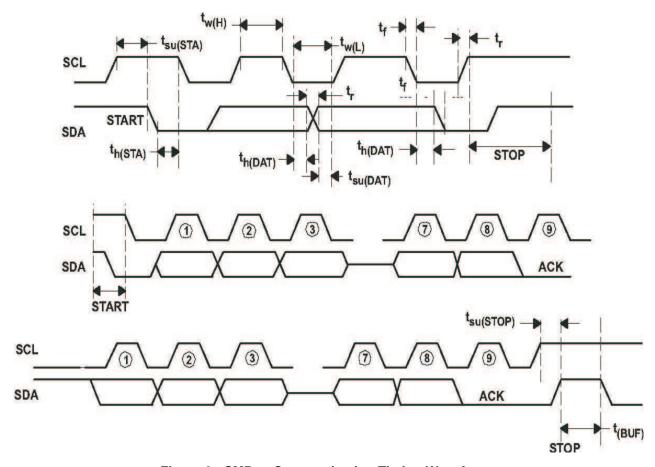

#### **ELECTRICAL CHARACTERISTICS**

7 Vdc  $\leq$  V<sub>(VCC)</sub>  $\leq$  24 Vdc,  $-20^{\circ}$ C<T<sub>J</sub> <125 $^{\circ}$ C, ref = AGND (unless otherwise noted)<sup>(1)</sup>

|                       | $V(C)$ $\leq$ 24 V(C), -20 C<1, <123 C, 1et = AGND (unless otherwise noted) |     |     |     |      |

|-----------------------|-----------------------------------------------------------------------------|-----|-----|-----|------|

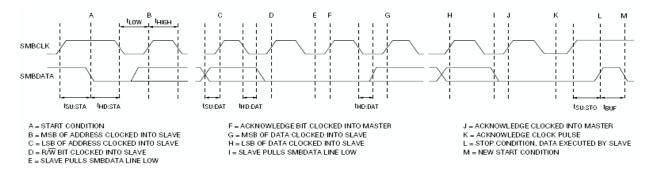

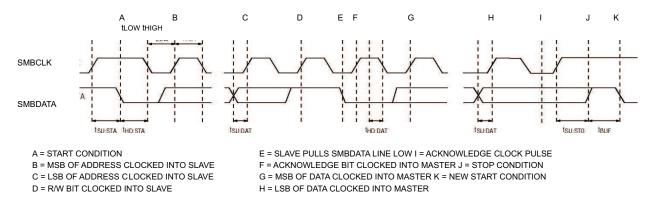

| PARAMET<br>[SMB TIMI  | NG SPECIFICATION (VDD = 2.7 V to 5.5 V) (see Figures 4 and 5)]              | MIN | TYP | MAX | UNIT |

| SMBus TII             | MING CHARACTERISTICS                                                        | "   |     |     |      |

| t <sub>R</sub>        | SCLK/SDATA rise time                                                        |     |     | 1   | μs   |

| t <sub>F</sub>        | SCLK/SDATA fall time                                                        |     |     | 300 | ns   |

| t <sub>W(H)</sub>     | SCLK pulse width high                                                       | 4   |     | 50  | μs   |

| $t_{W(L)}$            | SCLK Pulse Width Low                                                        | 4.7 |     |     | μs   |

| t <sub>SU(STA)</sub>  | Setup time for START condition                                              | 4.7 |     |     | μs   |

| t <sub>H(STA)</sub>   | START condition hold time after which first clock pulse is generated        | 4   |     |     | μs   |

| t <sub>SU(DAT)</sub>  | Data setup time                                                             | 250 |     |     | ns   |

| t <sub>H(DAT)</sub>   | Data hold time                                                              | 300 |     |     | ns   |

| t <sub>SU(STOP)</sub> | Setup time for STOP condition                                               | 4   |     |     | μs   |

| t <sub>(BUF)</sub>    | Bus free time between START and STOP condition                              | 4.7 |     |     | μs   |

| F <sub>S(CL)</sub>    | Clock Frequency                                                             | 10  |     | 100 | kHz  |

| HOST CO               | MMUNICATION FAILURE                                                         |     |     |     |      |

| t <sub>timeout</sub>  | SMBus bus release timeout                                                   | 22  | 25  | 35  | ms   |

| t <sub>WDI</sub>      | Watchdog timeout period                                                     | 140 | 170 | 210 | S    |

| OUTPUT E              | BUFFER CHARACTERISTICS                                                      |     |     |     |      |

| V <sub>(SDAL)</sub>   | Output LO voltage at SDA, I <sub>(SDA)</sub> = 3 mA                         |     |     | 0.4 | V    |

<sup>(1)</sup> Devices participating in a transfer will timeout when any clock low exceeds the 25 ms minimum timeout period. Devices that have detected a timeout condition must reset the communication no later than the 35 ms maximum timeout period. Both a master and a slave must adhere to the maximum value specified as it incorporates the cumulative stretch limit for both a master (10 ms) and a slave (25 ms).

Product Folder Link(s): bq24747

Figure 3. SMBus Communication Timing Waveforms

#### TYPICAL CHARACTERISTICS

VDDP LOAD AND LINE REGULATION

VS

LOAD CURRENT

DCIN = 10 V

DCIN = 20 V

JL - Load Current - mA

Figure 5.

Submit Documentation Feedback

#### **TYPICAL CHARACTERISTICS (continued)**

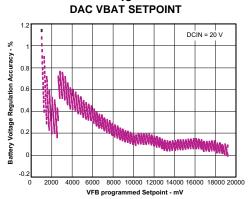

#### VFB (BATTERY) VOLTAGE REGULATION ACCURACY

#

Figure 6.

# CHARGE CURRENT REGULATION ACCURACY vs DAC ICHRG SETPOINT

Figure 8.

# INPUT CURRENT REGULATION (DPM) ACCURACY vs DAC IDPM SETPOINT

Figure 10.

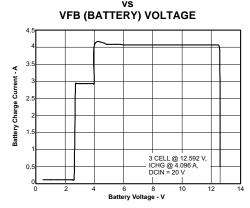

### VFB (BATTERY) VOLTAGE REGULATION ACCURACY vs

Figure 7.

#### CHARGE CURRENT REGULATION ACCURACY

Figure 9.

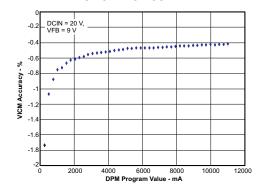

# VICM INPUT CURRENT SENSE AMPLIFIER ACCURACY INPUT CHARGE CURRENT

Figure 11.

#### Texas **INSTRUMENTS**

#### **TYPICAL CHARACTERISTICS (continued)**

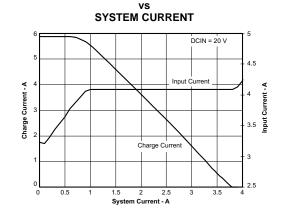

#### **INPUT CURRENT REGULATION (DPM) & CHARGE CURRENT**

Figure 12.

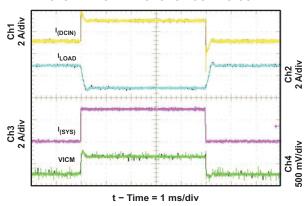

#### INPUT CURRENT REGULATION (DPM) TRANSIENT SYSTEM LOAD RESPONSE CCM TO CCM

Figure 13.

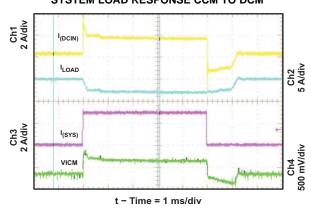

INPUT CURRENT REGULATION (DPM) TRANSIENT SYSTEM LOAD RESPONSE CCM TO DCM

Figure 14.

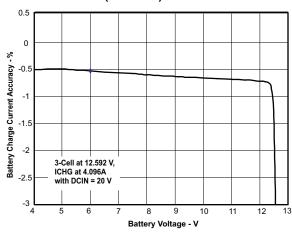

#### **CHARGE CURRENT REGULATION ACCURACY** VFB (BATTERY) VOLTAGE

Figure 15.

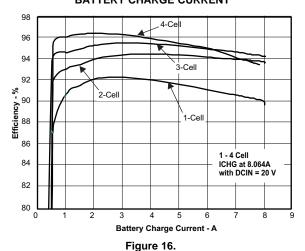

#### **EFFICIENCY BATTERY CHARGE CURRENT**

#### **BATTERY REMOVAL (From Constant Current Mode)**

Figure 17.

#### **TYPICAL CHARACTERISTICS (continued)**

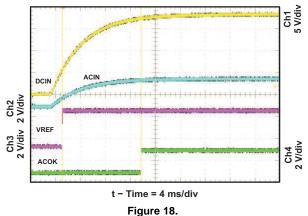

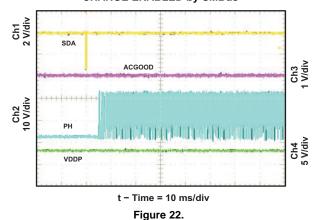

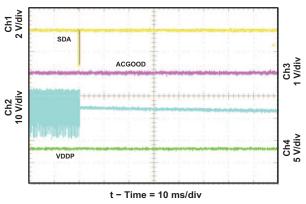

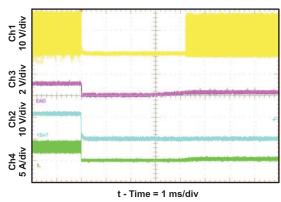

# CHARGER WHEN ADAPTER INSERTED

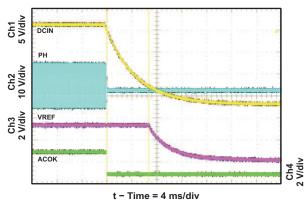

#### ADAPTER REMOVED WHILE CHARGING

Figure 19.

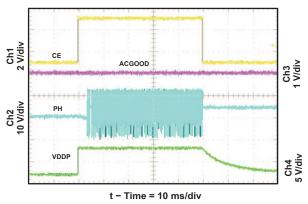

#### **CHARGE ENABLE/DISABLE**

Figure 20.

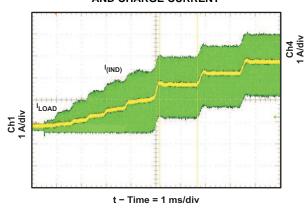

SOFT-START, INDUCTOR CURRENT AND CHARGE CURRENT

Figure 21.

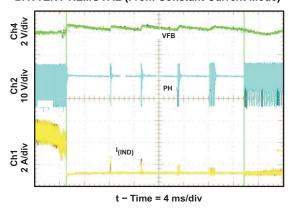

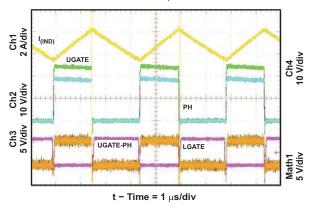

#### **CHARGE ENABLED by SMBus**

**CHARGE DISABLED by SMBus**

Figure 23.

Ch1 2 A/div

Ch2 10 V/div I(IND)

UGATE-PH

SLUS988 – OCTOBER 2009 www.ti.com

# TEXAS INSTRUMENTS

#### **TYPICAL CHARACTERISTICS (continued)**

Ch4 10 V/div

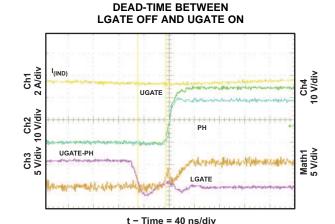

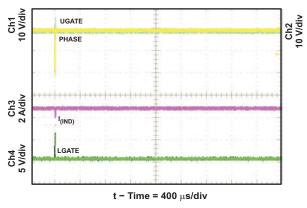

# DEAD-TIME BETWEEN UGATE OFF AND LGATE ON UGATE UGATE UGATE UGATE

LGATE

Figure 25.

#### **NEAR 100% DUTY CYCLE BOOTSTRAP RECHARGE PULSE**

Figure 26.

#### BATTERY SHORTED CHARGER RESPONSE, OVERCURRENT PROTECTION (OCP) AND CHARGE CURRENT REGULATION

Figure 27.

## CONTINUOUS CONDUCTION MODE (CCM) SWITCHING WAVEFORMS, ICHARGE = 3986 mA

Figure 28.

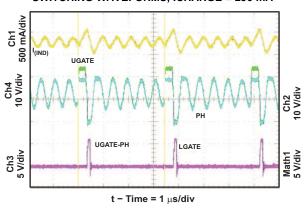

#### DISCONTINUOUS CONDUCTION MODE (DCM) SWITCHING WAVEFORMS, ICHARGE = 256 mA

Figure 29.

#### **TYPICAL CHARACTERISTICS (continued)**

# OFF-STATE BATTERY CURRENT (LOW Iq) VS VFB (BATTERY) VOLTAGE Total Part of the Property of

VFB - Voltage - V

Figure 30.

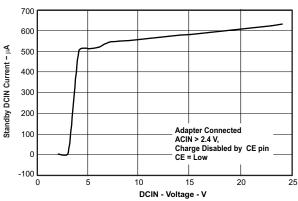

OFF-STATE DCIN CURRENT (LOW Iq)

vs

DCIN INPUT VOLTAGE (With Adapter Connected)

Figure 31.

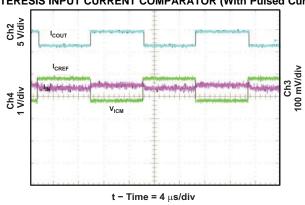

# PROGRAMMABLE REFERENCE AND HYSTERESIS INPUT CURRENT COMPARATOR (With Pulsed Current)

Figure 32.

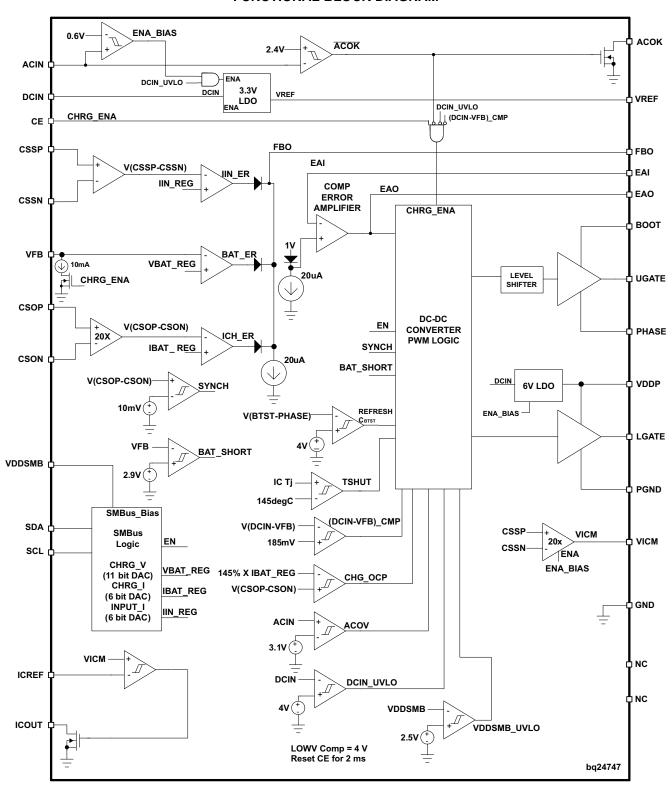

#### **FUNCTIONAL BLOCK DIAGRAM**

SLUS988 - OCTOBER 2009

#### DETAILED DESCRIPTION

#### **BATTERY VOLTAGE REGULATION**

The bq24747 uses a high-accuracy voltage regulator to supply charging voltage. The battery voltage regulation setting is programmed by the host microcontroller ( $\mu$ C), through the SMBus interface that sets an 11-bit DAC. The input voltage range of VFB is between 1.024 V and 19.2 V. The per-cell battery termination voltage is a function of the battery chemistry. (Consult the battery manufacturer to determine this voltage.) The programmed value should be the per-cell voltage times the number of series cells.

The VFB pin is used to sense the battery voltage for voltage regulation and should be connected as close to the battery as possible, or directly on the output capacitor. A 0.1-µF ceramic capacitor from VFB to GND is recommended to be as close to the VFB pin as possible to decouple high frequency noise.

#### **BATTERY CURRENT REGULATION**

The ChargeCurrent() SMBus 6-bit DAC register sets the maximum charging current. Battery current is sensed by resistor  $R_{SR}$  connected between the CSOP and CSON pins. The maximum full-scale differential voltage between CSOP and CSON is 80.64 mV. Thus, for a 0.010- $\Omega$  sense resistor, the maximum charging current is 8.064 A.

The CSOP and CSON pins are used to measure the voltage across  $R_{SR}$ , which has a default value of 10 m $\Omega$ . However, resistors of other values can also be used. A larger sense resistor gives a larger sense voltage and higher regulation accuracy, but at the expense of higher conduction loss.

#### INPUT ADAPTER CURRENT REGULATION

The total input current from an AC adapter or other DC source is a function of the system supply current and the battery charging current. System current normally fluctuates as portions of the systems are powered up or down. Without Dynamic Power Management (DPM), the source must be able to supply the maximum system current and the maximum charger input current simultaneously. By using DPM, the input current regulator reduces the charging current when the input current exceeds the limit set by the *InputCurrent()* SMBus 6 bit DAC register. With the high-accuracy limiting, the current capability of the AC adaptor can be lowered, reducing system cost.

In a manner similar to battery-current regulation, adaptor current is sensed by resistor  $R_{AC}$  connected between the CSSP and CSSN pins. The maximum full-scale differential voltage between CSSP and CSSN is 110.08 mV. Thus, for a  $0.010\Omega$  sense resistor, the maximum input current is 11.008 A.

The CSSP and CSSN pins are used to sense  $R_{AC}$  with default value of 10 m $\Omega$ . However, resistors of other values can also be used. A larger sense resistor gives a larger sense voltage and a higher regulation accuracy, but at the expense of higher conduction loss.

#### ADAPTER DETECT AND POWER UP

An external resistor voltage divider attenuates the adapter voltage before it goes to ACIN. The adapter-detect threshold should typically be programmed to a value greater than the maximum battery voltage and lower than the minimum allowed adapter voltage.

If DCIN is below 4 V, the charger is disabled and ACOK goes low.

If ACIN is below 0.6 V but DCIN is above 4 V, part of the bias is enabled, including a crude bandgap reference, ACFET drive and BATFET drive. VICM is disabled and pulled down to GND. The total quiescent current is less than 10µA.

When ACIN rises above 0.6 V and DCIN is above 4 V, all the bias circuits are enabled, the VDDP output goes to 6 V, and VREF goes to 3.3 V. VICM becomes valid to proportionally reflect the adapter current.

When ACIN keeps rising and passes 2.4 V, it indicates that a valid AC adapter is present. 200µs later, and the following occurs:

- · ACOK is pulled high through an external pull-up resistor to the host digital voltage rail;

- The charger turns on if all the conditions are satisfied after an additional 2-ms deglitch time. (refer to *Enable and Disable Charging*)

Product Folder Link(s): bg24747

# TEXAS INSTRUMENTS

#### **ENABLE AND DISABLE CHARGING**

The following conditions must be valid before charging is enabled:

- CE is HIGH;

- Adapter is detected (ACIN > 2.4 V);

- Adapter is higher than the DCIN-VFB threshold;

- 200µs delay is complete after adapter detected;

- VDDP and VREF are valid;

- Thermal Shutdown (TSHUT) is not active;

Any of the following conditions stop the charge cycle:

- CE is LOW;

- · Adapter is removed;

- Adapter voltage is less than 250 mV above the battery;

- Adapter is over voltage;

- Charge output current is over programmed current;

- TSHUT IC temperature threshold is reached (145°C on rising-edge with 15°C hysteresis).

#### **AUTOMATIC INTERNAL SOFT-START CHARGER CURRENT**

The charger automatically soft-starts the charger regulation current every time the charger is enabled to ensure that there is no overshoot or stress on the output capacitors or the power converter. The soft-start function steps up the charge current into 8 evenly-divided steps, gradually building up to the full programmed charge current. Each step lasts approximately 1 ms, for a typical rise time of 8 ms. No external components are needed for this function.

#### **CONVERTER OPERATION**

The synchronous-buck PWM converter operates at a fixed frequency (300 kHz) in voltage mode with a feed-forward control scheme. A type-III compensation network allows the use of ceramic capacitors at the output of the converter. The input compensation stage is connected between the feedback output (FBO) and the error amplifier input (EAI). The feedback compensation stage is connected between the error amplifier input (EAI) and error amplifier output (EAO). The LC output filter has a characteristic resonant frequency that ensures sufficient phase margin for the target bandwidth.

$$f_{o} = \frac{1}{2\pi \sqrt{L_{o}C_{o}}}$$

The resonant frequency,  $f_{o}$ , is given by:

An internal saw-tooth ramp is compared to the internal EAO error control signal to vary the converter duty cycle. The ramp height is 1/15 of the input adapter voltage, always keeping it directly proportional to the input adapter voltage. This cancels out any loop-gain variation due to an input voltage change, simplifying loop-compensation design. The ramp is offset by 250 mV in order to allow a 0% duty cycle when the EAO signal is below the ramp. The EAO signal is also allowed to exceed the saw-tooth ramp signal in order to respond to a 100% duty-cycle PWM request. The internal gate-drive logic allows a 99.98% duty cycle while ensuring that the N-channel upper device always has enough voltage to stay fully on. If the BOOT-pin-to-PHASE-pin voltage falls below 4.5 V for more than 3 cycles, the high-side n-channel power MOSFET is turned off and the low-side n-channel power MOSFET is turned on to pull the PHASE node down and recharge the BOOT capacitor. Then the high-side driver returns to 100% duty-cycle operation until the (BOOT-PHASE) voltage is again detected falling low due to leakage current discharging the BOOT capacitor below 4 V, and the reset pulse is reissued.

The 300-kHz fixed-frequency oscillator keeps tight control of the switching frequency under all conditions of input voltage, battery voltage, charge current, and temperature, simplifying output-filter design and keeping it out of the audible-noise region. The charge-current sense resistor  $R_{SR}$ ) should be positioned with half or more of the total output capacitance placed before  $R_{SR}$ , contacting both  $R_{SR}$  and the output inductor; and the remaining capacitance placed after  $R_{SR}$ . The output capacitance should be divided and placed on either side of  $R_{SR}$ . A ratio of 50:50% gives the best performance, but the node in which the output inductor and  $R_{SR}$  connect should have a minimum of 50% of the total capacitance. This capacitance provides sufficient filtering to remove the switching noise and give better accuracy. The type-III compensation provides phase boost near the crossover frequency to provide sufficient phase margin.

Submit Documentation Feedback

www.ti.com SLUS988 - OCTOBER 2009

#### SYNCHRONOUS AND NON-SYNCHRONOUS OPERATION

The charger operates in non-synchronous mode when the sensed charge current is below the internal ISYNSET value of 13 mV (1.3 A) falling, and 0.8 mV (800 mA) rising (with built-in hysteresis). Otherwise, the charger operates in synchronous mode.

In synchronous mode, the low-side n-channel power MOSFET is on, and the high-side n-channel power MOSFET is off. The internal gate-drive logic enforces break-before-make switching to prevent shoot-through currents. During the 30-ns dead time when both FETs are off, the back diode of the low-side power MOSFET conducts the inductor current. Having the low-side FET turned on keeps the power dissipation low, and safely allows high-current charging. In synchronous mode, the inductor current is always flowing and operates in Continuous Conduction Mode (CCM), creating a fixed two-pole system.

In non-synchronous operation, after the high-side n-channel power MOSFET turns off, and after the break-before-make dead-time, the low-side n-channel power MOSFET turns on for approximately 80 ns, then the low-side power MOSFET turns off and stays off until the beginning of the next cycle, when the high-side power MOSFET is turned on again. The 80-ns low-side MOSFET on-time is required to ensure that the bootstrap capacitor is always charged and able to keep the high-side power MOSFET turned on during the next cycle. This is important for battery chargers, where unlike regular dc-dc converters, there is a battery load that maintains a voltage, and can both source and sink current. The 80-ns low-side pulse pulls the PHASE node (connection between high and low-side MOSFET) down, allowing the bootstrap capacitor to recharge up to the VDDP LDO value. After the 80 ns, the low-side MOSFET is kept off to prevent negative inductor current from flowing. The inductor current is blocked by the off-state low-side MOSFET, and the inductor current becomes discontinuous. This mode is called Discontinuous Conduction Mode (DCM).

In DCM operation, the loop response automatically changes, and acts as a single-pole system at which the pole is proportional to the load current, because the converter does not sink current, and only the load provides a current sink. At very low currents, the loop response is slower, because there is less sinking current available to discharge the output voltage. At very low currents during non-synchronous operation, there may be a small amount of negative inductor current during the 80-ns recharge pulse. This should be low enough to be absorbed by the input capacitance.

When the converter goes into 0% duty cycle, neither MOSFET turns on (no 80-ns recharge pulse), and there is no discharge from the battery.

#### ISYNSET CONTROL (CHARGE UNDERCURRENT)

In bq24747, ISYN is the internally-set ISYNSET value as the charge-current threshold at which the charger switches from non-synchronous operation to synchronous operation. The low-side driver turns on for only 80 ns to charge the boost capacitor. This is important to prevent negative inductor current, which may cause a boost effect in which the input voltage increases as power is transferred from the battery to the input capacitors. This can lead to an overvoltage condition on the DCIN node, and potentially can damage the system. This programmable value allows setting the current threshold for any inductor ripple current to avoid negative inductor current. The minimum synchronous threshold should be set from 50%–100% of the inductor ripple current, where the inductor ripple current is calculated using Equation 1.

$$\frac{I_{\textit{ripple}\_max}}{2} \le I_{\textit{SYN}} \le I_{\textit{ripple}\_max}$$

and

$$I_{ripple} = \frac{(V_{in} - V_{bat}) \times \frac{V_{bat}}{V_{in}} \times \frac{1}{f_s}}{L} = \frac{V_{in} \times (1 - D) \times D \times \frac{1}{f_s}}{L}$$

(1)

Where: V<sub>IN MAX</sub>: maximum adapter voltage

V<sub>BAT MIN</sub>: minimum BAT voltage

f<sub>S</sub>: switching frequency

L<sub>MIN</sub>: minimum output inductor

The ISYNSET comparator, or charge undercurrent comparator, compares the voltage between CSOP-CSON and the 13-mV internal threshold. The threshold is set internally to 13 mV on the falling edge and 8 mV on the rising edge (with built-in hysteresis) with 10% variation.

#### HIGH ACCURACY VICM USING CURRENT SENSE AMPLIFIER (CSA)

An industry-standard, high-accuracy current-sense amplifier (CSA) provides an analog output voltage at the VICM pin that can be used by a host system to monitor the input current. The CSA amplifies the input sensed voltage of CSSP-CSSN by 20x through the VICM pin. The VICM output is a voltage source 20x the input differential voltage. When DCIN is above 4 V and ACIN is above 0.6 V, VICM no longer stays at ground, but becomes active. A lower voltage can be used by connecting a resistor divider from VICM to GND, while still achieving good accuracy over temperature if the resistors are matched by their thermal coefficients.

A  $0.1\mu F$  capacitor connected on the output is recommended for decoupling high-frequency noise. An additional RC filter is optional, after the  $0.1\mu F$  capacitor, if additional filtering is desired. Note that adding filtering also adds additional response delay.

#### VDDSMB INPUT SUPPLY

The VDDSMB input provides bias power to the SMBus interface which is active when: 1) DCIN > DCIN\_UVLO, 2) ACIN > 0.6 V, and 3) VDDSBM > VDDSBM\_UVLO. Connect VDDSMB to an external 3.3 V or 5 V supply rail to keep the SMBus interface active while the supply to DCIN is connected. Under this condition, the internal registers are maintained, and SMBus communication can occur between the host and the charger. Bypass VDDSMB to GND with a 0.1-µF or greater ceramic capacitor. The VDDSMB UVLO threshold is 2.7 V rising and 250 mV falling (with hysteresis). The SMBus is always active and can be written to or read from whenever VDDSMB is above the VDDSMB UVLO threshold.

#### **INPUT UNDER VOLTAGE LOCK OUT (UVLO)**

The system must have a minimum 4 V DCIN voltage from the input adapter to allow proper charger operation. When the DCIN voltage is below 4 V, the bias circuits VDDP and VREF stay inactive, even with ACIN above 0.6 V.

#### BATTERY OVERVOLTAGE PROTECTION

The converter will not allow the high-side FET to turn-on when the battery voltage at VFB exceeds 104% of the regulation voltage set-point, until the VFB voltage returns below 101% of the regulation voltage. This allows quick response to an overvoltage condition – such as occurs when the load is removed or the battery is disconnected. A 10-mA current sink from VFB to PGND is on only during charge and allows discharging the stored output inductor energy that is transferred to the output capacitors.

#### BATTERY SHORTED (Battery Undervoltage) PROTECTION AND BATTERY TRICKLE CHARGING