# dsPIC30F Family Reference Manual

# High-Performance Digital Signal Controllers

© 2006 Microchip Technology Inc.

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WAR-RANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# **QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV** — ISO/TS 16949:2002 —

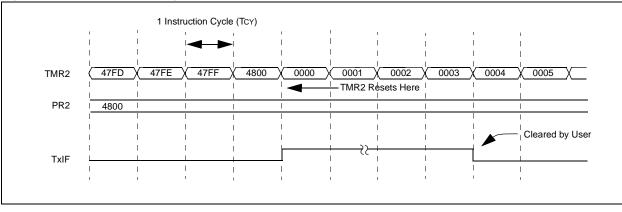

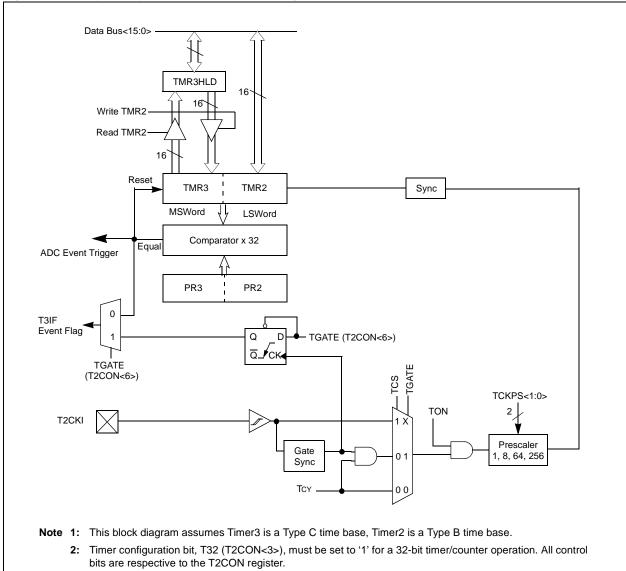

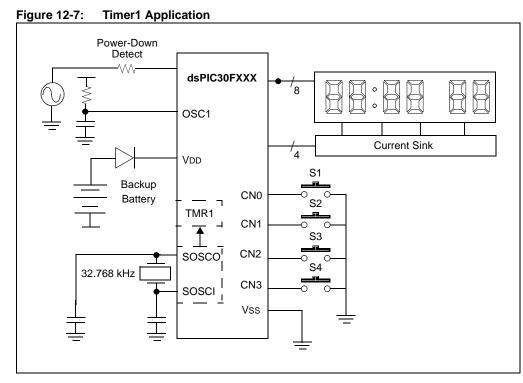

#### Trademarks

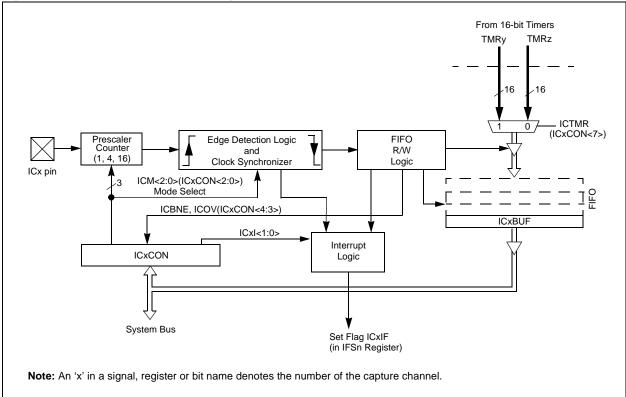

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Linear Active Thermistor, MPASM, MPLIB, MPLINK, MPSIM, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, Real ICE, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and Zena are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2006, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received ISO/TS-16949:2002 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona and Mountain View, California in October 2003. The Company's quality system processes and procedures are for its PICmicro® 8-bit MCUs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# <u>PAGE</u>

| SECTION 1. INTRODUCTION       | 1-1  |

|-------------------------------|------|

| Introduction                  |      |

| Manual Objective              |      |

| Device Structure              |      |

| Development Support           |      |

| Style and Symbol Conventions  |      |

| Related Documents             |      |

| Revision History              |      |

| SECTION 2. CPU                | 2-1  |

| Introduction                  |      |

| Programmer's Model            |      |

| Software Stack Pointer        |      |

| CPU Register Descriptions     | 2-11 |

| Arithmetic Logic Unit (ALU)   |      |

| DSP Engine                    |      |

| Divide Support                |      |

| Instruction Flow Types        |      |

| Loop Constructs               |      |

| Address Register Dependencies |      |

| Register Maps                 |      |

| Related Application Notes     |      |

| Revision History              | 2-41 |

| SECTION 3. DATA MEMORY        | 3-1  |

| Introduction                  | 2.2  |

| Introduction                              |  |

|-------------------------------------------|--|

| Data Space Address Generator Units (AGUs) |  |

| Modulo Addressing                         |  |

| Bit-Reversed Addressing                   |  |

| Control Register Descriptions             |  |

| Related Application Notes                 |  |

| Revision History                          |  |

|                                           |  |

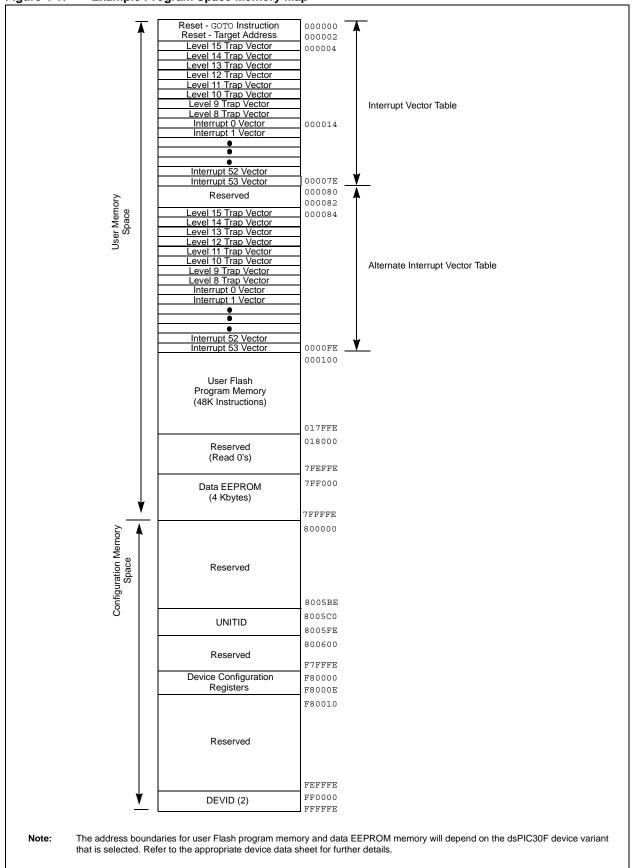

# SECTION 4. PROGRAM MEMORY

| 4 | -1 |  |

|---|----|--|

|   |    |  |

| Program Memory Address Map               |  |

|------------------------------------------|--|

| Program Counter                          |  |

| Data Access from Program Memory          |  |

| Program Space Visibility from Data Space |  |

| Program Memory Writes                    |  |

| PSV Code Examples                        |  |

| Related Application Notes                |  |

| Revision History                         |  |

|                                          |  |

# PAGE

| SECTION 5. FLASH AND EEPROM PROGRAMMING                         | 5-1 |

|-----------------------------------------------------------------|-----|

| Introduction                                                    |     |

| Table Instruction Operation                                     |     |

| Control Registers                                               |     |

| Run-Time Self-Programming (RTSP)                                |     |

| Data EEPROM Programming                                         |     |

| Design Tips                                                     |     |

| Related Application Notes                                       |     |

| Revision History                                                |     |

| SECTION 6. RESET INTERRUPTS                                     | 6-1 |

| Introduction                                                    | 6-2 |

| Non-Maskable Traps                                              |     |

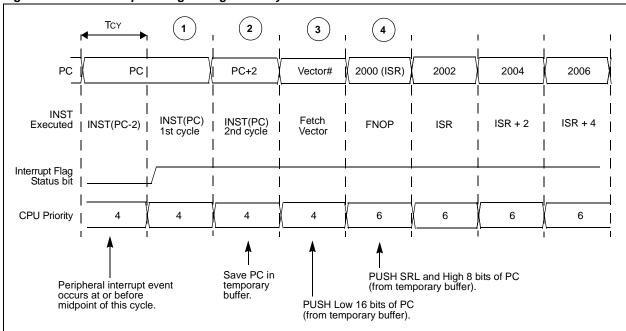

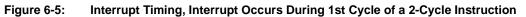

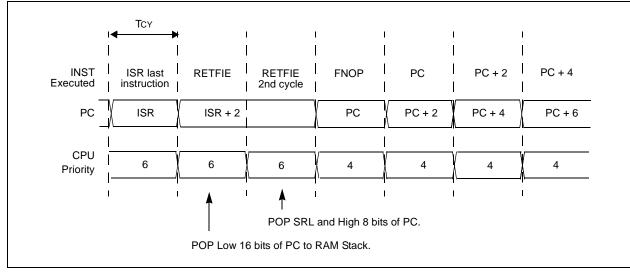

| Interrupt Processing Timing                                     |     |

| Interrupt Control and Status Registers                          |     |

| Interrupt Setup Procedures                                      |     |

| Design Tips                                                     |     |

| Related Application Notes                                       |     |

| Revision History                                                |     |

| SECTION 7. OSCILLATOR                                           | 7-1 |

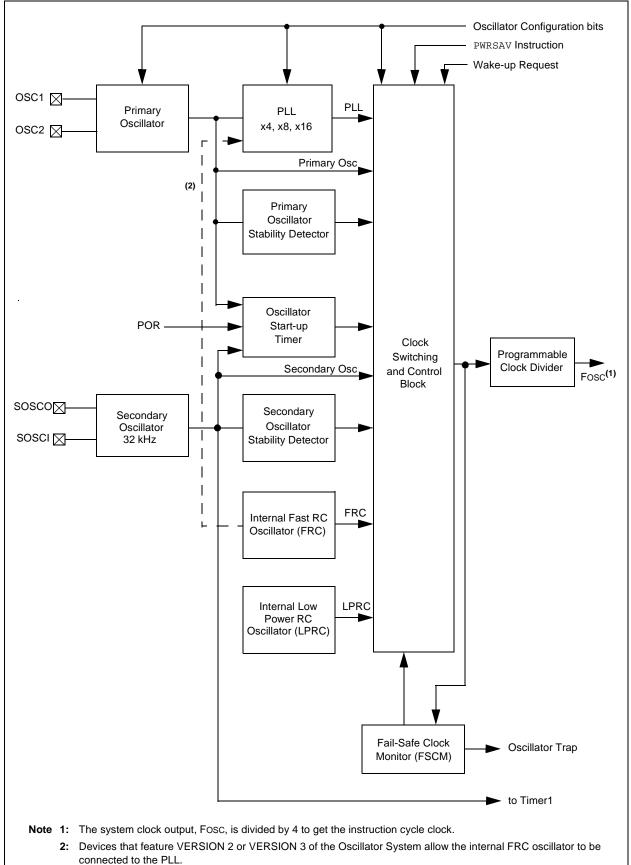

| Introduction                                                    |     |

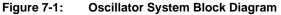

| Device Clocking and MIPS                                        |     |

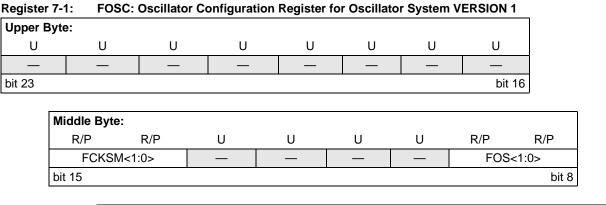

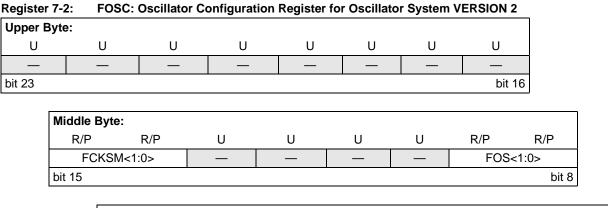

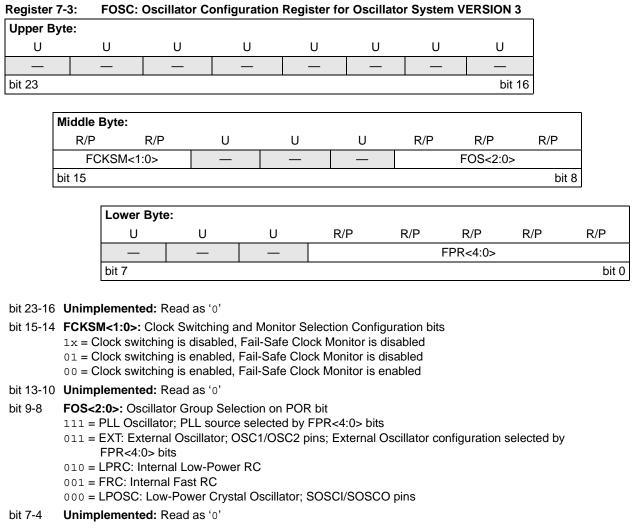

| Oscillator Configuration                                        | 7-6 |

| Oscillator Control Registers – OSCCON and OSCTUN                |     |

| Primary Oscillator                                              |     |

| Crystal Oscillators/Ceramic Resonators                          |     |

| Determining Best Values for Crystals, Clock Mode, C1, C2 and Rs |     |

| External Clock Input                                            |     |

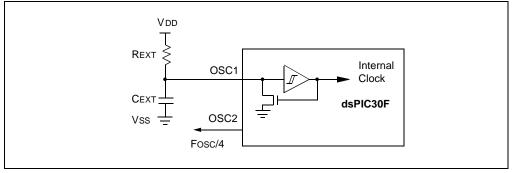

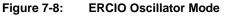

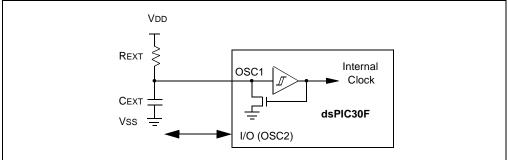

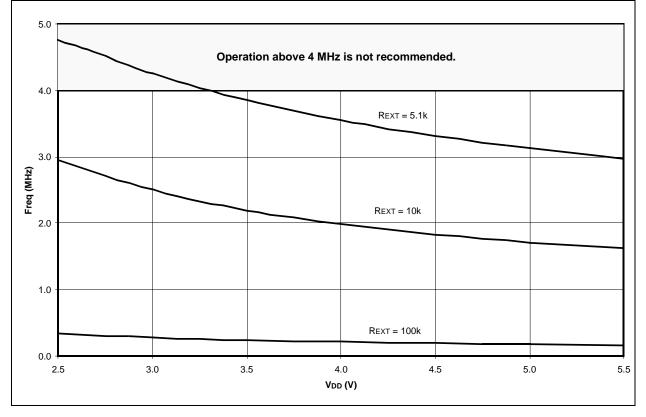

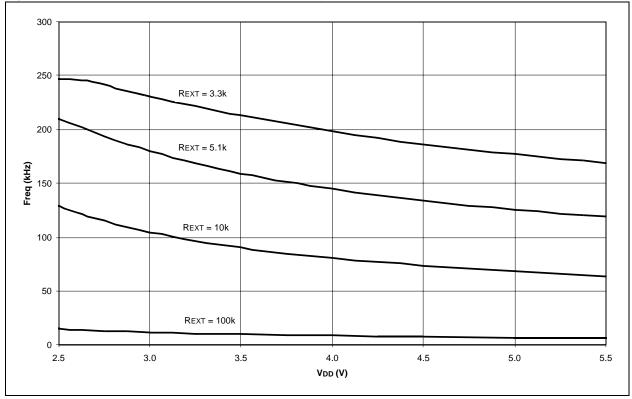

| External RC Oscillator                                          |     |

| Phase Locked Loop (PLL)                                         |     |

| Low-Power 32 kHz Crystal Oscillator                             |     |

| Oscillator Start-up Timer (OST)                                 |     |

| Internal Fast RC Oscillator (FRC)                               |     |

| Internal Low-Power RC (LPRC) Oscillator                         |     |

| Fail-Safe Clock Monitor (FSCM)                                  |     |

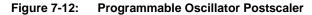

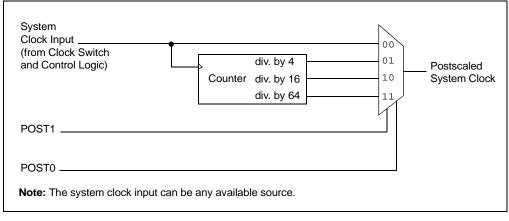

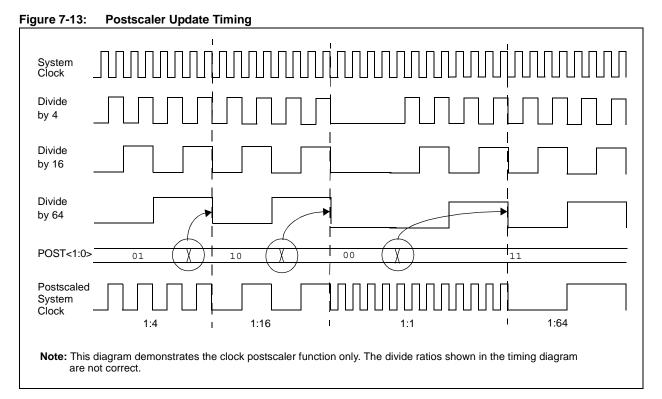

| Programmable Oscillator Postscaler                              |     |

# <u>PAGE</u>

| SECTION 8. RESET                                                                                                                                                                                                                                                                                                          | 8-1                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                         |

| Clock Source Selection at Reset                                                                                                                                                                                                                                                                                           |                                                                                                                                                                         |

| POR: Power-on Reset                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                         |

| External Reset (EXTR)                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                         |

| Software RESET Instruction (SWR)                                                                                                                                                                                                                                                                                          |                                                                                                                                                                         |

| Watchdog Time-out Reset (WDTR)                                                                                                                                                                                                                                                                                            |                                                                                                                                                                         |

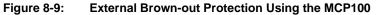

| Brown-out Reset (BOR)                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                         |

| Using the RCON Status Bits                                                                                                                                                                                                                                                                                                | 8-10                                                                                                                                                                    |

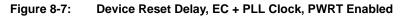

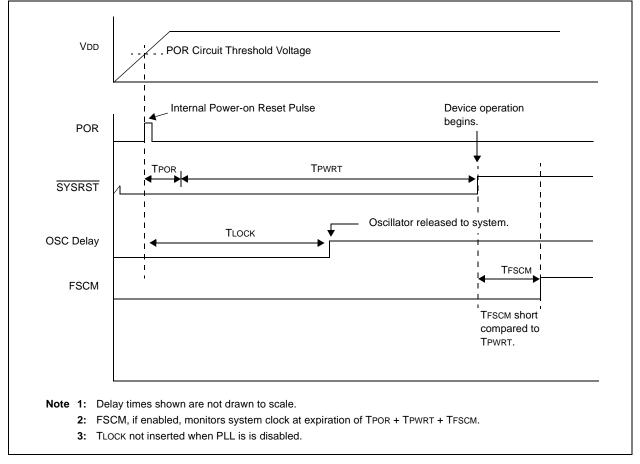

| Device Reset Times                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                         |

| Device Start-up Time Lines                                                                                                                                                                                                                                                                                                |                                                                                                                                                                         |

| Special Function Register Reset States                                                                                                                                                                                                                                                                                    |                                                                                                                                                                         |

| Design Tips                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                         |

| Related Application Notes                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                         |

| Revision History                                                                                                                                                                                                                                                                                                          | 8-19                                                                                                                                                                    |

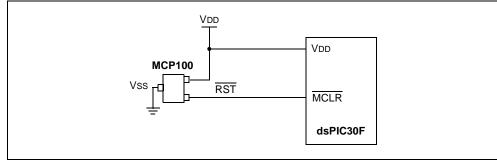

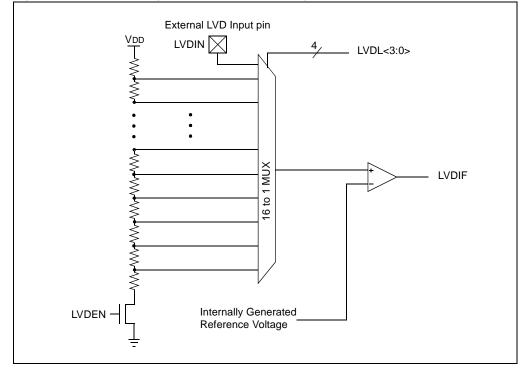

| SECTION 9. LOW VOLTAGE DETECT (LVD)                                                                                                                                                                                                                                                                                       | 9-1                                                                                                                                                                     |

| Introduction                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                         |

| LVD Operation                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                         |

| Design Tips                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                         |

| Related Application Notes                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                         |

| Revision History                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                         |

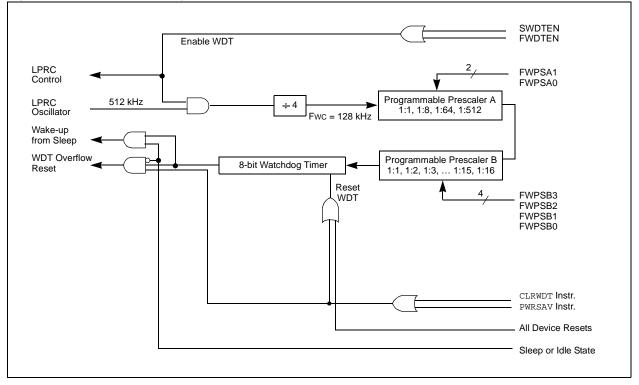

| SECTION 10. WATCHDOG TIMER AND POWER SAVING MODES                                                                                                                                                                                                                                                                         | 10-1                                                                                                                                                                    |

| SECTION 10. WATCHDOG TIMER AND POWER SAVING MODES                                                                                                                                                                                                                                                                         | <b>10-1</b>                                                                                                                                                             |

| Introduction                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                         |

| Introduction<br>Power Saving Modes                                                                                                                                                                                                                                                                                        |                                                                                                                                                                         |

| Introduction<br>Power Saving Modes<br>Sleep Mode                                                                                                                                                                                                                                                                          |                                                                                                                                                                         |

| Introduction<br>Power Saving Modes<br>Sleep Mode<br>Idle Mode                                                                                                                                                                                                                                                             |                                                                                                                                                                         |

| Introduction<br>Power Saving Modes<br>Sleep Mode<br>Idle Mode<br>Interrupts Coincident with Power Save Instructions                                                                                                                                                                                                       |                                                                                                                                                                         |

| Introduction<br>Power Saving Modes<br>Sleep Mode<br>Idle Mode<br>Interrupts Coincident with Power Save Instructions<br>Watchdog Timer                                                                                                                                                                                     |                                                                                                                                                                         |

| Introduction<br>Power Saving Modes<br>Sleep Mode<br>Idle Mode<br>Interrupts Coincident with Power Save Instructions<br>Watchdog Timer<br>Peripheral Module Disable (PMD) Registers                                                                                                                                        |                                                                                                                                                                         |

| Introduction<br>Power Saving Modes<br>Sleep Mode<br>Idle Mode<br>Interrupts Coincident with Power Save Instructions<br>Watchdog Timer<br>Peripheral Module Disable (PMD) Registers<br>Design Tips                                                                                                                         | 10-2<br>10-2<br>10-2<br>10-4<br>10-4<br>10-5<br>10-6<br>10-9<br>10-9                                                                                                    |

| Introduction<br>Power Saving Modes<br>Sleep Mode<br>Idle Mode<br>Interrupts Coincident with Power Save Instructions<br>Watchdog Timer<br>Peripheral Module Disable (PMD) Registers                                                                                                                                        | 10-2<br>10-2<br>10-2<br>10-2<br>10-4<br>10-4<br>10-5<br>10-6<br>10-9<br>10-10<br>10-11                                                                                  |

| Introduction<br>Power Saving Modes<br>Sleep Mode<br>Idle Mode<br>Interrupts Coincident with Power Save Instructions<br>Watchdog Timer<br>Peripheral Module Disable (PMD) Registers<br>Design Tips<br>Related Application Notes<br>Revision History                                                                        |                                                                                                                                                                         |

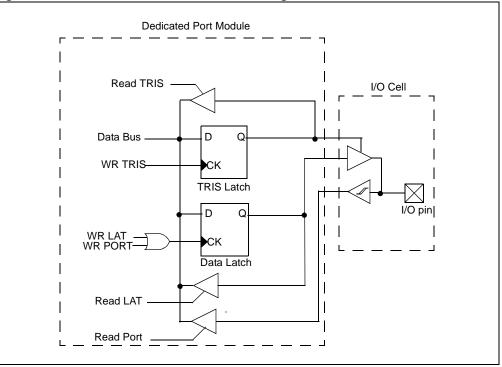

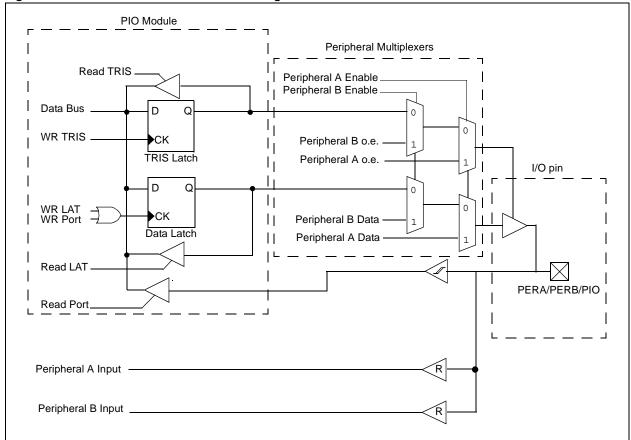

| Introduction<br>Power Saving Modes<br>Sleep Mode<br>Idle Mode<br>Interrupts Coincident with Power Save Instructions<br>Watchdog Timer<br>Peripheral Module Disable (PMD) Registers<br>Design Tips<br>Related Application Notes<br>Revision History<br>SECTION 11. I/O PORTS                                               |                                                                                                                                                                         |

| Introduction<br>Power Saving Modes<br>Sleep Mode<br>Idle Mode<br>Interrupts Coincident with Power Save Instructions<br>Watchdog Timer<br>Peripheral Module Disable (PMD) Registers<br>Design Tips<br>Related Application Notes<br>Revision History<br>SECTION 11. I/O PORTS<br>Introduction                               |                                                                                                                                                                         |

| Introduction<br>Power Saving Modes<br>Sleep Mode<br>Idle Mode<br>Interrupts Coincident with Power Save Instructions<br>Watchdog Timer<br>Peripheral Module Disable (PMD) Registers<br>Design Tips<br>Related Application Notes<br>Revision History<br>SECTION 11. I/O PORTS<br>Introduction<br>I/O Port Control Registers |                                                                                                                                                                         |

| Introduction                                                                                                                                                                                                                                                                                                              | 10-2<br>10-2<br>10-2<br>10-2<br>10-4<br>10-4<br>10-5<br>10-6<br>10-9<br>10-10<br>10-11<br>10-12<br><b>11-1</b><br>11-2<br>11-3<br>11-4                                  |

| Introduction<br>Power Saving Modes                                                                                                                                                                                                                                                                                        | 10-2<br>10-2<br>10-2<br>10-2<br>10-4<br>10-5<br>10-6<br>10-9<br>10-10<br>10-10<br>10-11<br>10-12<br><b>11-1</b><br>11-2<br>11-3<br>11-4                                 |

| Introduction<br>Power Saving Modes                                                                                                                                                                                                                                                                                        | 10-2<br>10-2<br>10-2<br>10-2<br>10-4<br>10-4<br>10-5<br>10-6<br>10-9<br>10-10<br>10-11<br>10-12<br><b>11-1</b><br>11-2<br>11-3<br>11-4<br>11-6<br>11-7                  |

| Introduction<br>Power Saving Modes                                                                                                                                                                                                                                                                                        |                                                                                                                                                                         |

| Introduction<br>Power Saving Modes                                                                                                                                                                                                                                                                                        | 10-2<br>10-2<br>10-2<br>10-2<br>10-4<br>10-4<br>10-5<br>10-6<br>10-9<br>10-10<br>10-11<br>10-12<br><b>11-1</b><br>11-2<br>11-3<br>11-4<br>11-6<br>11-7<br>11-8<br>11-11 |

# **PAGE**

14-1

| SECTION 12. TIMERS                                                  | 12-1 |

|---------------------------------------------------------------------|------|

| Introduction                                                        |      |

| Timer Variants                                                      |      |

| Control Registers                                                   |      |

| Modes of Operation                                                  |      |

| Timer Prescalers                                                    |      |

| Timer Interrupts                                                    |      |

| Reading and Writing 16-bit Timer Module Registers                   |      |

| Low Power 32 kHz Crystal Oscillator Input                           |      |

| 32-bit Timer Configuration                                          |      |

| 32-bit Timer Modes of Operation                                     |      |

| Reading and Writing into 32-bit Timers                              |      |

| Timer Operation in Power Saving States                              |      |

| Peripherals Using Timer Modules                                     |      |

| Design Tips                                                         |      |

| Related Application Notes                                           |      |

| Revision History                                                    |      |

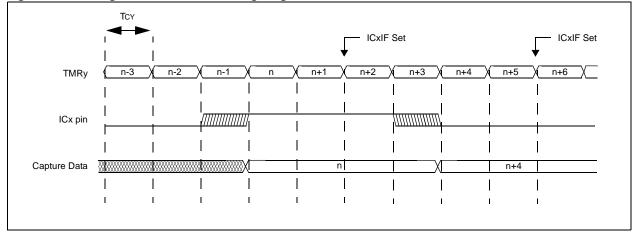

| SECTION 13. INPUT CAPTURE                                           | 13-1 |

| Introduction                                                        |      |

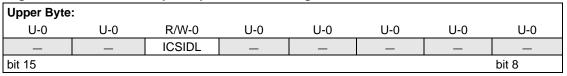

| Input Capture Registers                                             |      |

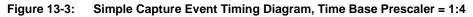

| Timer Selection                                                     |      |

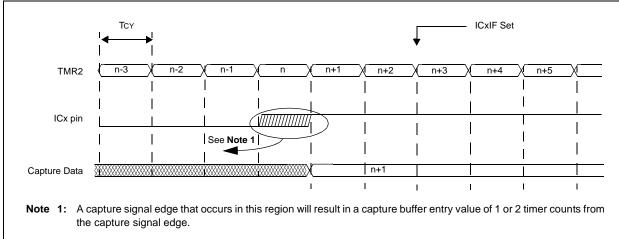

| Input Capture Event Modes                                           |      |

| Capture Buffer Operation                                            |      |

| Input Capture Interrupts                                            |      |

| UART Autobaud Support                                               |      |

| Input Capture Operation in Power Saving States                      |      |

| I/O Pin Control                                                     |      |

| Special Function Registers Associated with the Input Capture Module |      |

| Design Tips                                                         |      |

| Related Application Notes                                           |      |

| Revision History                                                    |      |

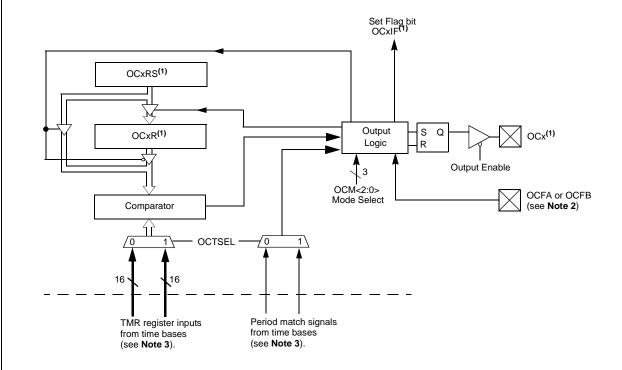

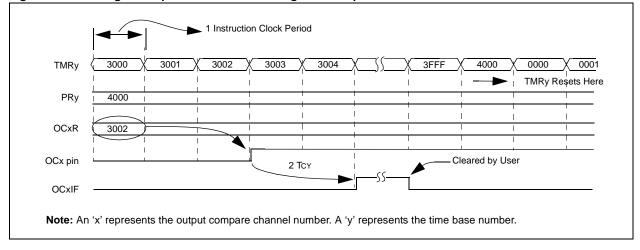

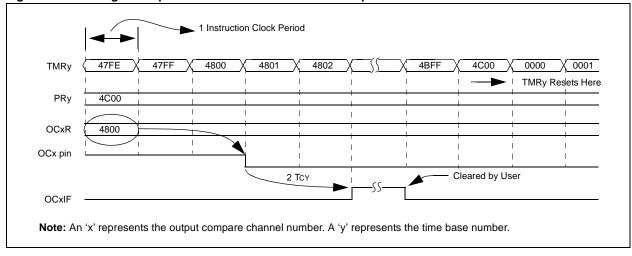

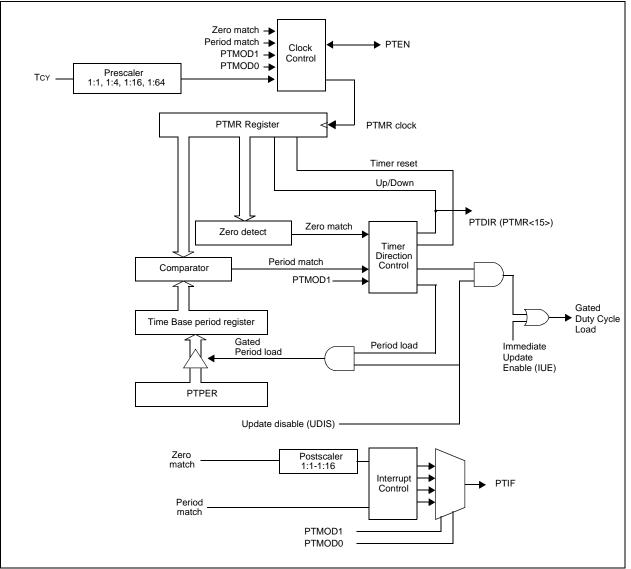

# **SECTION 14. OUTPUT COMPARE**

| Introduction                                    |  |

|-------------------------------------------------|--|

| Output Compare Registers                        |  |

| Modes of Operation                              |  |

| Output Compare Operation in Power Saving States |  |

| I/O Pin Control                                 |  |

| Design Tips                                     |  |

| Related Application Notes                       |  |

| Revision History                                |  |

|                                                 |  |

# PAGE

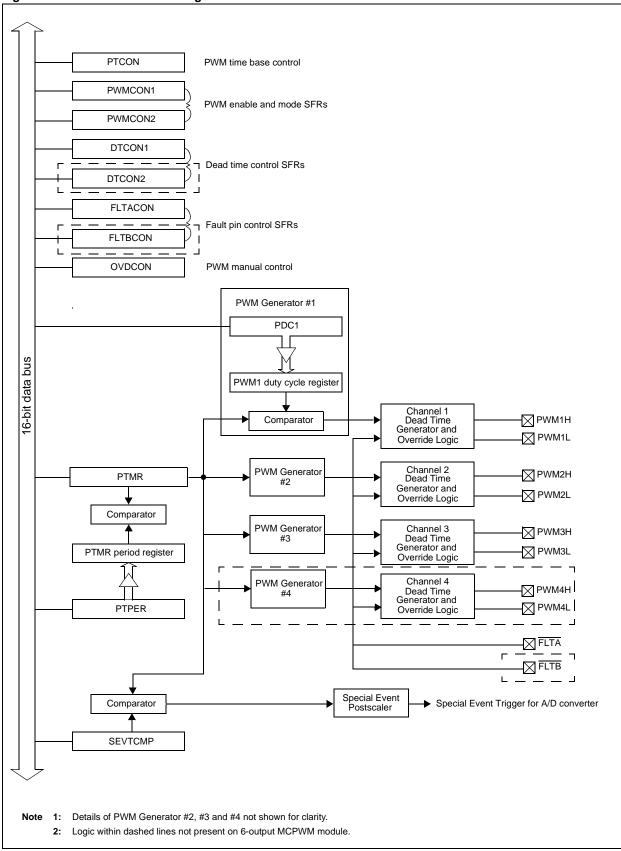

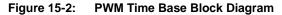

| SECTION 15. MOTOR CONTROL PWM                  | 15-1 |

|------------------------------------------------|------|

| Introduction                                   |      |

| Control Registers                              |      |

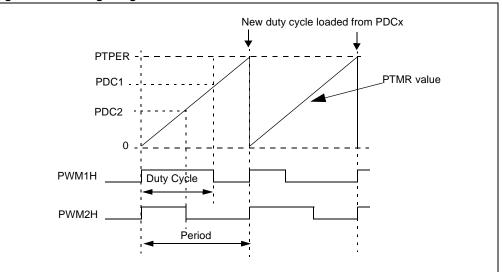

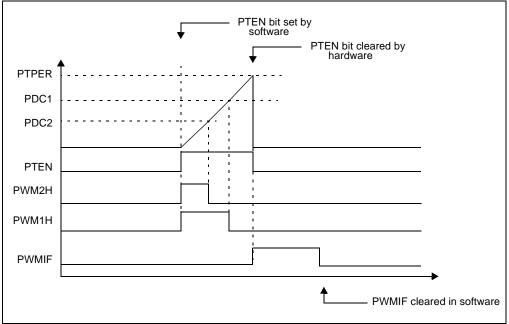

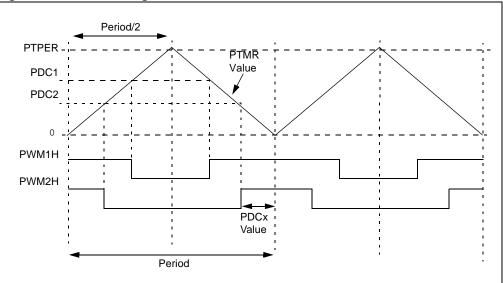

| PWM Time Base                                  |      |

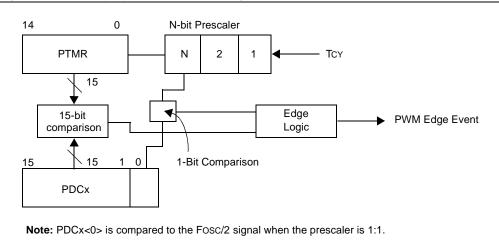

| PWM Duty Cycle Comparison Units                |      |

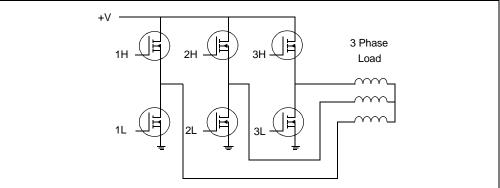

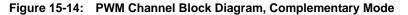

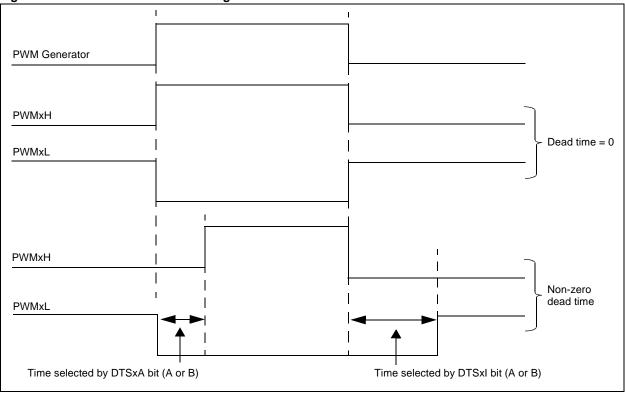

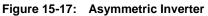

| Complementary PWM Output Mode                  |      |

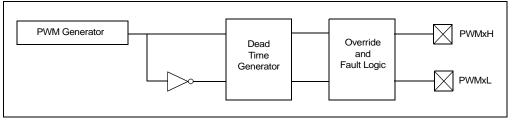

| Dead Time Control                              |      |

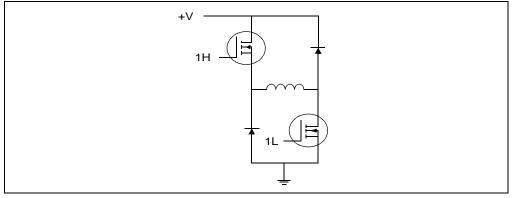

| Independent PWM Output Mode                    |      |

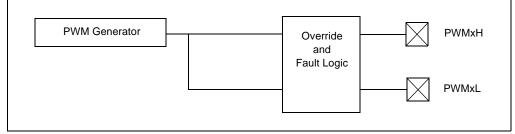

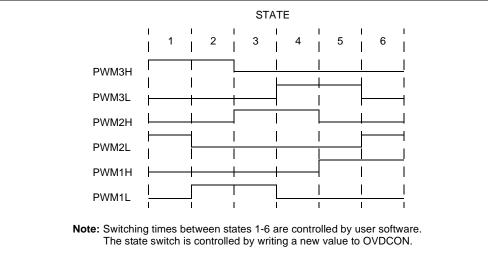

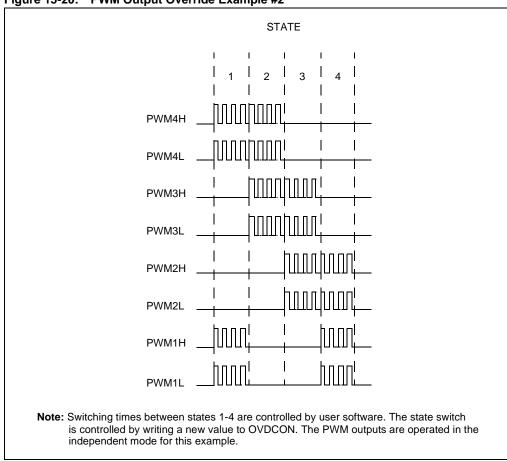

| PWM Output Override                            |      |

| PWM Output and Polarity Control                |      |

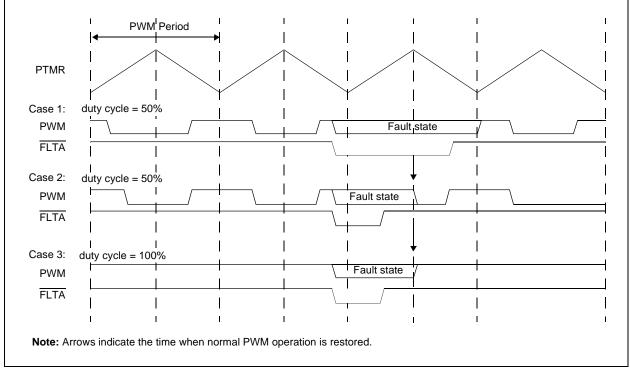

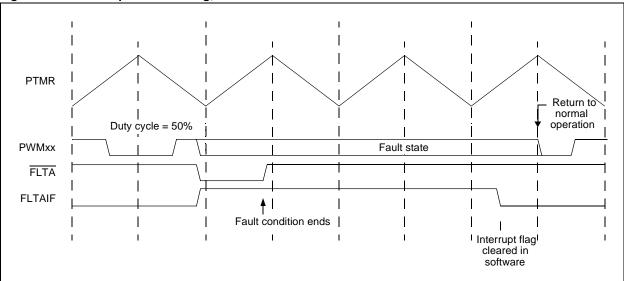

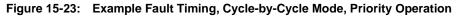

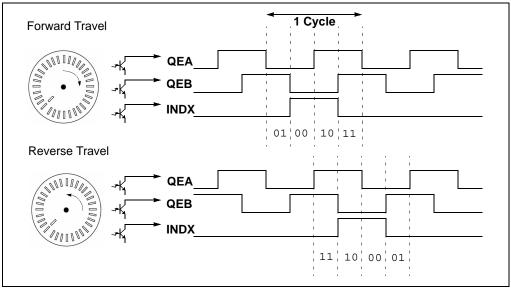

| PWM Fault Pins                                 |      |

| PWM Update Lockout                             |      |

| PWM Special Event Trigger                      |      |

| Operation in Device Power Saving Modes         |      |

| Special Features for Device Emulation          |      |

| Related Application Notes                      |      |

| Revision History                               |      |

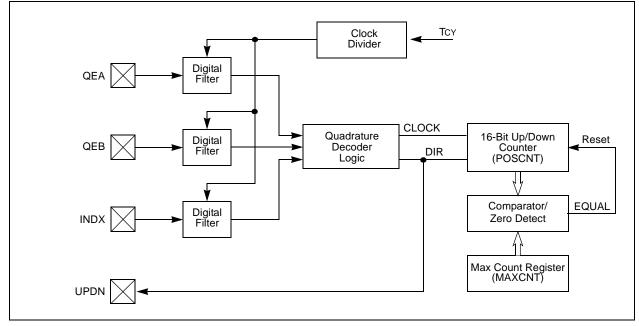

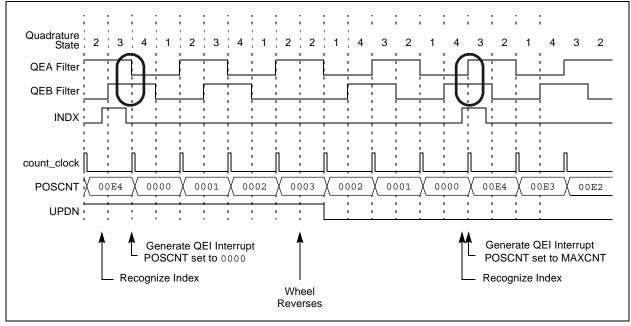

| SECTION 16. QUADRATURE ENCODER INTERFACE (QEI) | 16-1 |

| Module Introduction                            |      |

| Control and Status Registers                   |      |

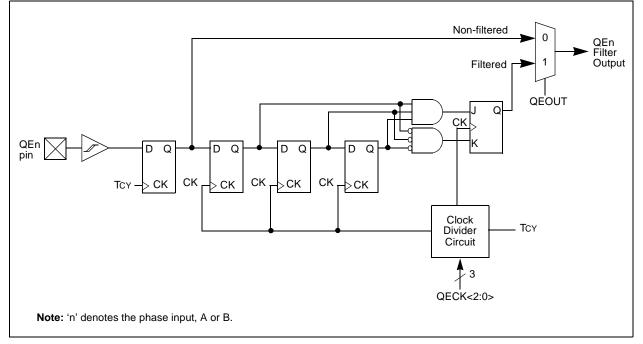

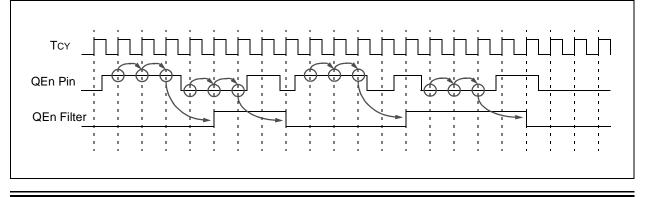

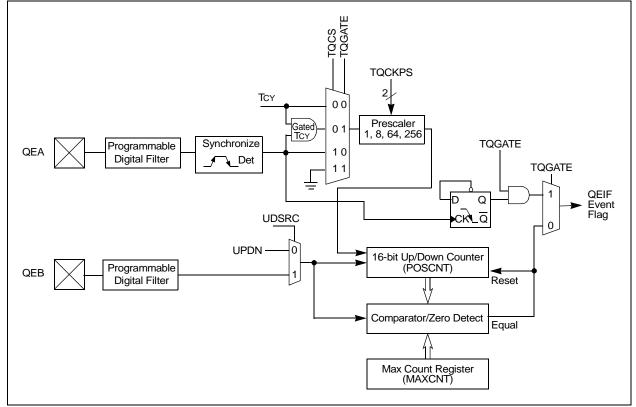

| Programmable Digital Noise Filters             |      |

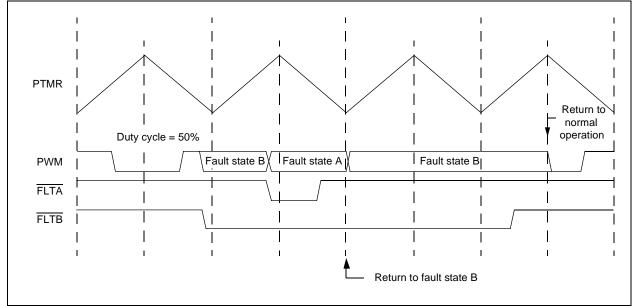

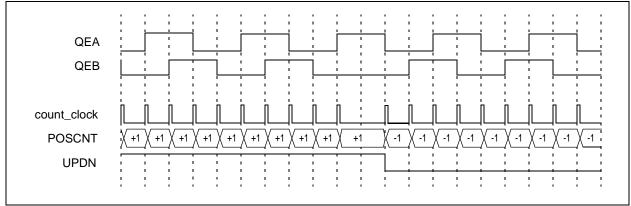

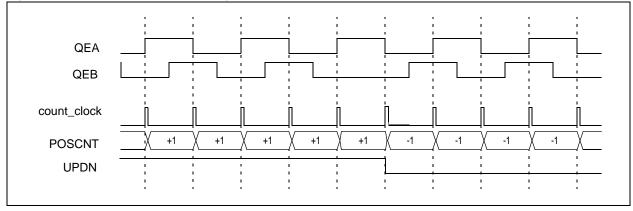

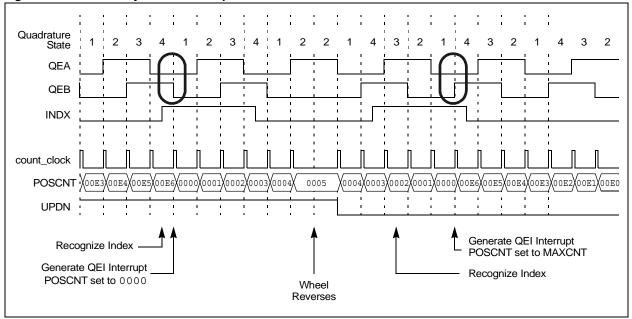

| Quadrature Decoder                             |      |

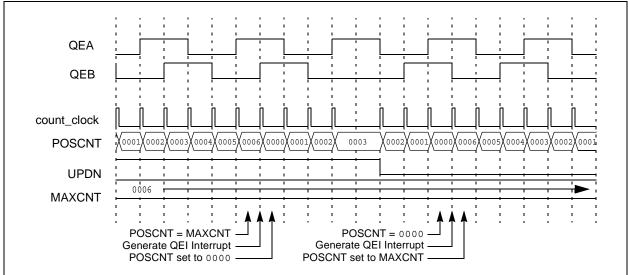

| 16-bit Up/Down Position Counter                |      |

| Using QEI as an Alternate 16-bit Timer/Counter |      |

| Quadrature Encoder Interface Interrupts        |      |

| I/O Pin Control                                |      |

| QEI Operation During Power Saving Modes        |      |

| Effects of a Reset                             |      |

| Design Tips                                    |      |

# <u>PAGE</u>

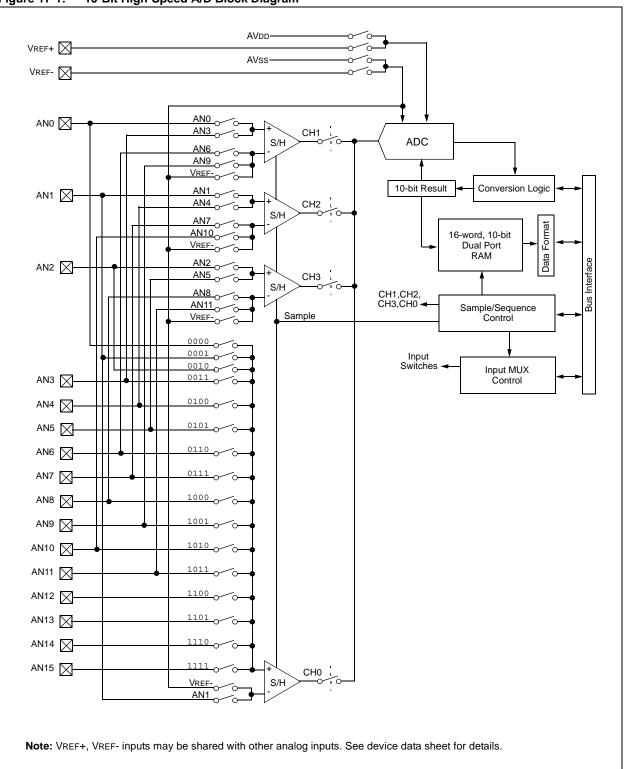

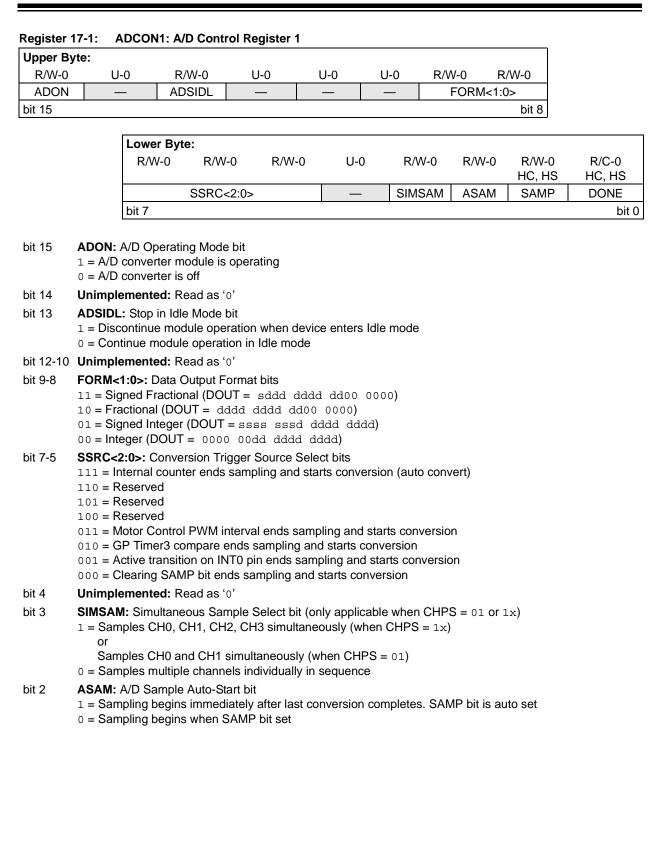

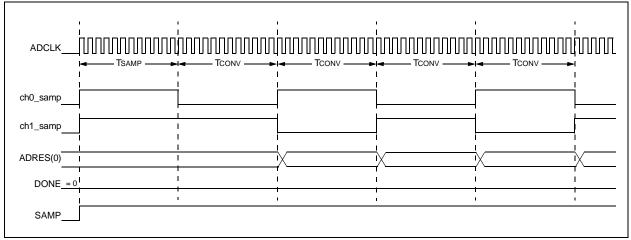

| SECTION 17. 10-BIT A/D CONVERTER                                    | 17-1 |

|---------------------------------------------------------------------|------|

| Introduction                                                        |      |

| Control Registers                                                   |      |

| A/D Result Buffer                                                   |      |

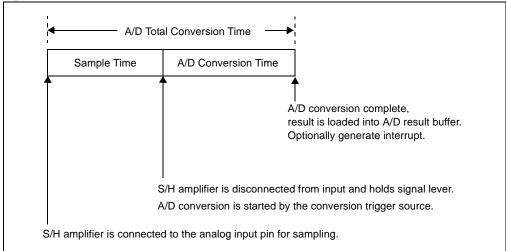

| A/D Terminology and Conversion Sequence                             |      |

| A/D Module Configuration                                            |      |

| Selecting the Voltage Reference Source                              |      |

| Selecting the A/D Conversion Clock                                  |      |

| Selecting Analog Inputs for Sampling                                |      |

| Enabling the Module                                                 |      |

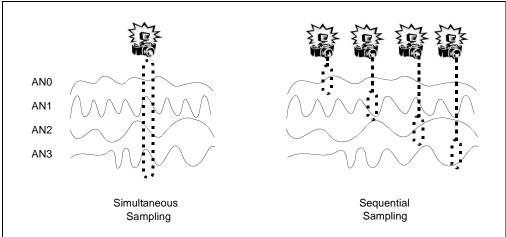

| Specifying the Sample/Conversion Sequence                           |      |

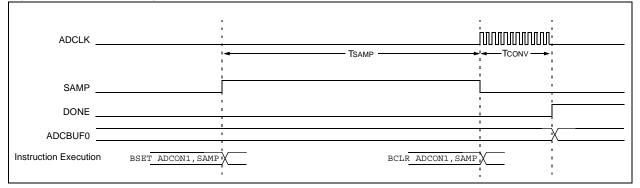

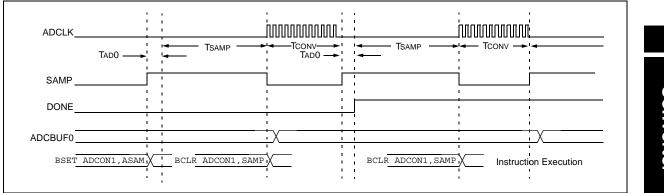

| How to Start Sampling                                               |      |

| How to Stop Sampling and Start Conversions                          |      |

| Controlling Sample/Conversion Operation                             |      |

| Specifying How Conversion Results are Written Into the Buffer       |      |

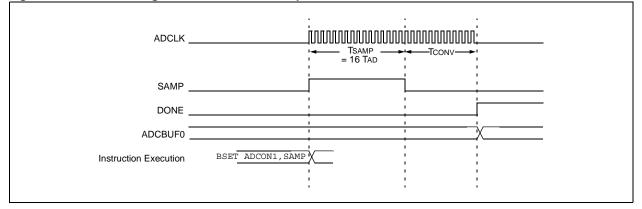

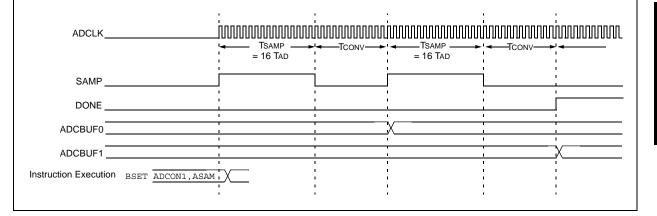

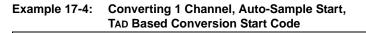

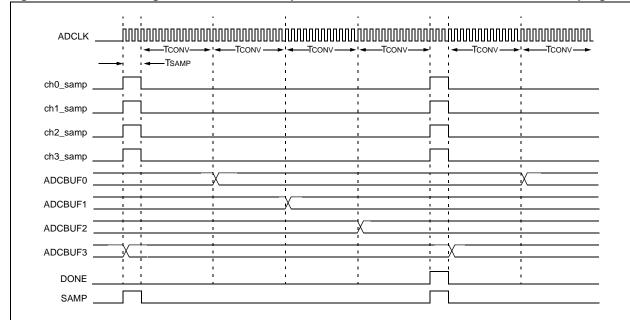

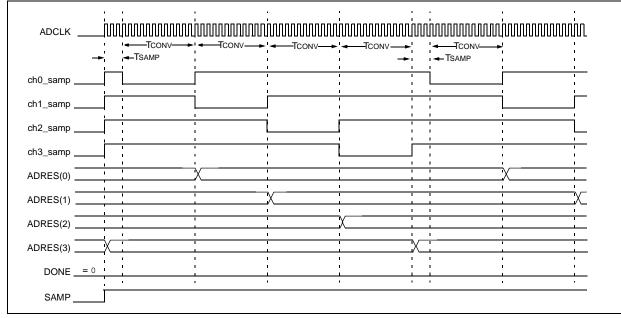

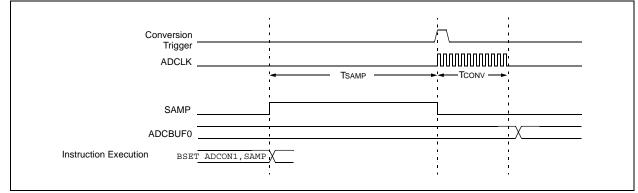

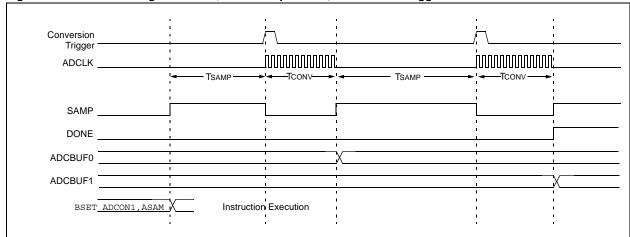

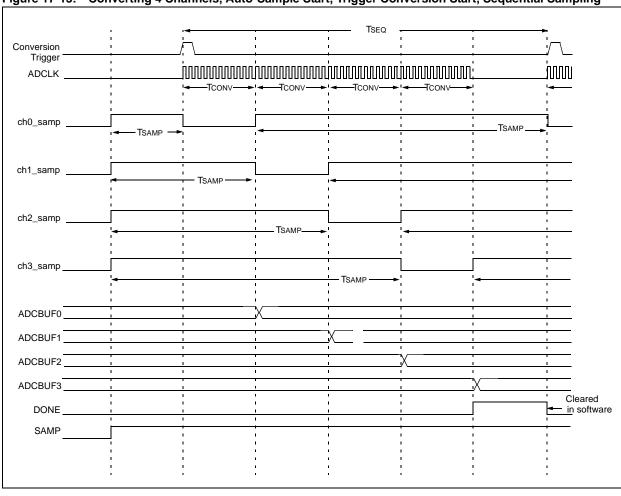

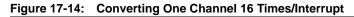

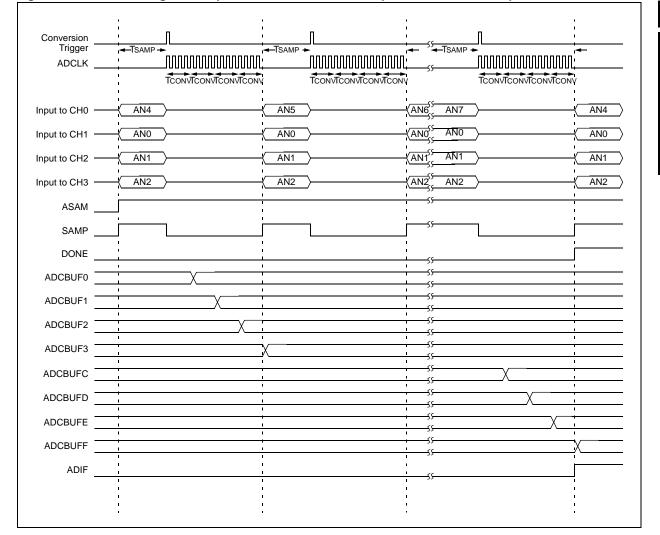

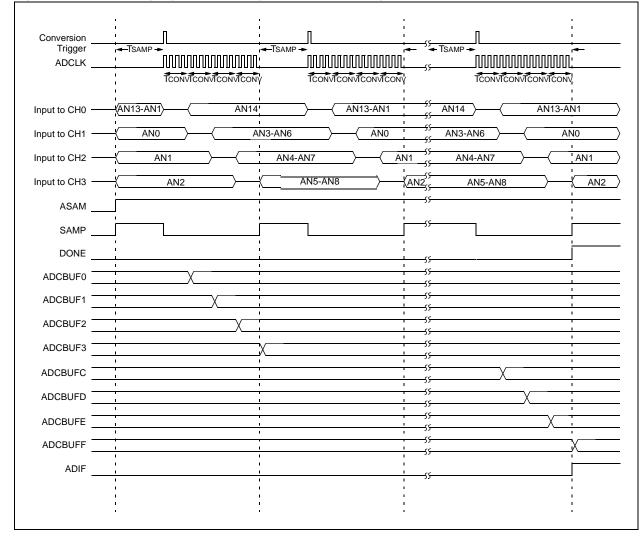

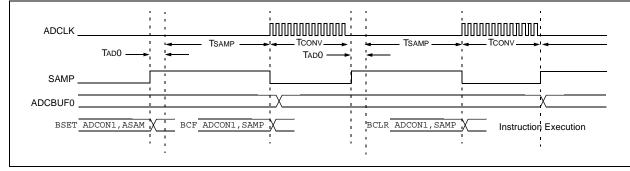

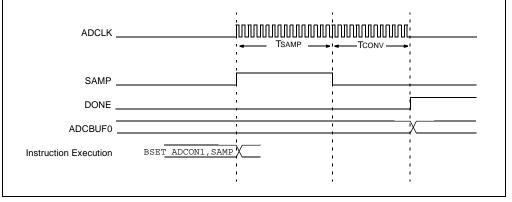

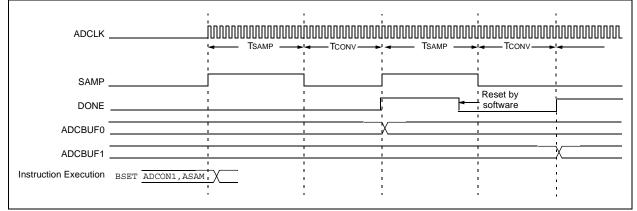

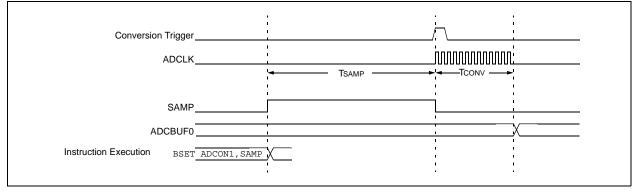

| Conversion Sequence Examples                                        |      |

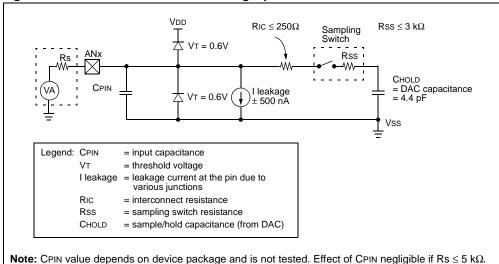

| A/D Sampling Requirements                                           |      |

| Reading the A/D Result Buffer                                       |      |

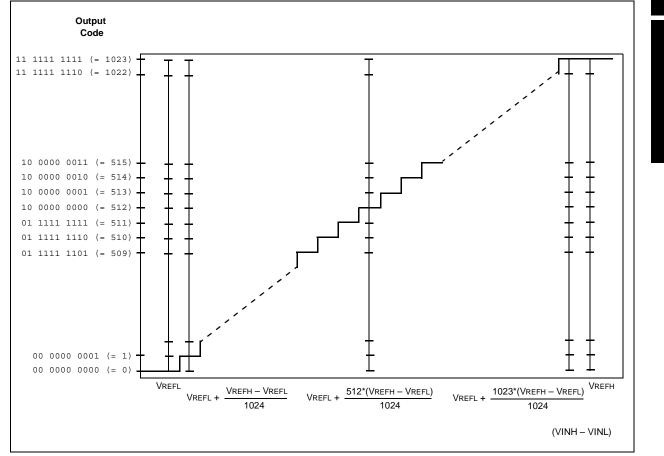

| Transfer Function                                                   |      |

| A/D Accuracy/Error                                                  |      |

| Connection Considerations                                           |      |

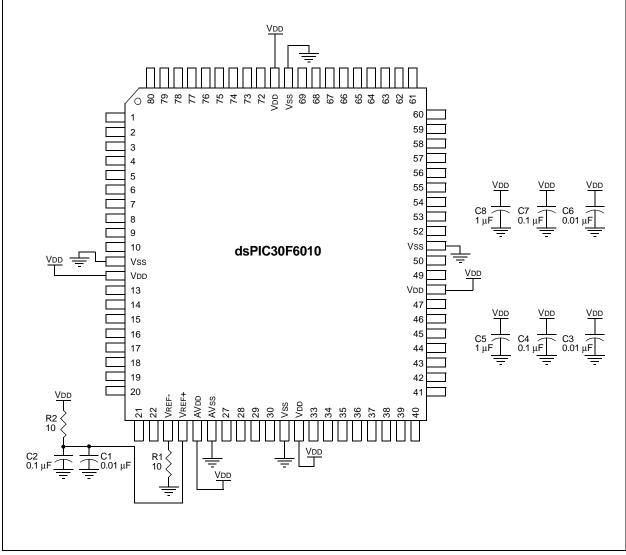

| Initialization                                                      |      |

| A/D Conversion Speeds                                               |      |

| Operation During Sleep and Idle Modes                               |      |

| Effects of a Reset                                                  |      |

| Special Function Registers Associated with the 10-bit A/D Converter |      |

| Design Tips                                                         |      |

| Related Application Notes                                           |      |

| Revision History                                                    |      |

|                                                                     |      |

# PAGE

19-1

|                                                                     | PAGE |

|---------------------------------------------------------------------|------|

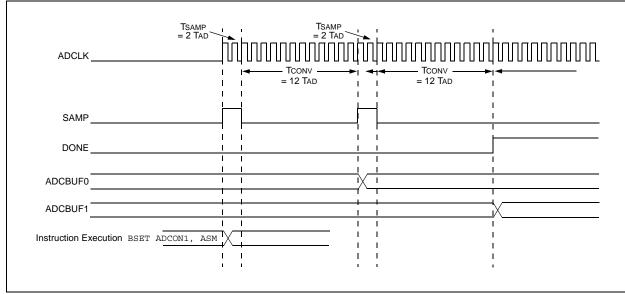

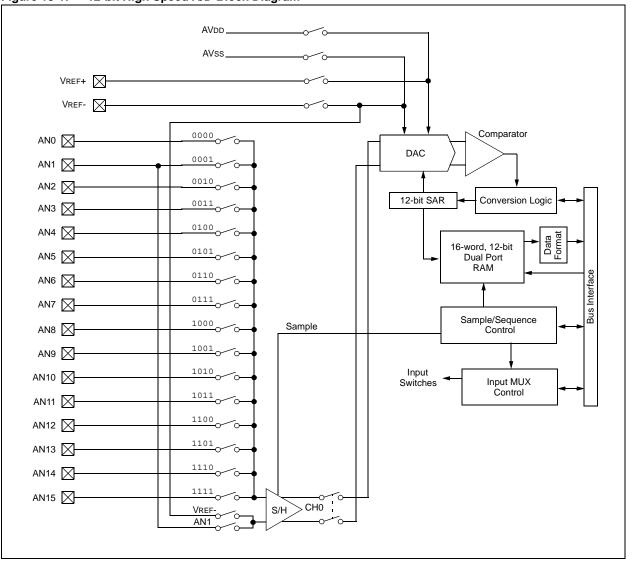

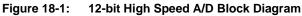

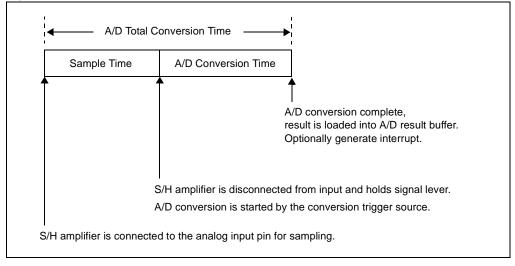

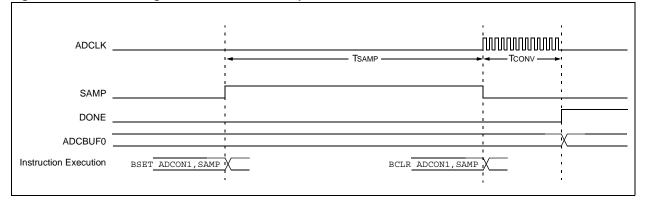

| SECTION 18. 12-BIT A/D CONVERTER                                    | 18-1 |

| Introduction                                                        |      |

| Control Registers                                                   |      |

| A/D Result Buffer                                                   |      |

| A/D Terminology and Conversion Sequence                             |      |

| A/D Module Configuration                                            |      |

| Selecting the Voltage Reference Source                              |      |

| Selecting the A/D Conversion Clock                                  |      |

| Selecting Analog Inputs for Sampling                                |      |

| Enabling the Module                                                 |      |

| How to Start Sampling                                               |      |

| How to Stop Sampling and Start Conversions                          |      |

| Controlling Sample/Conversion Operation                             |      |

| Specifying How Conversion Results are Written into the Buffer       |      |

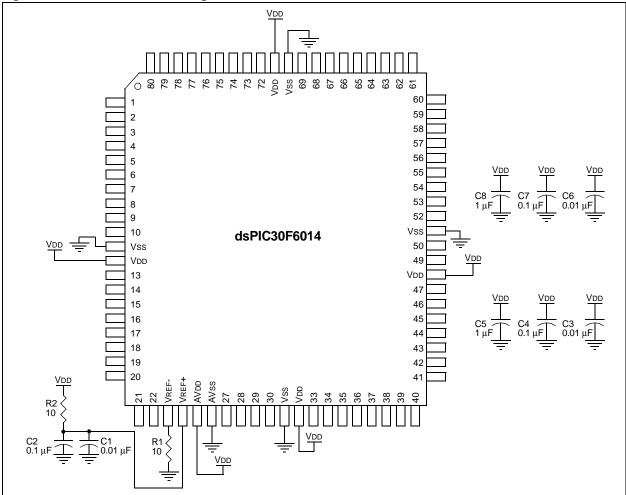

| Conversion Sequence Examples                                        |      |

| A/D Sampling Requirements                                           |      |

| Reading the A/D Result Buffer                                       |      |

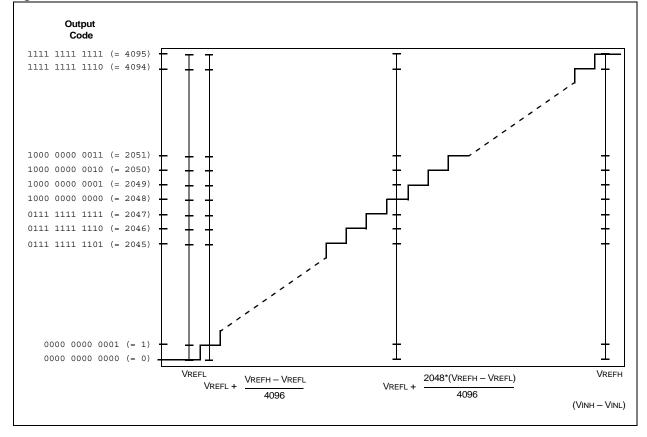

| Transfer Function                                                   |      |

| A/D Accuracy/Error                                                  |      |

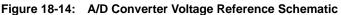

| Connection Considerations                                           |      |

| Initialization                                                      |      |

| A/D Conversion Speeds                                               |      |

| Operation During Sleep and Idle Modes                               |      |

| Effects of a Reset                                                  |      |

| Special Function Registers Associated with the 12-bit A/D Converter |      |

| Design Tips                                                         |      |

| Related Application Notes                                           |      |

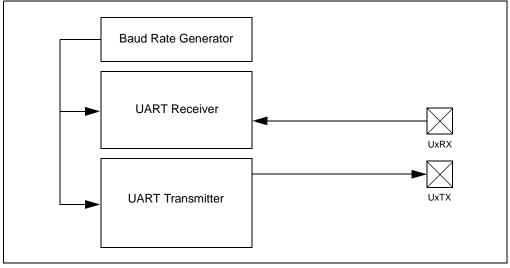

# **SECTION 19. UART**

| Introduction                                   |  |

|------------------------------------------------|--|

| Control Registers                              |  |

| UART Baud Rate Generator (BRG)                 |  |

| UART Configuration                             |  |

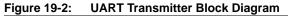

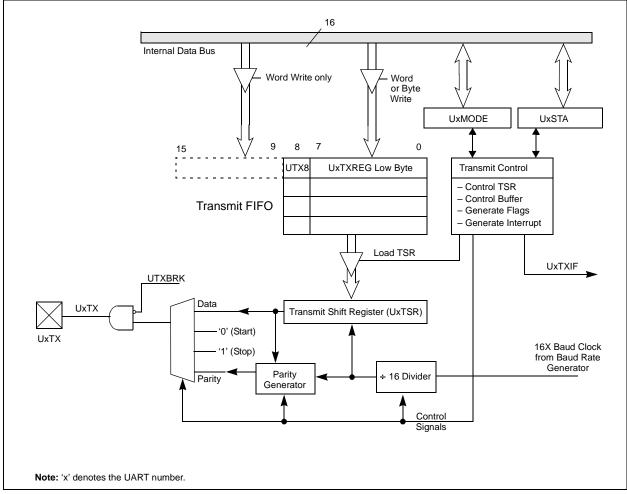

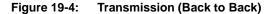

| UART Transmitter                               |  |

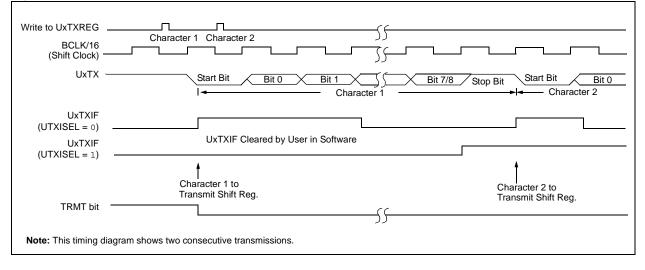

| UART Receiver                                  |  |

| Using the UART for 9-bit Communication         |  |

| Receiving Break Characters                     |  |

| Initialization                                 |  |

| Other Features of the UART                     |  |

| UART Operation During CPU Sleep and Idle Modes |  |

| Registers Associated with UART Module          |  |

| Design Tips                                    |  |

| Related Application Notes                      |  |

| Revision History                               |  |

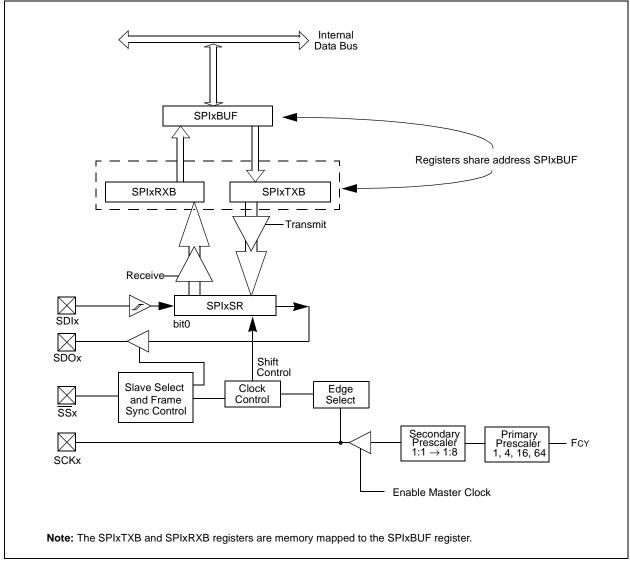

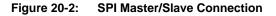

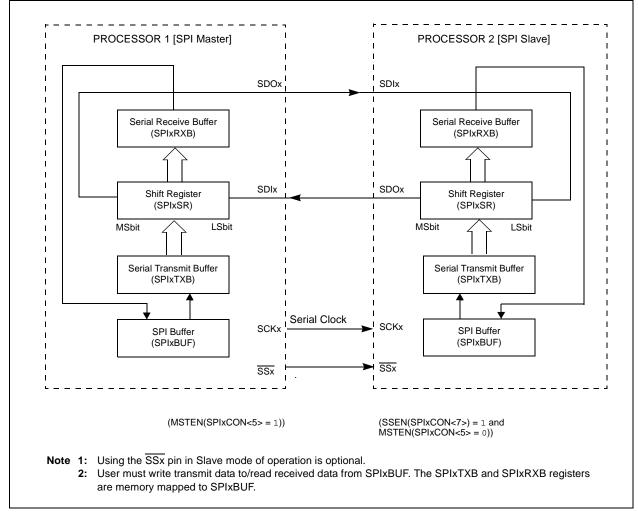

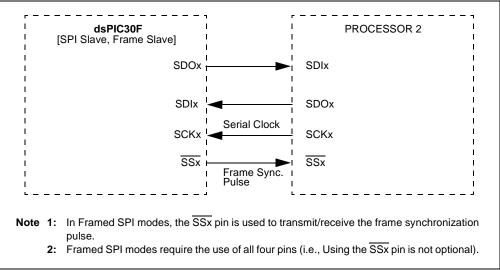

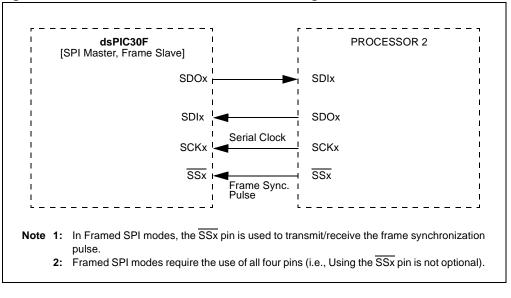

| SECTION 20. SERIAL PERIPHERAL INTERFACE (SPI™)            | 20-1 |

|-----------------------------------------------------------|------|

| Introduction                                              |      |

| Status and Control Registers                              |      |

| Modes of Operation                                        |      |

| SPI Master Mode Clock Frequency                           |      |

| Operation in Power Save Modes                             |      |

| Special Function Registers Associated with SPI Modules    |      |

| Related Application Notes                                 |      |

| Revision History                                          |      |

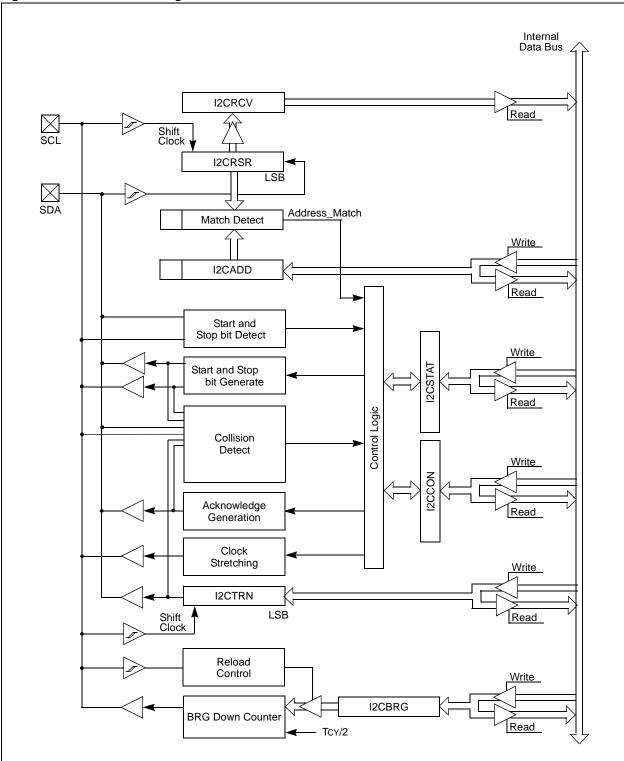

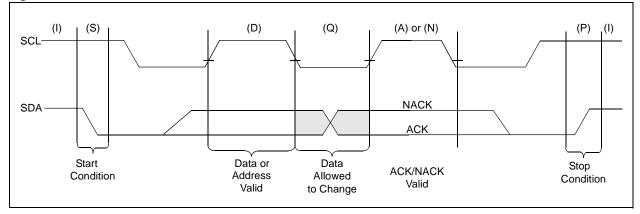

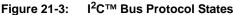

| SECTION 21. INTER-INTEGRATED CIRCUIT™ (I <sup>2</sup> C™) | 21-1 |

| Overview                                                  |      |

| I <sup>2</sup> C Bus Characteristics                      |      |

| Control and Status Registers                              |      |

| Enabling I <sup>2</sup> C Operation                       |      |

| Communicating as a Master in a Single Master Environment  |      |

| Communicating as a Master in a Multi-Master Environment   |      |

| Communicating as a Slave                                  |      |

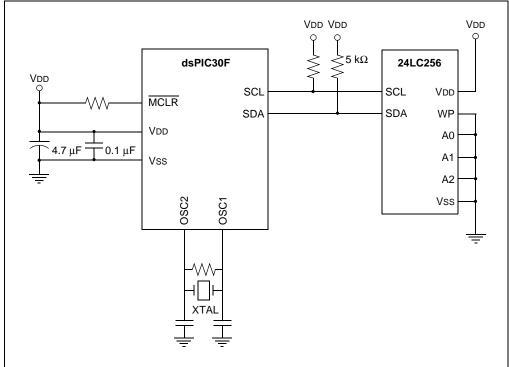

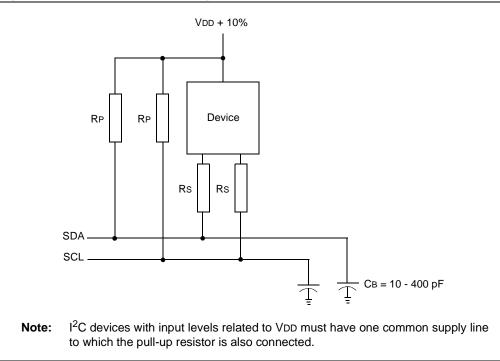

| Connection Considerations for I <sup>2</sup> C Bus        |      |

| Module Operation During PWRSAV Instruction                |      |

| Effects of a Reset                                        |      |

| Design Tips                                               |      |

| Related Application Notes                                 |      |

| Revision History                                          |      |

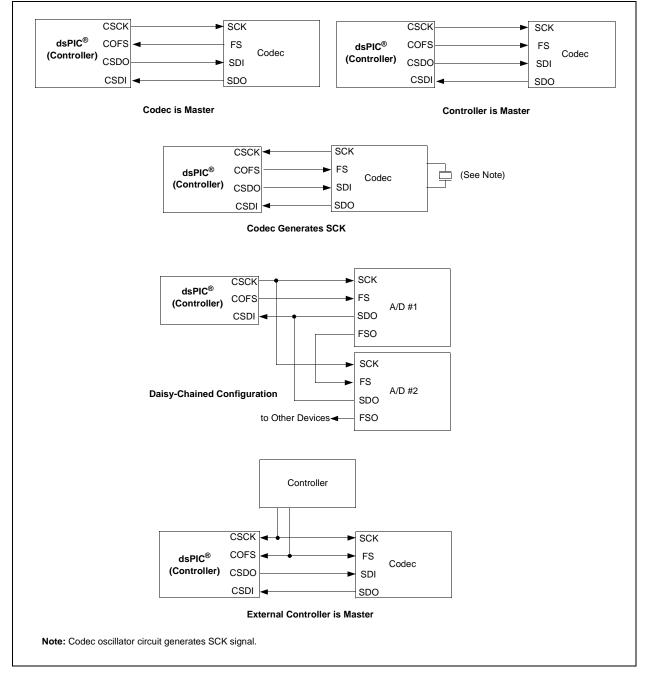

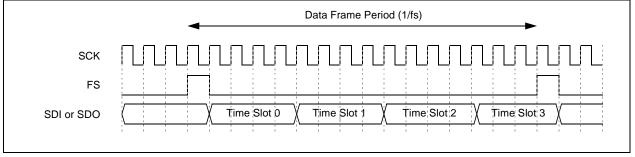

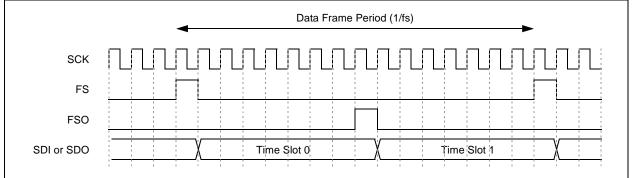

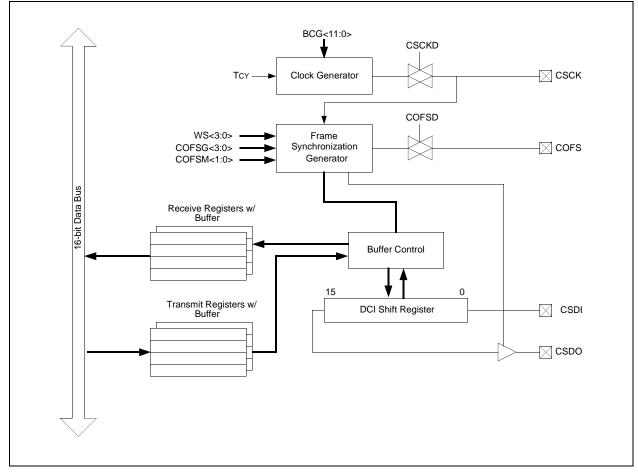

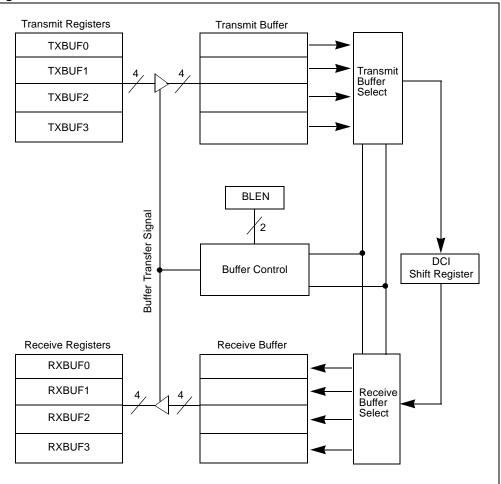

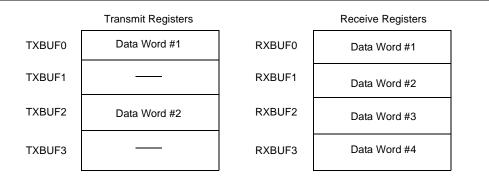

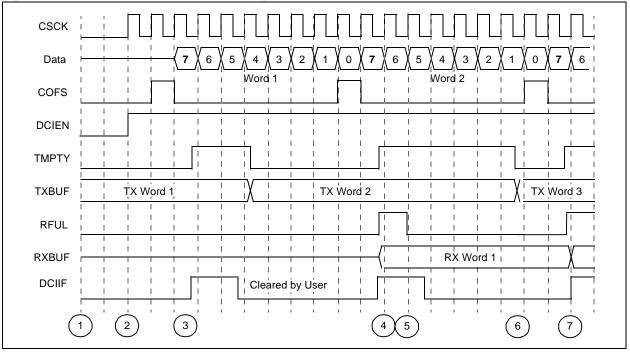

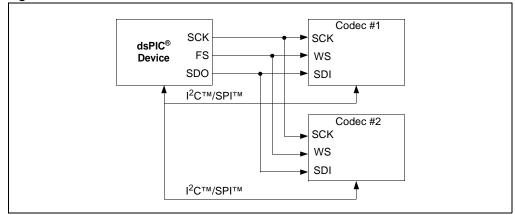

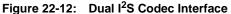

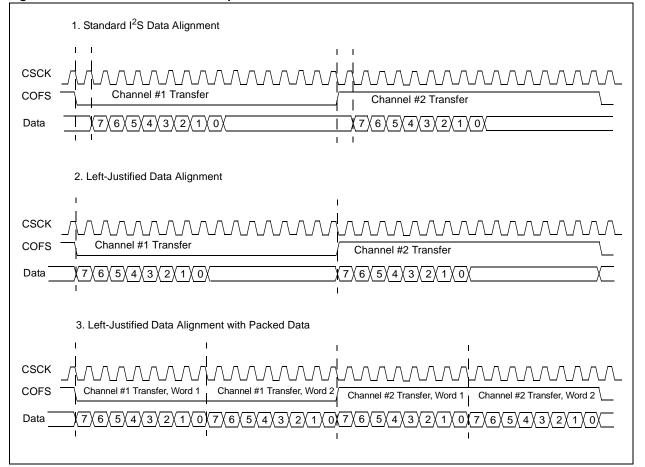

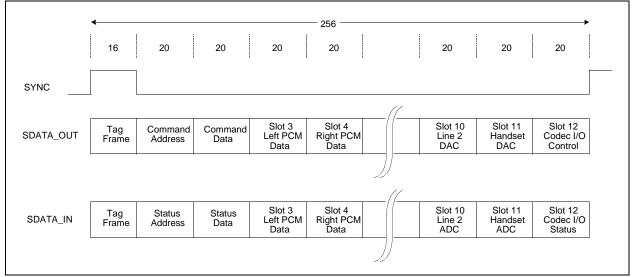

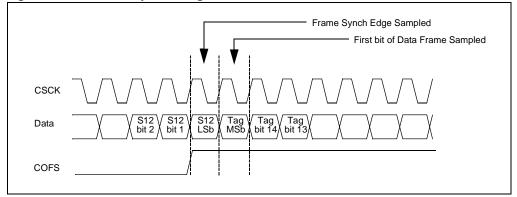

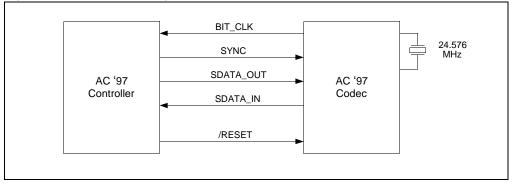

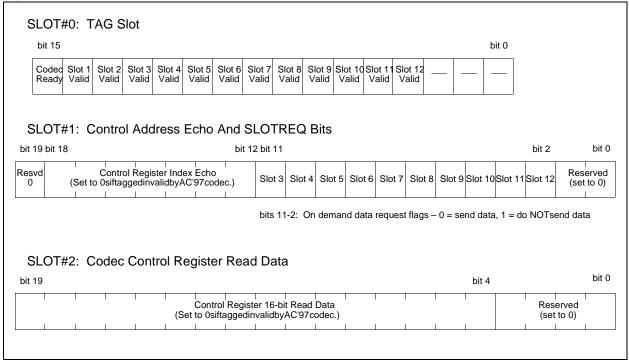

| SECTION 22. DATA CONVERTER INTERFACE (DCI)                | 22-1 |

| Introduction                                              |      |

| Control Register Descriptions                             |      |

| Codec Interface Basics and Terminology                    |      |

| DCI Operation                                             |      |

| Using the DCI Module                                      |      |

| Operation in Power Saving Modes                           |      |

| Registers Associated with DCI                             |      |

| Design Tips                                               |      |

| Related Application Notes                                 |      |

| Revision History                                          |      |

# <u>PAGE</u>

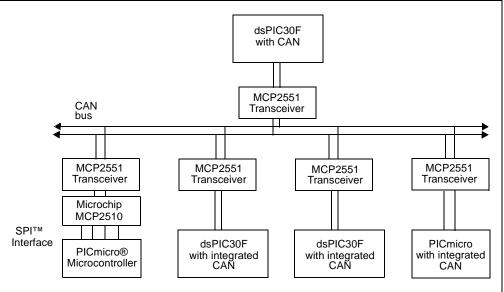

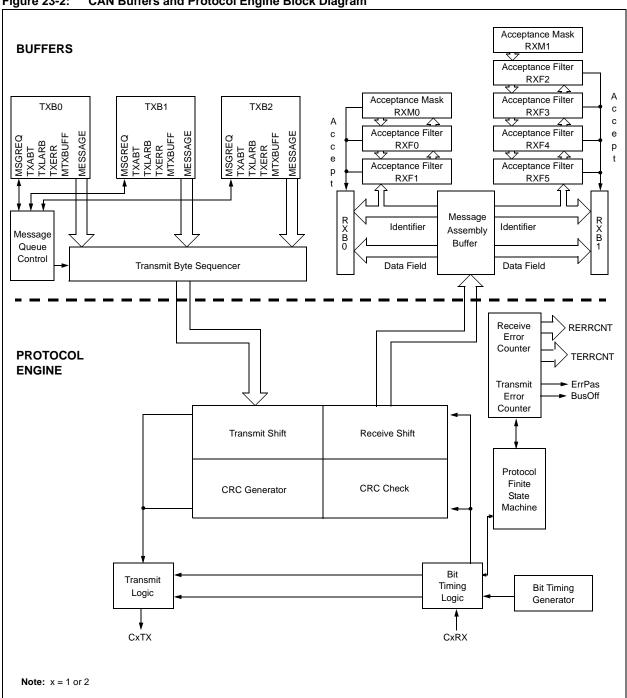

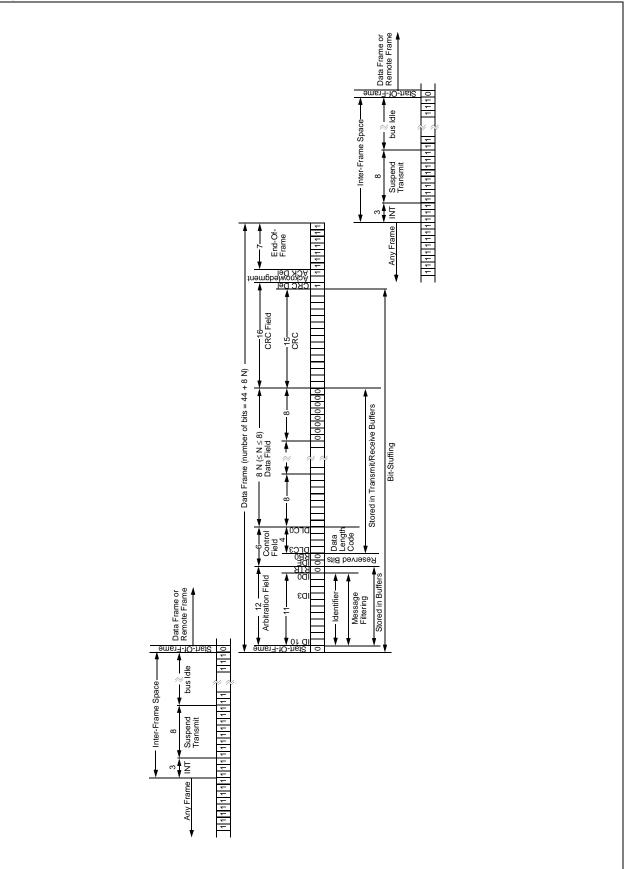

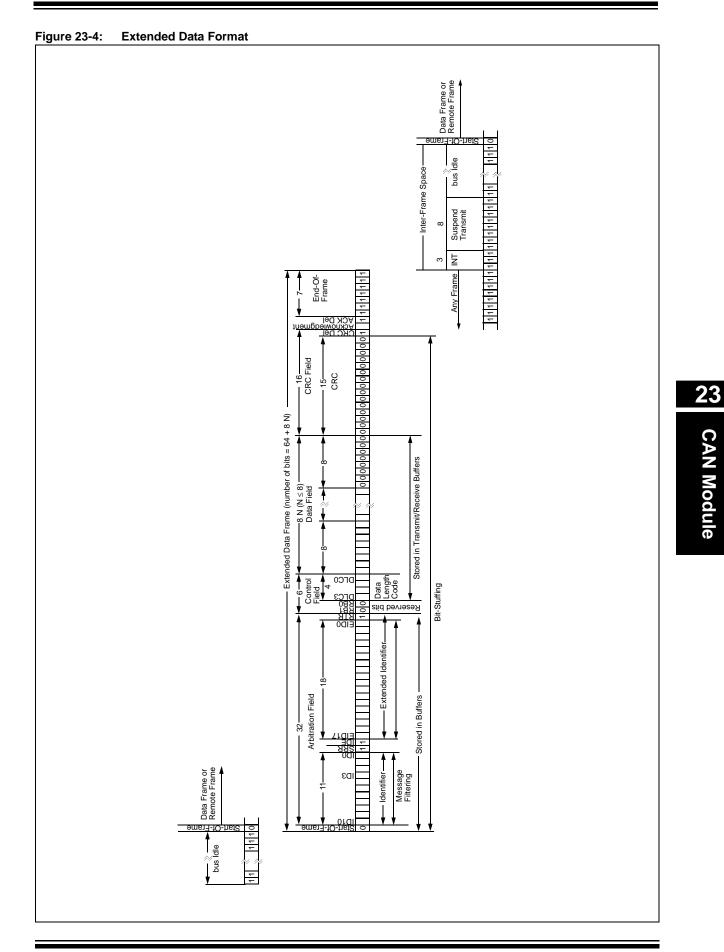

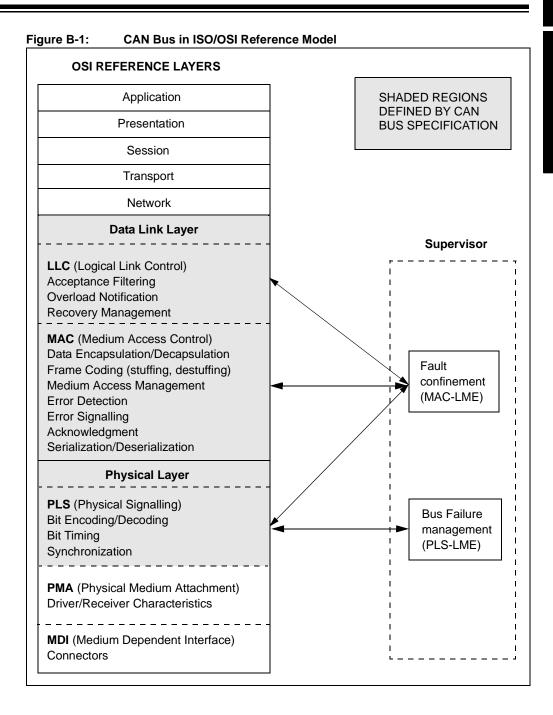

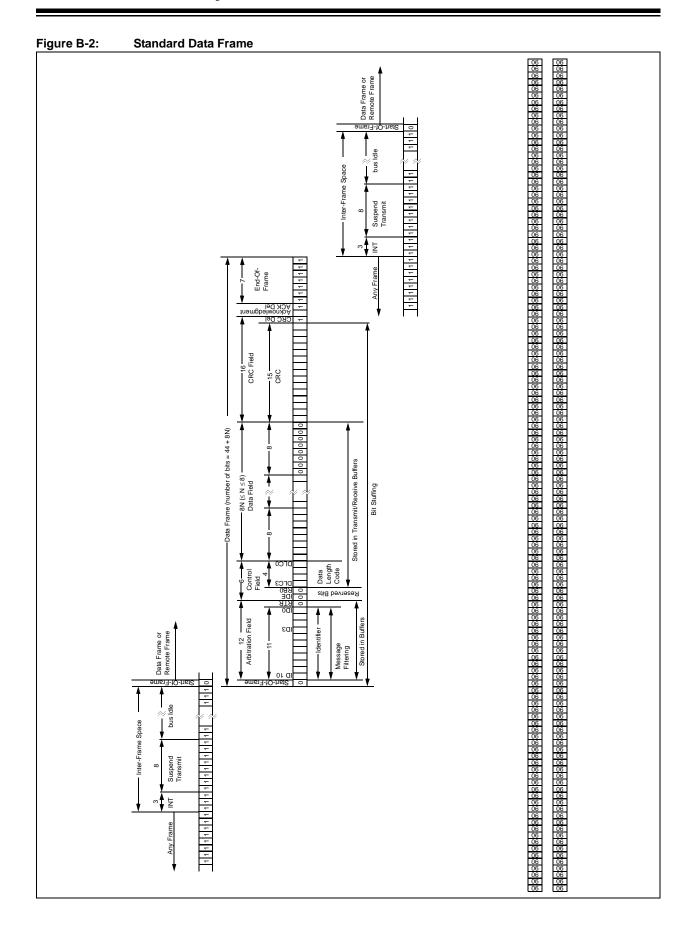

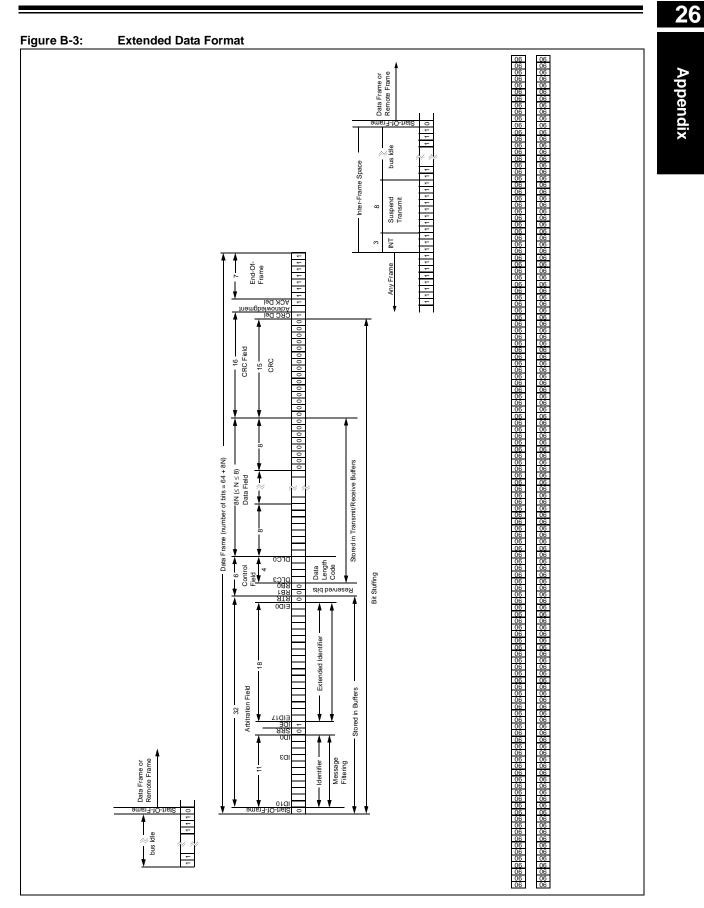

| SECTION 23. CAN MODULE                                            | 23-1 |

|-------------------------------------------------------------------|------|

| Introduction                                                      |      |

| Control Registers for the CAN Module                              |      |

| CAN Module Features                                               |      |

| CAN Module Implementation                                         |      |

| CAN Module Operation Modes                                        |      |

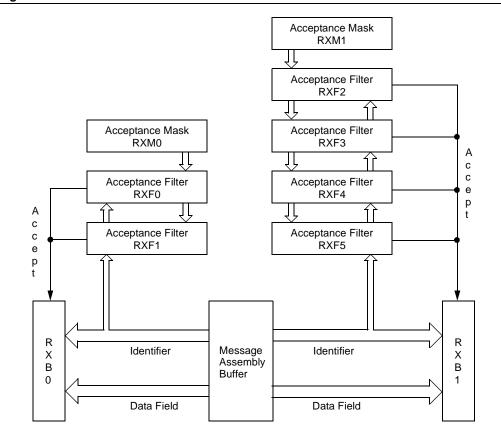

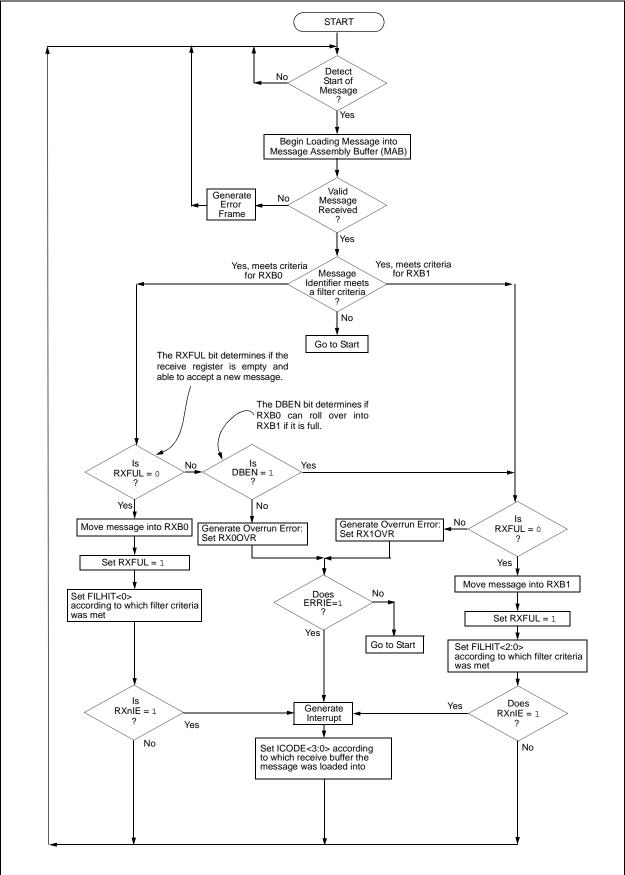

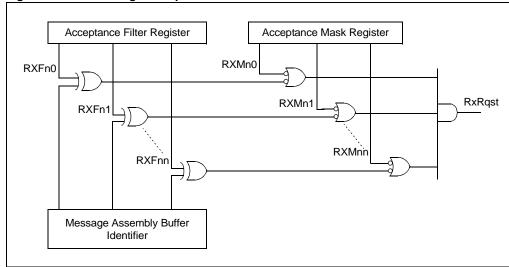

| Message Reception                                                 |      |

| Transmission                                                      |      |

| Error Detection                                                   |      |

| CAN Baud Rate                                                     |      |

| Interrupts                                                        |      |

| CAN Capture                                                       |      |

| CAN Module I/O                                                    |      |

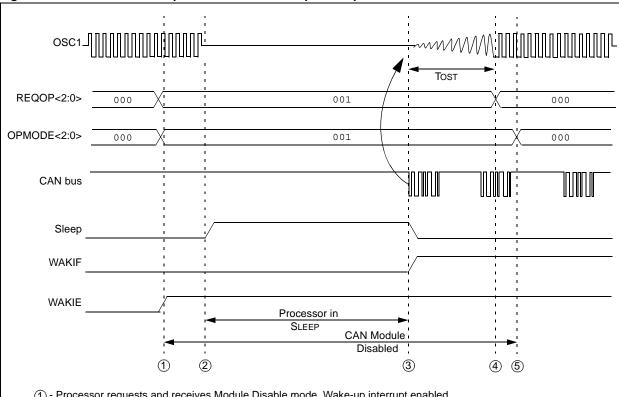

| Operation in CPU Power Saving Modes                               |      |

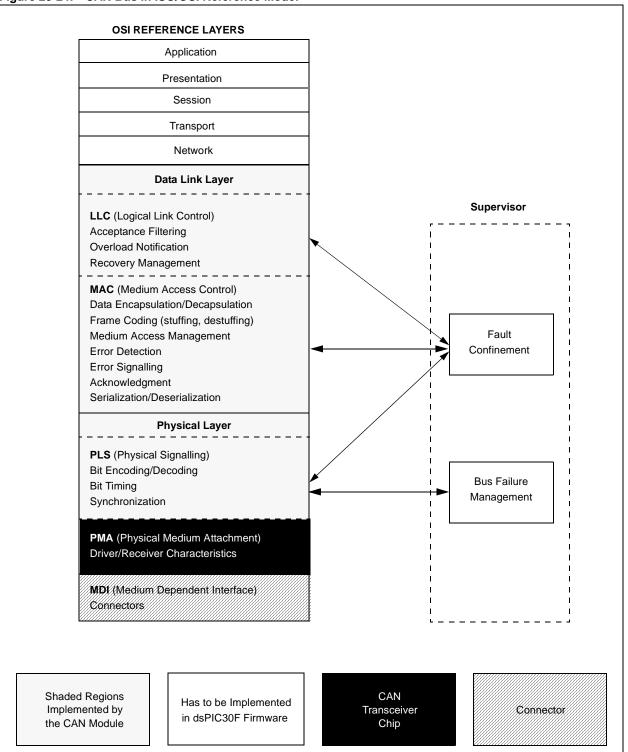

| CAN Protocol Overview                                             |      |

| Related Application Notes                                         |      |

| Revision History                                                  |      |

| SECTION 24. DEVICE CONFIGURATION                                  | 24-1 |

| Introduction                                                      | 24-2 |

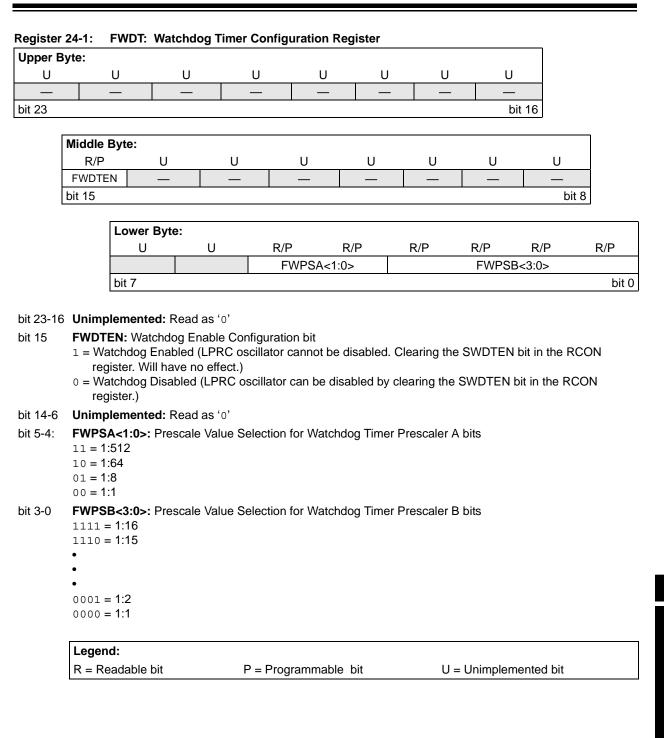

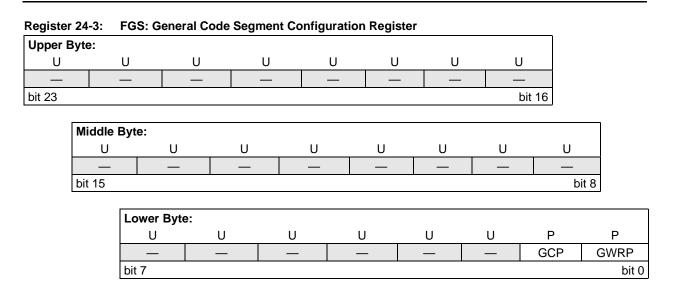

| Device Configuration Registers                                    |      |

| Configuration Bit Descriptions                                    |      |

| Device Identification Registers                                   |      |

| Related Application Notes                                         |      |

| Revision History                                                  |      |

| SECTION 25. DEVELOPMENT TOOL SUPPORT                              | 25-1 |

|                                                                   |      |

|                                                                   |      |

| Microchip Hardware and Language Tools                             |      |

| Third Party Hardware/Software Tools and Application Libraries     |      |

| dsPIC30F Hardware Development Boards<br>Related Application Notes |      |

|                                                                   |      |

| Revision History                                                  |      |

| SECTION 26. APPENDIX                                              | 26-1 |

NOTES:

<u>PAGE</u>

# Section 1. Introduction

# HIGHLIGHTS

This section of the manual contains the following topics:

| 1.1 | Introduction                 | . 1-2 |

|-----|------------------------------|-------|

| 1.2 | Manual Objective             | . 1-2 |

| 1.3 | Device Structure             | . 1-3 |

| 1.4 | Development Support          | . 1-4 |

| 1.5 | Style and Symbol Conventions | . 1-4 |

| 1.6 | Related Documents            | . 1-6 |

| 1.7 | Revision History             | . 1-7 |

# 1.1 Introduction

Microchip is a leading provider of microcontrollers and analog semiconductors. The company's focus is on products that meet the needs of the embedded control market. We are a leading supplier of:

- 8-bit general purpose microcontrollers (PICmicro<sup>®</sup> MCUs)

- dsPIC30F 16-bit microcontrollers

- · Speciality and standard non-volatile memory devices

- Security devices (KEELOQ<sup>®</sup>)

- Application specific standard products

Please request a Microchip Product Line Card for a listing of all the interesting products that we have to offer. This literature can be obtained from your local sales office, or downloaded from the Microchip web site (www.microchip.com).

# 1.2 Manual Objective

PICmicro and dsPIC30F devices are grouped by the size of their Instruction Word and Data Path. The current device families are:

- 1. Base-Line: 12-bit Instruction Word length, 8-bit Data Path

- 2. Mid-Range: 14-bit Instruction Word length, 8-bit Data Path

- 3. High-End: 16-bit Instruction Word length, 8-bit Data Path

- 4. Enhanced: 16-bit Instruction Word length, 8-bit Data Path

- 5. dsPIC30F: 24-bit Instruction Word length, 16-bit Data Path

This manual describes the dsPIC30F 16-bit MCU family of devices.

This manual explains the operation of the dsPIC30F MCU family architecture and peripheral modules, but does not cover the specifics of each device. The user should refer to the data sheet for device specific information. The information that can be found in the data sheet includes:

- Device memory map

- · Device pinout and packaging details

- Device electrical specifications

- List of peripherals included on the device

Code examples are given throughout this manual. These examples sometimes need to be written as device specific as opposed to family generic, though they are valid for most other devices. Some modifications may be required for devices with variations in register file mappings.

# 1.3 Device Structure

Each part of the dsPIC30F device can be placed into one of three groups:

- 1. CPU Core

- 2. System Integration

- 3. Peripherals

# 1.3.1 CPU Core

The CPU core pertains to the basic features that are required to make the device operate. The sections of the manual related to the CPU core include:

- 1. CPU

- 2. Data Memory

- 3. Program Memory

- 4. DSP Engine

- 5. Interrupts

# 1.3.2 System Integration

System integration functions help to:

- Decrease system cost

- Increase system reliability

- Increase design flexibility

The following sections of the manual discuss dsPIC30F system integration functions:

- 1. Oscillator

- 2. Reset

- 3. Low Voltage Detect

- 4. Watchdog Timer and Power Saving Modes

- 5. Flash and EEPROM Programming

- 6. Device Configuration

# 1.3.3 Peripherals

The dsPIC30F has many peripherals that allow the device to be interfaced to the external world. The peripherals discussed in this manual include:

- 1. I/O Ports

- 2. Timers

- 3. Input Capture Module

- 4. Output Compare Module

- 5. Quadrature Encoder Interface (QEI)

- 6. 10-bit A/D Converter

- 7. 12-bit A/D Converter

- 8. UART Module

- 9. SPI<sup>™</sup> Module

- 10. I<sup>2</sup>C<sup>™</sup> Module

- 11. Data Converter Interface (DCI) Module

- 12. CAN Module

# 1.3.4 Memory Technology

At the time of this writing, all dsPIC30F devices use Flash program memory technology. The Flash program memory can be electrically erased or programmed.

# 1.4 Development Support

Microchip offers a wide range of development tools that allow users to efficiently develop and debug application code. Microchip's development tools can be broken down into four categories:

- 1. Code generation

- 2. Hardware/Software debug

- 3. Device programmer

- 4. Product evaluation boards

A full description of each of Microchip's development tools is discussed in **Section 25.** "**Development Tool Support**". As new tools are developed, the latest product briefs and user guides can be obtained from the Microchip web site (www.microchip.com) or from your local Microchip Sales Office.

Microchip offers other reference tools to speed the development cycle. These include:

- Application Notes

- Reference Designs

- · Microchip web site

- · Local Sales Offices with Field Application Support

- Corporate Support Line

The Microchip web site lists other sites that may be useful references.

### 1.5 Style and Symbol Conventions

Throughout this document, certain style and font format conventions are used. Most format conventions imply a distinction should be made for the emphasized text. The MCU industry has many symbols and non-conventional word definitions/abbreviations. Table 1-1 provides a description for many of the conventions contained in this document. Located at the rear of this document, a glossary provides additional word and abbreviation definitions used throughout this manual.

# 1.5.1 Document Conventions

Table 1-1 defines some of the symbols and terms used throughout this manual.

Table 1-1:Document Conventions

| Table 1-1:         Document Conventions |                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol or Term                          | Description                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| set                                     | To force a bit/register to a value of logic '1'.                                                                                                                                                                                                                                                                                |  |  |  |  |

| clear                                   | To force a bit/register to a value of logic '0'.                                                                                                                                                                                                                                                                                |  |  |  |  |

| Reset                                   | <ol> <li>To force a register/bit to its default state.</li> <li>A condition in which the device places itself after a device Reset<br/>occurs. Some bits will be forced to '0' (such as interrupt enable bits),<br/>while others will be forced to '1' (such as the I/O data direction bits).</li> </ol>                        |  |  |  |  |

| 0xnn <b>or</b> nnh                      | Designates the number 'nn' in the hexadecimal number system. These conventions are used in the code examples. For example, 0x13F or 13Fh.                                                                                                                                                                                       |  |  |  |  |

| B'bbbbbbb'                              | Designates the number 'bbbbbbbb' in the binary number system. This convention is used in the text and in figures and tables. For example, B'10100000'.                                                                                                                                                                          |  |  |  |  |

| R-M-W                                   | Read-Modify-Write. This is when a register or port is read, then the value is modified, and that value is then written back to the register or port. This action can occur from a single instruction (such as bit set, BSET), or a sequence of instructions.                                                                    |  |  |  |  |

| : (colon)                               | Used to specify a range or the concatenation of registers/bits/pins.<br>One example is TMR3:TMR2, which is the concatenation of two 16-bit<br>registers to form a 32-bit timer value.<br>Concatenation order (left-right) usually specifies a positional relationship<br>(MSb to LSb, higher to lower).                         |  |  |  |  |

| <>                                      | Specifies bit(s) locations in a particular register.<br>One example is PTCON <ptmod1:ptmod0> (or PTMOD&lt;1:0&gt;), which<br/>specifies the register and associated bits or bit positions.</ptmod1:ptmod0>                                                                                                                      |  |  |  |  |

| MSb, MSbit, LSb,<br>LSbit               | Indicates the Least Significant or Most Significant bit in a field.                                                                                                                                                                                                                                                             |  |  |  |  |

| MSByte, MSWord,<br>LSByte, LSWord       | Indicates the Least/Most Significant Byte or Word in a field of bits.                                                                                                                                                                                                                                                           |  |  |  |  |

| Courier Font                            | Used for code examples, binary numbers and for instruction mnemonics in the text.                                                                                                                                                                                                                                               |  |  |  |  |

| Times Font                              | Used for equations and variables.                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Times, Bold Font,<br>Italics            | Used in explanatory text for items called out from a graphic/<br>equation/example.                                                                                                                                                                                                                                              |  |  |  |  |

| Note                                    | A Note presents information that we wish to re-emphasize, either to help<br>you avoid a common pitfall, or make you aware of operating differences<br>between some device family members. A Note is always in a shaded box<br>(as below), unless used in a table, where it is at the bottom of the table<br>(as in this table). |  |  |  |  |

|                                         | <b>Note:</b> This is a Note in a shaded note box.                                                                                                                                                                                                                                                                               |  |  |  |  |

# 1.5.2 Electrical Specifications

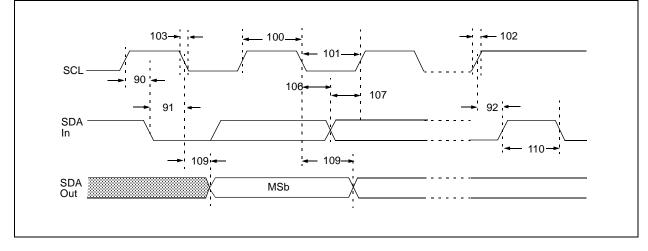

Throughout this manual, there will be references to electrical specifications and their parameter numbers. Table 1-2 shows the parameter numbering convention for dsPIC30F devices. A parameter number represents a unique set of characteristics and conditions that is consistent between every data sheet, though the actual parameter value may vary from device to device. This manual describes a family of devices and therefore, does not specify the parameter values. The user should refer to the "Electrical Specifications" section of the device data sheet for the actual parameter values for that device.

| Parameter Number Format | Comment                                      |

|-------------------------|----------------------------------------------|

| DXXX                    | DC Specification                             |

| AXXX                    | DC Specification for Analog Peripherals      |

| XXX                     | Timing (AC) Specification                    |

| PDXXX                   | Device Programming DC Specification          |

| PXXX                    | Device Programming Timing (AC) Specification |

Table 1-2:

Electrical Specification Parameter Numbering Convention

Legend: XXX represents a number.

### 1.6 Related Documents

Microchip, as well as other sources, offers additional documentation which can aid in your development with dsPIC30F MCUs. These lists contain the most common documentation, but other documents may also be available. Please check the Microchip web site (www.microchip.com) for the latest published technical documentation.

### 1.6.1 Microchip Documentation

The following dsPIC30F documentation is available from Microchip at the time of this writing. Many of these documents provide application specific information that gives actual examples of using, programming and designing with dsPIC30F MCUs.

1. dsPIC30F Programmer's Reference Manual (DS70030)

The dsPIC30F Programmer's Reference Manual provides information about the dsPIC30F programmer's model and instruction set. A description of each instruction and syntax examples are provided in this document.

2. dsPIC30F Family Overview (DS70043)

This document provides a summary of the available dsPIC30F family variants, including device pinouts, memory sizes and available peripherals.

3. dsPIC30F Data Sheets (DS70082 and DS70083)

The data sheets contain device specific information, such as pinout and packaging details, electrical specifications and memory maps.

# 1.6.2 Third Party Documentation

There are several documents available from third party sources around the world. Microchip does not review these documents for technical accuracy. However, they may be a helpful source for understanding the operation of Microchip dsPIC30F devices. Please refer to the Microchip web site for third party documentation related to the dsPIC30F.

# 1.7 Revision History

# **Revision A**

This is the initial released revision of this document.

# **Revision B**

There were no technical content or editorial revisions to this section of the manual, however, this section was updated to reflect Revision B throughout the manual.

# **Revision C**

There were no technical content revisions to this section of the manual, however, this section was updated to reflect Revision C throughout the manual.

NOTES:

# Section 2. CPU

# HIGHLIGHTS

This section of the manual contains the following topics:

| 2.1  | Introduction                  | 2-2  |

|------|-------------------------------|------|

| 2.2  | Programmer's Model            | 2-4  |

| 2.3  | Software Stack Pointer        | 2-8  |

| 2.4  | CPU Register Descriptions     | 2-11 |

| 2.5  | Arithmetic Logic Unit (ALU)   | 2-17 |

| 2.6  | DSP Engine                    | 2-18 |

| 2.7  | Divide Support                | 2-27 |

| 2.8  | Instruction Flow Types        | 2-27 |

| 2.9  | Loop Constructs               | 2-30 |

| 2.10 | Address Register Dependencies | 2-35 |

| 2.11 | Register Maps                 |      |

| 2.12 | Related Application Notes     |      |

| 2.13 | Revision History              | 2-41 |

### 2.1 Introduction

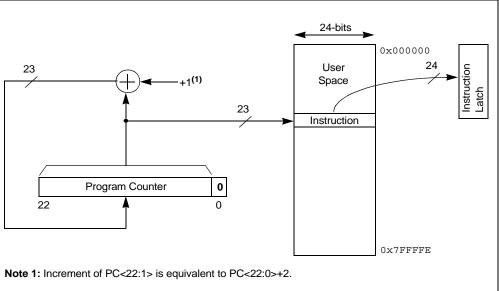

The dsPIC30F CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word, with a variable length opcode field. The program counter (PC) is 24-bits wide and addresses up to 4M x 24 bits of user program memory space. A single cycle instruction pre-fetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC30F devices have sixteen 16-bit working registers in the programmer's model. Each of the working registers can act as a data, address, or address offset register. The 16th working register (W15) operates as a software stack pointer for interrupts and calls.

The dsPIC30F instruction set has two classes of instructions: the MCU class of instructions and the DSP class of instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many Addressing modes and was designed for optimum C compiler efficiency.

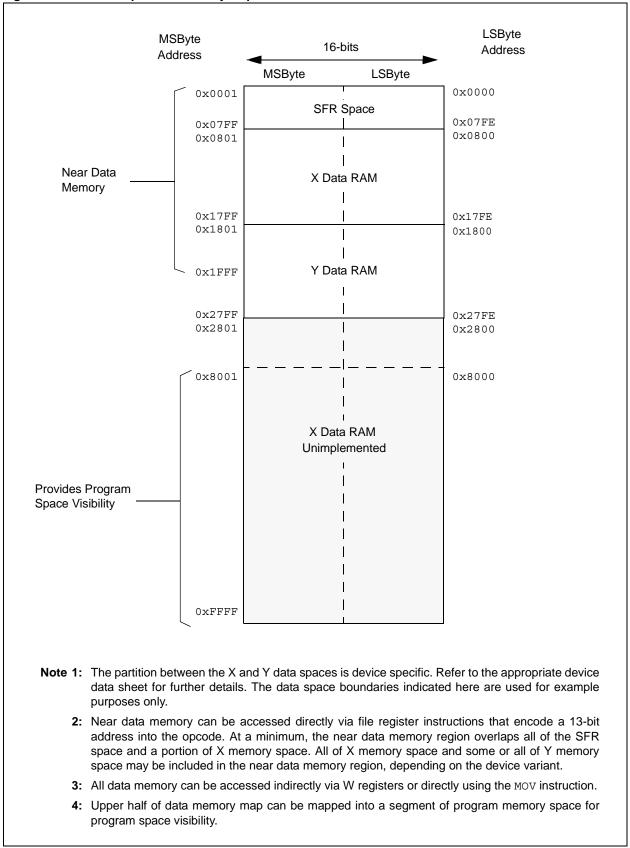

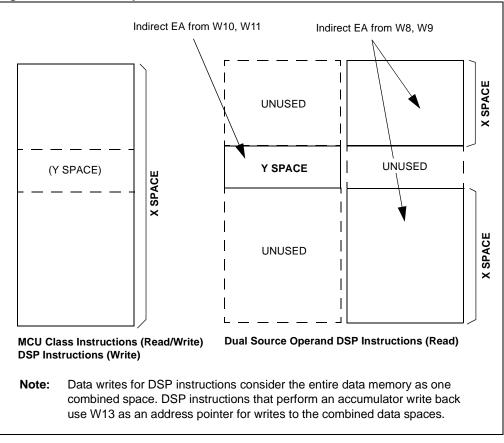

The data space can be addressed as 32K words or 64 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operate solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device specific.

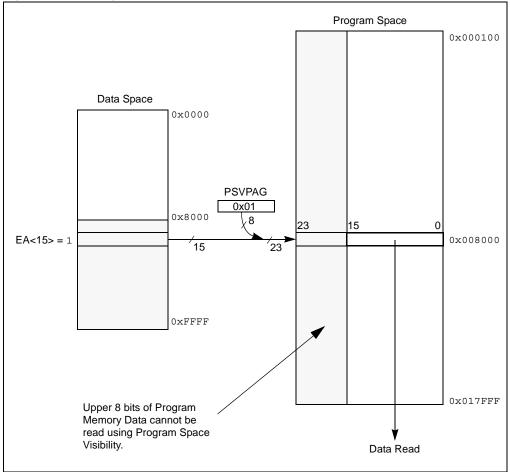

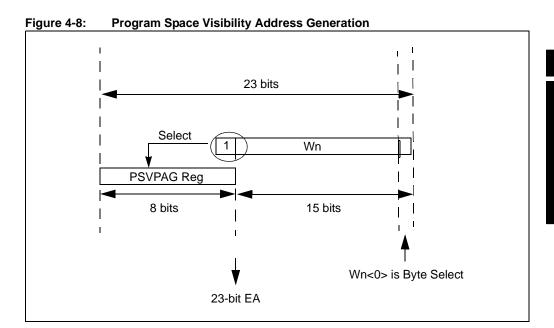

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space. Furthermore, RAM may be connected to the program memory bus on devices with an external bus and used to extend the internal data RAM.

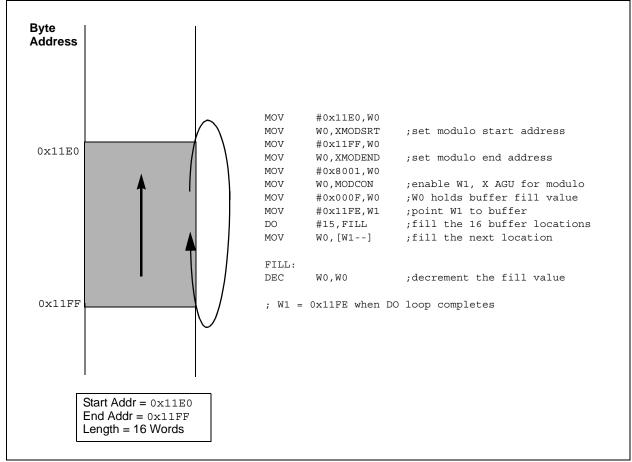

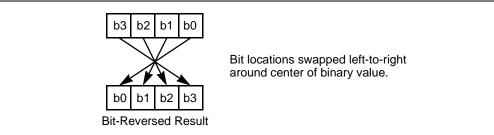

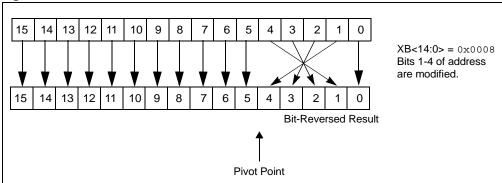

Overhead free circular buffers (modulo addressing) are supported in both X and Y address spaces. The modulo addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports bit-reverse addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The CPU supports Inherent (no operand), Relative, Literal, Memory Direct, Register Direct and Register Indirect Addressing modes. Each instruction is associated with a predefined Addressing mode group depending upon its functional requirements. As many as 6 Addressing modes are supported for each instruction.

For most instructions, the dsPIC30F is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, 3 operand instructions can be supported, allowing A+B=C operations to be executed in a single cycle.

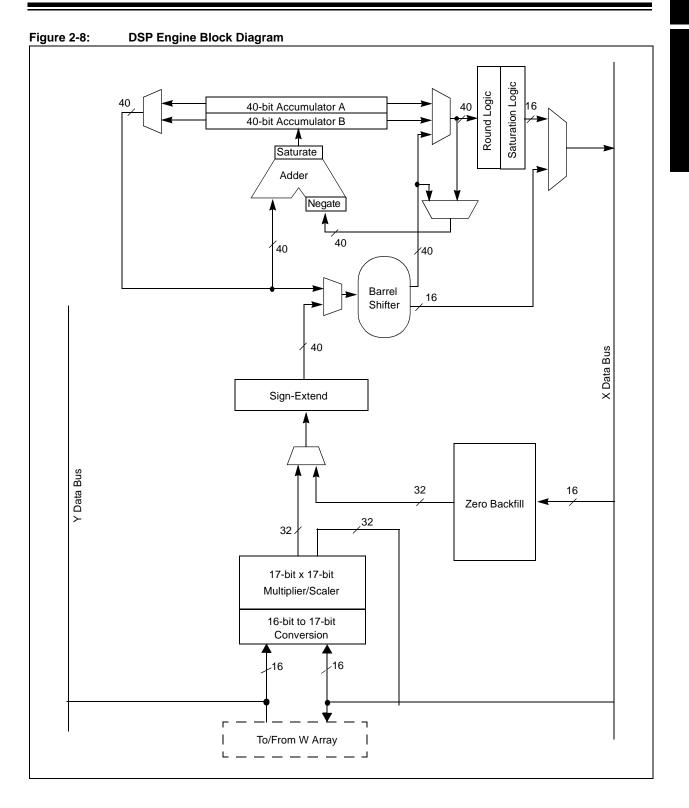

The DSP engine features a high speed, 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bi-directional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 15 bits right, or up to 16 bits left, in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory while multiplying two W registers. This requires that the data space be split for these instructions and linear for all others. This is achieved in a transparent and flexible manner through dedicating certain working registers to each address space.

The dsPIC30F has a vectored exception scheme with up to 8 sources of non-maskable traps and 54 interrupt sources. Each interrupt source can be assigned to one of seven priority levels.

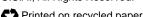

A block diagram of the CPU is shown in Figure 2-1.

# 2.2 Programmer's Model

The programmer's model for the dsPIC30F is shown in Figure 2-2. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions. A description of each register is provided in Table 2-1.

| Register(s) Name | Description                                    |

|------------------|------------------------------------------------|

| W0 through W15   | Working register array                         |

| ACCA, ACCB       | 40-bit DSP Accumulators                        |

| PC               | 23-bit Program Counter                         |

| SR               | ALU and DSP Engine Status register             |

| SPLIM            | Stack Pointer Limit Value register             |

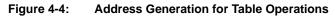

| TBLPAG           | Table Memory Page Address register             |

| PSVPAG           | Program Space Visibility Page Address register |

| RCOUNT           | REPEAT Loop Count register                     |

| DCOUNT           | DO Loop Count register                         |

| DOSTART          | DO Loop Start Address register                 |

| DOEND            | DO Loop End Address register                   |

| CORCON           | Contains DSP Engine and DO Loop control bits   |

Table 2-1:

Programmer's Model Register Descriptions

In addition to the registers contained in the programmer's model, the dsPIC30F contains control registers for modulo addressing, bit-reversed addressing and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory mapped, as shown in Table 2-8 on page 2-38.

# Section 2. CPU

Figure 2-2: **Programmer's Model**

### 2.2.1 Working Register Array

The 16 working (W) registers can function as data, address or address offset registers. The function of a W register is determined by the Addressing mode of the instruction that accesses it.

The dsPIC30F instruction set can be divided into two instruction types: register and file register instructions. Register instructions can use each W register as a data value or an address offset value. For example:

MOV W0,W1 ; move contents of W0 to W1 MOV W0,[W1] ; move W0 to address contained in W1 ADD W0,[W4],W5 ; add contents of W0 to contents pointed ; to by W4. Place result in W5.

#### 2.2.1.1 W0 and File Register Instructions

W0 is a special working register because it is the only working register that can be used in file register instructions. File register instructions operate on a specific memory address contained in the instruction opcode and W0. W1-W15 cannot be specified as a target register in file register instructions.

The file register instructions provide backward compatibility with existing PICmicro<sup>®</sup> devices which have only one W register. The label 'WREG' is used in the assembler syntax to denote W0 in a file register instruction. For example:

MOV WREG,0x0100 ; move contents of W0 to address 0x0100 ADD 0x0100,WREG ; add W0 to address 0x0100, store in W0

**Note:** For a complete description of Addressing modes and instruction syntax, please refer to the dsPIC30F Programmer's Reference Manual (DS70032).

#### 2.2.1.2 W Register Memory Mapping

Since the W registers are memory mapped, it is possible to access a W register in a file register instruction as shown below:

MOV 0x0004, W10 ; equivalent to MOV W2, W10

where 0x0004 is the address in memory of W2.

Further, it is also possible to execute an instruction that will attempt to use a W register as both an address pointer and operand destination. For example:

MOV W1, [W2++]

where:

W1 = 0x1234 W2 = 0x0004 ;[W2] addresses W2

In the example above, the contents of W2 are  $0 \times 0004$ . Since W2 is used as an address pointer, it points to location  $0 \times 0004$  in memory. W2 is also mapped to this address in memory. Even though this is an unlikely event, it is impossible to detect until run-time. The dsPIC30F ensures that the data write will dominate, resulting in W2 =  $0 \times 1234$  in the example above.

#### 2.2.1.3 W Registers and Byte Mode Instructions

Byte instructions which target the W register array only affect the Least Significant Byte of the target register. Since the working registers are memory mapped, the Least *and* Most Significant Bytes can be manipulated through byte wide data memory space accesses.

# 2.2.2 Shadow Registers

Many of the registers in the programmer's model have an associated shadow register as shown in Figure 2-2. None of the shadow registers are accessible directly. There are two types of shadow registers: those utilized by the PUSH.S and POP.S instructions and those utilized by the DO instruction.

### 2.2.2.1 PUSH.S and POP.S Shadow Registers

The PUSH.S and POP.S instructions are useful for fast context save/restore during a function call or Interrupt Service Routine (ISR). The PUSH.S instruction will transfer the following register values into their respective shadow registers:

- W0...W3

- SR (N, OV, Z, C, DC bits only)

The POP.S instruction will restore the values from the shadow registers into these register locations. A code example using the PUSH.S and POP.S instructions is shown below:

MyFunction:

```

PUSH.S; Save W registers, MCU statusMOV#0x03,W0; load a literal value into W0ADDRAM100; add W0 to contents of RAM100BTSCSR,#Z; is the result 0?BSETFlags,#IsZero; Yes, set a flagPOP.S; Restore W regs, MCU statusRETURN

```

The PUSH.S instruction will overwrite the contents previously saved in the shadow registers. The shadow registers are only one level in depth, so care must be taken if the shadow registers are to be used for multiple software tasks.

The user must ensure that any task using the shadow registers will not be interrupted by a higher priority task that also uses the shadow registers. If the higher priority task is allowed to interrupt the lower priority task, the contents of the shadow registers saved in the lower priority task will be overwritten by the higher priority task.

### 2.2.2.2 DO Loop Shadow Registers

The following registers are automatically saved in shadow registers when a  ${\tt DO}$  instruction is executed:

- DOSTART

- DOEND

- DCOUNT

The DO shadow registers are one level in depth, permitting two loops to be automatically nested. Refer to **Section 2.9.2.2 "DO Loop Nesting"** for further details.

# 2.2.3 Uninitialized W Register Reset

The W register array (with the exception of W15) is cleared during all Resets and is considered uninitialized until written to. An attempt to use an uninitialized register as an address pointer will reset the device.

A word write must be performed to initialize a W register. A byte write will not affect the initialization detection logic.

# 2.3 Software Stack Pointer

W15 serves as a dedicated software stack pointer and is automatically modified by exception processing, subroutine calls and returns. However, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating the stack pointer (e.g., creating stack frames).

**Note:** In order to protect against misaligned stack accesses, W15<0> is fixed to '0' by the hardware.

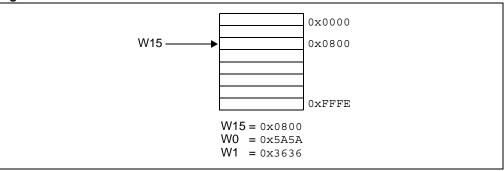

W15 is initialized to  $0 \times 0800$  during all Resets. This address ensures that the stack pointer (SP) will point to valid RAM in all dsPIC30F devices and permits stack availability for non-maskable trap exceptions, which may occur before the SP is initialized by the user software. The user may reprogram the SP during initialization to any location within data space.

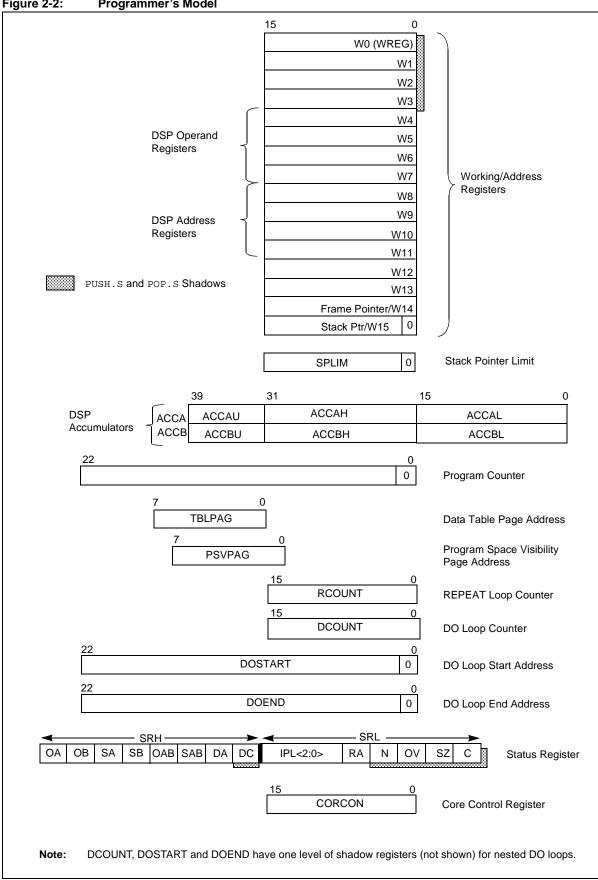

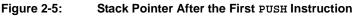

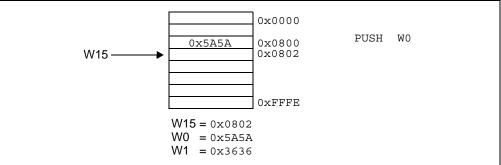

The stack pointer always points to the first available free word and fills the software stack working from lower towards higher addresses. It pre-decrements for a stack pop (read) and post-increments for a stack push (writes), as shown in Figure 2-3.

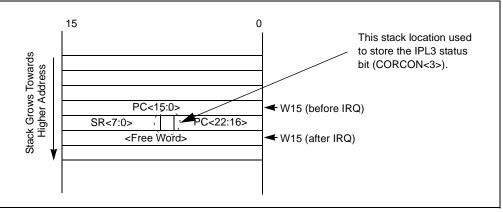

When the PC is pushed onto the stack, PC<15:0> is pushed onto the first available stack word, then PC<22:16> is pushed into the second available stack location. For a PC push during any CALL instruction, the MSByte of the PC is zero-extended before the push as shown in Figure 2-3. During exception processing, the MSByte of the PC is concatenated with the lower 8 bits of the CPU status register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

Figure 2-3: Stack Operation for a CALL Instruction

# 2.3.1 Software Stack Examples

The software stack is manipulated using the PUSH and POP instructions. The PUSH and POP instructions are the equivalent of a MOV instruction with W15 used as the destination pointer. For example, the contents of W0 can be pushed onto the stack by:

PUSH WO

This syntax is equivalent to:

MOV W0, [W15++]

The contents of the top-of-stack can be returned to W0 by:

POP W0

This syntax is equivalent to:

MOV [--W15],W0

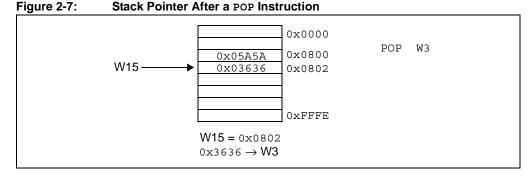

Figure 2-4 through Figure 2-7 show examples of how the software stack is used. Figure 2-4 shows the software stack at device initialization. W15 has been initialized to  $0 \times 0800$ . Furthermore, this example assumes the values  $0 \times 5A5A$  and  $0 \times 3636$  have been written to W0 and W1, respectively. The stack is pushed for the first time in Figure 2-5 and the value contained in W0 is copied to the stack. W15 is automatically updated to point to the next available stack location  $(0 \times 0802)$ . In Figure 2-6, the contents of W1 are pushed onto the stack. In Figure 2-7, the stack is popped and the top-of-stack value (previously pushed from W1) is written to W3.

2

© 2004 Microchip Technology Inc.

# 2.3.2 W14 Software Stack Frame Pointer

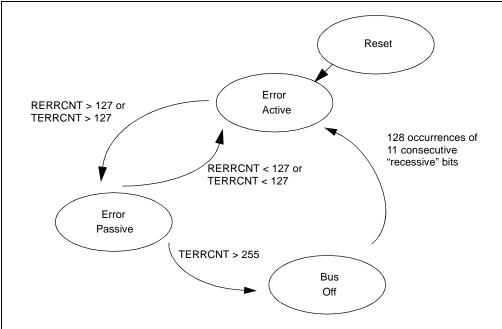

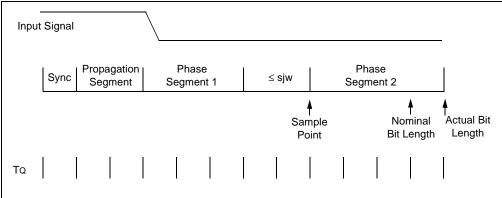

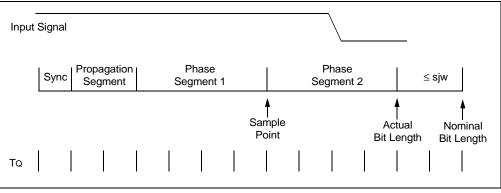

A frame is a user defined section of memory in the stack that is used by a single subroutine. W14 is a special working register because it can be used as a stack frame pointer with the LNK (link) and ULNK (unlink) instructions. W14 can be used in a normal working register by instructions when it is not used as a frame pointer.