(Advanced Information)

### **Description**

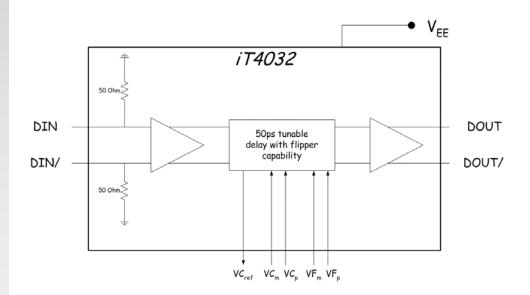

The iT4032D is an ultra-wideband phase delay fabricated using 0.1-µm HBT GaAs technology. The high output voltage, excellent rise and fall times, and the high eye diagram quality at all data rates up to 12.5 Gb/s makes the iT4032D suitable for timing adjustment in data and clock distribution at a very high speed. Complex digital applications that can benefit from the iT4032D include clock data recovery, edge detectors, NRZ/RZ converters, MUX/DEMUX, and data restoration It is based on an ECL topology in order to guarantee high-speed operation. The device features a single delay element that provides up to 50 ps delay and a 180 deg. shift capability.

The delay control can be either differential (using both VCp and VCm) or single-ended (VCp is the active control pad while VCm is shorted to VCref). The nominal control voltage range for the delay is from -2.2 V to -3.0 V, whether the control is single-ended or differential. The flipping control can be either differential (using both VFp and VFn), or single-ended (VFp is the active control pad while VFm is shorted to VCref). The nominal control voltage for the flipping is -2.2 V or -3.0 V whether the control is single-ended or differential. The device is capable of delaying NRZ streams with a data rate up to 12.5 Gb/s or a clock signal with frequency up to 10.7 GHz. The inputs and the outputs are DC coupled. At the input side the internal 50-ohm resistors avoid the need for external impedance matching terminations. The iT4032D uses SCFL I/O levels and is designed so to allow for either single ended or differential data input.

#### **Features**

- Wideband signal handling: up to 12.5 Gb/s NRZ

- Delay adjustment: to 50 ps

- Flipping capability (180 deg. shift)

- 900 mVpp typical single-ended output

- ❖ Jitter RMS: <1.5 ps</p>

- ❖ Output rise time (20% 80 %): <22 ps</p>

- ❖ Output fall time (20% 80 %): <20 ps</p>

- 50-ohm matched DC-coupled inputs and outputs

- Differential or single-ended I/O

- Power consumption: 1.15 W

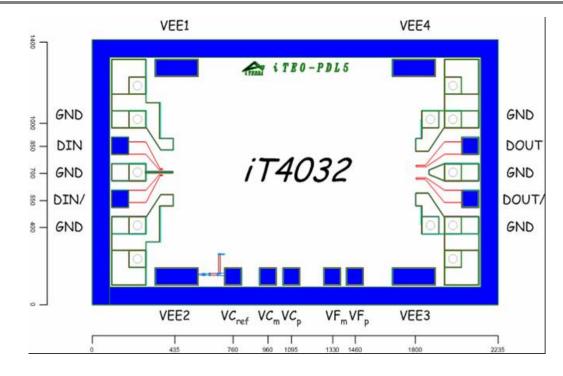

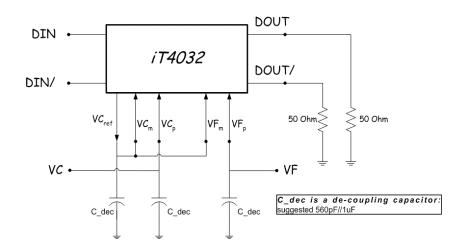

#### **Device Diagram**

www.iterrac.com

This is an Advanced data sheet. See "Product Status Definitions" on Web site or catalog for product development status.

October 5, 2005 Doc. 4036 Rev 0

iTerra Communications 2400 Geng Road, Ste. 100, Palo Alto, CA 94303 Phone (650) 424-1937, Fax (650) 424-1938

(Advanced Information)

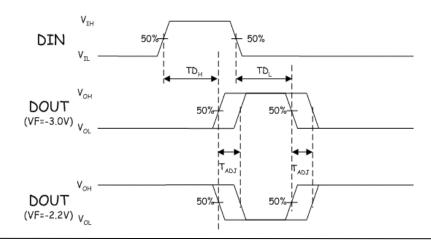

## Timing Diagram

### Absolute Maximum Ratings

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this document is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Symbol           | Parameters/conditions             | Min. | Max. | Units |

|------------------|-----------------------------------|------|------|-------|

| V <sub>EE</sub>  | Power supply voltage              | -5.5 | 0    | V     |

| V <sub>IH</sub>  | Input voltage level, high level   | -1.5 | 1.5  | V     |

| V <sub>IL</sub>  | Input voltage level, low level    | -1.5 | 1.5  | V     |

| VC               | Delay control voltage             | -5.0 | 0    | ٧     |

| VF               | Flipping control voltage          | -5.0 | 0    | V     |

| T <sub>A</sub>   | Operating temperature range – die | -15  | 125  | °C    |

| T <sub>STG</sub> | Storage temperature               | -65  | 150  | °C    |

### Recommended Operational Conditions

| Symbol            | Parameters/conditions                          | Min. | Тур.  | Max  | Units |

|-------------------|------------------------------------------------|------|-------|------|-------|

| T <sub>A</sub>    | Operating temperature range – die              | 0    |       | 85   | °C    |

| V <sub>EE</sub>   | Power supply voltage                           |      | -5    |      | V     |

| VC                | Delay control voltage                          | -3.0 | -2.6  | -2.2 | V     |

| VF                | Flipping control voltage                       | -3.0 |       | -2.2 | V     |

| V <sub>IH</sub>   | Input voltage level, high level (single ended) |      | 0.0   |      | V     |

| V <sub>IL</sub>   | Input voltage level, low level (single ended)  |      | -0.9  |      | V     |

| V <sub>INDC</sub> | DC input voltage (with DC-coupled input)       |      | -0.45 |      | V     |

www.iterrac.com

This is an Advanced data sheet. See "Product Status Definitions" on Web site or catalog for product development status.

(Advanced Information)

# **Electrical** Characteristics

- 1. Electrical characteristics at ambient temperature.

- 2. In case of singleended input the unused pin has to be tied to VINDC.

- 3. In case of singleended output, the unused pad must be terminated with 50 ohms to ground.

- 4. Refer to timing diagram.

- 5. On a 10.7 Gb/s PRBS pattern.

| Symbol            | Parameters                                      | Min  | Тур   | Max   | Units |

|-------------------|-------------------------------------------------|------|-------|-------|-------|

| V <sub>EE</sub>   | Power supply voltage                            | -4.5 | -5.00 | -5.25 | V     |

| V <sub>IH</sub>   | Input voltage level, high level (single ended)  |      | 0.0   |       | V     |

| V <sub>IL</sub>   | Input voltage level, low level (single ended)   |      | -0.9  |       | V     |

| V <sub>INDC</sub> | DC input voltage (with DC-coupled input) (2)    |      | -0.45 |       | V     |

| V <sub>OUT</sub>  | Data output voltage amplidude (3)               | 0.8  | 0.9   | 1.0   | V     |

| T <sub>R</sub>    | Output rise time (20% – 80%)                    |      | 22    |       | ps    |

| T <sub>F</sub>    | Output fall time (20% – 80%)                    |      | 20    |       | ps    |

| TD <sub>H</sub>   | Output delay low-high transition <sup>(4)</sup> |      | 180   |       | ps    |

| TD <sub>L</sub>   | Output delay high-low transition <sup>(4)</sup> |      | 180   |       | ps    |

| T <sub>ADJ</sub>  | Output phase delay adjustment <sup>(4)</sup>    |      | 50    |       | ps    |

| S <sub>11</sub>   | Input return loss (up to 15 GHz)                |      | 23    |       | dB    |

| S <sub>22</sub>   | Output return loss (up to 15 GHz)               |      | 8     |       | dB    |

| F <sub>MAX</sub>  | Maximum clock frequency                         |      | 10.7  |       | GHz   |

| J <sub>p-p</sub>  | Peak-to-peak jitter <sup>(5)</sup>              |      | 9     |       | ps    |

| J <sub>rms</sub>  | RMS jitter <sup>(5)</sup>                       |      | 1.5   |       | ps    |

| I <sub>EE</sub>   | Power supply current                            |      | 230   |       | mA    |

| P <sub>D</sub>    | Power dissipation                               |      | 1.15  |       | W     |

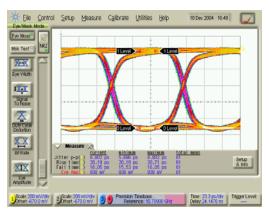

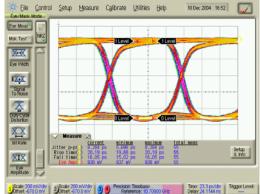

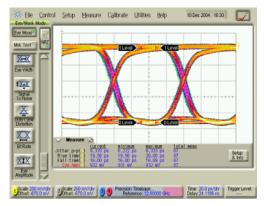

# **Eye Diagram Performance**

Die measurement Vee: -5.0 V Input data rate: 10.7 Gb/s Single-ended data input: +/-450 mVpp Control voltage: VCm= VFm =VCREF VCp=-2.2 V; VFp=-3.0 V

Die measurement

Vee: -5.0 V Input data rate: 10.7 Gb/s

Single-ended data input: +/-450 mVpp

Control voltage: VCm=VFm=VCREF;

VCp =-3.0 V; VFp =-3.0 V

www.iterrac.com

This is an Advanced data sheet. See "Product Status Definitions" on Web site or catalog for product development status.

October 5, 2005 Doc. 4036 Rev 0

iTerra Communications 2400 Geng Road, Ste. 100, Palo Alto, CA 94303 Phone (650) 424-1937, Fax (650) 424-1938

(Advanced Information)

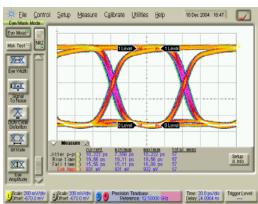

Eye Diagram Performance (cont.)

Die measurement

Vee: -5.0 V

Input data rate: 12.5 Gb/s

Single-ended data input: +/-450 mVpp

Control voltage: VCm=VFm=VCREF;

VCp=-2.2 V; VFp=-3.0 V

Die measurement

Vee: -5.0 V

Input data rate: 12.5 Gb/s

Single-ended data input: +/-450 mVpp

Control voltage: VCm=VFm=VCREF;

VCp=-2.2 V; VFp=-3.0 V

Elle Control Setup Measure Calibrate Utilities Help 10 Dec 2004 16:57

Eye Measure

Nak Test 10

Setup Measure Calibrate Utilities Help 10 Dec 2004 16:57

Mak Test 10

Mak Test 10

Measure A REMS

Average Power Power Power 11

Average Power 12

A

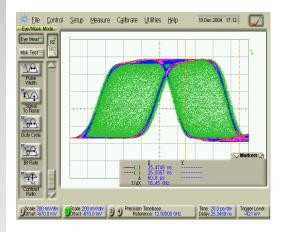

Die measurement

Vee: 5.0 V

Input data rate: 12.5 Gb/s

Single-ended data input: +/-450 mVpp

Control voltage: VCm=VFm=VCREF;

VCp=-2.2 V to -3 V (accumulating); VFp=-3.0 V

Die measurement

Vee: 5.0 V

Input data rate: 10.7 Gb/s

Single-ended clock input: +/-450 mVpp

Control voltage: VCm=VFm=VCREF;

VCp=-2.2 V to -3 V (accumulating); VFp=-3.0 V

(Advanced Information)

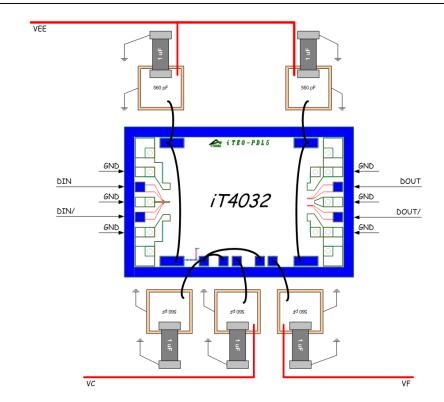

### Recommended Operational Setup

### Recommended Chip Mounting

Chip size 2235  $\mu$ m ±10  $\mu$ m x 1400  $\mu$ m ±10  $\mu$ m

Chip thickness: 104  $\mu m$  ±3  $\mu m$

Pad size: 100 μm x 100 μm

RF pad pitch: 150 µm

(Advanced Information)

### Pad Positions And Dimensions

Chip size: 2235  $\mu$ m ±10  $\mu$ m x 1400  $\mu$ m ±10  $\mu$ m

Chip thickness: 104 µm

$\pm 3~\mu m$

Pad size: 100 µm x 100

μm

RF pad pitch: 150 µm