### 1.0 Features

- Supports MediaTek Pump Express™ technology fast charge protocol

- Supports Lenovo fast charge protocol

- Universal input off-line controller for applications up to 24W output power

- No-load power consumption < 30mW at 230V<sub>AC</sub> along with fast dynamic load response and short turn-on delay in typical 15W adapter applications

- PrimAccurate<sup>™</sup> primary-side feedback eliminates optoisolators and simplifies design

- Adaptive multi-mode PWM/PFM control improves efficiency

- Proprietary optimized 79kHz maximum PWM switching frequency with quasi-resonant operation achieves best size, efficiency and common mode noise

- Active start-up scheme enables fastest possible start-up

- Tight constant-voltage regulation across line and load range

- User-configurable 5-level cable drop compensation provides design flexibility

- EZ-EMI® design enhances manufacturability

- No external loop compensation components required

- Built-in single-point fault protections against output short-circuit, output over-voltage, output over-current, auxiliary winding open, and current-sense-resistor-short fault

- Dedicated pin for external over-temperature protection

- Tight constant current control enables output current limit and over-load protection

- Built-in over-temperature protection

- No audible noise over entire operating range

## 2.0 Description

The iW1788-42 is a high performance AC/DC power supply controller which uses digital control technology to build peak current mode PWM flyback power supplies and is compatible with MediaTek's Pump Express™ Plus fast charge protocol. With PrimAccurate™ digital primary-side control technology integrated, the iW1788-42 enables simple, low component count power supplies for universal input off-line applications requiring low BOM cost, high performance solutions. The iW1788-42 removes the need for secondary feedback circuitry and loop compensation components while achieving excellent stability and line and load regulation.

The Pump Express Plus fast charge protocol enables communication between a smartphone and a wall adapter designed with the iW1788-42. The high power protocol allows the smartphone to send commands back to the controller to increase the output voltage of the adapter above the default 5V output, to optimize charge time. The built-in constant current regulating function maintains the output current of the adapter as the voltage output increases. See section 9.14 for more information on this function.

The iW1788-42 works with an external power MOSFET to allow for an output power of up to 24W. The device operates in quasi-resonant mode to provide high efficiency and integrates a number of key built-in protection features, such as EZ-EMI technology, pulse-by-pulse waveform analysis for faster dynamic load response and a full range of protection features from over-temperature, over-voltage and short-circuit.

Dialog's innovative proprietary technology ensures that power supplies built with the iW1788-42 can achieve both highest average active efficiency and less than 30mW noload power consumption in 15W output power applications, and have fast yet smooth start-up with a wide range of capacitive loads at output voltages up to 12V.

## 3.0 Applications

- Compact AC/DC adapter/chargers for cell phones, PDAs, digital still cameras

- · Fast charge enabled adapters for smartphones

- Universal input AC/DC adapters (7.5W 24W)

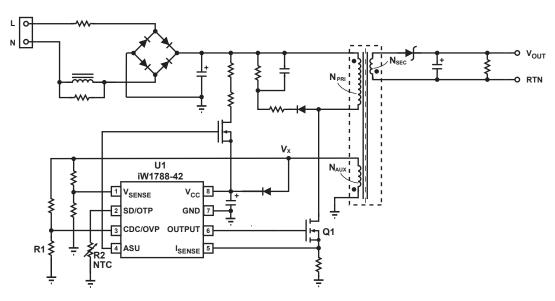

Figure 3.1: iW1788-42 Typical Application Diagram

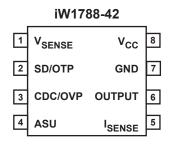

## **4.0 Pinout Description**

Figure 4.1: 8-Lead SOIC-8 Package

| Pin # | Name               | Туре         | Pin Description                                                                                                                       |

|-------|--------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1     | $V_{SENSE}$        | Analog Input | Auxiliary voltage sense (used for primary regulation).                                                                                |

| 2     | SD/OTP             | Analog Input | External shutdown control. Used for external over-temperature protection (OTP) by connecting an NTC resistor from this pin to Ground. |

| 3     | CDC/OVP            | Analog Input | Used for external cable drop compensation (CDC) configuration and supplemental over-voltage protection (OVP).                         |

| 4     | ASU                | Output       | Control signal for active start-up device (BJT or depletion mode NFET).                                                               |

| 5     | I <sub>SENSE</sub> | Analog Input | Primary current sense. Used for cycle-by-cycle peak current control and limit.                                                        |

| 6     | OUTPUT             | Output       | Gate drive for external MOSFET switch.                                                                                                |

| 7     | GND                | Ground       | Ground.                                                                                                                               |

| 8     | V <sub>CC</sub>    | Power Input  | Power supply for control logic.                                                                                                       |

## **5.0 Absolute Maximum Ratings**

Absolute maximum ratings are the parameter values or ranges which can cause permanent damage if exceeded. For maximum safe operating conditions, refer to Electrical Characteristics in Section 6.0.

| Parameter                                                      | Symbol            | Value        | Units |

|----------------------------------------------------------------|-------------------|--------------|-------|

| DC supply voltage range (pin 8, I <sub>CC</sub> = 20mA max)    | V <sub>CC</sub>   | -0.3 to 25.0 | V     |

| Continuous DC supply current at $V_{CC}$ pin ( $V_{CC}$ = 15V) | I <sub>cc</sub>   | 20           | mA    |

| ASU output (pin 4)                                             |                   | -0.3 to 19.0 | V     |

| OUTPUT (pin 6)                                                 |                   | -0.3 to 20.0 | V     |

| V <sub>SENSE</sub> input (pin 1, I <sub>Vsense</sub> ≤ 10mA)   |                   | -0.7 to 4.0  | V     |

| I <sub>SENSE</sub> input (pin 5)                               |                   | -0.3 to 4.0  | V     |

| SD (pin 2)                                                     |                   | -0.3 to 4.0  | V     |

| CDC/OVP (pin 3, I <sub>CDC/OVP</sub> ≤ 20mA)                   |                   | -0.8 to 4.0  | V     |

| Maximum junction temperature                                   | T <sub>JMAX</sub> | 150          | °C    |

| Operating junction temperature                                 | T <sub>JOPT</sub> | -40 to 150   | °C    |

| Storage temperature                                            | T <sub>STG</sub>  | -65 to 150   | °C    |

| Thermal resistance junction-to-ambient                         | $\theta_{JA}$     | 160          | °C/W  |

| ESD rating per JEDEC JESD22-A114                               |                   | ±2,000       | V     |

| Latch-up test per JESD78A                                      |                   | ±100         | mA    |

3 of 18

### **6.0 Electrical Characteristics**

$V_{CC}$  = 12V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  +85°C, unless otherwise specified.

| Parameter                                              | Symbol                    | Test Conditions                                             | Min  | Тур   | Max  | Unit |  |  |

|--------------------------------------------------------|---------------------------|-------------------------------------------------------------|------|-------|------|------|--|--|

| V <sub>SENSE</sub> SECTION (Pin 1)                     |                           |                                                             |      |       |      |      |  |  |

| Input leakage current                                  | I <sub>BVS</sub>          | V <sub>SENSE</sub> = 2V                                     |      |       | 1    | μA   |  |  |

| Nominal voltage threshold                              | V <sub>SENSE(NOM)</sub>   | T <sub>A</sub> =25°C, negative edge, V <sub>OUT</sub> = 12V | 1.70 | 1.75  | 1.80 | V    |  |  |

| V <sub>SENSE</sub> -based output OVP threshold with no | V                         | $T_A$ =25°C, negative edge, $V_{OUT}$ = 5V                  |      | 0.885 |      | V    |  |  |

| CDC compensation (Note 1)                              | $V_{SENSE(MAX)}$          | $T_A$ =25°C, negative edge, $V_{OUT}$ = 12V                 |      | 2.025 |      | V    |  |  |

| I <sub>SENSE</sub> SECTION (Pin 5)                     |                           |                                                             |      |       |      |      |  |  |

| Over-current threshold                                 | V <sub>OCP</sub>          |                                                             | 1.11 | 1.15  | 1.19 | V    |  |  |

| I <sub>SENSE</sub> regulation upper limit (Note 2)     | $V_{IPK(HIGH)}$           |                                                             |      | 0.9   |      | V    |  |  |

| I <sub>SENSE</sub> regulation lower limit (Note 2)     | $V_{IPK(LOW)}$            |                                                             |      | 0.1   |      | V    |  |  |

| Input leakage current                                  | I <sub>LK</sub>           | I <sub>SENSE</sub> = 1.0V                                   |      |       | 1    | μΑ   |  |  |

| SD/OTP SECTION (Pin 2)                                 |                           |                                                             |      |       |      |      |  |  |

| Shutdown threshold (falling edge)                      | $V_{\text{SD-TH(F)}}$     |                                                             | 0.95 | 1.0   | 1.05 | V    |  |  |

| Shutdown threshold before start-up                     | $V_{\text{SD-TH(SD\_F)}}$ |                                                             | 1.14 | 1.2   | 1.26 | V    |  |  |

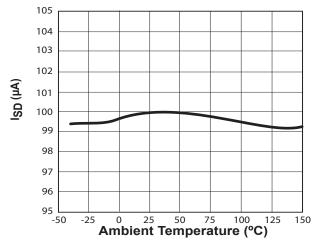

| Shutdown current source                                | I <sub>SD</sub>           |                                                             | 95   | 100   | 105  | μA   |  |  |

| CDC SECTION (Pin 3)                                    |                           |                                                             |      |       |      |      |  |  |

| Input leakage current                                  | I <sub>CDC</sub>          | V <sub>CDC</sub> = 1.0V                                     |      |       | 2.5  | μA   |  |  |

| OUTPUT SECTION (Pin 6)                                 |                           |                                                             |      |       | ı    |      |  |  |

| Driver pull-down ON-resistance                         | R <sub>DS(ON)PD</sub>     | I <sub>SINK</sub> = 5mA                                     |      | 12    |      | Ω    |  |  |

| Driver pull-up ON-resistance                           | R <sub>DS(ON)PU</sub>     | I <sub>SOURCE</sub> = 5mA                                   |      | 80    |      | Ω    |  |  |

| Rise time (Note 2)                                     | t <sub>R</sub>            | T <sub>A</sub> = 25°C, C <sub>L</sub> = 330pF<br>10% to 90% |      | 95    |      | ns   |  |  |

| Fall time (Note 2)                                     | t <sub>F</sub>            | T <sub>A</sub> = 25°C, C <sub>L</sub> = 330pF<br>90% to 10% |      | 14    |      | ns   |  |  |

## **6.0 Electrical Characteristics (cont.)**

$V_{CC}$  = 12V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C, unless otherwise specified (Note 1)

| Parameter                                  | Symbol                                                                                    | Test Conditions                                   | Min  | Тур  | Max  | Unit |  |

|--------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------|------|------|------|------|--|

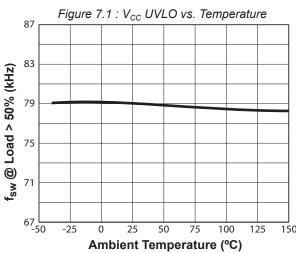

| Switching frequency (Note 3)               | f <sub>SW</sub>                                                                           | > 50% load                                        |      | 79   |      | kHz  |  |

| Fast Charge Control SECTION (Secon         | Fast Charge Control SECTION (Secondary Output Current - Affected by R <sub>S</sub> and N) |                                                   |      |      |      |      |  |

| Command current programming                | I <sub>CONTROL_L</sub>                                                                    |                                                   |      |      | 130  | mA   |  |

| levels (Note 4 & 5)                        | I <sub>CONTROL_H</sub>                                                                    |                                                   | 250  |      |      | mA   |  |

| Output voltage accuracy during fast        | $V_{OUT}$                                                                                 | V <sub>OUT</sub> = 3.6V to 4.8V                   | -7.5 |      | 7.5  | %    |  |

| charge (Note 4 & 5)                        | V <sub>OUT</sub>                                                                          | V <sub>OUT</sub> = 5V to 12V                      | -5   |      | 5    | %    |  |

| Watchdog timeout (Note 5)                  | $T_WD$                                                                                    |                                                   | 180  | 190  | 220  | ms   |  |

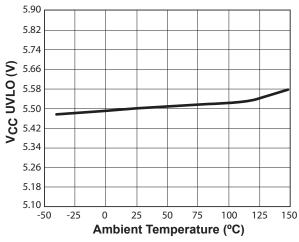

| V <sub>cc</sub> SECTION (Pin 8)            |                                                                                           |                                                   |      |      |      |      |  |

| Operating voltage (Note 2)                 | $V_{\rm CC(MAX)}$                                                                         |                                                   |      |      | 20   | V    |  |

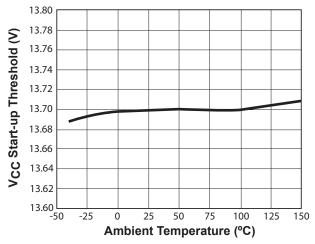

| Start-up threshold                         | $V_{\text{CC(ST)}}$                                                                       | V <sub>CC</sub> rising                            | 12.7 | 13.7 | 14.7 | V    |  |

| Under-voltage lockout threshold            | $V_{\rm CC(UVL)}$                                                                         | V <sub>CC</sub> falling                           | 5.2  | 5.5  | 5.8  | V    |  |

| Start-up current                           | I <sub>IN(ST)</sub>                                                                       | V <sub>CC</sub> = 12V                             |      | 7.6  |      | μA   |  |

| Quiescent current                          | I <sub>CCQ</sub>                                                                          | C <sub>L</sub> = 330pF, V <sub>SENSE</sub> = 1.5V |      | 4.1  |      | mA   |  |

| ASU SECTION (Pin 4)                        |                                                                                           |                                                   |      |      |      |      |  |

| Maximum operating voltage (Note 2)         | V <sub>ASU(MAX)</sub>                                                                     |                                                   |      |      | 16   | V    |  |

| Resistance between V <sub>CC</sub> and ASU | $R_{Vcc\_ASU}$                                                                            |                                                   |      | 1100 |      | kΩ   |  |

### Notes:

- Note 1: See Section 9.12 for more details on CDC functionality.

- Note 2: These parameters are not 100% tested. They are guaranteed by design and characterization.

- Note 3: Operating frequency varies based on the load conditions, see Section 9.6 for more details.

- Note 4. R<sub>S</sub> and N must be set for an output of 2A in 5V setting.

- Note 5. See Section 9.14 for details.

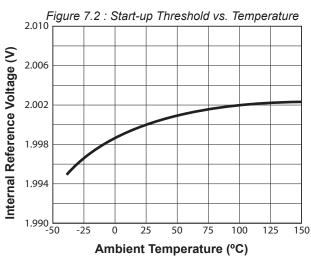

## 7.0 Typical Performance Characteristics

Figure 7.3 : Switching Frequency vs. Temperature<sup>1</sup>

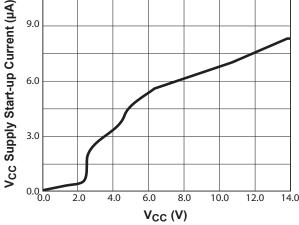

Figure 7.5: V<sub>CC</sub> Supply Start-up Current vs. V<sub>CC</sub>

Figure 7.4: Internal Reference vs. Temperature

Figure 7.6: I<sub>SD</sub> vs. Temperature

### Notes:

Note 1. Operating frequency varies based on the load conditions, see Section 9.6 for more details. iW1788-42 Rev. 0.9 Preliminary

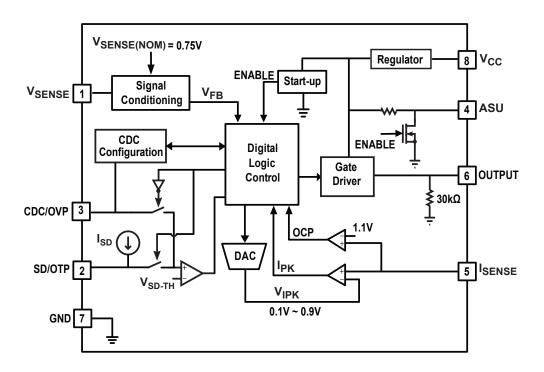

## 8.0 Functional Block Diagram

Figure 8.1: iW1788-42 Functional Block Diagram

### 9.0 Theory of Operation

The iW1788-42 is a digital controller that uses a proprietary primary-side control technology to eliminate the opto-isolated feedback and secondary regulation circuits required in traditional designs. This results in a low-cost solution for low power AC/DC adapters. The core PWM processor uses fixed-frequency Discontinuous Conduction Mode (DCM) operation at higher power levels and switches to variable frequency operation at light loads to maximize efficiency. Furthermore, Dialog's digital control technology enables fast dynamic response, tight output regulation, and full-featured circuit protection with primary-side control.

The block diagram in Figure 8.1 illustrates the iW1788-42 operating in peak current mode control. The digital logic control block generates the switching on-time and off-time information based on the output voltage and current feedback signal and provides commands to dynamically control the external MOSFET gate voltage. The I<sub>SENSE</sub> is an analog input configured to sense the primary current in a voltage form. In order to achieve the peak current mode control and cycle-by-cycle current limit, the V<sub>IPK</sub> sets the threshold for the  $I_{\text{SENSE}}$  to compare with, and it varies in the range of 0.1V (typical) to 0.9V (typical) under different line and load conditions. The system loop is automatically compensated internally by a digital error amplifier. Adequate system phase margin and gain margin are guaranteed by design and no external analog components are required for loop compensation. The iW1788-42 uses an advanced digital control algorithm to reduce system design time and increase reliability.

Furthermore, accurate secondary constant current operation is achieved without the need for any secondary-side sense and control circuits.

The iW1788-42 uses adaptive multi-mode PWM/PFM control to dynamically change the MOSFET switching frequency for efficiency, EMI, and power consumption optimization. In addition, it achieves unique MOSFET quasi-resonant switching to further improve efficiency and reduce EMI. Built-in single-point fault protection features include over-voltage protection (OVP), output short-circuit protection (SCP), over-current protection (OCP), auxiliary winding open detection, and I<sub>SENSE</sub> fault detection.

Dialog's digital control scheme is specifically designed to address the challenges and trade-offs of power conversion design. This innovative technology is ideal for balancing new regulatory requirements for green mode operation with more practical design considerations such as minimum cost, smallest size, and high performance output control.

### 9.1 Pin Detail

### Pin 1 - V<sub>SENSE</sub>

Sense signal input from auxiliary winding. This provides the secondary voltage feedback used for output regulation.

#### Pin 2 - SD/OTP

External shutdown control. If the voltage at this pin is lower than 1.2V (typical) at the beginning of start-up or lower than 1.0V(typical) during normal operation, then the IC shuts down. Leave this pin unconnected if the shutdown control is not used (refer to Section 9.14).

### Pin 3 - CDC/OVP

Used to configure external cable drop compensation (CDC) at the beginning of start-up and to provide over-voltage protection during normal operation by sensing output voltage via auxiliary winding.

#### Pin 4 - ASU

Control signal for active start-up device. This signal is pulled low after start-up is finished to cut off the active device.

### Pin 5 - I<sub>SENSE</sub>

Primary current sense. Used for cycle-by-cycle peak current control and limit.

### Pin 6 - OUTPUT

Gate drive for the external power MOSFET switch.

### Pin 7 - GND

Ground.

### Pin 8 - V<sub>cc</sub>

Power supply for the controller during normal operation. The controller starts up when  $V_{\text{CC}}$  reaches 12.0V (typical), and shuts down when the  $V_{\text{CC}}$  voltage drops below 6.5V (typical). A decoupling capacitor of 0.1  $\mu F$  or so should be connected between the  $V_{\text{CC}}$  pin and GND.

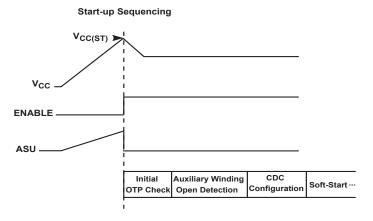

## 9.2 Active Start-up and Adaptively Controlled Soft-Start

The iW1788-42 features an innovative proprietary soft-start scheme to achieve fast yet smooth build-up of output voltage with a wide range of output loads, including capacitive loads

typically from  $330\mu\text{F}$  to  $6,000\mu\text{F}$ , and for output voltages covering typically from 5V to 12V. In addition, the active start-up schemes enable the shortest possible turn-on delay without sacrificing no-load power loss.

Refer to Figure 3.1 for active start-up circuits using external depletion mode N-FET. Prior to start-up, the ENABLE signal is low, and the ASU pin voltage closely follows the V<sub>CC</sub> pin voltage, as shown in Figure 9.1. Consequently, the depletion mode N-FET is turned on, allowing the start-up current to charge the  $V_{CC}$  bypass capacitor. When the  $V_{CC}$  bypass capacitor is charged to a voltage higher than the start-up threshold V<sub>CC(ST)</sub>, the ENABLE signal becomes active and the iW1788-42 begins to perform initial OTP check (see Section 9.14), followed by CDC configuration and auxiliary winding open detection (see Section 9.12). Afterwards, the iW1788-42 commences soft-start function. During the soft-start process, the primary-side peak current is limited cycle-by-cycle by the I<sub>PEAK</sub> comparator. The whole soft-start process can break down into several stages based on the output voltage levels, which is indirectly sensed by V<sub>SENSE</sub> signal at the primary side. At different stages, the iW1788-42 adaptively controls the switching frequency and primaryside peak current so that the output voltage can always build up very fast at the early stages and smoothly transition into the desired regulation voltage at the final stage, regardless of any capacitive and resistive loads that the applications may incur.

Figure 9.1: Start up Sequencing Diagram

As the ENABLE signal initiates the soft-start process, it also pulls down the ASU pin voltage at the same time, which turns off the depletion mode N-FET, thus minimizing the no-load standby power consumption.

If at any time the  $V_{\text{CC}}$  voltage drops below the under-voltage lockout (UVLO) threshold  $V_{\text{CC}(\text{UVL})}$ , then the iW1788-42 goes to shut-down. At this time the ENABLE signal becomes low, the depletion mode N-FET turns on, and the  $V_{\text{CC}}$  capacitor

begins to charge up again towards the start-up threshold to initiate a new soft-start process.

In applications where the active start-up is not needed, the start-up resistor can be directly connected to the  $V_{\text{CC}}$  pin without using the active start-up device, and the ASU pin can be left unconnected.

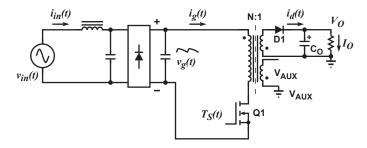

### 9.3 Understanding Primary Feedback

Figure 9.2 illustrates a simplified flyback converter. When the switch Q1 conducts during  $t_{\text{ON}}(t)$ , the current  $i_g(t)$  is directly drawn from rectified sinusoid  $v_g(t)$ . The energy  $E_g(t)$  is stored in the magnetizing inductance  $L_{\text{M}}.$  The rectifying diode D1 is reversely-biased and the load current  $I_{\text{O}}$  is supplied by the secondary capacitor  $C_{\text{O}}.$  When Q1 turns off, D1 conducts and the stored energy  $E_g(t)$  is delivered to the output.

Figure 9.2: Simplified Flyback Converter

In order to tightly regulate the output voltage, the information about the output voltage and load current needs to be accurately sensed. In the DCM flyback converter, this information can be read via the auxiliary winding or the primary magnetizing inductance ( $L_{\text{M}}$ ). During the Q1 on-time, the load current is supplied from the output filter capacitor  $C_{\text{O}}$ . The voltage across  $L_{\text{M}}$  is  $v_{\text{g}}(t)$ , assuming the voltage dropped across Q1 is zero. The current in Q1 ramps up linearly at a rate of:

$$\frac{di_g(t)}{dt} = \frac{v_g(t)}{L_M} \tag{9.1}$$

At the end of on-time, the current has ramped up to:

$$i_{g\_peak}(t) = \frac{v_g(t) \times t_{ON}}{L_M}$$

(9.2)

This current represents a stored energy of:

$$E_g = \frac{L_M}{2} \times i_{g\_peak} \left(t\right)^2 \tag{9.3}$$

When Q1 turns off at  $t_{\text{O}}$ ,  $i_{\text{g}}(t)$  in  $L_{\text{M}}$  forces a reversal of polarities on all windings. Ignoring the communication-time caused by the leakage inductance  $L_{\text{K}}$  at the instant of turn-off  $t_{\text{O}}$ , the primary current transfers to the secondary at a peak amplitude of:

$$i_d(t) = \frac{N_P}{N_S} \times i_{g_peak}(t) \tag{9.4}$$

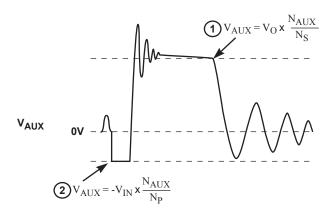

Assuming the secondary winding is master, and the auxiliary winding is slave,

Figure 9.3: Auxiliary Voltage Waveforms

The auxiliary voltage is given by:

$$V_{AUX} = \frac{N_{AUX}}{N_S} (V_O + \Delta V)$$

(9.5)

and reflects the output voltage as shown in Figure 9.3.

The voltage at the load differs from the secondary voltage by a diode drop and IR losses. Thus, if the secondary voltage is always read at a constant secondary current, the difference between the output voltage and the secondary voltage is a fixed  $\Delta V$ . Furthermore, if the voltage can be read when the secondary current is small,  $\Delta V$  is also small. With the iW1788-42,  $\Delta V$  can be ignored.

The real-time waveform analyzer in the iW1788-42 reads this information cycle by cycle. The device then generates a feedback voltage  $V_{\text{FB}}$ . The  $V_{\text{FB}}$  signal precisely represents the output voltage under most conditions and is used to regulate the output voltage.

### 9.4 Constant Voltage Operation

After soft-start has been completed, the digital control block measures the output conditions. It determines output power levels and adjusts the control system according to a light load or heavy load. If this is in the normal range, the device operates in the Constant Voltage (CV) mode, and changes the pulse width ( $t_{\text{ON}}$ ) and off time ( $t_{\text{OFF}}$ ) in order to meet the output voltage regulation requirements.

If no voltage is detected on  $V_{\text{SENSE}}$  it is assumed that the auxiliary winding of the transformer is either open or shorted and the iW1788-42 shuts down.

## 9.5 Current Limit and Constant Current Operation

The constant current (CC) mode is useful in battery charging applications. During this mode of operation the iW1788-42 regulates the output current at a constant level regardless of the output voltage, while avoiding continuous conduction mode. To achieve this regulation the iW1788-42 senses the load current indirectly through the primary current, detected by the  $I_{\text{SENSE}}$  pin via a resistor from the MOSFET source to ground.

The constant current limit is set as a function of  $R_{\text{SENSE}}$  and the turns ratio of the transformer (N), with a correction term for the transformer efficiency  $(\eta_x)$  and is defined by equation 9.6.  $R_{\text{SENSE}}$  is calculated assuming a 5V output and 2A output current.

$$I_{CC\_LIMIT} = 0.225 \times \frac{N}{R_{SENSF}} \times \eta_{x}$$

(9.6)

The iW1788-42 monitors the output voltage, and shuts down the system when the detected output voltage is 2V less than regulated CV level constant currrent (CC) shutdown threshold.

For example, lets consider a 5V/2A charger design, if the cable resistance is around  $75m\Omega$  the voltage drop cross the cable is around 150mV under both the CV mode at full load and CC mode conditions. If CDC Comp is zero, at CV full load, the voltage at the PCB end is around 5V, and the voltage at the cable end is around 4.85V. Then the CC shutdown occurs when the voltage at the PCB end decreases to 3V. Without any cable compensation, and with the iW1788-42's internally fixed CV-2V CC shutdown voltage, the voltage at the end of cable is 2.85V when shutdown occurs. Normally a product option with CDC is needed in this design in order to achieve a desirable voltage regulation at CV mode, e.g., the CDC Comp production option is selected as 150mV. Then at CV full load, the voltage at the PCB end is around 5.15V, and

the voltage at the cable end is around 5V. Correspondingly the CC shutdown occurs when the voltage at the PCB end decreases to 3.15V, and the voltage at the cable end deceases to 3V.

When operating in the CC mode, with the decrease of equivalent load resistance or battery voltage, both the output voltage and  $V_{\rm CC}$  decrease. Once the  $V_{\rm CC}$  voltage is below UVLO threshold, the iW1788-42 shuts down (see Section 9.10).

## 9.6 Multi-Mode PWM/PFM Control and Quasi-Resonant Switching

The iW1788-42 uses a proprietary adaptive multi-mode PWM /PFM control to dramatically improve the light-load efficiency and the overall average efficiency.

During the constant voltage (CV) operation, the iW1788-42 normally operates in a pulse-width-modulation (PWM) mode in heavy load conditions. In the PWM mode, the switching frequency keeps around constant. As the output load  $I_{\text{OUT}}$  is reduced, the on-time  $t_{\text{ON}}$  is decreased, and the controller adaptively transitions to a pulse-frequency-modulation (PFM) mode. In the PFM mode, the MOSFET is turned on for a set duration under a given instantly-rectified AC input voltage, but its period is modulated by the load current. With a decreasing load current, the period increases and thus the switching frequency decreases.

When the switching frequency approaches the human ear audio band, the iW1788-42 transitions to a second level of PWM mode, namely the DCV mode. In the DCV mode, the switching frequency keeps around 22kHz in order to avoid audible noise. As the load current is further reduced, the iW1788-42 transitions to a second level of PFM mode, namely the Deep PFM mode (DPFM), which can reduce the switching frequency to a very low level. Although the switching frequency drops across the audible frequency range during the DPFM mode, the output current in the power converter has reduced to an insignificant level in the DCV mode before transitioning to the DPFM mode. Therefore, the power converter practically produces no audible noise, while achieving high efficiency across various load conditions.

As the load current reduces to very low or no-load condition, the iW1788-42 transitions from the DPFM to the third level of PWM mode, namely the Deep PWM mode (DPWM), in which the switching frequency is fixed at around 2.1kHz.

The iW1788-42 also incorporates a unique proprietary quasi-resonant switching scheme that achieves valley-mode

turn-on for every PWM/PFM switching cycle, in all PFM and PWM modes and in both CV and CC operations. This unique feature greatly reduces the switching loss and dv/dt across the entire operating range of the power supply. Due to the nature of quasi-resonant switching, the actual switching frequency can vary slightly cycle by cycle, providing the additional benefit of reducing EMI. These innovative digital control architecture and algorithms enable the iW1788-42 to achieve the highest overall efficiency and lowest EMI, without causing audible noise over entire operating range.

## 9.7 Less Than 30mW No-Load Power with Fast Load Transient Response

The iW1788-42 features a distinctive DPWM control in no-load conditions to help achieve ultra-low no-load power consumption (< 30mW for typical 15W applications) and meanwhile to ensure fast dynamic load response. The power supply system designs including the pre-load resistor selection should ensure the power supply can operate in the DPWM mode under the steady-state no-load condition. If the pre-load resistor is too small, the no-load power consumption increases; on the other hand, if it is too large, the output voltage may increase and even cause over-voltage since the switching frequency is fixed at around 2.1kHz. For typical designs, the pre-load resistor is in the range of  $8k\Omega$  to  $10k\Omega$ .

In addition to using pre-load resistor, the iW1788-42 employs a few other features to bring down no-load power consumption. First, the iW1788-42 implements an intelligent low-power management technique that achieves ultra-low chip operating current at no-load, typically less than 350µA. Second, a low UVLO threshold of 6.5V (typical) enables the power supply system design to have a low V<sub>CC</sub> voltage at the no-load operation in order to minimize the no-load power. In addition, the active start-up scheme with depletion mode N-FET eliminates the start-up resistor power consumption after the ENABLE signal becomes active. These features combined ensure the lowest system cost power supplies built with the iW1788-42 can achieve less than 30 mW no-load power consumption at 230V<sub>AC</sub> input, and very tight constant voltage and constant current regulation over the entire operating range in typical 15W adapter/charger applications.

While achieving ultra-low no-load power consumption, the iW1788-42 implements innovative proprietary digital control technology to intelligently detect any load transient events, and achieve fast dynamic load response for both one-time and repetitive load transients. In particular, for load transients that are demanded in some applications from no-load to full-load, the iW1788-42 can still maintain a fast enough response to meet the most stringent requirements, with the no-load operating frequency designed at around 2.1kHz.

### 9.8 Variable Frequency Operation Mode

In each of the switching cycles, the falling edge of  $V_{\text{SENSE}}$  is checked. If the falling edge of  $V_{\text{SENSE}}$  is not detected, the off-time is extended until the falling edge of  $V_{\text{SENSE}}$  is detected. The maximum allowed transformer reset time is 125 $\mu$ s. When the transformer reset time reaches 125 $\mu$ s, the iW1788-42 shuts off.

### 9.9 Internal Loop Compensation

The iW1788-42 incorporates an internal Digital Error Amplifier with no requirement for external loop compensation. For a typical power supply design, the loop stability is guaranteed to provide at least 45 degrees of phase margin and -20dB of gain margin.

### 9.10 Voltage Protection Features

The secondary maximum output DC voltage is limited by the iW1788-42. When the  $V_{\text{SENSE}}$  signal exceeds the output OVP threshold at point 1 indicated in Figure 9.3, the iW1788-42 shuts down.

The iW1788-42 protects against input line under-voltage by setting a maximum  $t_{\text{ON}}$  time. Since output power is proportional to the squared  $V_{\text{IN}}$   $t_{\text{ON}}$  product, then for a given output power, as  $V_{\text{IN}}$  decreases the  $t_{\text{ON}}$  increases. Thus by knowing when the maximum  $t_{\text{ON}}$  time occurs the iW1788-42 detects that the minimum  $V_{\text{IN}}$  is reached, and shuts down. The maximum  $t_{\text{ON}}$  limit is set to 15.5µs. Also, the iW1788-42 monitors the voltage on the  $V_{\text{CC}}$  pin and when the voltage on this pin is below UVLO threshold the IC shuts down immediately.

When any of these faults are met the IC remains biased to discharge the  $V_{CC}$  supply. Once  $V_{CC}$  drops below UVLO threshold, the controller resets itself and then initiates a new soft-start cycle. The controller continues attempting start-up until the fault condition is removed.

### 9.11 PCL, OCP and SRS Protection

Peak-current limit (PCL), over-current protection (OCP) and sense-resistor-short protection (SRSP) are features built into the iW1788-42. With the  $I_{\rm SENSE}$  pin the iW1788-42 is able to monitor the peak primary current. This allows for cycle-by-cycle peak current control and limit. When the peak primary current multiplied by the  $I_{\rm SENSE}$  resistor is greater than 1.1V, over-current is detected and the IC immediately turns off the gate driver until the next cycle. The output driver sends out a switching pulse in the following cycle, and the switching pulse continues if the OCP threshold is not reached; or, the switching pulse turns off again if the

OCP threshold is reached. If the OCP occurs for several consecutive switching cycles, the iW1788-42 shuts down.

If the  $I_{SENSE}$  resistor is shorted, there is a potential danger that over-current condition may not be detected. Thus, the IC is designed to detect this sense-resistor-short fault after start-up and shut down immediately. The  $V_{CC}$  is discharged since the IC remains biased. Once  $V_{CC}$  drops below the UVLO threshold, the controller resets itself and then initiates a new soft-start cycle. The controller continues attempting to start up, but does not fully start up until the fault condition is removed.

### 9.12 CDC Configuration

The iW1788-42 incorporates an innovative approach to allow users to configure cable drop compensation (CDC) externally. This configuration is only performed once at the beginning of start-up. It is completed after the initial OTP check but before the soft-start commences. During the CDC configuration, the internal digital control block senses the external resistance value between the CDC pin and ground, and then sets a corresponding CDC level to allow the device to compensate for IR drop in the secondary circuitry during normal operation.

Figure 3.1 shows a simple circuit to set CDC level by connecting a resistor from the CDC pin to ground. The iW1788-42 provides five levels of CDC configurations: 0, 75mV, 150mV, 300mV, and 450mV, which refer to 5V nominal output voltage. Table 9.1 below shows the resistance range for each of the five CDC levels. In practice, it is recommended to select resistance in the middle of the range wherever possible.

The "Cable Comp" specified in Table 9.1 refers to the voltage increment at PCB end from no-load to full-load conditions in the CV mode, with the assumption that the secondary diode voltage drop can be ignored at the point when the secondary voltage is sensed.

To calculate the amount of cable compensation needed, take the resistance of the cable and connector and multiply it by the maximum output current.

### 9.13 External OTP

The iW1788-42 can be configured to provide external over-temperature protection (OTP) by connecting a Negative-Temperature-Coefficient (NTC) resistor from SD/OTP pin to GND. Internally, a 100 $\mu$ A current source is injected to the SD/OTP pin, which generates a voltage proportional to the NTC resistance. At high ambient temperatures, the NTC resistance becomes low, which results in a low voltage at the SD/OTP pin. If the SD/OTP pin voltage drops below an

internally-set threshold, then the OTP is triggered, and the iW1788-42 shuts down.

In the iW1788-42, the external OTP has a built-in hysteresis by having two thresholds. Before start-up, the OTP is triggered if the SD/OTP pin voltage is less than 1.2V; otherwise the device begins the CDC configuration (see Section 9.12), then followed by a normal soft-start process. During normal operation, the OTP threshold is switched to 1.0V, and the device only shuts down when the SD/OTP pin voltage is less than 1.0V.

During normal operation, if the voltage of the SD/OTP pin is below 1.0, then the OTP is triggered, and the device shuts down.

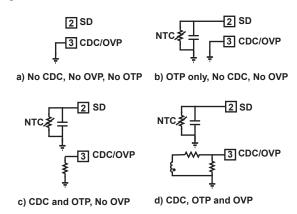

The SD and CDC/OVP pins can be configured to provide different types of applications. Figure 9.4 shows four basic configurations:

Figure 9.4: CDC and SD/OTP Pins Configurations

In Scheme (a), the CDC/OVP pin is directly connected to ground, which sets CDC level to be 1 (i.e. no CDC). On the

other side, leaving the SD/OTP pin unconnected disables the OTP function.

In Scheme (b), CDC/OVP is set to level 1, as in Scheme (a) by grounding the CDC pin. An NTC resistor in paralleled with a capacitor enables the external OTP protection. Note this capacitor is only for decoupling purpose. Its capacitance needs to be less than 47pF; otherwise the voltage at this pin can cause a prolonged delay and incur unwanted behaviors.

In Scheme (c), a resistor from the CDC/OVP pin to ground allows for setting the desired CDC level. Similarly, the NTC resistor enables the external OTP, as it does in Scheme (b).

In Scheme (d), a resistor from the CDC/OVP pin to ground allows for setting the desired CDC level. On the other side, leaving the SD/OTP pin unconnected disables the OTP function.

### 9.14 Pump Express™ Plus Protocol

The iW1788-42 is another rapid charge device from Dialog, compatible with MediaTek's Pump Express Plus protocol, a complement to the standard Pump Express protocol for lower power applications, served by the iW1680. MediaTek's Pump Express Plus technology, established to improve charging times for smartphones and tablets in adapters, allows for output power capability up to 24W for larger capacity batteries and even faster charging times than the main Pump Express Protocol. Being compatible with Pump Express Plus means that the iW1788-42 can change its output voltage from its default 5V output state to as high as 12V in order to optimize battery charging, reducing charge time and helping to minimize cost. The iW1788-42 contains a core digital algorithm to interface with a Pump Express Plus-compatible device that sends commands to the iW1788-42 in order to change the output voltage of the power supply. The command string is detected via the V<sub>BUS</sub> pin of the USB connector, leaving the D+ and D- pins unused to send or receive these commands, improving the reliability of the adapter.

Table 9.1: Recommended resistance range and corresponding CDC levels for 5V output

| CDC Level                   | 1       | 2       | 3          | 4            | 5         |

|-----------------------------|---------|---------|------------|--------------|-----------|

| R <sub>CDC</sub> Range (kΩ) | 0 ~ 5.5 | 5.9 ~ 8 | 8.5 ~ 11.6 | 12.18 ~ 16.6 | 17.5 ~ 20 |

| Cable Comp (mV)             | 0       | 75      | 150        | 300          | 450       |

### **Command Strings**

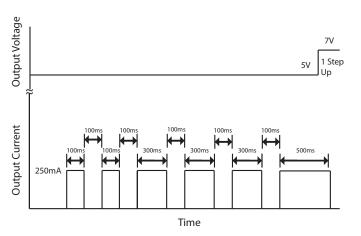

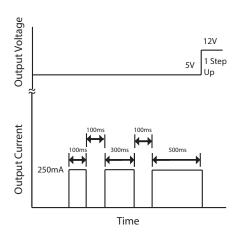

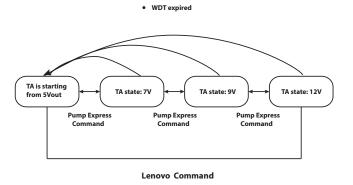

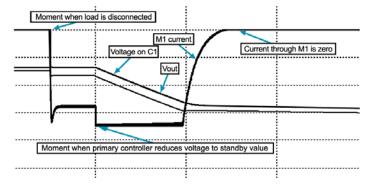

The output voltage is controlled via a simple command string that is generated by drawing pulses of current from the output and that current is detected at the I<sub>SENSE</sub> pin by the PrimAccurate™ primary-side digital control block. The command string is comprised of two key elements, the programming code and a watchdog timer. The string is one of the two mutually orthogonal patterns of current pulses that are detected on the I<sub>SENSE</sub> pin. The I<sub>SENSE</sub> pin detects a specific pattern based on a current amplitude and period. The logic high current level is any current above 250mA and the logic low current level is any current below 130mA. Figure 9.5 and 9.6 show the Pump Express command string and Lenovo command string to increase the output voltage. There is no initialization or handshaking protocol. The output starts at a default 5V when initially powered and stays at 5V until any command is received.

Figure 9.5: Pump Express Command String

On the iW1788-42, the user can step up the voltage from 5V to 7V, 9V or 12V via the Pump Express™ command or increase the voltage to 12V directly with Lenovo command.

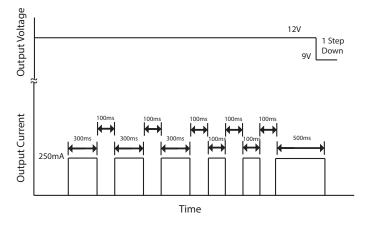

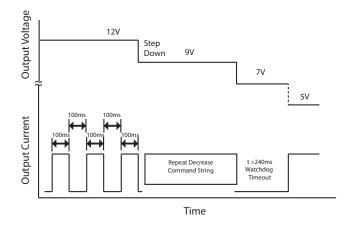

The current pulse train shown in Figure 9.7 represents the string to decrease the output voltage from 12V down to 5V. The user can apply the decrease commands, cycling through the voltages until reaching the final desired output voltage. Current limit remains in 2A without being effected while output increases or decreases the voltage. The watchdog timer monitors the output and if the output current goes below the minimum low current level for programming (130mA) for 220ms or longer, the output automatically resets to 5V. This serves two functions, to act as a quick return to 5V and to determine if the adapter is unplugged from the mobile device.

Figure 9.6: Lenovo Command String

At any time, the user can return to the default 5V by removing the load from the output and waiting at least 220ms, at which time, the controller returns the output voltage to 5V. This is a shortcut in the event that the system needs to return quickly to 5V. In the event that the connector is disconnected when the output of the adapter is at a high voltage, an external discharge circuit is recommended to ensure that the output voltage returns quickly to 5V prior to reconnecting to the adapter. Figure 9.8 shows the state machine for the iW1788-42 output voltage.

Figure 9.7: Command to Decrease Output Voltage

Figure 9.8: State Machine

### **Watchdog Timeout**

The watchdog function primarily serves to detect if the adapter has been unplugged from the mobile device, subsequently resetting the output voltage back to the default 5V output voltage. Figure 9.9 depicts the watchdog functionality and how it is used. After two command strings, the output current stays below 130mA for more than 220ms and the output resets to its default 5V state. This guarantees that when the adapter is reconnected, it is always in its default state. And, it also guarantees that if the adapter is used with a non fast-charge-enabled mobile device, the output maintains its USB-compliant 5V output, making adapters using the iW1788-42 backwards-compatible with 5V USB standards. The messages used to control the output voltage are orthaganol and guarantee no practical possiblity of a false positive message, and they also ensure that the same adapter can be used for devices that offer the fast-charge capability and devices that do not.

Figure 9.9: Watchdog Timeout

### **Power Limiting Function**

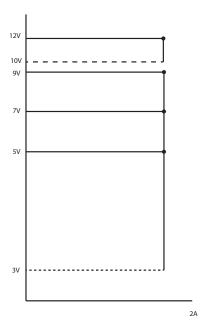

The iW1788-42 provides the competitive solution by offering the constant current regulate function across all voltages. Figure 9.10 shows the typical characteristics of the output current vs output voltage for the iW1788-42. The constant current regulate is initially programmed using the formula shown in section 9.5 of the iW1788-42 datasheet. The current limit should be programmed for all output voltage setting.

Figure 9.10: iW1788-42 Constant Current/Constant Voltage Curves

### **Output Discharge Circuit**

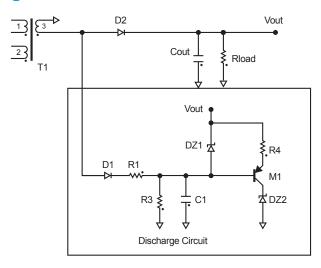

Such a wide output voltage range of 5V to 12V could result in a condition where the output voltage needs to quickly change from 12V to 5V. When the current drawn by the output drops below 100mA for more than 220ms, the controller's watchdog timeout circuit detects this and the output defaults back to 5V. This could be because the battery is now fully charged (or near full charge) or the cable has been disconnected. In the event of a disconnect event, the load goes away and the output needs to discharge quickly back to 5V to avoid an potential problems that could occur if the output voltage is not at 5V when reconnected to the mobile device. An additional circuit can be added to the output to ensure that transitions from high to low happen quickly. Figure 9.11 shows a very simple discharge circuit that is only active when the output needs to discharge. The remainder of the time, the discharge circuit is off, avoiding adding any static load to maintain the no-load power consumption of 30mW or below.

Figure 9.11: Output Discharge Circuit

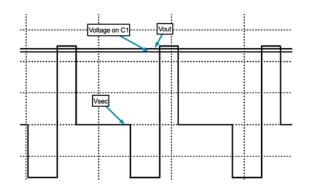

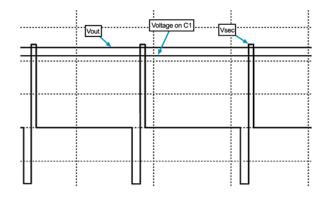

When the output is at 12V and supplying current to the load, the output of the transformer is sending pulses of current through to the load. D1 and R1 peak detect the voltage off of the output of the transformer and C1 charges up to approximately the same voltage as the output voltage (see figure 9.14).

When the output current drops, the pulses from the transformer become smaller and smaller, allowing C1 to discharge through R3. When C1 discharges to a diode drop below the output voltage voltage, M1 turns on and conducts a maximum current established by R4 and DZ1. At the

Figure 9.12: Discharge Circuit Waveform (a)

Figure 9.13: Discharge Circuit Waveform (b)

same time, the controller detects the disconnect condition and resets the default output voltage to 5V, reducing the pulses to the output even further, and current through M1 increases to its max limit set by R4 and DZ1. DZ2 sets the voltage at which the discharge circuit stops discharging the output. The voltage should be set slightly above the output voltage ensuring that during normal operation at 5V that the discharge circuit is not consuming any nominal power, allowing the controller to maintain its no-load power consumption levels.

Figure 9.14: Output Voltage Waveforms - Discharge Circuit

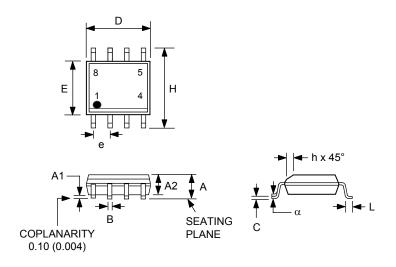

## **10.0 Physical Dimensions**

### 8-Lead Small Outline (SOIC) Package

| Symbol | Incl      | hes   | Millimeters |      |  |

|--------|-----------|-------|-------------|------|--|

| Syr    | MIN       | MAX   | MIN         | MAX  |  |

| Α      | 0.053     | 0.069 | 1.35        | 1.75 |  |

| A1     | 0.0040    | 0.010 | 0.10        | 0.25 |  |

| A2     | 0.049     | 0.059 | 1.25        | 1.50 |  |

| В      | 0.014     | 0.019 | 0.35        | 0.49 |  |

| С      | 0.007     | 0.010 | 0.19        | 0.25 |  |

| D      | 0.189     | 0.197 | 4.80        | 5.00 |  |

| Е      | 0.150     | 0.157 | 3.80        | 4.00 |  |

| е      | 0.050 BSC |       | 1.27 BSC    |      |  |

| Н      | 0.228     | 0.244 | 5.80        | 6.20 |  |

| h      | 0.10      | 0.020 | 0.25        | 0.50 |  |

| L      | 0.016     | 0.049 | 0.4         | 1.25 |  |

| α      | 0°        | 8°    |             |      |  |

Compliant to JEDEC Standard MS12F

Controlling dimensions are in inches; millimeter dimensions are for reference only

This product is RoHS compliant and Halide free.

Soldering Temperature Resistance:

- [a] Package is IPC/JEDEC Std 020D moisture sensitivity level 1

- [b] Package exceeds JEDEC Std No. 22-A111 for solder immersion resistance; package can withstand 10 s immersion < 260°C

Dimension D does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion. Interlead flash or protrusion shall not exceed 0.25 mm per side.

The package top may be smaller than the package bottom. Dimensions D and E1 are determined at the outermost extremes of the plastic body exclusive of mold flash, tie bar burrs, gate burrs and interlead flash, but including any mismatch between the top and bottom of the plastic body.

## 11.0 Ordering Information

| Part Number | Options                                                                   | Package | Description              |

|-------------|---------------------------------------------------------------------------|---------|--------------------------|

| iW1788-42   | 24W, CC shutdown=CV-2V, SR support, Max Voltage=12V, Voltage Skip Enabled | SOIC-8  | Tape & Reel <sup>1</sup> |

Note 1: Tape & Reel packing quantity is 2,500/reel. Minimum ordering quantity is 2,500.

#### **Disclaimer**

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including without limitation the specification and the design of the related semiconductor products, software and applications.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog Semiconductor excludes all liability in this respect.

Customer notes that nothing in this document may be construed as a license for customer to use the Dialog Semiconductor products, software and applications referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document are subject to Dialog Semiconductor's Standard Terms and Conditions of Sale, unless otherwise stated.

© Dialog Semiconductor (UK) Ltd. All rights reserved.

### RoHS compliance

Dialog Semiconductor complies to European Directive 2001/95/EC and from 2 January 2013 onwards to European Directive 2011/65/EU concerning Restriction of Hazardous Substances (RoHS/RoHS2).

Dialog Semiconductor's statement on RoHS can be found on the customer portal https://support.diasemi.com/. RoHS certificates from our suppliers are available on request.

### **Contacting Dialog Semiconductor**

**United Kingdom**

Dialog Semiconductor (UK) Ltd Phone: +44 1793 757700

Germany

Dialog Semiconductor GmbH Phone: +49 7021 805-0

The Netherlands

Dialog Semiconductor B.V. Phone: +31 73 640 88 22

Email

info\_pcbg@diasemi.com

North America

Dialog Semiconductor Inc. Phone: +1 408 845 8500

Japan

Dialog Semiconductor K. K. Phone: +81 3 5425 4567

Taiwan

Dialog Semiconductor Taiwan Phone: +886 8178 6222

Web site:

www.dialog-semiconductor.com

Singapore

Dialog Semiconductor Singapore Phone: +65 64849929

Hong Kong

Dialog Semiconductor Hong Kong Phone: +852 2607 4271

Korea

Dialog Semiconductor Korea Phone: +82 2 3469 8200 China

Dialog Semiconductor (Shenzhen)

Phone: +86 755 2981 3669

Dialog Semiconductor (Shanghai)

Phone: +86 21 5178 2561