# 2 to 4 Phase PWM Extender for Multiphase Synchronous Buck Converter

## **General Description**

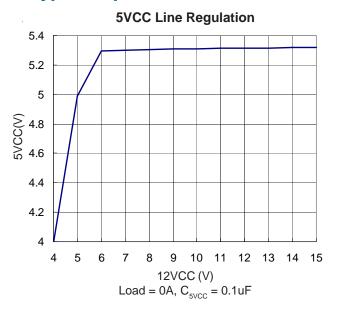

The uP1911R is a high precision sequence array, which is intended for operation phase number extension in multiphase synchronous-rectified buck converter. It consists of three individual sequence circuits to support up to 2 to 4 phase extension application. This part has 4 PWM outputs for external MOSFET drivers, and 4 ISEN inputs. With this phase extender, a 2-phase buck PWM controller is able to control a 4-phase synchronous buck regulator. This device has an internal LDO that regulates 12V input to a 5.2V output as the power supply of control logic. Designed with 12V CMOS process, the uP1911R provides high switching speed and low power dissipation. The uP1911R is available in WQFN3x3 - 16L package.

## Ordering Information

| Order Number | Package      | Top Marking |  |  |

|--------------|--------------|-------------|--|--|

| uP1911RQDD   | WQFN3x3 -16L | uP1911R     |  |  |

Note: uPI products are compatible with the current IPC/ JEDEC J-STD-020 requirement. They are halogen-free, RoHS compliant and 100% matte tin (Sn) plating that are suitable for use in SnPb or Pb-free soldering processes. \_\_\_\_\_ Features

- 5V/12V Supply Voltage

- Integrated 5.2V LDO Regulator for 12V Input

- Support 1 to 2, 2 to 4 Phase Extension

- Low Power Dissipation

- Low Charge Injection

- Near Zero Switching Time

- □ RoHS Compliant and Halogen Free

- WQFN3x3 16L Package

**Applications**

- Desktop Computer

- Motherboards

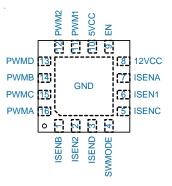

Pin Configuration

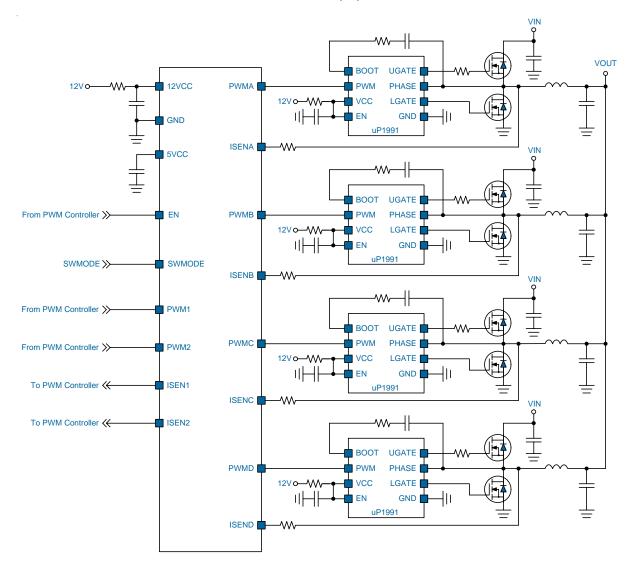

## **Typical Application Circuit**

#### Low-Side MOSEFET Rds(on) Current Sense

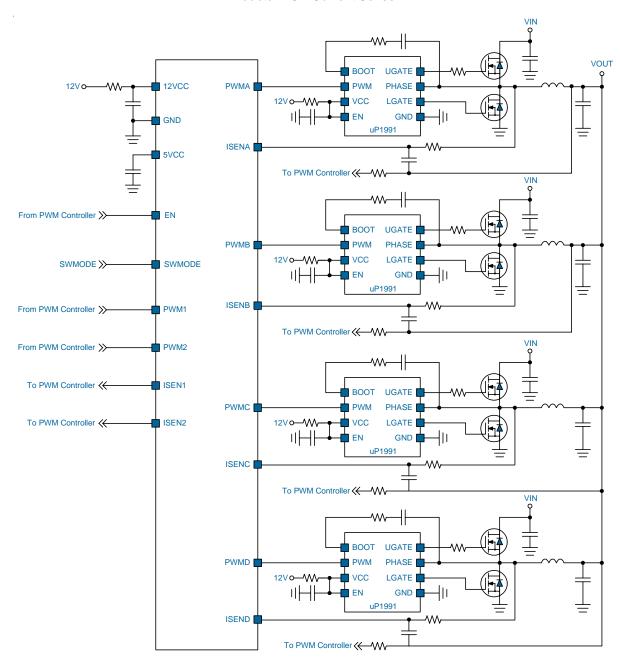

## Typical Application Circuit

#### Inductor DCR Current Sense

# Functional Pin Description

| No. | Pin Name | Pin Function                                                                                                                                                                                                                                                                             |  |  |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | ISENB    | ISENB Input. Connect this pin to phase 2 switching node via a resistor.                                                                                                                                                                                                                  |  |  |

| 2   | ISEN2    | ISEN2 Output. Connect this pin to PWM controller ISEN2 pin.                                                                                                                                                                                                                              |  |  |

| 3   | ISEND    | ISEND Input. Connect this pin to phase 4 switching node via a resistor.                                                                                                                                                                                                                  |  |  |

| 4   | SWMODE   | <b>SWMODE Input.</b> This pin controls the internal analog switch on-state connection timing of ISENA(B) or ISENC(D) to ISEN1(2). Connect this pin to GND at the default, and it can be connected to 5VCC for another switching timing. See ISEN Connection Sequence section for detail. |  |  |

| 5   | ISENC    | ISENC Input. Connect this pin to phase 3 switching node via a resistor.                                                                                                                                                                                                                  |  |  |

| 6   | ISEN1    | ISEN1 Output. Connect this pin to PWM controller ISEN1 pin.                                                                                                                                                                                                                              |  |  |

| 7   | ISENA    | ISENA Input. Connect this pin to phase 1 switching node via a resistor.                                                                                                                                                                                                                  |  |  |

| 8   | 12VCC    | 12V Supply Voltage. Connect a minimum of 1uF ceramic capacitor from this pin to ground.                                                                                                                                                                                                  |  |  |

| 9   | EN       | <b>PWM Output Disable.</b> This pin disables normal operation and forces all PWM outputs off when it is pulled low.                                                                                                                                                                      |  |  |

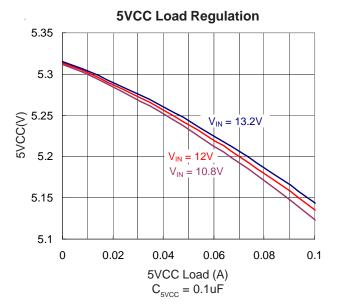

| 10  | 5VCC     | <b>LDO Output Voltage.</b> This pin is the output of internal LDO that regulates 12VCC to a 5.2V output. Connect a minimum of 1uF ceramic capacitor from this pin to ground. For single 5V input operation, connect this pin together with 12VCC to 5V.                                  |  |  |

| 11  | PWM1     | PWM1 Input. Connect this pin to the PWM controller PWM1 output.                                                                                                                                                                                                                          |  |  |

| 12  | PWM2     | PWM2 Input. Connect this pin to the PWM controller PWM2 output.                                                                                                                                                                                                                          |  |  |

| 13  | PWMD     | PWMD Output. Connect this pin to the input of external MOSFET driver for phase 4.                                                                                                                                                                                                        |  |  |

| 14  | PWMB     | PWMB Output. Connect this pin to the input of external MOSFET driver for phase 2.                                                                                                                                                                                                        |  |  |

| 15  | PWMC     | PWMC Output. Connect this pin to the input of external MOSFET driver for phase 3.                                                                                                                                                                                                        |  |  |

| 16  | PWMA     | PWMA Output. Connect this pin to the input of external MOSFET driver for phase 1.                                                                                                                                                                                                        |  |  |

|     |          | <b>Ground.</b> This pin is the signal ground of the IC. Tie this pin to the ground island/plane through the lowest impedance connection available.                                                                                                                                       |  |  |

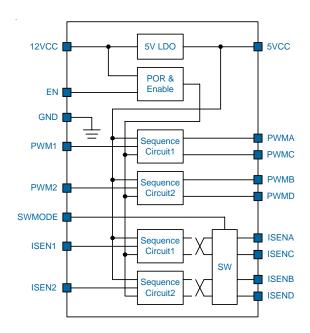

## Functional Block Diagram

## **Functional Description**

#### **Supply Voltage**

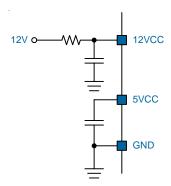

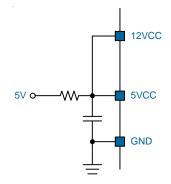

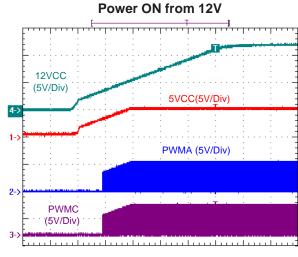

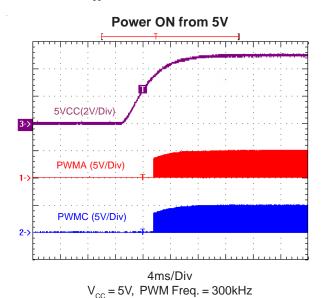

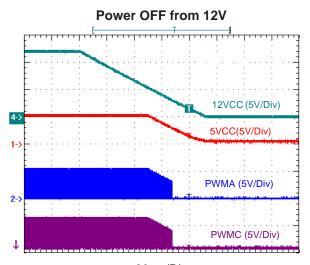

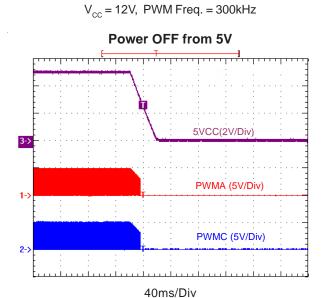

The uP1911R works with a single 12V or 5V supply input voltage. Figure 1 and Figure 2 show the ways of being powered from 12V and 5V, respectively. For single 12V input operation, connect 12VCC to a 12V voltage source, and bypass this pin to ground with at least 1uF ceramic capacitor for noise decoupling. An internal LDO regulator regulates this 12V input to a 5.2V at 5VCC pin as the power for the whole chip. Connect 1uF ceramic capacitor from 5VCC to ground for noise decoupling. For single 5V input operation, connect both 12VCC and 5VCC to a 5V voltage source, and bypass 5VCC to ground with at least 1uF ceramic capacitor for noise decoupling. When the uP1911R is directly supplied from 5V, the internal LDO is inactive. The 12VCC voltage is monitored for power on reset (POR). If 12VCC voltage is higher than the POR rising threshold, the PWM outputs and ISEN sequence circuits will be enabled. The POR threshold has a hysteresis to avoid advertently shutdown.

Figure 1. Single 12V Supply Input

Figure 2. Single 5V Supply Input

#### **PWM Output Sequence**

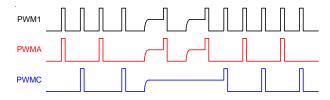

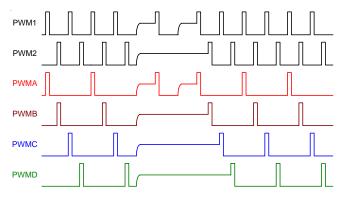

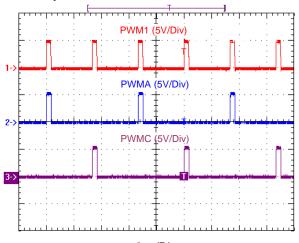

The uP1911R has two individual sequence circuits to control the PWM input and output sequence. Figure 3 shows the sequence of PWM1, PWMA and PWMC. The PWM1 receives PWM signal from the voltage regulator (VR) controller and outputs the received signal to PWMA or PWMC in an alternating way. That is to say PWMA and PWMC output the received signal in turn. For 2-phase to 4-phase application, the uP1911R receives signals PWM[1,2] from VR controller and outputs them to PWM[A:D]. Therefore, the operation phase number is extended from 2 to 4, and the 2-phase PWM VR controller can be used in a 4-phase VR design. Figure 4 shows the 2-phase to 4-phase PWM extension.

For the PWM controller uses its PWM pin as a multifunction pin,a resistor will be connected from PWM pin to GND to set parameter. Note that this resistor must be greater than  $15 \text{K}\Omega$ . Lower resistor value will cause incorrect PWM voltage level at the PWM pin when the PWM controller output is in tri-state (high-impedance state).

Figure 3. Sequence of PWM1, PWMA and PWMC

Figure 4. Sequence of PWM[1,2] and PWM[A:D]

## **Functional Description**

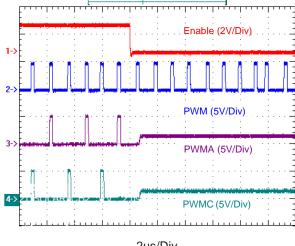

#### **Enable**

Logic low of EN disables all PWM outpus off and tie the EN pin to controller.

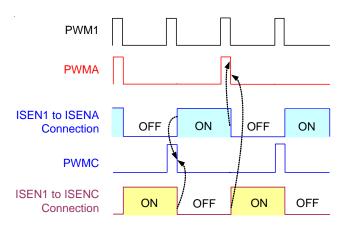

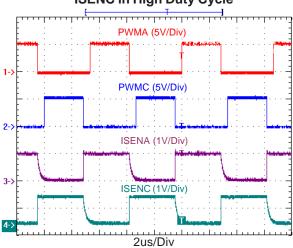

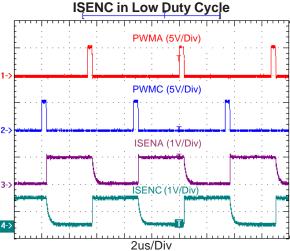

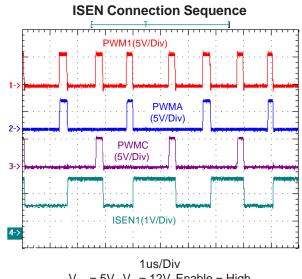

#### **ISEN Connection Sequence**

The uP1911R provides two individual sequence circuits to control the ISEN connection sequence. The ISEN connection sequence. The ISEN connection sequence is for LGATE sensing or DCR sensing. When SWMODE connects to GND, Figure 5 shows the sequence of PWM outputs and the ISEN connection states. The on-state of the connection betweenISEN1 and ISENA begins at the PWMC falling edge, and it ends at the next PWMA falling edge. The on-state of the connection between ISEN1 and ISENA allows switching node voltage signal passing from ISENA to ISEN1. The operational principle of ISEN1 to ISENC is similar as described above. The on-state of the connection between ISEN1 and ISENC begins at the PWMA falling edge, and it ends at the next PWMC falling edge.

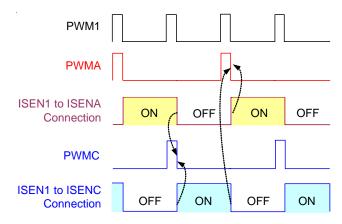

When SWMODE connects to 5VCC, Figure 6 shows the sequence of PWM outputs and the ISEN connection states. The on-state of the connection between ISEN1 and ISENA begins at the PWMA falling edge, and it ends at the next PWMC falling edge. The on-state of the connection between ISEN1 and ISENA allows switching node voltage signal passing from ISENA to ISEN1. The operational principle of ISEN1 to ISENC is similar as described above. The onstate of the connection between ISEN1 and ISENC begins at the PWMC falling edge, and it ends at the next PWMA falling edge.

The connection between ISEN1 to ISENA and ISEN1 to ISENC changes in an alternating way. That is to say when ISEN1 to ISENA connection is ON, ISEN1 to ISENC connection is OFF, and vice versa.

There is a break-before-make delay time to ensure that ISENA and ISENC never connect to each other. ISEN2 and ISEN[B,D] works in a similar way.

Figure 5. Sequence of PWM Outputs and ISEN Connection States

Figure 6. Sequence of PWM Outputs and ISEN

Connection States

|                                                           | Absolute Maximum Rating                              |

|-----------------------------------------------------------|------------------------------------------------------|

| (Note 1)                                                  |                                                      |

| Supply Input Voltage 12VCC                                |                                                      |

| ISENA~D/ISEN1~2/EN/SWMODE/PWM1~2                          |                                                      |

| Storage Temperature Range                                 |                                                      |

|                                                           | 150°C                                                |

| Lead Temperature (Soldering, 10 sec)                      | 260°C                                                |

| ESD Rating (Note 2)                                       |                                                      |

|                                                           | 2kV                                                  |

| MM (Machine Mode)                                         | Thermal Information                                  |

|                                                           | I hermal Information                                 |

| WQFN3x3 - 16L $\theta_{JC}$                               | 68°C/W                                               |

| Power Dissipation, P <sub>D</sub> @ T <sub>A</sub> = 25°C | 1.47W                                                |

|                                                           |                                                      |

|                                                           | Recommended Operation Conditions                     |

| Operating Ambient Temperature Range                       |                                                      |

| Note 1. Stresses listed as the above Absolute Maximu      | um Ratings may cause permanent damage to the device. |

- These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

- Note 2. Devices are ESD sensitive. Handling precaution recommended.

- **Note 3.**  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}\text{C}$  on a low effective thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

- **Note 4.** The device is not guaranteed to function outside its operating conditions.

- Note 5. Guaranteed by design.

## Electrical Characteristics

(Test Condition: 12VCC = 12V,  $T_A = 25^{\circ}C$ , unless otherwise specified)

| Parameter                      | Symbol                | Test Conditions                                                        | Min    | Тур  | Max   | Unit  |

|--------------------------------|-----------------------|------------------------------------------------------------------------|--------|------|-------|-------|

| Supply Input Voltage           | Symbol                | rest conditions                                                        | IVIIII | ТУР  | IVIAX | Oilit |

| POR Threshold                  | 12\/                  | PWM [A:D] outputs enabled                                              | 3.0    | 3.4  | 4.4   | V     |

| POR Hysteresis                 | 12V <sub>CC_RTH</sub> | P VVIVI [A.D] Outputs enabled                                          | 0.1    | 0.3  | 0.46  | V     |

| Supply Input Current           | 12V <sub>CC_HYS</sub> |                                                                        |        | 2.5  | 5.0   | mA    |

| 5VCC Regulated Voltage         | I <sub>12VCC</sub>    | 12VCC = 12V                                                            | 4.95   | 5.20 | 5.45  | V     |

| Analog Switch                  | V <sub>5VCC</sub>     | 12000 = 120                                                            | 4.95   | 5.20 | 5.45  | V     |

|                                | В                     | ISENIA 21 to ISENIA DI ourront - 0.5mA                                 | 100    | 200  | 300   |       |

| On Resistance                  | R <sub>ON</sub>       | ISEN[1,2] to ISEN[A:D] current = 0.5mA                                 | 100    | 200  | 300   | Ω     |

| Analog Switch Dynamic Char     | acteristics           | I                                                                      |        |      |       |       |

| Turn Off Time                  | T <sub>OFF</sub>      | $R_{LOAD} = 10k\Omega$ , $C_{LOAD} = 4.7pF$ , $V_{ISEN} = 1V$ (Note 5) |        | 15   |       | ns    |

| Turn On Time                   | T <sub>ON</sub>       | $R_{LOAD} = 10 k\Omega$ , $C_{LOAD} = 4.7 pF$ $V_{ISEN} = 1V$ (Note 5) |        | 30   |       | ns    |

| Break-Before-Make Delay        | T <sub>DLY</sub>      | $C_{LOAD} = 4.7pF \text{ (Note 5)}$                                    |        | 3.4  |       | ns    |

| PWM Digital Logic Gate Outpu   | ıt Characte           | ristic                                                                 | ,      |      |       |       |

| High-Z to High Threshold Level | V <sub>IH_HiZ-H</sub> |                                                                        |        | 2.34 | 2.80  | V     |

| High to High-Z Threshold Level | V <sub>IL_HiZ-H</sub> | PWM[A:D], $R_{LOAD} = 10k\Omega$ to GND, and                           | 1.80   | 2.18 |       | V     |

| Low to High-Z Threshold Level  | V <sub>IH_L-HiZ</sub> | 10kΩ to 5VCC                                                           |        | 0.83 | 1.20  | V     |

| High-Z to Low Threshold Level  | V <sub>IL_HiZ-L</sub> |                                                                        | 0.40   | 0.67 |       | V     |

| Output High Voltage            | V <sub>OH</sub>       | $R_{LOAD} = 10k\Omega$ to GND                                          | 4.5    | 4.9  |       | V     |

| Output Low Voltage             | V <sub>OL</sub>       | $R_{LOAD} = 10k\Omega$ to 5VCC                                         |        | 0.1  | 0.4   | V     |

| Output Minimum Low Time        | T <sub>L_MIN</sub>    | PWM[1,2] input = 3.3V to 1.5V (Note 5)                                 |        | 200  |       | ns    |

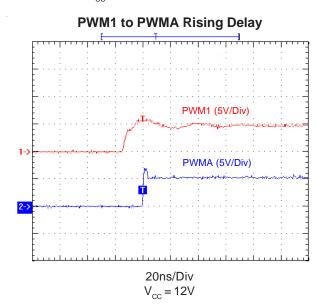

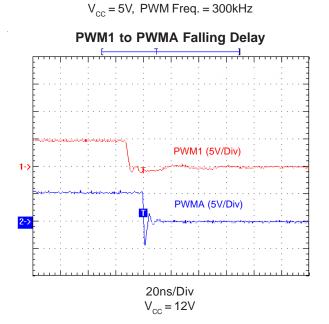

| Output High to Low Delay Time  | T <sub>HL_DLY</sub>   |                                                                        |        | 15   | 60    | ns    |

| Output Low to High Delay Time  | T <sub>LH_DLY</sub>   |                                                                        |        | 15   | 60    | ns    |

| SWMODE Voltage                 |                       |                                                                        | •      |      |       |       |

| Input High                     | V <sub>SW_H</sub>     |                                                                        | 2.2    |      |       | V     |

| Input Low                      | V <sub>sw_L</sub>     |                                                                        |        |      | 0.8   | V     |

| Enable Voltage                 |                       |                                                                        | •      |      |       |       |

| Input High                     | V <sub>EN_H</sub>     |                                                                        | 2.2    |      |       | V     |

| Input Low                      | V <sub>EN_L</sub>     |                                                                        |        |      | 0.8   | V     |

| Enable Delay Time              |                       |                                                                        |        |      |       |       |

| Enable High Delay              | V <sub>EN_H</sub>     |                                                                        | 800    | 2500 | 5000  | ns    |

| Enable Low Delay               | V <sub>EN_L</sub>     |                                                                        | 100    | 500  | 1000  | ns    |

|                                |                       |                                                                        |        |      |       |       |

# **Typical Operation Characteristics**

$V_{CC} = 12V$ , PWM Freq. = 300kHz

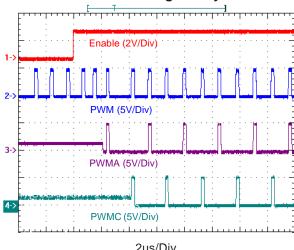

#### Sequence of PWM1, PWMA and PWMC

$V_{cc} = 12V$ , PWM Freq. = 300kHz, D = 10%

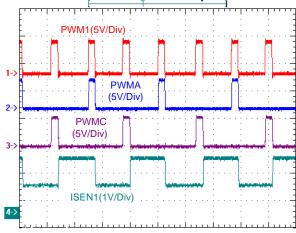

# Sequence of PWMA, PWMC and ISENA, ISENC in High Duty Cycle

$V_{CC} = 12V$ , PWM Freq. = 300kHz, D = 85%,  $V_{ISEN1} = 1V$ , ISENA/C  $R_{LOAD} = 10k\Omega$

### **Enable High to Low Delay Time**

2us/Div  $V_{CC} = 5V, \ V_{IN} = 12V$

## **Typical Operation Characteristics**

# Sequence of PWMA, PWMC and ISENA,

$V_{CC}$  = 12V, PWM Freq. = 300kHz, D = 10%,  $V_{ISEN1}$  = 1V, ISENA/C R<sub>LOAD</sub> = 10k $\Omega$

#### **Enable Low to High Delay Time**

2us/Div  $V_{CC} = 5V, \ V_{IN} = 12V$

#### **ISEN Connection Sequence**

$\label{eq:vcc} \begin{array}{c} \text{1us/Div} \\ \text{V}_{\text{CC}} = \text{5V}, \ \text{V}_{\text{IN}} = \text{12V}, \ \text{Enable} = \text{High} \\ \text{ISENA} = \text{1V}, \ \text{ISENC} = \text{2 V}, \ \text{SWMODE} = \text{High} \\ \end{array}$

## **Typical Operation Characteristics**

$V_{CC} = 5V$ ,  $V_{IN} = 12V$ , Enable = High ISENA = 1V, ISENC = 2 V, SWMODE = Low

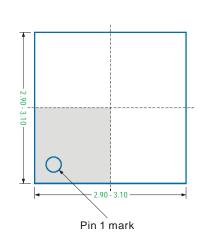

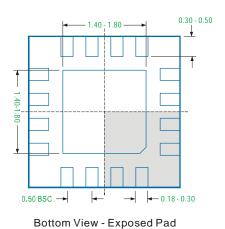

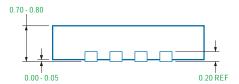

## **Package Information**

#### WQFN3x3-16L

#### Note

1. Package Outline Unit Description:

BSC: Basic. Represents theoretical exact dimension or dimension target

MIN: Minimum dimension specified.

MAX: Maximum dimension specified.

REF: Reference. Represents dimension for reference use only. This value is not a device specification.

TYP. Typical. Provided as a general value. This value is not a device specification.

- 2. Dimensions in Millimeters.

- 3. Drawing not to scale.

- 4. These dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm.

#### **Important Notice**

The contents of this document are provided in connection with uPI Semiconductor Corp. ("uPI") products. uPI makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice.

No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights, is granted by this publication. Except as provided in uPI's terms and conditions of sale for such products, uPI assumes no liability whatsoever, and uPI disclaims any express or implied warranty relating to sale and/or use of uPI products, including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. uPI products are not designed, intended, authorized or warranted for use as components in systems intended for medical, life-saving, or life sustaining applications. uPI reserves the right to discontinue or make changes to its products at any time without notice.

Copyright 2019 ©, uPI Semiconductor Corp. All rights reserved.

uPI, uPI Micro Power Intellect logo, and combinations thereof, are registered trademarks of uPI Semiconductor Corp. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

uPI Semiconductor Corp.

9F.,No.5, Taiyuan 1st St. Zhubei City, Hsinchu, Taiwan, R.O.C. TEL: 886.3.560.1666 FAX: 886.3.560.1888