# 2A Ultra Low Dropout Linear Regulator for DDR4 Memory VTT Termination

## **General Description**

The uP8817Q is an ultra low dropout regulator for Double Date Rate (DDR) termination system. It is specifically designed for low input voltage and low external component count systems. The uP8817Q is capable of sinking/sourcing up to 2A output current, providing fast load transient and only requires a minimum 3x10uF ceramic output capacitor. The uP8817Q supports all power requirements for DDR VTT bus termination, DDR4 especially. Other features include thermal protection, bi-directional current limit protection. The uP8817Q is available in a PSOP-8L package.

# Ordering Information

| Order Number | Package | Top Marking |

|--------------|---------|-------------|

| uP8817QSW8   | PSOP-8L | uP8817Q     |

### Note:

- (1) Please check the sample/production availability with uPl representatives.

- (2) uPI products are compatible with the current IPC/JEDEC J-STD-020 requirement. They are halogen-free, RoHS compliant and 100% matte tin (Sn) plating that are suitable for use in SnPb or Pb-free soldering processes.

# \_\_\_\_\_ Features

- VIN Input Voltage Range: 1V to 3.6V

- VCNTL Input Voltage: 2.9V to 5.5V

- Low External Component Count

- Enable/Disable Control from REFIN

- Discharge MOSFET at VOUT Shutdown

- Up to 2A Source/Sink Current

- Support DDR3 and Low Power DDR3/DDR4

- Stable with Pure MLCC as Output Cap

- RoHS Compliant and Halogen Free

# Applications

- DDR Memory Termination

- Desktop PCs, Notebook Computers, and Server

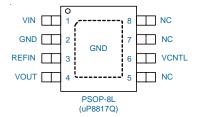

.Pin Configuration

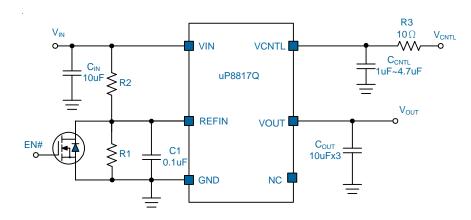

# **Typical Application Circuit**

# Functional Pin Description

| Pin No. | Name   | Pin Function                                                                                                                                                                                                                                                                                                                                                               |  |

|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1       | VIN    | <b>Input Voltage.</b> This is the drain input to the power device that supplies current the output pin. Use a ceramic capacitor of at least 10uF on the uP8817Q Input stability and improving transient response.                                                                                                                                                          |  |

| 2       | GND    | Ground.                                                                                                                                                                                                                                                                                                                                                                    |  |

| 3       | REFIN  | Reference Input. The input to REFIN also controls enable/disable state of this device.                                                                                                                                                                                                                                                                                     |  |

| 4       | VOUT   | Output Voltage. This pin is the power output of the device. A minimum capacitance of 10uFx3 output capacitor is recommended. And the maximum is 50uF capacitor.                                                                                                                                                                                                            |  |

| 5       | NC     | No Internal Connection.                                                                                                                                                                                                                                                                                                                                                    |  |

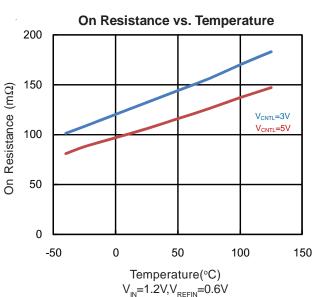

| 6       | VCNTL  | <b>Supply Input for Control Circuit.</b> This pin provides bias voltage to the control circuitry and driver for the pass transistor. The driving capability of output current is proportioned to the V <sub>CNTL</sub> . For the device to regulate, the voltage on this pin must be at least 1.5V greater than the output voltage, and no less than V <sub>CNTL MIN</sub> |  |

| 7       | NC     | No Internal Connection.                                                                                                                                                                                                                                                                                                                                                    |  |

| 8       | NC     | No Internal Connection.                                                                                                                                                                                                                                                                                                                                                    |  |

| Expos   | ed Pad | <b>Ground.</b> The exposed pad is the ground of the IC, and it must be soldered to a large PCB and connect to GND for power dissipation.                                                                                                                                                                                                                                   |  |

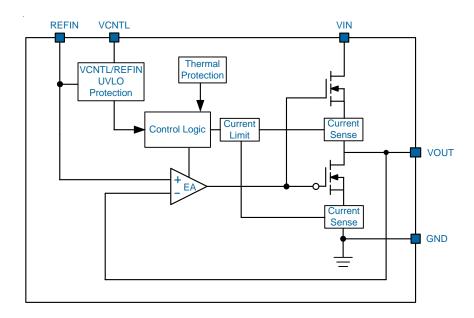

# Functional Block Diagram

# Functional Description

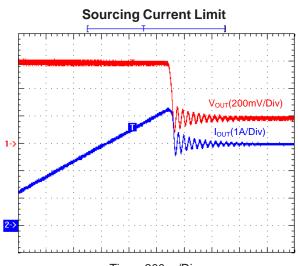

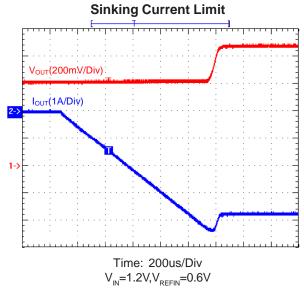

## Source/Sink Current Limit

The uP8817Q monitor sourcing and sinking output currents and it has a constant over current limit by reducing power MOSFET gate voltage. Note that the current limit level will be reduced to short circuit current limit level when the output voltage is short to ground. This current limit function is a non-latch protection.

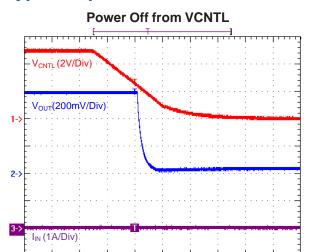

## **VCNTL UVLO Protection**

This device provides UVLO function by monitoring the input voltage to VCNTL pin. If  $V_{\text{CNTL}}$  is less than the UVLO threshold voltage,  $V_{\text{OUT}}$  regulator is powered off.

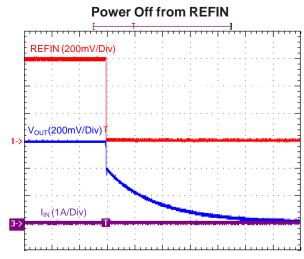

## **REFIN**

The REFIN also provides UVLO protection. And It can be set by external voltage divider connected to the memory supply bus (VDDQ). When the REFIN voltage is below shutdown threshold, the regulator is turned off.

|                                                                                                                                                                                                                    | Absolute Maximum Rating                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| (Note 1)                                                                                                                                                                                                           | •                                            |

| Control Input Voltage, V <sub>CNTL</sub>                                                                                                                                                                           |                                              |

| DC                                                                                                                                                                                                                 |                                              |

| <200ns                                                                                                                                                                                                             |                                              |

| Power Input Voltage, V <sub>IN</sub>                                                                                                                                                                               |                                              |

| DC                                                                                                                                                                                                                 |                                              |

| <200ns                                                                                                                                                                                                             |                                              |

| Other Pins                                                                                                                                                                                                         |                                              |

| Storage Temperature Range                                                                                                                                                                                          |                                              |

| Junction Temperature                                                                                                                                                                                               | 150°C                                        |

| Lead Temperature (Soldering, 10 sec)                                                                                                                                                                               | 260°C                                        |

| ESD Rating (Note 2)                                                                                                                                                                                                |                                              |

| HBM (Human Body Mode)                                                                                                                                                                                              | 2kV                                          |

| MM (Machine Mode)                                                                                                                                                                                                  | 200V                                         |

|                                                                                                                                                                                                                    | Thormal Information                          |

|                                                                                                                                                                                                                    | Thermal Information                          |

| Package Thermal Resistance (Note 3)                                                                                                                                                                                |                                              |

| PSOP-8L θ <sub>1A</sub>                                                                                                                                                                                            | 47°C/W                                       |

| PSOP-8L 0 C                                                                                                                                                                                                        | 17.9°C/W                                     |

| Power Dissipation, P <sub>D</sub> @ T <sub>A</sub> = 25°C                                                                                                                                                          |                                              |

| PSOP-8L                                                                                                                                                                                                            | 2.13W                                        |

|                                                                                                                                                                                                                    |                                              |

|                                                                                                                                                                                                                    | mmended Operation Conditions                 |

| (Note 4)                                                                                                                                                                                                           |                                              |

| Operating Junction Temperature Range                                                                                                                                                                               |                                              |

| Operating Ambient Temperature Range                                                                                                                                                                                |                                              |

| Supply Input Voltage, V <sub>IN</sub>                                                                                                                                                                              | +1V to +3.6V                                 |

| Supply Input Voltage, V <sub>CNTL</sub>                                                                                                                                                                            | +2.9V to +5.5V                               |

| <b>Note 1.</b> Stresses listed as the above <i>Absolute Maximum Ratings</i> m<br>These are for stress ratings. Functional operation of the dev<br>those indicated in the operational sections of the specification | rice at these or any other conditions beyond |

- maximum rating conditions for extended periods may remain possibility to affect device reliability. **Note 2.** Devices are ESD sensitive. Handling precaution recommended.

- Note 3.  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}\text{C}$  on a low effective thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

- Note 4. The case temp location for measuring  $\theta_{\text{JC}}$  is on the top of the package.

- Note 5. The device is not guaranteed to function outside its operating conditions.

# Electrical Characteristics

$(V_{CNTL} = 5V, C_{OUT} = 10uFx3, T_{A} = 25^{\circ}C, unless otherwise specified)$

| Parameter                    | Symbol                   | Test Conditions                                        | Min   | Тур   | Max   | Units |

|------------------------------|--------------------------|--------------------------------------------------------|-------|-------|-------|-------|

| VCNTL Supply Input           |                          |                                                        |       | •     |       |       |

| VCNTL POR Threshold          | V <sub>CNTLRTH</sub>     | V <sub>CNTLRTH</sub> rising                            | 2.5   | 2.7   | 2.85  | V     |

| VCNTL POR Hysteresis         | V <sub>CNTLHYS</sub>     | V <sub>CNTLRTH</sub> falling                           |       | 0.2   |       | V     |

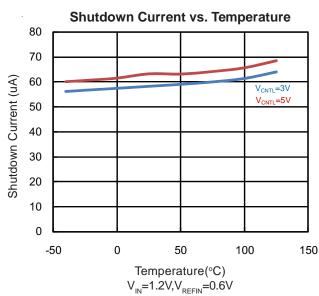

| VCNTL Shutdown Current       | I <sub>SD_VCNTL</sub>    | V <sub>REFIN</sub> = 0V, I <sub>OUT</sub> =0A          |       | 65    | 80    | uA    |

| VCNTL Input Current          | I <sub>VCNTL</sub>       | $V_{CNTL} = 5V$ , $I_{OUT} = 0A$ , $V_{REFIN} > 0.4V$  |       | 0.7   | 1     | mA    |

| VIN Supply Input             |                          |                                                        | -     |       |       |       |

| VIN Supply Current           | I <sub>VIN</sub>         | $V_{CNTL} = 5V$ , $I_{OUT} = 0A$ , $V_{REFIN} > 0.4V$  |       | 1     | 50    | uA    |

| VIN Shutdown Current         | I <sub>SHDN_VIN</sub>    | V <sub>REFIN</sub> = 0V, No Load                       |       | 0.1   | 50    | uA    |

| Output Voltage               |                          | -                                                      |       |       |       |       |

|                              |                          | $V_{IN} = 1.5V, V_{REFIN} = 0.75V; I_{OUT} = 0A$       | 0.735 | 0.75  | 0.765 |       |

| Output Voltage               | V <sub>OUT</sub>         | $V_{IN} = 1.35V, V_{REFIN} = 0.675V; I_{OUT} = 0A$     | 0.66  | 0.675 | 0.69  | V     |

|                              |                          | $V_{IN} = 1.2V, V_{REFIN} = 0.6V; I_{OUT} = 0A$        | 0.585 | 0.6   | 0.615 |       |

|                              |                          | $I_{OUT} = \pm 2A, V_{IN} = 1.5V, V_{REFIN} = 0.75V$   | -25   |       | 25    |       |

| VOUT Voltage Offset to REFIN | V <sub>OUT_OS</sub>      | $I_{OUT} = \pm 2A, V_{IN} = 1.35V, V_{REFIN} = 0.675V$ | -25   |       | 25    | mV    |

|                              |                          | $I_{OUT} = \pm 2A, V_{IN} = 1.2V, V_{REFIN} = 0.6V$    | -25   |       | 25    |       |

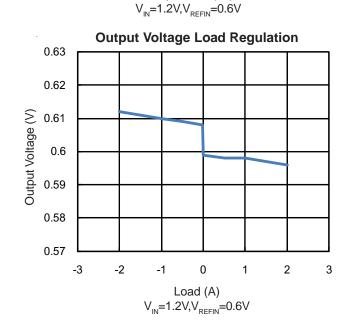

| Load Regulation              | $\Delta V_{LOAD}$        | -1A < I <sub>OUT</sub> <1A                             | -20   |       | 20    | mV    |

| VOUT Discharge Resistance    | R <sub>DISCHARGE</sub>   | $V_{REFIN} = 0V, V_{OUT} = 0.3V$                       |       | 18    | 25    | Ω     |

| VOUT Source Current Limit    | I <sub>LIM_VOUT_SR</sub> |                                                        | 3.5   | 4.5   | 5.5   | Α     |

| VOUT Sink Current Limit      | LIM_VOUT_SK              |                                                        | 3.5   | 4.5   | 5.5   | А     |

| REFIN                        |                          |                                                        |       |       |       |       |

| REFIN Logic High Threshold   | V <sub>ENH</sub>         | REFIN rising to enable the device                      | 360   | 390   | 420   | mV    |

| REFIN Hysteresis             | V <sub>HYS</sub>         |                                                        |       | 20    |       | mV    |

| REFIN Input Current          | <br> REFIN               |                                                        |       |       | 1     | uA    |

| REFIN Voltage Range          | V <sub>REFIN</sub>       |                                                        | 0.5   |       | 1.8   | V     |

| Soft Start                   | 1                        |                                                        |       |       |       |       |

| Soft Start Time              | T <sub>ss</sub>          | $V_{IN} = 1.2V, V_{OUT} = 0.6V$                        |       |       | 35    | us    |

| Thermal Protection           |                          | 1                                                      |       |       | 1     |       |

| Thermal Shutdown Temperature | T <sub>SD</sub>          |                                                        |       | 160   |       | °C    |

| Thermal Shutdown Hysteresis  | T <sub>SDH_HYS</sub>     |                                                        |       | 30    |       | °C    |

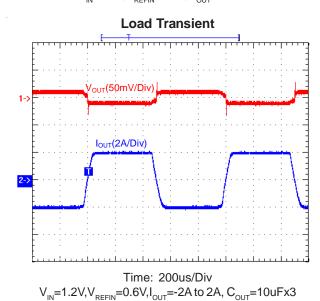

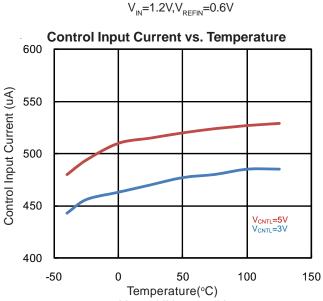

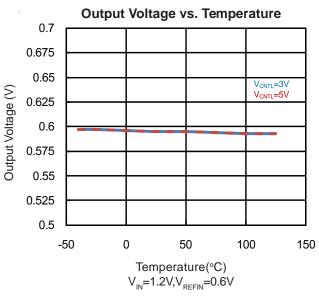

# **Typical Operation Characteristics**

# Power On from VCNTL VcNrL (2V/Div) Vour(200mV/Div) 1-> 2->

$\label{eq:continuity} \begin{aligned} & \text{Time: 10us/Div} \\ & \textit{V}_{\text{IN}} = 1.2 \textit{V}, \textit{V}_{\text{REFIN}} = 0.6 \textit{V}, \textit{C}_{\text{OUT}} = 10 \textit{uFx3} \end{aligned}$

# Power On from REFIN REFIN (200mV/Div) Vour(200mV/Div) IN (1A/Div)

Time: 10us/Div  $V_{IN}$ =1.2V, $V_{REFIN}$ =0.6V, $C_{OUT}$ =10uFx3

Time: 4ms/Div  $V_{IN}$ =1.2V, $V_{REFIN}$ =0.6V, $C_{OUT}$ =10uFx3

$\label{eq:constraints} \begin{aligned} & \text{Time: 200us/Div} \\ & \textit{V}_{\text{IN}} = 1.2 \textit{V}, \textit{V}_{\text{REFIN}} = 0.6 \textit{V}, \textit{C}_{\text{OUT}} = 10 u Fx3 \end{aligned}$

Time: 200us/Div  $V_{IN}$ =1.2V, $V_{REFIN}$ =0.6V

# **Typical Operation Characteristics**

# Application Information

The uP8817Q is an ultra low dropout linear regulator specifically designed to provide termination voltage for DDR memory system. Designed with low on-resistance NMOSFETs, this device is capable of sinking/sourcing up to 2A output current. The output voltage is tightly regulated to track reference voltage input with fast to line/load transient.

## Supply Voltage for Control Circuit VCNTL

This uP8817Q works with dual supplies, a control input for the control circuitry and a power input as low as 1.0V for providing current to output. The control input provides bias current for control circuit and gate voltage for turning on and off the NMOSFETs. It is highly recommended to keep the control input 1.5V higher than the output voltage for optimal performance. The control voltage should be locally bypassed by a minimum 1uF ceramic capacitor plus a  $10\Omega$  resistor.

# Power Input Capacitor ( $C_{IN}$ ) and Control Input Capacitor ( $C_{CNTL}$ )

The VIN pin supplies current to output when the upper MOSFET turns on. The uP8817Q is designed to work with minimum 10uF ceramic input capacitor. When work with large output capacitor, the uP8817Q may demand large input current during soft start. Make sure the power input is capable of delivering up to 2A.

Table 1 Component Recommended Value

| Component         | Recommended Value                 |  |

|-------------------|-----------------------------------|--|

| C <sub>CNTL</sub> | 1uF ~ 4.7uF Ceramic Capacitor     |  |

| C <sub>IN</sub>   | 10uF or greater Ceramic Capacitor |  |

## **Reference Input**

The output voltage is regulated to track the reference input at REFIN pin. The reference input can be obtained from power input by voltage divider or from an independent voltage reference. A ceramic capacitor physically near the IC is required to filter the reference voltage.

## Output Voltage and Output Capacitor, Cour

The uP8817Q is designed to work with low ESR ceramic capacitors. Attach three, 10-uF ceramic capacitors in parallel to minimize the effect of equivalent series resistance (ESR) and equivalent series inductance (ESL).

## **Thermal Consideration**

The uP8817Q integrates internal thermal limiting function to protect the device from damage during fault conditions. However, continuously keeping the junction near the thermal shutdown temperature may remain possibility to affect device reliability. It is highly recommended to keep the junction temperature below the recommended operation condition 125°C for maximum reliability. Power dissipation in the device is calculated as:

$$P_D = (V_{IN} - V_{OUT}) \times I_{OUT} + V_{CNTL} \times I_{CNTL}$$

It is adequate to neglect power loss with respective to control circuit  $V_{CNTL}$  x  $I_{CNTL}$  when considering thermal management in uP8817Q. This power dissipation is conducted through the package into the ambient environment, and, in the process, the temperature of the die  $(T_J)$  rises above ambient. Large power dissipation may cause considerable temperature raise in the regulator in large dropout applications. The geometry of the package and of the printed circuit board (PCB) greatly influence how quickly the heat is transferred to the PCB and away from the chip. The most commonly used thermal metrics for IC packages are thermal resistance from the chip junction to the ambient air surrounding the package  $(\Delta T_{IA})$ :

$$\theta_{JA} = (T_J - T_A) / P_D$$

$\theta_{JA}$  specified in the Thermal Information section is measured in the natural convection at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity test board (4 Layers, 2S2P) of JEDEC 51-5 thermal measurement standard. Given power dissipation  $P_D$ , ambient temperature and thermal resistance  $\theta_{JA}$ , the junction temperature is calculated as:

$$T_{J} = T_{A} + \Delta T_{JA} = T_{A} + P_{D} \times \theta_{JA}$$

To limit the junction temperature within its maximum rating, the allowable maximum power dissipation is calculated as:

$$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = \left(\;\mathsf{T}_{\mathsf{J}(\mathsf{MAX})}\;\mathsf{-T}_{\mathsf{A}}\right)\;/\;\theta_{\mathsf{JA}}$$

where  $\rm T_{\rm J(MAX)}$  is the maximum operation junction temperature 125°C,  $\rm T_{\rm A}$  is the ambient temperature and the  $\theta_{\rm JA}$  is the junction to ambient thermal resistance.

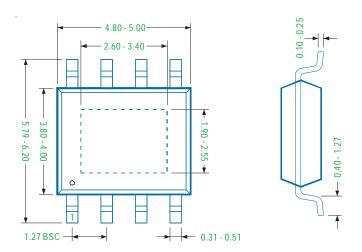

# Package Information

## PSOP - 8L

## Note

- 1. Package Outline Unit Description:

- BSC: Basic. Represents theoretical exact dimension or dimension target

- MIN: Minimum dimension specified.

- MAX: Maximum dimension specified.

- REF: Reference. Represents dimension for reference use only. This value is not a device specification.

- TYP. Typical. Provided as a general value. This value is not a device specification.

- 2. Dimensions in Millimeters.

- 3. Drawing not to scale.

- 4. These dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm.

## **Important Notice**

The contents of this document are provided in connection with uPI Semiconductor Corp. ("uPI") products. uPI makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice.

No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights, is granted by this publication. Except as provided in uPI's terms and conditions of sale for such products, uPI assumes no liability whatsoever, and uPI disclaims any express or implied warranty relating to sale and/or use of uPI products, including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. uPI products are not designed, intended, authorized or warranted for use as components in systems intended for medical, life-saving, or life sustaining applications. uPI reserves the right to discontinue or make changes to its products at any time without notice.

Copyright 2019 ©, uPI Semiconductor Corp. All rights reserved.

uPI, uPI Micro Power Intellect logo, and combinations thereof, are registered trademarks of uPI Semiconductor Corp. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

uPI Semiconductor Corp.

9F.,No.5, Taiyuan 1st St. Zhubei City, Hsinchu, Taiwan, R.O.C. TEL: 886.3.560.1666 FAX: 886.3.560.1888