. Features

# 1MHz, 2.0A, High-Efficiency Synchronous-Rectified Buck Converter

## **General Description**

The uP9617 is a high efficiency synchronous-rectified buck converter with internal power switches. Fixed 1MHz PWM operation allows possible smallest output ripple and external component size. With high conversion efficiency and small package, the uP9617 is ideally suitable for portable devices and USB/PCIE-based interface cards where PCB area is especially concerned.

With internal low R<sub>DS(ON)</sub> switches, the uP9617 is capable of delivering 2.0A output current over a wide input voltage range from 2.6V to 5.5V. The output voltage is adjustable from 0.6V to V<sub>IN</sub> by a voltage divider. Other features include internal soft-start, chip enable, over-voltage, undervoltage, over-temperature and over-current protections. The uP9617 is available in a space-saving WQFN3x3-16L package.

## **Applications**

- Battery-Powered Portable Devices

- MP3 Players

- Digital Still Cameras

- Wireless and DSL Modems

- Personal Information Appliances

- 802.11 WLAN Power Supplies

- FPGA/ASIC Power Supplies

- Dynamically Adjustable Power Supply for CDMA/WCSMA Power Amplifiers

- USB-Based xDSL Modems and Other Network Interface Cards

- Point-of-Load Regulation

- 2.6V to 5.5V Input Voltage Range

- ☐ Adjustable Output from 0.6V to V<sub>IN</sub>

- Guaranteed 2.0A Output Current

- Accurate Reference: 0.6V (± 1.5%)

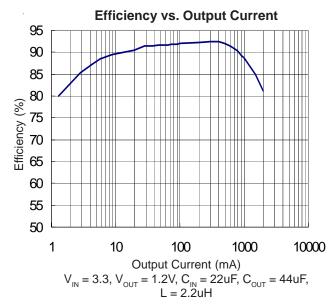

- Up to 95% Conversion Efficiency

- Low Quiescent Current

- Integrated Low R<sub>DS(ON)</sub> Upper and Lower MOSFET Switches: 100m $\Omega$  and 85m $\Omega$

- Current Mode PWM Operation

- ☐ Fixed Frequency: 1MHz

- 100% Maximum Duty Cycle for Lowest Dropout

- Internal Soft-Start

- No Schottky Diode Required

- Over-Voltage and Under-Voltage Protection

- Over-Temperature and Over-Current Protection

- WQFN3x3-16L Package

- RoHS Compliant and Halogen Free

## **Ordering Information**

| Order Number | Package Type | Top Marking |  |  |

|--------------|--------------|-------------|--|--|

| uP9617PQDD   | WQFN3x3-16L  | uP9617P     |  |  |

#### Note:

- (1) Please check the sample/production availability with uPI representatives.

- (2) uPI products are compatible with the current IPC/JEDEC J-STD-020 requirement. They are halogen-free, RoHS compliant and 100% matte tin (Sn) plating that are suitable for use in SnPb or Pb-free soldering processes.

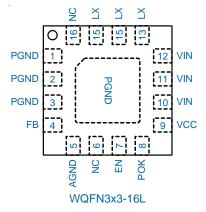

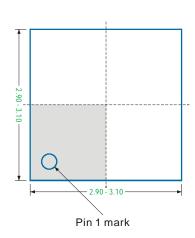

**Pin Configuration**

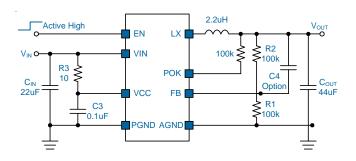

## Typical Application Circuit

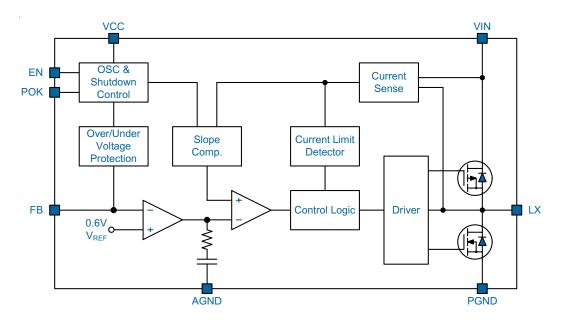

## Functional Block Diagram

# Functional Pin Description

| Pin No.       | Pin Name | Pin Function                                                                                                                                                                                             |  |  |  |

|---------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PQDD          | Pin Name | Pin Function                                                                                                                                                                                             |  |  |  |

| 1,2,3         | PGND     | Power Ground. Connect to the output and input capacitors return.                                                                                                                                         |  |  |  |

| 4             | FB       | <b>Feedback Input.</b> This pin is the inverting input of the error amplifier. FB senses the switcher output through an external resistor divider network.                                               |  |  |  |

| 5             | AGND     | Signal Ground. Connect the return of all small signal componenets to this pin.                                                                                                                           |  |  |  |

| 6,16          | NC       | Not Internally Connected. This pin should be left floating.                                                                                                                                              |  |  |  |

| 7             | EN       | Chip Enable (Active High). Logic low shuts down the converter.                                                                                                                                           |  |  |  |

| 9             | VCC      | <b>Bias Supply.</b> Supplies power for the internal circuitry. Connect to input power via low pass filter with decoupling to AGND.                                                                       |  |  |  |

| 10,11,12      | VIN      | <b>Power Supply Input.</b> Input voltage that supplies current to the output voltage and powers the internal control circuit. Bypass the input voltage with a minimum 10uF X5R or X7R ceramic capacitor. |  |  |  |

| 13,14,15      | LX       | Internal Switches Output. Connect these pins to the output inductor.                                                                                                                                     |  |  |  |

| 8             | POK      | <b>Power OK Indication</b> . This pin is set high impedance after soft start end and no fault occurs.                                                                                                    |  |  |  |

| I EVINCEN PAN |          | <b>Power Ground.</b> The exposed pad should be well soldered to PCB with multiple vias to ground plane for optimal thermal performance.                                                                  |  |  |  |

## Functional Description

The uP9617 is a high efficiency synchronous-rectified buck converter with internal power switches. Fixed 1.0MHz PWM operation allows possible smallest output ripple and external component size. With high conversion efficiency and small package, the uP9617 is ideally suitable for portable devices and USB/PCIE-based interface cards where PCB area is especially concerned.

With internal low  $R_{\rm DS(ON)}$  switches, the uP9617 is capable of delivering 2.0A output current over a wide input voltage range from 2.6V to 5.5V. The output voltage is adjustable from 0.6V to  $V_{\rm IN}$  by a voltage divider. Other features include internal soft-start, chip enable, over voltage, under-voltage, over-temperature and over-current protections. The uP9617 is available in a space-saving WQFN3x3-16L, WLCSP1.5x1.5-9B or PSOP-8L packages.

### Input Supply Voltages, V<sub>IN</sub> & V<sub>CC</sub>

The uP9617 features seperate power supply and ground pins for power stages and control circuit, isolating the control circuit from noise associated with the power MOSFET switching.

The VIN pins provide current to the power stage. The supply voltage range is from 2.6V to 5.5V. The uP9617 draws pulsed current with sharp edges from  $V_{\rm IN}$  each time the upper switch turns on, resulting in voltage ripples and spikes at supply input. A minimum 10uF ceramic capacitor with shortest PCB trace is highly recommended for bypassing the supply input.

The VCC pin provides currents for the internal control circuit. A power on reset (POR) continuously monitors the input supply voltage. The POR level is typically 2.3V at  $V_{\rm cc}$  rising. Use low pass filter R3 and C3 as shown in the Typical Application Circuit to filter the input noise associated with the power switching.

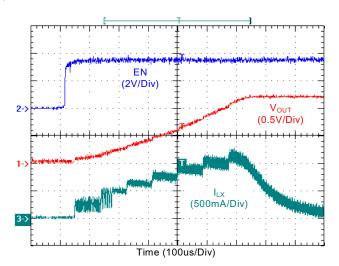

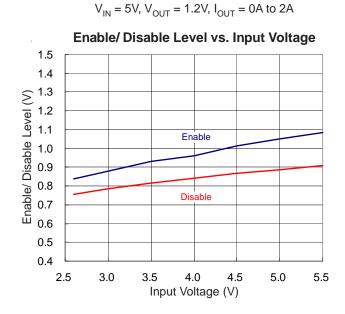

#### Chip Enable/Disable and Soft Start

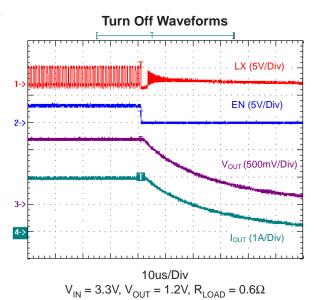

The uP9617 features an EN pin for enable/disable control of the output voltage. Pulling the EN pin lower than 0.4V shuts down the uP9617 and reduces its quiescent current lower than 1uA. In the shutdown mode, both upper and lower switches are turned off.

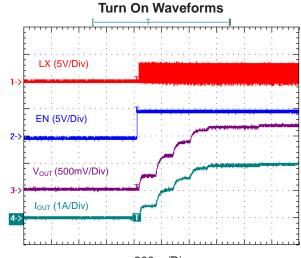

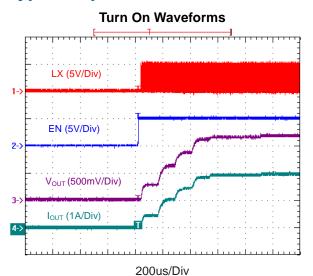

Pulling EN pin higher than 1.5V enables the uP9617 and initiates the softstart cycle once the  $V_{\rm CC}$  POR is granted. The inductor current is limited to fractions of its rated value during the softstart cycle. Figure 1 illustrates the softstart behavior of the uP9617. The inductor current ramps up stairwisely with 250mA increments and 60us duration each step. Note that the output capacitor is large to illustrate the whole softstart behavior. The output voltage may ramp up to its target level in 2 or 3 steps in real applications

where output capacitor is about 22uF.

Figure 1. Softstart of uP9617.

The uP9617 asserts end of soft start and set the current limit to its normal level when the soft start duration expires. After soft start end, the POK pin is set high impedance if no fault occurs.

### **PWM Operation**

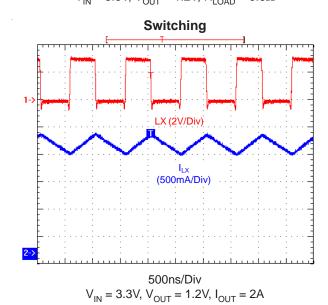

The uP9617 adopts slope-compensated, current mode PWM control capable of achieving 100% duty cycle. During normal operation, the uP9617 operates at PWM mode to regulate output voltage by transferring the power to the output voltage cycle by cycle at a constant 1.0MHz frequency. The uP9617 turns on the upper switch at each rising edge of the internal oscillator allowing the inductor current to ramp up linearly. The switch remains on until either the current-limit is tripped or the PWM comparator turns off the switch for regulating output voltage. The upper switch current is sensed, slope compensated and compared with the error amplifier output COMP to determine the adequate duty cycle. The VOUT pin senses output feedback voltage from an external resistive divider.

When the load current increases, it causes a slight decrease in the feedback voltage relative to the 0.6V reference, which in turn, causes the error amplifier output voltage to increase until the average inductor current matches the new load current.

### **Low Dropout Mode**

The uP9617 increases duty cycle to maintain output voltage within its regulation as the supply input drops gradually in the battery-powered applications. The uP9617 operates with 100% duty cycle and enters low dropout mode as the supply input approaches the output voltage. This maximizes the battery life.

## Functional Description

### **Output Voltage Setting and Feedback Network**

The output voltage can be set from  $V_{REF}$  to  $V_{IN}$  by a voltage divider as:

$$V_{OUT} = \frac{R1 + R2}{R1} \times V_{REF}$$

The internal  $V_{\text{REF}}$  is 0.6V with 1.5% accuracy. In real applications, a 22pF feedforward ceramic capacitor is recommended in parallel with R2 for better transient response.

#### **Current Limit Function**

The uP9617 continuously monitors the inductor current for current limit by sensing the voltage drop across the upper switch when it turns on. When the inductor current is higher than current limit threshold (3.0A typical), the current limit function activates and forces the upper switch turning off to limit inductor current cycle by cycle. If the load continuously demands more current than what uP9617 could provide, uP9617 can not regulate the output voltage. Eventually under voltage protection will be triggered and shuts down the uP9617 if  $\mbox{V}_{\mbox{OUT}}$  is too low.

### **Under Voltage Protection**

Under voltage Protection is triggered if the FB voltage is lower than 0.3V and shuts down uP9617. The under voltage protection is hiccup type.

### **Over Temperature Protection (OTP)**

The OTP is triggered and shuts down the uP9617 if the junction temperature is higher than 150°C. The OTP is a non-latch type protection. The uP9617 automatically initiates another soft start cycle if the junction temperature drops below 130°C.

|                                                                  | Absolute Maximum Rating                                 |

|------------------------------------------------------------------|---------------------------------------------------------|

| (Note 1)                                                         | •                                                       |

| Supply Input Voltage, V <sub>IN</sub> , V <sub>CC</sub>          | 0.3V to +6.5V                                           |

| LX Pin Voltage                                                   |                                                         |

| DC                                                               | 0.3V to +( $V_{IN}$ +0.3V)                              |

| <50ns                                                            | 5V to + $(V_{IN} + 5V)$                                 |

| Other Pins                                                       |                                                         |

| Storage Temperature Range                                        |                                                         |

| Junction Temperature                                             |                                                         |

| Lead Temperature (Soldering, 10 sec)                             | 260°C                                                   |

| ESD Rating (Note 2)                                              |                                                         |

| HBM (Human Body Mode)                                            |                                                         |

| MM (Machine Mode)                                                | 200V                                                    |

|                                                                  |                                                         |

|                                                                  | Thermal Information                                     |

| Package Thermal Resistance (Note 3)                              | Thermal Information                                     |

| Package Thermal Resistance (Note 3)  WQFN3x3-16L θ <sub>10</sub> |                                                         |

| WQFN3x3-16L $\theta_{JA}$                                        | 68°C/W                                                  |

| WQFN3x3-16L $\theta_{JA}$                                        | 68°C/W                                                  |

| WQFN3x3-16L $\theta_{JA}$                                        | 68°C/W<br>6°C/W                                         |

| WQFN3x3-16L $\theta_{JA}$                                        | 68°C/W<br>6°C/W                                         |

| $WQFN3x3-16L \theta_{JA}$                                        | 68°C/W<br>6°C/W<br>1.47W<br>nended Operation Conditions |

| $WQFN3x3-16L \theta_{JA}$                                        |                                                         |

| $WQFN3x3-16L \theta_{JA}$                                        |                                                         |

- **Note 1.** Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

- Note 2. Devices are ESD sensitive. Handling precaution recommended.

- Note 3.  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}\text{C}$  on a low effective thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

- Note 4. The device is not guaranteed to function outside its operating conditions.

## Electrical Characteristics

$(V_{CC} = V_{IN} = 5V, T_A = 25^{\circ}C, \text{ unless otherwise specified})$

| Parameter                           | Symbol                 | Test Conditions                                        | Min      | Тур  | Max  | Units             |

|-------------------------------------|------------------------|--------------------------------------------------------|----------|------|------|-------------------|

| Supply Current                      |                        |                                                        | <u> </u> | 1    |      | '                 |

| Supply Voltage Range                | V <sub>IN</sub>        | $V_{IN} = V_{CC}$                                      | 2.6      |      | 5.5  | V                 |

| Under Voltage Lockout               | V <sub>UVLO</sub>      | $V_{CC}$ Rising, $V_{EN} = V_{CC}$                     |          |      | 2.5  | \/                |

|                                     |                        | $V_{CC}$ Falling, $V_{EN} = V_{CC}$                    | 2.1      |      |      | - V               |

| Quiescent Current                   | I <sub>Q</sub>         | V <sub>FB</sub> = 0.8V (No Switching)                  |          | 50   |      | uA                |

| Shutdown Current                    | I <sub>SHDN</sub>      | $V_{EN} = 0V$                                          |          | 0.01 | 1    | uA                |

| Reference                           |                        |                                                        | •        |      |      |                   |

| Reference Voltage                   | V <sub>FB</sub>        | I <sub>OUT</sub> = 0mA                                 | 0.59     | 0.60 | 0.61 | V                 |

| Output Voltage Accuracy             | $\Delta V_{OUT}$       | I <sub>OUT</sub> = 0mA                                 | -1.5     |      | +1.5 | %                 |

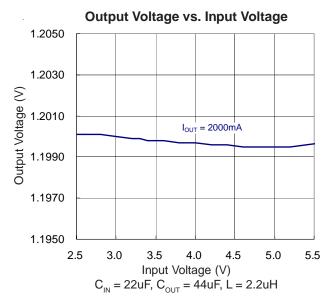

| Output Voltage Line Regulation      | $\Delta V_{OUT}$       | $V_{IN} = 2.6V \text{ to } 5.5V, I_{OUT} = 0\text{mA}$ |          | 0.04 | 0.4  | %/V               |

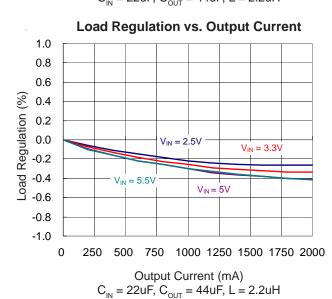

| Output Voltage Load Regulation      | $\Delta V_{OUT}$       | I <sub>OUT</sub> = 0A ~ 2A                             |          | 0.5  |      | %/A               |

| Oscillator                          |                        |                                                        | •        |      |      |                   |

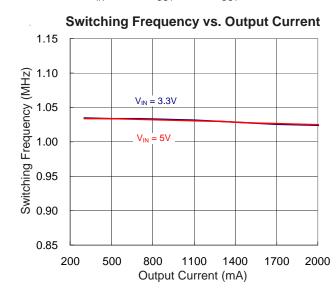

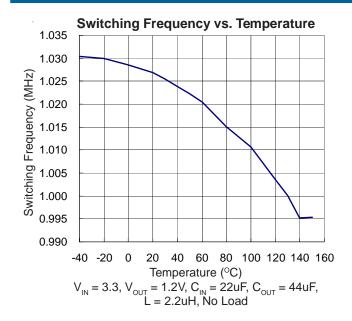

| Switching Frequency Range           | f <sub>osc</sub>       |                                                        | 0.8      | 1.0  | 1.2  | MHz               |

| Maximum Duty Cycle                  | DC                     | $V_{IN} = V_{OUT}$ ; $V_{FB} = 0.55V$                  | 100      |      |      | %                 |

| Power Switches                      |                        |                                                        | •        |      |      |                   |

| R <sub>DS(ON)</sub> of Upper Switch | R <sub>P_FET</sub>     | V <sub>IN</sub> = 3.6V, I <sub>LX</sub> = 100mA        |          | 100  |      | mΩ                |

| R <sub>DS(ON)</sub> of Lower Switch | R <sub>N_FET</sub>     | V <sub>IN</sub> = 3.6V, I <sub>LX</sub> = -100mA       |          | 85   |      | mΩ                |

| Logic Input                         |                        |                                                        | ,        |      |      | •                 |

| EN Logic Low Threshold              | V <sub>IL</sub>        | $V_{IN} = 2.6V$ to 5.5V, Shutdown                      |          |      | 0.4  | V                 |

| EN Logic High Threshold             | V <sub>IH</sub>        | $V_{IN} = 2.6V$ to 5.5V, Enable                        | 1.5      |      |      | V                 |

| Power OK Output                     |                        |                                                        | ·        |      |      |                   |

| Logic High Leakage Current          | I <sub>POK</sub>       | $V_{POK} = V_{CC} = 5V$                                |          |      | 1    | uA                |

| Logic Low Voltage                   | V <sub>POK</sub>       | $I_{POK} = 50uA$                                       |          |      | 0.2  | V                 |

| Protection                          |                        |                                                        |          |      |      |                   |

| FB Under Voltage Protection         | $\Delta_{\rm FB\_UVP}$ | FB Falling                                             |          | 50   |      | %V <sub>REF</sub> |

| Over Current Protection             |                        |                                                        |          | 3    |      | А                 |

| Thermal Shutdwon Temperature        | T <sub>SHDN</sub>      | by design                                              |          | 150  |      | °C                |

| Thermal Shutdown Hysteresis         | $\Delta T_{SHDN}$      | by design                                              |          | 20   |      | °C                |

## **Typical Operation Characteristics**

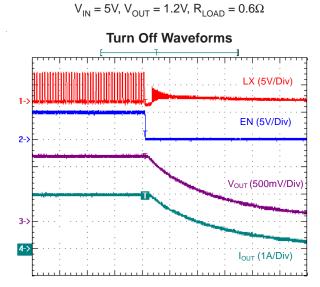

$$\label{eq:vine_policy} \begin{aligned} &200 \text{us/Div} \\ \text{V}_{\text{IN}} = 3.3 \text{V, V}_{\text{OUT}} = 1.2 \text{V, R}_{\text{LOAD}} = 0.6 \Omega \end{aligned}$$

$$500$$

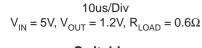

ns/Div

V<sub>IN</sub> = 5V, V<sub>OUT</sub> = 1.2V, I<sub>OUT</sub> = 2A

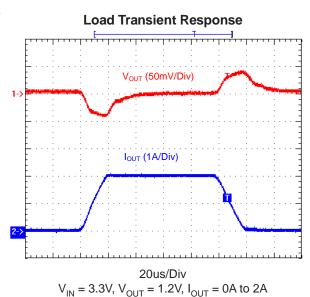

## **Typical Operation Characteristics**

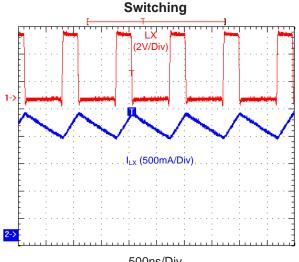

$$V_{IN} = 3.3V$$

,  $V_{OUT} = 1.2V$ ,  $I_{OUT} = 0A$  to  $1A$

### FB vs. Input Voltage 0.605 0.604 0.603 0.602 0.601 € 0.600 © 0.599 0.598 0.597 0.596 0.595 2.5 3.0 4.0 4.5 5.0 5.5 Input Voltage (V) $\label{eq:vin} \begin{aligned} \mathbf{V_{IN}} = 3.3, \, \mathbf{V_{OUT}} = 1.2 \\ \mathbf{V_{IN}} = 2.2 \\ \mathbf{uF}, \, \mathbf{C_{OUT}} = 44 \\ \mathbf{uF}, \\ \mathbf{L} = 2.2 \\ \mathbf{uH}, \, \mathbf{No} \, \, \mathbf{Load} \end{aligned}$

### Line Regulation vs. Input Voltage 0.3 0.2 Line Regulation (%) 0.1 = 2000mA 0.0 -0.1 -0.2 -0.3 2.5 3.0 4.0 5.0 5.5 Input Voltage (V) $C_{IN} = 22uF, C_{OUT} = 44uF, L = 2.2uH$

## **Typical Operation Characteristics**

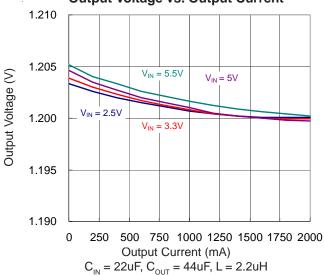

### **Output Voltage vs. Output Current**

# **Typical Operation Characteristics**

## Application Information

### **Output Inductor Selection**

Output inductor selection is usually based the considerations of inductance, rated current value, size requirements and DC resistance (DCR).

The inductance is chosen based on the desired ripple current. Large value inductors result in lower ripple currents and small value inductors result in higher ripple currents. Higher  $V_{IN}$  or  $V_{OUT}$  also increases the ripple current as shown in the equation below. A reasonable starting point for setting ripple current is  $\Delta I_L = 600 \text{mA}$  (30% of 2A).

$$\Delta I_{L} = \frac{1}{f_{OSC} \times L_{OUT}} \times V_{OUT} \times (1 - \frac{V_{OUT}}{V_{IN}})$$

For most applications, the value of the inductor will fall in the range of 1uH to 10uH.

Maximum current ratings of the inductor are generally specified in two methods: permissible DC current and saturation current. Permissible DC current is the allowable DC current that causes 40°C temperature raise. The saturation current is the allowable current that causes 10% inductance loss. Make sure that the inductor will not saturate over the operation conditions including temperature range, input voltage range, and maximum output current. If possible, choose an inductor with rated current higher than 3A so that it will not saturate even under current limit condition.

The size requirements refer to the area and height requirement for a particular design. For better efficiency, choose a low DC resistance inductor. DCR is usually inversely proportional to size.

Different core materials and shapes will change the size/current and price/current relationship of an inductor. Toroid or shielded pot cores in ferrite or permalloy materials are small and don't radiate much energy, but generally cost more than powdered iron core inductors with similar electrical characteristics. The choice of which style inductor to use often depends on the price vs. size requirements and any radiated field/EMI requirements.

### **Input Capacitor Selection**

The uP9617 draws pulsed current with sharp edges from the input capacitor resulting in ripple and noise at the input supply voltage. A minimum 10uF X5R or X7R ceramic capacitor is highly recommended to filter the pulsed current. The input capacitor should be placed as near the device as possible to avoid the stray inductance along the connection trace. Y5V dielectrics, aside from losing

most of their capacitance over temperature, they also become resistive at high frequencies. This reduces their ability to filter out high frequency noise.

The capacitor with low ESR (equivalent series resistance) provides the small drop voltage to stabilize the input voltage during the transient loading. For input capacitor selection, the ceramic capacitors larger than 1uF is recommend. The capacitor must conform to the RMS current requirement. The maximum RMS ripple current is calculated as:

$$I_{IN(RMS)} = I_{OUT(MAX)} \times \frac{\sqrt{V_{OUT} \times (V_{IN} - V_{OUT})}}{V_{IN}}$$

This formula has a maximum at  $V_{IN} = 2xV_{OUT}$ , where  $I_{IN(RMS)} = I_{OUT(MAX)}/2$ . This simple worst-case condition is commonly used for design because even significant deviations do not offer much relief. Note that the capacitor manufacturer's ripple current ratings are often based on 2000 hours of life. This makes it advisable to further derate the capacitor, or choose a capacitor rated at a higher temperature than required. Always consult the manufacturer if there is any question.

### **Output Capacitor Selection**

The uP9617 is specifically design to operate with minimum 10uF X5R or X7R ceramic capacitor. The value can be increased to improve load/line transient performance. Y5V dielectrics, aside from losing most of their capacitance over temperature, they also become resistive at high frequencies. This reduces their ability to filter out high frequency noise.

The ESR of the output capacitor determines the output ripple voltage and the initial voltage drop following a high slew rate load transient edge. The output ripple voltage can be calculated as:

$$\Delta V_{OUT} = \Delta I_{C} \times (ESR + \frac{1}{8 \times f_{OSC} \times C_{OUT}})$$

where  $f_{OSC}$  = operating frequency,  $C_{OUT}$  = output capacitance and  $\Delta I_{C}$  =  $\Delta I_{L}$  = ripple current in the inductor.

The ceramic capacitor with low ESR value provides the low output ripple and low size profile. Connect a 22uF ceramic capacitor at output terminal for good performance and place the input and output capacitors as close as possible to the device.

#### **Using Ceramic Capacitors**

Higher value, lower cost ceramic capacitors are now available in smaller case sizes. Their high ripple current, high voltage rating and low ESR make them ideal for switching regulator applications. Because the uP9617

## Application Information

control loop does not depend on the output capacitor's ESR for stable operation, ceramic capacitors can be used to achieve very low output ripple and small circuit size.

However, care must be taken when these capacitors are used at the input and the output. When a ceramic capacitor is used at the input and the power is supplied by a wall adapter through long wires, a load step at the output can induce ringing at the input,  $V_{\rm IN}$ . At best, this ringing can couple to the output and be mistaken as loop instability. At worst, a sudden inrush of current through the long wires can potentially cause a voltage spike at  $V_{\rm IN}$ , large enough to damage the part.

When choosing the input and output ceramic capacitors, choose the X5R or X7R dielectric formulations. These dielectrics have the best temperature and voltage characteristics of all the ceramics for a given value and size.

#### **Thermal Considerations**

In most applications the uP9617 does not dissipate much heat due to its high efficiency. However, overtemperature protection is implemented in case of applications where the uP9617 is operating at high ambient temperature. If the junction temperature reaches approximately 150°C, the OTP turns both power switches and let the LX node become high impedance. The uP9617 restores to normal operation if the junction temperature drops to 130°C.

It is helpful to analysis the power dissipation of uP9617 for avoding the uP9617 from exceeding the maximum junction temperature. In typical applications, the conduction loss dominates the total power loss in uP9617. The conduction loss has its maximum at high duty-ratio, low input voltage, and high ambient temperatures.

Consider the uP9617 in dropout mode operation at an input voltage of 2.5V, a load current of 1.5A and an ambient temperature of 75°C. The on-resistance of the upper swith is about  $100 \text{m}\Omega$  at this condition. Therefore the power dissipation  $P_D$  is:

$$P_D = I_{OUT}^2 \times R_{DS(ON)} = 225 \text{mW}$$

This results in 50 x  $0.225 = 12^{\circ}$ C temperature raise at junction. The juction temperature is 87°C and is lower than it maximum rating 125°C.

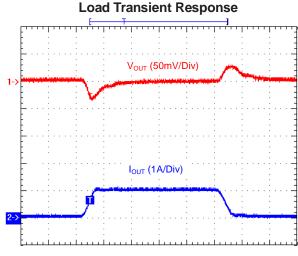

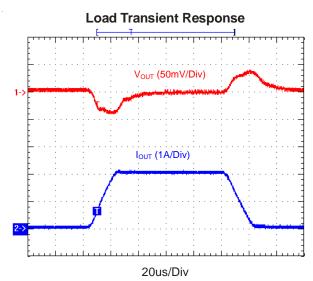

#### **Checking Transient Response**

The regulator loop response can be checked by looking at the load transient response. Switching regulators take several cycles to respond to a step in load current. When a load step occurs,  $V_{\text{OUT}}$  immediately shifts by an amount equal to  $(\Delta I_{\text{OUT}} \text{ x ESR})$ , where ESR is the effective series resistance of  $C_{\text{OUT}} \cdot \Delta I_{\text{OUT}}$  also begins to discharge or charge

$C_{\text{OUT}}$ , which generates a feedback error signal. The regulator loop then acts to return  $V_{\text{OUT}}$  to its steady state value. During this recovery time  $V_{\text{OUT}}$  can be monitored for overshoot or ringing that would indicate a stability problem.

#### **PCB Layout Considerations**

High switching frequencies and relatively large peak currents make the PCB layout a very important part of switching mode power supply design. Good design minimizes excessive EMI on the feedback paths and voltage gradients in the ground plane, both of which can result in instability or regulation errors. Follow the PCB layout guidelines for optimal performance of uP9617.

- 1. For the main current paths, keep their traces short, direct and wide.

- 2. Put the input/output capacitors as close as possible to the device pins.

- LX node is with high frequency voltage swing and should be kept small area. Keep analog components away from LX node to prevent stray capacitive noise pick-up.

- Connect feedback network behind the output capacitors. Place the feedback components near the uP9617 and keep the loop area small.

- 5. A ground plane is preferred, but if not available, keep the signal and power grounds sepregated with small signal components returning to the GND pin at one point. They should not share the high current path of  $C_{\rm IN}$  or  $C_{\rm OUT}$ .

- Flood all unused areas on all layers with copper. Flooding with copper will reduce the temperature rise of power components. These copper areas should be connected to V<sub>IN</sub> or GND.

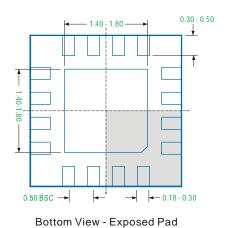

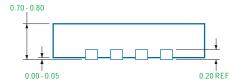

## Package Information

### WQFN3x3-16L Package

### Note

1. Package Outline Unit Description:

BSC: Basic. Represents theoretical exact dimension or dimension target

MIN: Minimum dimension specified.

MAX: Maximum dimension specified.

REF: Reference. Represents dimension for reference use only. This value is not a device specification.

TYP. Typical. Provided as a general value. This value is not a device specification.

- 2. Dimensions in Millimeters.

- 3. Drawing not to scale.

- 4. These dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm.

## **Important Notice**

uPI and its subsidiaries reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

uPI products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment. However, no responsibility is assumed by uPI or its subsidiaries for its use or application of any product or circuit; nor for any infringements of patents or other rights of third parties which may result from its use or application, including but not limited to any consequential or incidental damages. No uPI components are designed, intended or authorized for use in military, aerospace, automotive applications nor in systems for surgical implantation or life-sustaining. No license is granted by implication or otherwise under any patent or patent rights of uPI or its subsidiaries.

COPYRIGHT (c) 2016, UPI SEMICONDUCTOR CORP.

uPI Semiconductor Corp.

Headquarter 9F.,No.5, Taiyuan 1st St. Zhubei City, Hsinchu Taiwan, R.O.C.

TEL: 886.3.560.1666 FAX: 886.3.560.1888

Sales Branch Office 12F-5, No. 408, Ruiguang Rd. Neihu District, Taipei Taiwan, R.O.C.

TEL: 886.2.8751.2062 FAX: 886.2.8751.5064