**Features**

# 6A Dual-Channel, Wide Input Range CC/CV Synchronous Rectified Buck Converter

## **General Description**

The uP9626R is a high-efficiency synchronous-rectified buck converter with internal power switch. With internal low RDS(ON) switches, the high-efficiency buck converter is capable of delivering up to 6.0A output current for charger interface and a wide input voltage range from 4.75V to 36V. That operates in either CV (Constant Output Voltage) mode or CC (Constant Output Current) mode, function provides a current limitation function. The output voltage ranges from 3V to 21V for portable charger devices application.

Other features for the buck converter include internal softstart, adjust operating frequency from 100kHz to 500kHz, adjust output CC(Constant Current) current limit, adjust input current limit setting, adjust output total current limit for dual channel application, chip enable, built in fixed and adjustable line-compensation, short circuit protection, over voltage, and over temperature protections. It is available in a space WQFN4x4-24L package.

## **Ordering Information**

| Order Number | Package Type | Top Marking |

|--------------|--------------|-------------|

| uP9626RQMG   | WQFN4x4-24L  | uP9626R     |

#### Note

- (1) Please check the sample/production availability with uPl representatives.

- (2) uPI products are compatible with the current IPC/JEDEC J-STD-020 requirement. They are halogen-free, RoHS compliant and 100% matte tin (Sn) plating that are suitable for use in SnPb or Pb-free soldering processes.

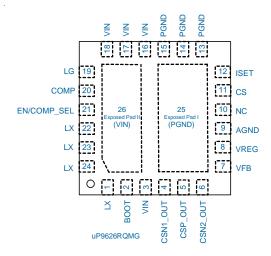

## . Pin Configuration

- 4.75 to 36V Wide Input Voltage Range

- Up to 6.0A Output Current

- CV/CC Mode Control (Constant Voltage and Constant Current)

- Adjust Output Total Current Limit for Dual Channel Application

- Adjust Input Current Limit Setting

- Output Voltage Range: 3V to 21V

- Default Output Voltage Accuracy: ± 1.5%

- Built-In Internal V<sub>RFF</sub> = 1.03V Accuracy: ± 1%

- Up to 98% Conversion Efficiency

- ☐ Fixed Frequency: 100kHz

- Internal Soft Start Time:

- 20ms at F<sub>s</sub>=100kHz

Adjustable Line-Compensation

- Adjustable External Constant Current Setting

- ☐ Constant Current Limit Accuracy with R<sub>SENSE</sub>: ± 10%

- Output Under Voltage and Short Circuit Protection

- Input and Output Over Voltage Protection

- Over Temperature Protection

- WQFN4x4-24L Package

- RoHS Compliant and Halogen Free

**Applications**

- PDA Like Device Car Charger

- Portable Charging Devices

- Wall Adaptors

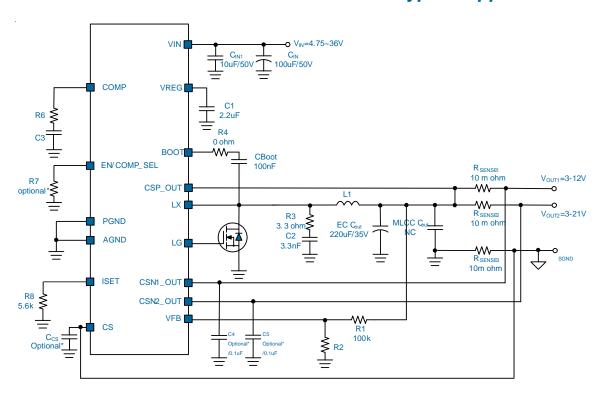

## **Typical Application Circuit**

uP9626R Application Circuit for External Low Side MOSFET

## Functional Pin Description

| Pin No. | Pin Name              | Pin Function                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|---------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1,22-24 | LX                    | Internal Switches Output. Connect this pin to the output inductor.                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 2       | воот                  | Bootstrap Supply for the Floating Upper Gate Driver. Connect the bootstrap capacitor $C_{BOOT}$ between BOOT pin and the LX pin to form a bootstrap circuit. The bootstrap capacitor provides the charge to turn on the upper MOSFET. Typical value for CBOOT is 0.1uF or greater. Ensure that $C_{BOOT}$ is placed near the IC.                                                       |  |  |  |

| 3,16~18 | VIN                   | <b>Power Supply Input.</b> Input voltage that supplies current to the output voltage and powers the internal control circuit. Bypass the input voltage with a minimum 10uFx2 X5R or X7R ceramic capacitor.                                                                                                                                                                             |  |  |  |

| 4       | CSN1_OUT              | The Current Sense Input (-) HV Pin.                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 5       | CSP_OUT               | The Current Sense Input (+) HV Pin.                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 6       | CSN2_OUT              | The Current Sense Input (-) HV Pin.                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 7       | VFB                   | <b>Feedback Input.</b> This pin is the inverting input to the error amplifier. A resistor divider from output to GND is used to set regulator voltage. When VFB is shorted to GND, the default VOUT is 5.15V.                                                                                                                                                                          |  |  |  |

| 8       | VREG                  | 5.1V LDO Output and Gate Drive Supply Voltage Input.                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 9       | AGND                  | Signal Ground.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 10 NC   |                       | Not internally Connected.                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 11      | CS                    | The Current Sense Input Pin. A external sense resistor for detect output total current limit at dual channel application and input current limit application.                                                                                                                                                                                                                          |  |  |  |

| 12      | ISET                  | Output total current limit and input current limit setting pin. Connect a resistor from this pin to GND to set output total current limit and input current limit.                                                                                                                                                                                                                     |  |  |  |

| 13-15   | PGND                  | Power Ground.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 19      | LG                    | Lower Gate Driver Output. Connect this pin to the gate of lower MOSFET.                                                                                                                                                                                                                                                                                                                |  |  |  |

| 20      | COMP                  | <b>Compensation.</b> This pin is output of the error amplifier. The current comparator threshold increases with this control voltage. Connect an RC network to ground for control loop compensation.                                                                                                                                                                                   |  |  |  |

| 21      | EN/COMP_SEL           | Car Charger Enable (Active High) and Adjustable Cable Compensation. Connect a resistor from $43k\Omega$ ~ $360k\Omega$ between EN/COMP_SEL and GND pins to select USB cable compensation for prevent output voltage drop in the output cable. Pull the EN/COMP_SEL pin<14k $\Omega$ to GND disables the car charger, the EN/COMP_SEL pin internal pull high to enable the car charger. |  |  |  |

| 25      | PGND_Exposed<br>Pad I | Power Ground. The exposed pad should be well soldered to PCB with multiple vias to ground plane for optimal thermal performance.                                                                                                                                                                                                                                                       |  |  |  |

| 26      | VIN_Exposed<br>Pad II | Power Supply Input. Input voltage that supplies current to the output voltage.                                                                                                                                                                                                                                                                                                         |  |  |  |

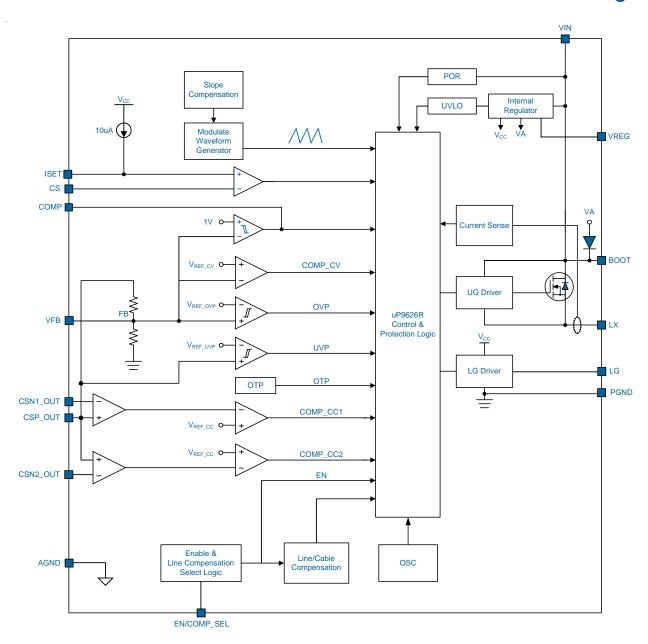

## Functional Block Diagram

uP9626R

## Functional Description

#### CV/CC Mode Control

The uP9626R provides CV/CC function. That operates in either CV (Constant Output Voltage) mode or CC (Constant Output Current) mode, function provides a current limitation function and adjust CC (Constant Output Current) limit setting(Default=3A).In the CV mode, the output voltage is controlled within  $\pm 1\%$ . In the CC mode, the output current variation is less than  $\pm 10\%$  of the nominal value which can be set up to 5A by the current sensing resistor.

When Output current increase until it reaches the CC limit set by the RSENSE resistor. At this point, the device will transition from regulating output voltage to regulating output current, and the output voltage will drop with increasing load.

The CC (Constant Output Current) limit is set at 3A by default with an external resistance RSENSE1/2 =10m $\Omega$ , When the (CSN\_OUT) - (CSP\_OUT) voltage gets higher than 30mV and reaches the current limit, the driver is turned

off. The CC (Constant Output Current) limit is set according to the following equation:

CC (Constant Output Current) Limit=30mV/R<sub>SENSE1/2</sub>

# Output Total Current Limit and Input Current Limit Setting

Adjust output total current limit for dual channel application, The output total current limit is set at 5.6A by default with an external resistance  $R_{\text{SENSE3}} = 10 \text{m}\Omega$ , When the (CS) - (PGND) voltage gets higher than 56mV(default) and reaches the current limit, the driver is turned off. Use an external resistance RISET can adjust difference Voltage between CS and PGND at Current Limit Mode Operation. The output total current limit is set according to the following equation:

When

$$R_{ISET} = 5.6k\Omega$$

,

Output total current limit =  $56mV/R_{SENSE3}$

Input current limit for AC/DC application, The input current limit is setting at 3A by default with an external resistance RSENSE3 =10m $\Omega$ , When the (CS) - (Input GND) voltage gets higher than 30mV(default) and reaches the current limit, the driver is turned off. Use an external resistance  $R_{\rm ISET}$  can adjust difference Voltage between CS and Input GND at Current Limit Mode Operation. The input current limit is set according to the following equation:

When

$$R_{ISET} = 3k\Omega$$

,

Input current limit =30mV /R<sub>SENSE3</sub>

#### **USB Cable Resistance Compensation Select**

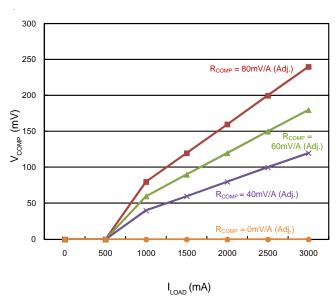

This pin floating (Signal H) or connect a R<sub>EN/COMP\_SEL</sub> resistor <  $360 \text{k}\Omega$  between EN/COMP\_SEL and GND pins (Signal L) to select USB cable compensation for preventing output voltage drop in the output cable, as shown in Figure 1 and Table 1.

# **Enable Control and Output Cable Resistance Compensation**

The uP9626R pull the EN/COMP\_SEL pin<14k $\Omega$  to GND disables the car charger, the EN/COMP\_SEL pin internal pull high to enable the car charger. Connect a resistor between EN/COMP\_SEL and GND pins to adjust USB cable compensation for preventing output voltage drop in the output cable.

In charger applications, the large load will cause voltage drop in the output cable. The uP9626R has a built-in cable compensation function. When the load increases, the cable compensator will increase a adjustable regulation of the error amplifier that can make the output voltage constant. Use the curve and table to adjust the internal reference voltage values for fixed USB and adjustable cable compensation by the external resistance  $R_{\text{SENSE3}}$  and  $R_{\text{SENSE3}}$  =10m $\Omega$  (default) , as shown in Figure 1 and Table 1. The  $R_{\text{COMP}}$  is the internal equivalent resistor.

The fixed and adjustable cable compensation is calculated as follows:

| $R_{\text{SENSE1}}$ and $R_{\text{SENSE3}}$ = 10m $\Omega$ for USB Cable Resistance Compensation Application Table |                                     |                                        |                  |                 |  |  |

|--------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------|------------------|-----------------|--|--|

| $R_{\substack{EN/COMP\_SEL\\ \left(k\Omega\right)}}$                                                               | 43 <u>+</u> 10%                     | 360±10%<br>or<br>Floating<br>(default) | 180 <u>+</u> 10% | 91 <u>+</u> 10% |  |  |

| $R_{COMP} \ (m\Omega)$                                                                                             | 0 (disable)                         | 40<br>(default)                        | 60               | 80              |  |  |

| I <sub>LOAD</sub> (mA)                                                                                             | USB Cable Compensation Voltage (mV) |                                        |                  |                 |  |  |

| 0                                                                                                                  | 0                                   | 0                                      | 0                | 0               |  |  |

| 500                                                                                                                | 0                                   | 0                                      | 0                | 0               |  |  |

| 1000                                                                                                               | 0                                   | 40                                     | 60               | 80              |  |  |

| 1500                                                                                                               | 0                                   | 60                                     | 90               | 120             |  |  |

| 2000                                                                                                               | 0                                   | 80                                     | 120              | 160             |  |  |

| 2500                                                                                                               | 0                                   | 100                                    | 150              | 200             |  |  |

| 3000                                                                                                               | 0                                   | 120                                    | 180              | 240             |  |  |

Table 1. USB Cable Resistance Compensation

Application Table

## Functional Description

Figure 1. USB Compensation at Various Resistor Divider Values

#### **Current Limit Protection**

The uP9626R continuously monitors the inductor current, when the inductor current is higher than current limit

threshold 10A(typ.), the current limit function activates and forces the upper switch turning off to limit inductor current cycle by cycle.

#### **Output Short Circuit Protection**

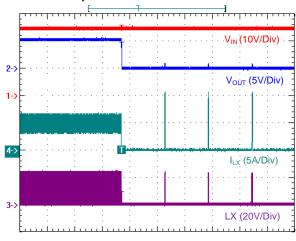

The uP9626R provides output short circuit protection function. Once the output loader short-circuits or the output voltage becomes lower than 2.7V, the SCP will be triggered then always hiccup. The hiccup cycle time is set by an internal counter. When the SCP condition disappears, the converter will resume normal operation and the hiccup status will terminate.

#### **Output Over Voltage Protection**

The uP9626R monitors FB voltage to detect over voltage. When the FB voltage becomes higher than 110% of the target voltage, the OVP will be triggered, the power MOS will turn off and allow low side MOS turn on to charge bootstrap capacitor. When the OVP condition is disappeared, the converter will resume normal operation and recover to normal state.

#### **Input Over Voltage Protection**

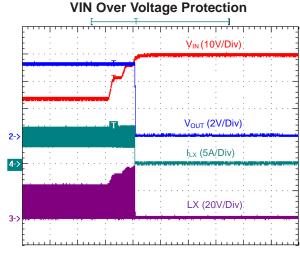

The uP9626R monitors VIN voltage to detect input over voltage protection. When the VIN voltage becomes higher than the target voltage, the VIN OVP will be triggered, the power MOS will turn off and allow low side MOS turn on to charge bootstrap capacitor until output voltage under the collapse threshold 2.7V. When the VIN OVP condition is disappeared, the converter will recover to normal state and restart the soft start sequence.

#### **Over Temperature Protection**

The OTP is triggered and shuts down the uP9626R if the junction temperature is higher than 130°C. The OTP is a non-latch type protection. The uP9626R automatically initiates another soft start cycle if the junction temperature drops below 110°C.

#### **Output Voltage Setting and Feedback Network**

The output voltage can be set from  $V_{REF}$  to  $V_{IN}$  by a voltage divider. The output voltage can be set as follows,

$$V_{OUT} = \left(\frac{R1 + R2}{R2}\right) \times V_{REF}$$

.

R2 must be higher than  $10k\Omega$ .

The internal  $V_{\rm REF}$  is 1.03V with 1.0% accuracy in real apploications, when control loop compensation connects to an RC entwork to ground at COMP pin for better transient response.

|                                                                                                                                       | Absolute Maximum Ratii                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| (Note 1)                                                                                                                              |                                                                                                                      |

| Supply Input Voltage, V <sub>IN</sub>                                                                                                 | 0.3V to +-                                                                                                           |

| LX/LX_C Voltage to GND                                                                                                                | 0.3V to (V <sub>IN</sub> + 0.                                                                                        |

| BOOT to LX Voltage                                                                                                                    |                                                                                                                      |

| CSN1/CSN2_OUT/CSP_OUT Pin Voltage                                                                                                     | 0.3V to +2                                                                                                           |

| CS Pin Voltage                                                                                                                        | 0.3V to -                                                                                                            |

| EN/COMP_SEL Voltage                                                                                                                   |                                                                                                                      |

| Other Pin Voltage                                                                                                                     |                                                                                                                      |

| Storage Temperature Range                                                                                                             |                                                                                                                      |

| Junction Temperature                                                                                                                  | 15                                                                                                                   |

| Lead Temperature (Soldering, 10 sec)                                                                                                  | 26                                                                                                                   |

| ESD Rating (Note 2)                                                                                                                   |                                                                                                                      |

| HBM (Human Body Mode)                                                                                                                 |                                                                                                                      |

| CDM (Charged Device Mode)                                                                                                             | 50                                                                                                                   |

|                                                                                                                                       | Thermal Information                                                                                                  |

| Package Thermal Resistance (Note 3)                                                                                                   |                                                                                                                      |

| WQFN4x4-24L $\theta_{JA, controller}$                                                                                                 | 54°C                                                                                                                 |

| WQFN4x4-24L θ <sub>IA HS</sub>                                                                                                        | 42°C                                                                                                                 |

| WQFN4x4-24L $\theta_{\text{IC. controller}}$                                                                                          | 21°C                                                                                                                 |

| WQFN4x4-24L $\theta_{\text{IC HS}}$                                                                                                   | 10°C                                                                                                                 |

| Power Dissipation, P <sub>D</sub> @ T <sub>A</sub> = 25°C                                                                             |                                                                                                                      |

|                                                                                                                                       | 1.8                                                                                                                  |

| WQFN4x4-24L P <sub>D-US</sub>                                                                                                         | 2.3                                                                                                                  |

|                                                                                                                                       | Recommended Operation Condition                                                                                      |

| (Note 4)                                                                                                                              |                                                                                                                      |

| Supply Input Voltage, V <sub>IN</sub>                                                                                                 |                                                                                                                      |

| Output Voltage, V <sub>OUT</sub>                                                                                                      |                                                                                                                      |

| Operating Junction Temperature Range                                                                                                  |                                                                                                                      |

| Operating Ambient Temperature Range                                                                                                   |                                                                                                                      |

|                                                                                                                                       | t these or any other conditions beyond those indicated in t<br>d. Exposure to absolute maximum rating conditions for |

| Note 2. Devices are ESD sensitive. Handling precaution recon                                                                          | mmended.                                                                                                             |

| <b>Note 3.</b> $\theta_{JA}$ is measured in the natural convection at $T_A = 25^{\circ}\text{C}$ c 51-3 thermal measurement standard. | on a low effective thermal conductivity test board of JEDEC                                                          |

|                                                                                                                                       |                                                                                                                      |

Note 4. The device is not guaranteed to function outside its operating conditions.

## Electrical Characteristics

$(V_{IN} = 12V, T_A = 25^{\circ}C, unless otherwise specified)$

| Parameter                                | Symbol               | Test Conditions                                                                                                                                                                                                                                                                                                          | Min    | Тур  | Max    | Units |

|------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|--------|-------|

| Supply Input Voltage                     |                      |                                                                                                                                                                                                                                                                                                                          |        |      | •      |       |

| Input Voltage Range                      | V <sub>IN</sub>      |                                                                                                                                                                                                                                                                                                                          | 4.75   |      | 36     | V     |

| \(\(\mathrea{\pi}\)                      |                      | V <sub>N</sub> rising                                                                                                                                                                                                                                                                                                    |        | 4.6  |        | .,    |

| VIN POR Threshold                        |                      | V <sub>IN</sub> falling                                                                                                                                                                                                                                                                                                  |        | 4.3  |        | V     |

| leased OV/D Three should                 | .,                   | V <sub>IN_OVP</sub> rising                                                                                                                                                                                                                                                                                               | 37.5   |      |        |       |

| Input OVP Threshold                      | V <sub>IN_OVP</sub>  | V <sub>IN_OVP</sub> falling                                                                                                                                                                                                                                                                                              | 37     |      |        | V     |

| Supply Input Current                     | 1                    |                                                                                                                                                                                                                                                                                                                          |        |      | 1      |       |

| Input Quiescent Current                  | I <sub>Q</sub>       | No switching                                                                                                                                                                                                                                                                                                             |        |      | 1      | mA    |

| Input Shutdown Current                   | I <sub>s</sub>       | EN disable (LDO On) for uP9626R                                                                                                                                                                                                                                                                                          |        |      | 200    | uA    |

| Oscillator                               | 1                    |                                                                                                                                                                                                                                                                                                                          |        |      |        | ı     |

| Oscillation Frequency                    | f <sub>osc</sub>     |                                                                                                                                                                                                                                                                                                                          |        | 100  |        | kHz   |

| Maximum Duty Cycle                       | D <sub>MAX</sub>     | f <sub>s</sub> = 100kHz                                                                                                                                                                                                                                                                                                  | 96     | 98   |        | %     |

| Minimum On Time                          | t <sub>ON-MIN</sub>  |                                                                                                                                                                                                                                                                                                                          |        | 450  |        | ns    |

| Minimum Off Time                         | t <sub>OFF-MIN</sub> |                                                                                                                                                                                                                                                                                                                          |        | 200  | 400    | ns    |

| Power Switches                           | '                    |                                                                                                                                                                                                                                                                                                                          |        |      | !      | -     |

| Hi-Side Switch On Resistance             | R <sub>DS(ON)</sub>  | VCC = 5.1V                                                                                                                                                                                                                                                                                                               |        | 12   |        | mΩ    |

| Internal Reference Voltage               |                      |                                                                                                                                                                                                                                                                                                                          |        |      | !      | !     |

| Feedback Voltage                         | V <sub>FB</sub>      |                                                                                                                                                                                                                                                                                                                          | 1.0197 | 1.03 | 1.0403 | V     |

| Default Output Voltage                   | V <sub>CSP_OUT</sub> | VFB short to GND, at I <sub>OUT</sub> = 0A                                                                                                                                                                                                                                                                               | 5.073  | 5.15 | 5.227  | V     |

| Error Amplifier Transconductance         | GEA                  |                                                                                                                                                                                                                                                                                                                          |        | 580  |        | uA/V  |

| VREG LDO Voltage                         |                      |                                                                                                                                                                                                                                                                                                                          |        |      | •      | •     |

| LDO Output Voltage                       | $V_{REG}$            |                                                                                                                                                                                                                                                                                                                          | 4.93   | 5.1  | 5.27   | V     |

| LDO Output Current                       | I <sub>REG</sub>     |                                                                                                                                                                                                                                                                                                                          | 40     |      |        | mA    |

| Soft Start                               | ,                    |                                                                                                                                                                                                                                                                                                                          |        |      | '      | •     |

| Soft Start Time                          | T <sub>ss</sub>      | From VOUT = 0% to 100% at f <sub>S</sub> = 100kHz                                                                                                                                                                                                                                                                        | 16     | 20   | 24     | ms    |

| Enable/Cable Resistance Compe            |                      |                                                                                                                                                                                                                                                                                                                          |        |      | !      |       |

| EN/COMP_SEL Logic Low                    | R <sub>EN/COMP</sub> | R <sub>EN/COMP</sub> falling                                                                                                                                                                                                                                                                                             |        |      | 14     | kΩ    |

| EN/COMP_SEL Current                      | I <sub>EN/COMP</sub> |                                                                                                                                                                                                                                                                                                                          |        | 5    |        | uA    |

| Disable Line Compensation                | V <sub>out</sub>     | $\begin{array}{c} \text{V}_{\text{OUT}}\text{=-}5.15\text{V}, \text{I}_{\text{OUT}}\text{=-}(2\text{A}\text{-}1\text{A}), \ \text{R}_{\text{EN/COMP\_SEL}}\text{=-}43\text{k}\Omega, \\ \text{R}_{\text{SENSE1}} \text{ and } \text{R}_{\text{SENSE3}}\text{=-}10\text{m}\Omega, \\ \text{measured at VOUT} \end{array}$ |        | 0    |        | mV/A  |

| Adjustable Line Compensation 1           | V <sub>out</sub>     | $\begin{array}{l} \text{V}_{\text{OUT}}\text{=-}5.15\text{V}, \text{I}_{\text{OUT}}\text{=-}(2\text{A}1\text{A}), \ \text{R}_{\text{EN/COMP\_SEL}}\text{=-}91\text{k}\Omega, \\ \text{R}_{\text{SENSE1}} \ \text{and} \ \text{R}_{\text{SENSE3}}\text{=-}10\text{m}\Omega, \\ \text{measured at VOUT} \end{array}$       |        | 80   |        | mV/A  |

| Adjustable Line Compensation 2           | V <sub>out</sub>     | $\begin{array}{c} \text{$V_{\text{OUT}}$=$5.15$V,$I_{\text{OUT}}$=$(2A$-$1A$),}\\ \text{$R_{\text{ENCOMP\_SEL}}$=$180k$\Omega, $R_{\text{SENSE1}}$ and}\\ \text{$R_{\text{SENSE3}}$=$10m$\Omega, measured at VOUT } \end{array}$                                                                                         |        | 60   |        | mV/A  |

| Adjustable Line Compensation 3 (default) | V <sub>out</sub>     | $\begin{array}{c} \textbf{V}_{\text{OUT}}\text{=}5.15 \textbf{V}, \textbf{I}_{\text{OUT}}\text{=}(2 A\text{-}1 A), \\ \textbf{R}_{\text{ENCOMP\_SEL}}\text{=}360 k\Omega \text{ or NC, R}_{\text{SENSE1}} \text{ and} \\ \textbf{R}_{\text{SENSE3}}\text{=}10 m\Omega, \text{ measured at VOUT} \end{array}$             |        | 40   |        | mV/A  |

## Electrical Characteristics

| Parameter                                                               | Symbol              | Test Conditions                                                                                                       | Min   | Тур | Max   | Units |  |

|-------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-------|--|

| Current Sense Amplifier                                                 |                     |                                                                                                                       |       |     |       |       |  |

| Voltage Difference between<br>CSP and CSN1/CSN2 at CC<br>Mode Operation | $\Delta V_{_{SEN}}$ | $R_{SENSE1/2}$ =10m $\Omega$                                                                                          | 27    | 30  | 33    | mV    |  |

| Voltage Difference between CS and PGND at Current Limit Mode Operation  | CS                  | $R_{SENSE3}$ =10m $\Omega$ , $R_{ISET}$ =5.6k $\Omega$                                                                | 49.28 | 56  | 62.72 | mV    |  |

| Output Total Current Limit and Input Current Limit Setting              | I <sub>SET</sub>    |                                                                                                                       | 9     | 10  | 11    | uA    |  |

| Protection                                                              |                     |                                                                                                                       | •     |     |       |       |  |

| CC1 (Constant Output Current)<br>Limit                                  | I <sub>OUT1</sub>   | R <sub>SENSE1</sub> =10mΩ at CSN1_OUT=5.15V                                                                           | 2.7   | 3   | 3.3   | А     |  |

| CC2 (Constant Output Current)<br>Limit                                  | l <sub>OUT2</sub>   | R <sub>SENSE2</sub> =10mΩ at CSN2_OUT=5.15V                                                                           | 2.7   | 3   | 3.3   | А     |  |

| CC (Constant Output Current)<br>Limit                                   | I <sub>OUT</sub>    | $R_{SENSE3}$ =10m $\Omega$ for IOUT1+IOUT2                                                                            | 4.928 | 5.6 | 6.272 | А     |  |

| High Side Current Limit<br>Protection                                   | I <sub>LIM</sub>    |                                                                                                                       | 8     | 10  |       | А     |  |

| Output Voltage Needs to Collapse Threshold                              | CSN                 | Into CC(Constant Output Current) Limit, measreued at CSN1_OUT or CSN2_OUT, with respect to VOUT UVP threshold voltage |       | 2.7 |       | V     |  |

| Reference Voltage of the Over<br>Voltage Comparator                     | V <sub>OVP</sub>    | measrued at FB, with respect to reference voltage                                                                     | 105   | 110 | 115   | %     |  |

| Hiccup Short Circuit Protection                                         | TH1                 | at f <sub>s</sub> =100kHz                                                                                             |       | 650 |       | ms    |  |

| Thermal Shutdown<br>Temperature                                         | T <sub>SD</sub>     | Shutdown Temperature                                                                                                  |       | 130 |       | °C    |  |

| Thermal Shutdown Hysteresis                                             | T <sub>SDHYS</sub>  | Hysteresis                                                                                                            |       | 20  |       | °C    |  |

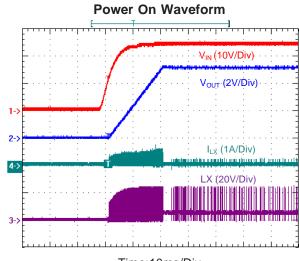

## **Typical Operation Characteristics**

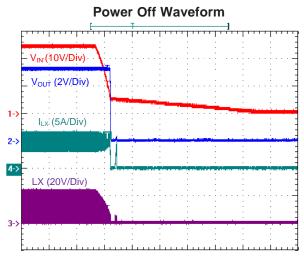

$\begin{aligned} & \text{Time:10ms/Div} \\ & V_{\text{IN}} = 24\text{V}, \, V_{\text{OUT}} = 5.15\text{V}, \, I_{\text{OUT}} = 0\text{A}, \, \text{Fs} = 100\text{kHz} \end{aligned}$

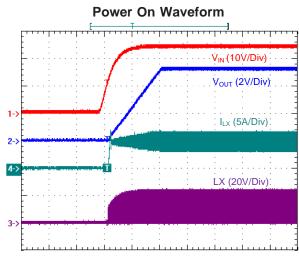

Time:10ms/Div  $V_{IN} = 24V, V_{OUT} = 5.15V, I_{OUT} = 4.8A, Fs = 100kHz$

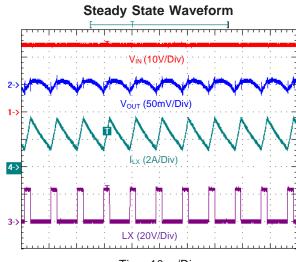

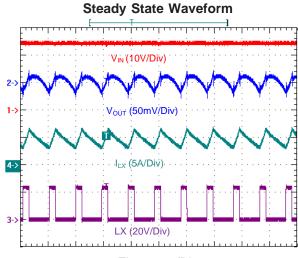

Time:10us/Div  $V_{IN} = 24V, V_{OUT} = 5.15V, I_{OUT} = 2.4A, Fs = 100kHz$

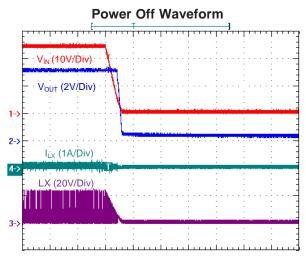

$\begin{aligned} & \text{Time:400ms/Div} \\ & \text{V}_{\text{IN}} = 24 \text{V}, \, \text{V}_{\text{OUT}} = 5.15 \text{V}, \, \text{I}_{\text{OUT}} = 0 \text{A}, \, \text{Fs} = 100 \text{kHz} \end{aligned}$

Time:10ms/Div  $V_{IN} = 24V, V_{OUT} = 5.15V, I_{OUT} = 4.8A, Fs = 100kHz$

Time:10us/Div  $V_{IN} = 24V, V_{OUT} = 5.15V, I_{OUT} = 4.8A, Fs = 100kHz$

## **Typical Operation Characteristics**

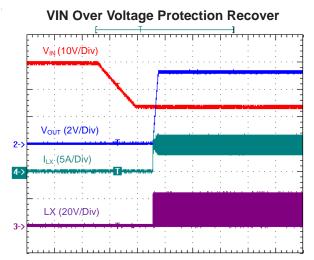

$\begin{aligned} &\text{Time:20ms/Div}\\ \text{V}_{\text{IN}} = 24 \text{V to 40V}, \text{V}_{\text{OUT}} = 5.15 \text{V}, \text{I}_{\text{OUT}} = 4.8 \text{A},\\ &\text{Fs} = 100 \text{kHz} \end{aligned}$

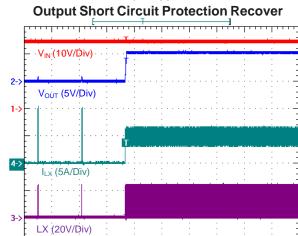

### **Output Short Circuit Protection**

$\label{eq:lower_lower} \begin{aligned} & \text{Time:400ms/Div} \\ & \text{V}_{\text{IN}} = 24 \text{V}, \, \text{V}_{\text{OUT}} = 5.15 \text{V}, \, \text{I}_{\text{OUT}} = 4.8 \text{A}, \, \text{Fs} = 100 \text{kHz} \end{aligned}$

Time:100ms/Div  $V_{IN} = 40V$  to 24V,  $V_{OUT} = 5.15V$ ,  $I_{OUT} = 4.8A$ , Fs = 100kHz

$\label{eq:Vin} \begin{aligned} & \text{Time:400ms/Div} \\ & \text{V}_{\text{IN}} = 24 \text{V}, \, \text{V}_{\text{OUT}} = 5.15 \text{V}, \, \text{I}_{\text{OUT}} = 4.8 \text{A}, \, \text{Fs} = 100 \text{kHz} \end{aligned}$

## Application Information

#### **Output Inductor Selection**

Output inductor selection is usually based the considerations of inductance, rated current value, size requirements and DC resistance (DCR). The inductance is chosen based on the desired ripple current. Large value inductors result in lower ripple currents and small value inductors result in higher ripple currents. Higher VIN or VOUT also increases the ripple current as shown in the equation below. A reasonable starting point for setting ripple current is IL = 900mA (30% of 3000mA).

$$\Delta I_{L} = \frac{1}{f_{OSC} \times L_{OUT}} \times V_{OUT} (1 - \frac{V_{OUT}}{V_{IN}})$$

Maximum current ratings of the inductor are generally specified in two methods: permissible DC current and saturation current. Permissible DC current is the allowable DC current that causes 40°C temperature raise. The saturation current is the allowable current that causes 10% inductance loss. Make sure that the inductor will not saturate over the operation conditions including temperature range, input voltage range, and maximum output current. If possible, choose an inductor with rated current higher than 7A so that it will not saturate even under current limit condition.

The size requirements refer to the area and height requirement for a particular design. For better efficiency, choose a low DC resistance inductor. DCR is usually inversely proportional to size.

Different core materials and shapes will change the size, current and price/current relationship of an inductor. Toroid or shielded pot cores in ferrite or permalloy materials are small and don; It radiate much energy, but generally cost more than powdered iron core inductors with similar electrical characteristics. The choice of which style inductor to use often depends on the price vs. size requirements and any radiated field/EMI requirements.

#### **Input Capacitor Selection**

The input capacitor needs to be carefully selected to maintain sufficiently low ripple at the supply input of the converter. A low ESR capacitor is highly recommended. Since large current flows in and out of this capacitor during switching, its ESR also affects efficiency.

The input capacitance needs to be higher than 100uF. The best choice is the ceramic type and low ESR electrolytic types may also be used provided that the RMS ripple current rating is higher than 50% of the output current.

In the case of electrolytic types, they can be further away if a small parallel 10uF ceramic capacitor is placed right close to the IC. A 100uF OSCON capacitor and 10uF ceramic capacitor are recommended and placed close to the VIN and GND pins, with the shortest traces possible.

#### **Output Capacitor Selection**

The ESR of the output capacitor determines the output ripple voltage and the initial voltage drop following a high slew rate load transient edge. The output ripple voltage can be calculated as:

$$\Delta V_{OUT} = \Delta I_{C} \times (ESR + \frac{1}{8 \times f_{OSC} \times C_{OUT}})$$

Where  $f_{OSC}$  = operating frequency,  $C_{OUT}$  = output capacitance and  $\Delta I_{C} = \Delta I_{L}$  = ripple current in the inductor. The ceramic capacitor with low ESR value provides the low output ripple and low size profile.

The ceramic capacitor with low ESR value provides the low output ripple and low size profile.

In the case of electrolytic capacitors, the ripple is dominated by  $R_{\text{ESR}}$  multiplied by the ripple current.

Connect a 220uF OSCON capacitor at output CSP terminal for good performance and low output ripple and place output capacitors as close as possible to the device.

In the case of ceramic output capacitors,  $R_{\rm ESR}$  is very small and does not contribute to the output ripple at Fs=100kHz. Connect a 0.1uF optional ceramic capacitor close to IC CSN1 and CSN2 pins for best

noise immunity and good CC performance.

Connect a 4.7uF~10uF optional ceramic capacitor close to USB connector VOUT1 and VOUT2 for good CC performance.

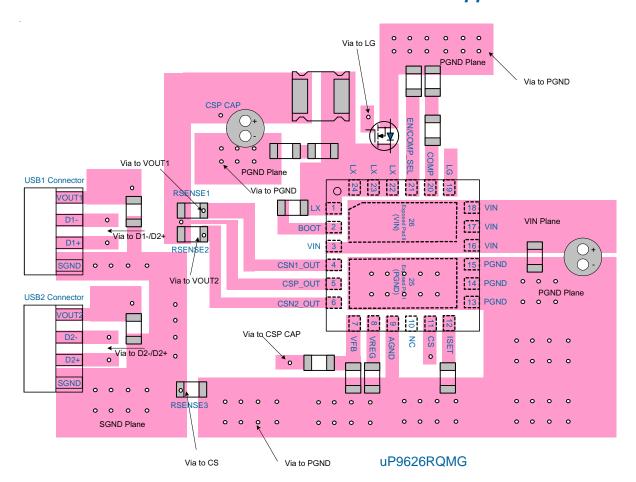

#### **PCB Layout Consideration**

The PCB layout is an important step to maintain the high performance of the uP9626R. High switching frequencies and relatively large peak currents make the PCB layout is a very important part of all high frequency switching power supplies design. Both the high current and the fast switching nodes demand full attention to the PCB layout to save the robustness of the uP9626R through the PCB layout. Improper layout might show the symptoms of poor load or line regulation, radiate excessive noise at ground or input, output voltage shifts, stability issues, unsatisfying EMI behavior or worsened efficiency. Follow the PCB layout guidelines for optimal performances of uP9626R.

## Application Information

#### Application limitation For uP9626R

For output voltage setting from 3.6V to 21V, uP9626R is capable of sourcing load current up to 3.0A at CSN1 and CSN2 during power on. When output voltage setting is under 3.6V, the sourcing capability at CSN1 and CSN2 is not guaranteed, but there is no such limitation after power on.

#### Layout Guidelines For uP9626R:

- 1. The input decoupling ceramic capacitor 10uF must be placed close to the VIN (Pin16,17,18) and PGND plane through vias or a short and wide path.

- 2. The 5.1V VREG LDO output capacitor (2.2uF, MLCC) for gate drive supply voltage must be placed close to the VREG( Pin8) and connected to AGND (Pin9) directly, to avoid noise and instability.

- 3. When adjust output total current limit for dual channel application, AGND and PGND (power ground) should be connected together at a single point, apply copper plane to Exposed Pad PGND (Pin25) and through vias for best heat dissipation and noise immunity. The exposed pad is the main path for heat convection and should be well-soldered to the PCB for best thermal performance.

- 4. Use a short trace connecting the bootstrap capacitor CBOOT close to BOOT (Pin 2) and LX (Pin1,22,23,24) to form a bootstrap circuit.

- 5. The FB feedback resistor should be close to VFB( Pin 7) and be away from switching node.

- 6. The current sense traces should be connected to the current sense resistor's (RSENSE1/2/3) pads in Kelvin sense way as below figure, and routed in parallel (differential routing), and be away from switching node as LX and inductor.

- 7. The current sense resistor's (RSENSE1/2/3) should be close to CSN1/CSP/CSN2/CS( Pin 4,5,6,11) to avoid noise and constant current instability.

- 8. The Optional ceramic capacitor 0.1uF must be placed close to the CSN1/CSN2/CS (Pin 4,6,11) and PGND plane through vias or a short path to to avoid noise and constant current instability.

- 9. The Optional ceramic capacitor 4.7uF must be placed close to USB connector VOUT1 and VOUT2 for good CC performance.

- 10. The RC snubber is connected between LX and PGND or VIN and LX to absorb switching noise. The snubber should be close to LX and PGND or VIN and LX pin to eliminate the high frequency voltage spike and minimize the loop area to optimize EMI.

- 11. The LX (Pin1,22,23,24) is the noise node switching from VIN to GND. LX node copper area should be minimized and wide to reduce EMI and should be isolated from the rest of circuit for good EMI and low noise operation. The Low side NMOS and inductor must be placed close to the LX (1,22,23,24) for good efficiency and decrease PCB trace loss

- 12. The D+ and D- of the USB Connector are the USB detect data line input node, the D+ and D- Pin of the via or trace area should be isolated using 0.96mm space to prevent direct contact with VOUT area components which may cause voltage of D+ and D- pins to exceed maximum rating voltage.

- 13. The 4-layered PCB layout can increase heat dissipation area by taking advantage of the middle layers of the PGND plane. This may also lower the temperature of IC and its peripheral components of the demo board such as inductor.

## Application Information

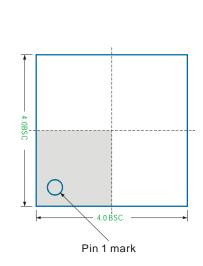

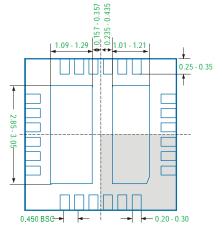

## **Package Information**

#### **WQFN4x4 - 24L**

Bottom View - Exposed Pad

#### Note

1. Package Outline Unit Description:

BSC: Basic. Represents theoretical exact dimension or dimension target

MIN: Minimum dimension specified.

MAX: Maximum dimension specified.

REF: Reference. Represents dimension for reference use only. This value is not a device specification.

TYP. Typical. Provided as a general value. This value is not a device specification.

- 2. Dimensions in Millimeters.

- 3. Drawing not to scale.

- 4. These dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm.

## **Important Notice**

The contents of this document are provided in connection with uPI Semiconductor Corp. ("uPI") products. uPI makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice.

No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights, is granted by this publication. Except as provided in uPI's terms and conditions of sale for such products, uPI assumes no liability whatsoever, and uPI disclaims any express or implied warranty relating to sale and/or use of uPI products, including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. uPI products are not designed, intended, authorized or warranted for use as components in systems intended for medical, life-saving, or life sustaining applications. uPI reserves the right to discontinue or make changes to its products at any time without notice.

Copyright 2019 ©, uPI Semiconductor Corp. All rights reserved.

uPI, uPI Micro Power Intellect logo, and combinations thereof, are registered trademarks of uPI Semiconductor Corp. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

uPI Semiconductor Corp.

9F.,No.5, Taiyuan 1st St. Zhubei City, Hsinchu, Taiwan, R.O.C. TEL: 886.3.560.1666 FAX: 886.3.560.1888 sales@upi-semi.com