# Smart Power Stage (SPS) with Integrated Current and Temperature Monitors

### **General Description**

The uP9642B is a Smart Power Stage (SPS) solution with fully optimized, integrated driver and MOSFETs for high-current, high frequency, synchronous buck DC-DC converters. The SPS enables higher performance at lower output voltages required by cutting edge CPU, GPU and DDR memory designs.

The uP9642B also enables advanced high accuracy module temperature reporting and on-chip synchronous MOSFET current monitoring. The protection includes cycle-by-cycle over current protection, phase fault detection, preliminary over voltage protection, VCC/VDRV UVLO protection, and thermal shutdown.

The uP9642B is optimized for CPU core power delivery. This device combined with a multi-phase buck PWM controller forms a complete core voltage regulator for advanced micro- processors.

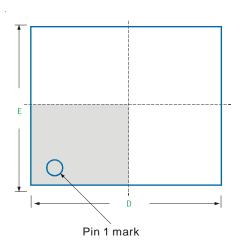

### **Ordering Information**

| Order Number | Package Type | Top Marking |  |  |

|--------------|--------------|-------------|--|--|

| uP9642BQR1   | VQFN6X5-39L  | uP9642B     |  |  |

#### Note:

- (1) Please check the sample/production availability with uPI representatives.

- (2) uPI products are compatible with the current IPC/JEDEC J-STD-020 requirement. They are halogen-free, RoHS compliant and 100% matte tin (Sn) plating that are suitable for use in SnPb or Pb-free soldering processes.

### **Applications**

- High Frequency, Low Profile DC-DC Converter

- Voltage Regulator for CPUs, GPUs and DDR Memory Arrays

### **Features**

- Input Voltage (V<sub>IN</sub>) Range: 4.5V to 16V

- VCC and VDRV Supply Range: 4.5V to 5.5V

- Output Voltage Range: 0.4V to 2.0V

- Up to 60A of Current Handling Capability

- Switching Frequency Range: 200kHz to 700kHz

- 5mV / A On-Chip MOSFET Current Sensing

- 8mV /°C Temperature Analog Output

- On-Chip MOSFET Temperature Compensation

- VCC / VDRV Under Voltage Lockout (UVLO)

- Thermal Shutdown and Fault Flag

- MOSFET Phase Fault Detection and Flag

- Cycle-by-Cycle Over Current Protection

- Preliminary Over Voltage (OV) Protection and Flag

- Support 3.3V and 5V Tri-State PWM Input

- Deep-Sleep Mode for Power Saving

- VOS Output Voltage Sensing Input

- Lead Free and RoHS Compliant Package

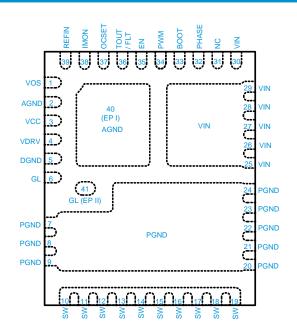

### **Pin Configuration**

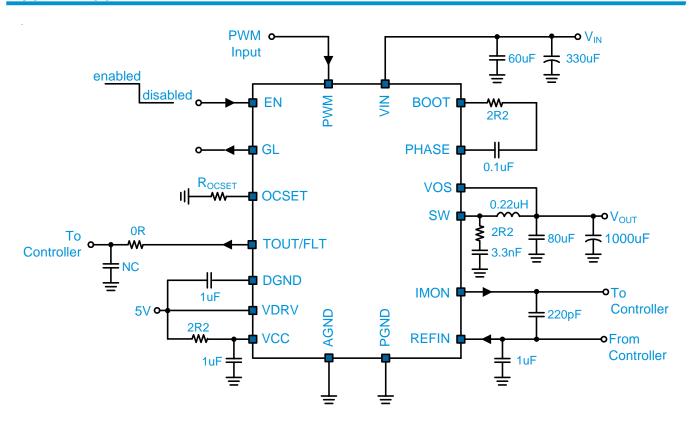

# **Typical Application Circuit**

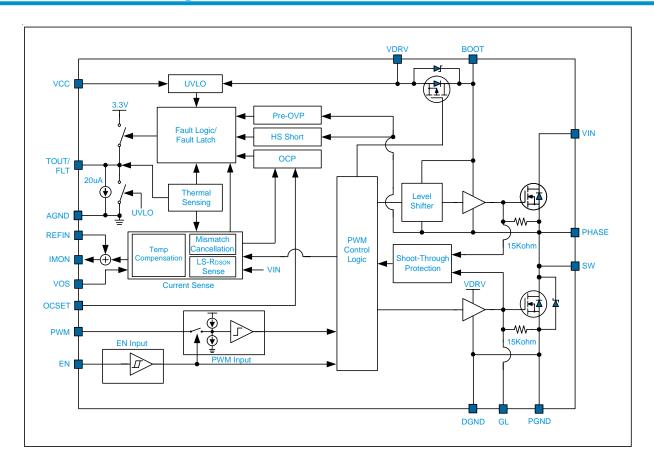

### **Functional Block Diagram**

# **Functional Pin Description**

| Pin No.   | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                |

|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | VOS      | VOUT Sense. Output voltage sensing pin for current sensing application.                                                                                                                                                                                                                                                     |

| 2         | AGND     | Signal Ground. All signals are referenced to this pin.                                                                                                                                                                                                                                                                      |

| 3         | VCC      | <b>Supply Voltage for the IC.</b> 5V supply voltage for internal control logic circuit. Connect a 1uF capacitor between VCC and AGND and place it as close to the pin as possible.                                                                                                                                          |

| 4         | VDRV     | <b>Drive Voltage Output.</b> 5V supply voltage for internal gate drivers. Connect a 1uF capacitor between VDRV and DGND and place it as close to the pin as possible.                                                                                                                                                       |

| 5         | DGND     | Driver Ground.                                                                                                                                                                                                                                                                                                              |

| 7-9,20-24 | PGND     | Power Ground. It is also the power ground of the synchronous MOSFET.                                                                                                                                                                                                                                                        |

| 6         | GL       | <b>Lower Gate Driver Output.</b> Synchronous MOSFET gate monitor pin enables the user to easily observe the waveform.                                                                                                                                                                                                       |

| 10-19     | SW       | <b>Switch Node.</b> Switching node of internal control/synchronous MOSFETs, and connects to the external inductor.                                                                                                                                                                                                          |

| 25-30     | VIN      | Supply Voltage for the Power Stage. 4.5V to 16V input voltage connection.                                                                                                                                                                                                                                                   |

| 31        | NC       | Not Connected. This pin needs to be left floating in application.                                                                                                                                                                                                                                                           |

| 32        | PHASE    | <b>Switch Node.</b> For bootstrap capacitor connection only. It is connected to SW internally.                                                                                                                                                                                                                              |

| 33        | воот     | <b>Bootstrap Supply.</b> Connect a minimum 0.1uF capacitor in series with a $2.2\Omega$ resistor from BOOT to PHASE pin. The bootstrap capacitor provides the charge to turn on the control MOSFET.                                                                                                                         |

| 34        | PWM      | <b>PWM Input.</b> Compatible with 3.3V/5V logic level PWM Input. PWM input: "High level" turns control MOSFET on; "Tri-state"turns both MOSFETs off; "Low level" turns the synchronous MOSFET on.                                                                                                                           |

| 35        | EN       | <b>Enable Control.</b> Pulling EN high enables the driver and requires maximum 15us power up time; pulling EN low disables the driver and enters ultralow quiescent current mode. There is no internal pull-up or pull-down mechanism to this pin.                                                                          |

| 36        | TOUT/FLT | Temperature Sense Reporting/ Fault Flag. The voltage at this pin is defined by the equation: 8mV * (Temperature in Celsius of driver IC) + 0.6V. This pin will be pulled up to 3.3V internally under the following conditions: over temperature, over current, preliminary over voltage condition or phase fault condition. |

| 37        | OCSET    | Over Current Setting. Setting over current threshold by placing a resistor from OCSET pin to AGND. If OCSET is floating or directly tied to VCC, the over current threshold is fixed at 80A. It is recommended to keep $R_{\text{OCSET}}$ above 37.5k $\Omega$ to keep OCP level under 80A.                                 |

| 38        | IMON     | Current Sense Reporting. Sensed current output signal referenced to the REFIN pin. V(IMON - REFIN) voltage represents current information at 5mV/A.                                                                                                                                                                         |

| 39        | REFIN    | Reference Input. External reference voltage input for the IMON function. This pin has a low bias current and can be tied to a fixed voltage (1.2V recommended) between 1.1V and 1.8V from a PWM controller.                                                                                                                 |

# **Functional Pin Description**

| Pin No. Pin |             | Pin Name | Pin Function |                                                                                                                                        |

|-------------|-------------|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 4           | 40 EPI AGND |          | AGND         | Signal Ground.                                                                                                                         |

| 4           | 11          | EP II    | GL           | <b>Lower Gate Driver Output.</b> Synchronous MOSFET driver pin that can be connected to a test point in order to observe the waveform. |

### **Functional Description**

The uP9642B contains features as follows, the temperature sensing functionality, accurate current monitoring, ultracompact, low-quiescent current, high-efficiency and high speed MOSFET driver fully optimized to drive a pair of integrated control and synchronous MOSFETs up to 700kHz for simplifying system design and improving functionality accuracy.

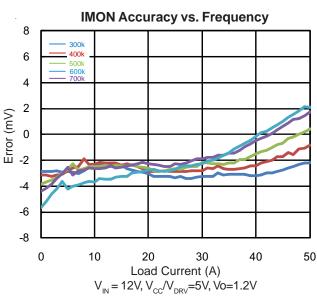

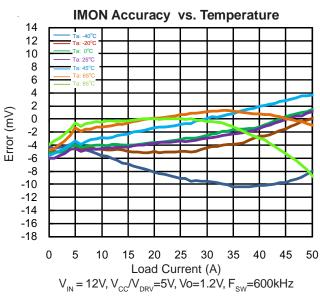

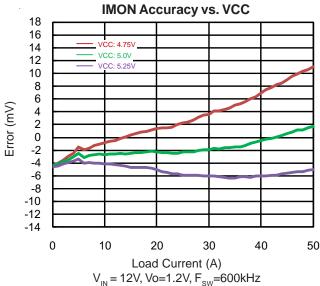

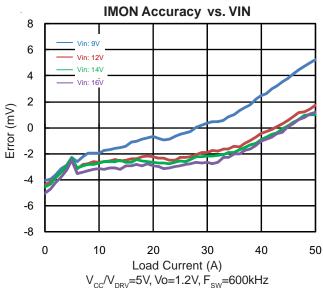

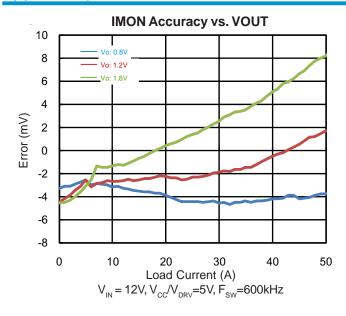

The uP9642B incorporates a synchronous MOSFET based current sense technique to provide an accurate output signal (IMON) which reports the real-time module current and to overcome the conventional inaccuracy of inductor DCR system method and resistor sense method leading to system inefficiency. V<sub>(IMON-REFIN)</sub> voltage represents current information at 5mV/A. The IMON signal can be used to replace inductor DCR sensing or resistor sense methods in multi-phase applications. The superior current sense accuracy achieved with on-chip current sensing technique improves the end-system performance.

The uP9642B also provides a very accurate module thermal monitor (TOUT) in normal operation. TOUT is a voltage source signal that is calibrated to provide a 0.6V output at 25°C with 8mV /°C linear slope for monitoring power stage temperature. If used in multi-phase topologies, multiple temperature outputs can be tied together to share common thermal bus. Operating with this configuration will force the thermal bus signal to report the highest voltage (highest temperature) output TOUT signal to the controller. Also, this pin is used as a module fault flag pin. If preliminary over voltage condition, a shorted control MOSFET, a prolonged over current event, or an over temperature condition inside the power stage is detected, the TOUT will be pulled up to 3.3V internally.

The uP9642B PWM input is compatible with standard either 3.3V or 5V PWM input with tri-state.

The uP9642B also supports deep-sleep power saving mode. When in deep-sleep mode that VCC is ready but EN is low, the driver will disable most of the function circuitry (with very low quiescent current) to greatly reduce power consumptions.

The uP9642B includes protection features as follows, VCC/VDRV Under Voltage-Lockout (UVLO), thermal shutdown (OTP, when SPS driver IC over temperature condition), phase fault detection, preliminary over voltage protection (Pre-OVP, when the control MOSFET is shorted), and programmable cycle-by-cycle over current protection (OCP, when in overload condition).

#### **Tri-State PWM Input**

The uP9642B PWM accepts standard 3-level input signals. When PWM logic input is high, it turns on the control

MOSFET and turns off the synchronous MOSFET once the POR of VCC is granted and EN is kept high. When logic is low, it turns off the control MOSFET and turns on the synchronous MOSFET. If the PWM input is floated, the internal circuit will pull the PWM pin into the tri-state region and turn off the control MOSFET and synchronous MOSFET. The PWM pin voltage is kept around 1.5V by internal bias circuit when floating.

#### Deep-Sleep Mode

If VCC is ready but EN is pulled low, the power stage will enter deep-sleep mode. The gate driver circuitry will be disabled immediately and PWM pin will be in high input impedance state and most of the logic circuitry will be shut down to lower the biasing current to less than typical 200uA. The IMON output will be shorted to ground in deep-sleep mode. When EN pin is pulled high, the power stage will be activated and able to respond to the PWM signal after maximum 15us delay time.

#### Over Temperature Protection and Flag (OTP)

The TOUT/FLT pin of uP9642B is a thermal monitor output in normal operation. Once the temperature of driver IC goes above the rising threshold (130°C)(the temperature of control MOSFET may reach up to 150°C), the TOUT/FLT output will raise fault flag to 3.3V immediately and the driver will be turned off for self-protection. The TOUT/FLT will remain high until temperature of driver IC falls below the falling threshold (115°C) (the temperature of control MOSFET may reach 130°C). The driver will resume switching when the temperature of driver IC falls below 115°C.

#### Phase Fault Detection and Flag

The phase fault circuit monitors the SW node with respect to ground when VCC POR is granted and PWM input transits from high to low and the synchronous MOSFET is still conducting. If there is a control MOSFET failure which causes the switch node voltage to exceed the control MOSFET Short Threshold (V<sub>PHASFLT\_TH</sub>=400mV), a phase fault will be activated. The TOUT/FLT will be pulled high to 3.3V immediately and will remain high until the phase fault condition is released. When TOUT/FLT is flagged high, SPS continues to respond to PWM pulses.

#### VCC/VDRV Under Voltage Lockout (UVLO)

The uP9642B features both internal UVLO circuitry to monitor the VCC and VDRV pins separately. When a VCC or VDRV UVLO condition is detected, the driver will be in tri-state by shutting down both MOSFETs. In addition, IMON and TOUT/FLT pins will be pulled down to ground to indicate there is a UVLO fault. When both VCC UVLO and VDRV UVLO faults are cleared, the TOUT/FLT and IMON pins will be released and the driver will resume switching.

### **Functional Description**

# Cycle-by-Cycle Over Current Protection (OCP) and Flag

With cycle-by-cycle self-protection, the current of synchronous MOSFET will be monitored every cycle. The over current threshold is programmable by connecting an external resistor  $R_{\text{OCSET}}$  between OCSET and AGND pins, refer to (EQ1). When OCSET pin is floating or shorted to VCC, the OCSET threshold is fixed to 80A. It is recommended to keep  $R_{\text{OCSET}}$  above 37.5k $\Omega$  to keep OCP level under 80A.

Once the current exceeds the over current threshold ( $I_{\text{CC\_OCP}}$ ), the internal logic of SPS will automatically reduce the PWM duty cycle so that the inductor current is allowed to relieve

$$I_{CC\_OCP}(A) = \frac{3000(k\Omega \times A)}{R_{OCSET}(k\Omega)} \quad \text{(EQ1)}$$

The TOUT/FLT pin will be pulled high to 3.3V after 9 cycles rise-fall events where a severe over current event has been registered. The TOUT/FLT fault flag will clear once no severe over current event is registered within one consecutive PWM cycle. When TOUT/FLT is flagged high, SPS continue to respond to PWM pulses.

#### Preliminary Over Voltage Protection Flag (Pre-OVP)

The Pre-OVP feature is to protect the load during the VCC power up period, especially from control MOSFET short failure. It works against pre-biased start-up when pre-charged output voltage is higher than the Pre-OVP threshold. When the VIN rail is powered up but the controller is not powered up, the controller cannot react to any over voltage condition at the load side and all PWMs are tristated. Pre-OVP feature is active and allows the power stage to turn on the synchronous MOSFET when VCC is in transition from pre-POR to POR and SW node voltage exceeds Pre-OVP threshold. This function is to protect the CPU from damage.

When VCC UVLO clears and there is no existing pre-biased over voltage condition, the pre-OVP feature will be disabled after receiving the first PWM pulse from the controller. The controller must manage its output voltage from that moment on.

When VCC UVLO clears and the preliminary over voltage condition remains, the synchronous MOSFET will be latched ON regardless of the PWM input and the TOUT/FLT pin will be latched high to 3.3V so that the controller can detect the fault event after it is powered up. The fault can be cleared by an under voltage condition on VCC.

#### Temperature Sense Output and Fault Flag (TOUT/FLT)

The uP9642B incorporates an internal temperature sensing circuitry from driver IC to provide a linear voltage slope of 8mV/°C with a 0.6V offset at 0°C on the TOUT/FLT pin, refer to (EQ2). In multi-phase systems the uP9642B temperature outputs can be connected together on the bus and enable to provide the highest temperature to controller IC.

$$V_{TOUT/FLT}(V) = 0.6V + \frac{0.008V}{^{\circ}C} \times T(^{\circ}C)$$

(EQ2)

The TOUT/FLT also provides four fault flag conditions as follows, over temperature, phase fault, over current, and preliminary over voltage conditions. TOUT/FLT will be pulled up to 3.3V internally if any fault event of the above-mentioned is detected. The TOUT/FLT can also be used as an indicator of low VCC voltage as it will be weakly pulled down to ground under the VCC UVLO condition. In a multi-phase system where the TOUT/FLT pins are tied together, once any faults occur in the phases, TOUT/FLT is able to be pulled to 3.3V internally.

#### Internal Current Sensing and Reporting (IMON, REFIN)

The uP9642B provides an internal real-time synchronous MOSFET current sense circuit. To use VOS pin and REFIN pin and synchronous MOSFET to make a current signal simulating the inductor current which reports to the controller. The current sense amplifier circuit in the uP9642B is completely temperature compensated for  $R_{\scriptscriptstyle DS(ON)}$  of synchronous MOSFET. The current signal will be reported to the controller in the form of a differential voltage between IMON pin and REFIN pin with a conversion gain 5mV/A to the actual inductor current  $I_{\rm L}$ , refer to (EQ3). The REFIN voltage is an externally supplied DC voltage from controller IC or other power rail in system.

$$V_{IMON}(V) - V_{REFIN}(V) = \frac{0.005V}{A} \times I_L(A)$$

(EQ3)

The internal current sense circuit of the uP9642B may replace the standard inductor DCR and greatly improve system efficiency.

# uP9642B

# **Absolute Maximum Rating**

| VCC/VDRV/EN/PWM/VOS                  | CC+0.3V)<br>0.3V to 25V |

|--------------------------------------|-------------------------|

| VIN                                  | ).3V to 25V             |

| BOOT to PHASE  DC                    |                         |

| DC                                   | .3V to +6V              |

|                                      | .3V to +6V              |

|                                      |                         |

|                                      | V to +6.6V              |

| VIN to SW/PHASE                      |                         |

| DC                                   | 3V to +25V              |

| < 2ns                                |                         |

| < 100ns                              | -                       |

| SW to GND                            | 127 V                   |

| DC                                   | 3\/to±25\/              |

| < 2ns                                |                         |

| < 100ns                              |                         |

| PHASE to GND                         | +Z/V                    |

| DC                                   | 2)/40 . 25)/            |

|                                      |                         |

| < 2ns                                |                         |

| <100ns                               | )V to +30V              |

| BOOT to GND                          |                         |

| DC 0V to (VD                         | ,                       |

| <2ns                                 | 3V to +31V              |

| GL to GND                            |                         |

| DC                                   |                         |

| <2ns                                 |                         |

| Storage Temperature Range            |                         |

| Junction Temperature                 | 150°C                   |

| Lead Temperature (Soldering, 10 sec) | 260°C                   |

| ESD Rating (Note 2)                  |                         |

| HBM (Human Body Mode)                | 2kV                     |

| CDM (Charged Device Mode)            | 4147                    |

### **Thermal Information**

| Package Thermal Resistance                               |                                 |

|----------------------------------------------------------|---------------------------------|

| VQFN6x5-39L $\theta_{JA}$                                | 25°C/W                          |

| $VQFN6x5-39L\theta_{J-PCB}$                              |                                 |

| $VQFN6x5-39L\theta_{J-TOP}$                              | 11°C/W                          |

| Power Dissipation, P <sub>D</sub> @T <sub>A</sub> = 25°C |                                 |

| VQFN6x5-39L                                              | 4W                              |

| Recommended Operation Conditions                         |                                 |

| (Note 3)                                                 |                                 |

| Operating Junction Temperature Range                     |                                 |

| Operating Ambient Temperature Range                      |                                 |

| VIN                                                      | 4.5V <sup>(Note 4)</sup> to 16V |

| \(\text{OOA} \pi \pi \text{V}\)                          | 4 - 1 / 4 1 /                   |

- Note 1. Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

- Note 2. Devices are ESD sensitive. Handling precaution recommended.

- **Note 3.** The device is not guaranteed to function outside its operating conditions.

- **Note 4.** The on-time of synchronous MOSFET must be greater than 800ns to ensure effective and correct current sensing for IMON signal.

### **Electrical Characteristics**

$(V_{CC} = V_{DRV} = 5V, T_A = 25^{\circ}C, unless otherwise specified)$

| Parameter                               | Symbol Test Conditions  |                                                                     |     |      | Max  | Units |

|-----------------------------------------|-------------------------|---------------------------------------------------------------------|-----|------|------|-------|

| Supply Input                            | •                       |                                                                     |     |      |      | !     |

|                                         | I <sub>VCC_ENH</sub>    | EN=1,PWM=600kHz,Duty=15%                                            |     | 6    | 7.8  | 0     |

| VCC Supply Current                      | I <sub>VCC_ENF</sub>    | EN=1, PWM floating                                                  |     | 6    |      | mA    |

|                                         | I <sub>VCC_ENL</sub>    | EN=0                                                                |     | 200  | 260  | uA    |

| VCC POR Threshold                       | V <sub>CCRTH</sub>      | V <sub>vcc</sub> rising                                             | 3.8 | 4    | 4.2  | V     |

| VCC POR Hysteresis                      | V <sub>CCHYS</sub>      |                                                                     |     | 0.2  |      | V     |

|                                         | l <sub>VDRV_ENH</sub>   | EN=1,PWM=600kHz,Duty=15%                                            |     | 30   |      | mA    |

| VDRV Supply Current                     | l <sub>VDRV_ENF</sub>   | EN=1, PWM floating                                                  |     | 0.02 | 1    | mA    |

|                                         | <br>VDRV_ENL            | EN=0                                                                |     | 0.5  | 1    | uA    |

| VDRV POR Threshold                      | $V_{\text{DRVRTH}}$     | V <sub>VDRV</sub> rising                                            | 3.8 | 4    | 4.2  | V     |

| VDRV POR Hysteresis                     | V <sub>DRVHYS</sub>     |                                                                     |     | 0.2  | -    | V     |

| Enable Input                            |                         |                                                                     |     |      |      |       |

| Input High                              | EN <sub>H</sub>         |                                                                     | 2   |      | -    | V     |

| Input Low                               | EN <sub>L</sub>         |                                                                     |     |      | 0.8  | V     |

| Proposition Polov                       | T <sub>PDHDEN</sub>     | PWM=0. Measured from EN rising edge to GL>1V.                       |     |      | 15   | us    |

| Propagation Delay                       | T <sub>PDLDEN</sub>     | PWM=0. Measured from EN falling edge to GL<4V.                      |     | 30   | 55   | ns    |

| PWM Input                               |                         |                                                                     |     |      |      |       |

| PWM High Voltage                        | $V_{\text{IH\_PWM}}$    | PWM low to high or tri-state to high                                | 2.4 |      |      | V     |

| PWM Low Voltage                         | $V_{\text{IL\_PWM}}$    | PWM high to low or tri-state to low                                 |     |      | 0.6  | V     |

| Tri-State Open Voltage                  | V <sub>HiZ_PWM</sub>    | PWM input floating                                                  | 1.4 | 1.5  | 1.6  | V     |

|                                         |                         | PWM=0V                                                              |     | -210 | -260 |       |

| PWM Input Current                       | <b>I</b> <sub>PWM</sub> | PWM=3.3V                                                            |     | 210  | 260  | uA    |

|                                         |                         | PWM=5V                                                              |     | 210  | 260  |       |

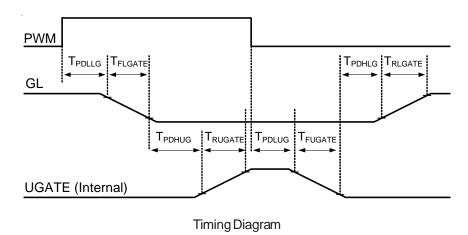

| PWM Propagation Delay and De            | ad Time F               | Range (Refer to Timing Diagram on P.10                              | 0)  |      |      |       |

| PWM High Propagation Delay              | T <sub>PDLLGATE</sub>   | PWM going high to GL going low VIH_PWM to 90% GL                    |     | 20   |      | ns    |

| PWM Low Propagation Delay               | _                       | PWM going low to SW going low VIL_PWM to 90% SW                     |     | 20   |      | ns    |

| Tri-State to Turn-On Propagation Delay  | T <sub>PDTSGHH</sub>    | PWM (from tri-state) going high to SW going high, VIH_PWM to 10% SW |     | 15   |      | ns    |

| Tri-State to Turn-Off Propagation Delay | T <sub>PDTSGLH</sub>    | PWM (from tri-state) going low to GL going high, VIL_PWM to 10% GL  |     | 15   |      | ns    |

| Tri-State Shut-Off Time                 | T <sub>PDTSOFF</sub>    | PWM (from low) going tri-state to GL going low, VIL_PWM to 10% GL   |     | 25   |      | ns    |

|                                         |                         |                                                                     |     |      |      |       |

# **Electrical Characteristics**

| Parameter                                 | Symbol                        | Test Conditions                                                                      | Min   | Тур  | Max   | Units |

|-------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------|-------|------|-------|-------|

| PWM Propagation Delay and De              | ad Time (c                    | ont.)                                                                                |       |      |       |       |

| GL Off to SW On Dead Time                 | T <sub>PDHUGATE</sub>         |                                                                                      |       | 15   |       | ns    |

| SW Off to GL On Dead Time                 | T <sub>PDHLGATE</sub>         |                                                                                      |       | 20   |       | ns    |

| Minimum SW Pulse Width                    | T <sub>MINSW</sub>            |                                                                                      |       | 50   |       | ns    |

| Internal Bootstrap Switch                 |                               |                                                                                      |       |      |       |       |

| Forward Voltage                           | $V_{\scriptscriptstyle{FWD}}$ | VDRV to BOOT, I <sub>BOOT</sub> = 10mA,<br>PWM = floating                            |       | 500  |       | mV    |

| On Resistance                             | $R_{\rm sw}$                  | VDRV to BOOT, I <sub>BOOT</sub> = 10mA,<br>PWM = 0V                                  |       | 15   |       | Ω     |

| Temperature Sense Output and              | Fault Flag                    | - TOUT / FLT                                                                         |       |      |       |       |

| Temperature Sense Slope                   | T <sub>SNS_GAIN</sub>         | $0^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C} \text{ (Note 1)}$ | 7.8   | 8    | 8.2   | mV/ºC |

| Temperature Sense Offset Voltage          |                               | $T_J = 90^{\circ}C, 0.6V + 8mV/^{\circ}C^*T_J$                                       | 1.302 | 1.32 | 1.338 | ٧     |

| TOUT Source Current                       | L<br>TOUT_SRC                 |                                                                                      |       | 850  |       | uA    |

| TOUT Sink Current                         | L<br>TOUT_SNK                 |                                                                                      |       | 20   |       | uA    |

| Fault Mode Active High Voltage            | V <sub>FLTHIGH</sub>          | Under over temperature, over current, phase fault or pre-OV fault                    | 2.6   | 3.3  | 3.6   | V     |

| TOUT / FLT Active Low Voltage             | $V_{FLTLOW}$                  | No fault, VCC < UVLO                                                                 |       | -    | 0.28  | V     |

| Fault Mode Source Current                 | I <sub>FLTSRC</sub>           | 3.3V source to GND                                                                   |       | 3.75 |       | mA    |

| TOUT / FLT Active Pull Down<br>Resistance | R <sub>PULLDN_TOUT</sub>      | No fault, VCC < UVLO, VCC = 3.5V                                                     |       | 10   |       | Ω     |

| Current Sense Output - IMON (7            | $T_A = T_J = 0$ °C            | C to 85°C)                                                                           |       |      |       |       |

|                                           | A <sub>cc_cs</sub>            | $T_J = 90$ °C, 20A load, REFIN = 1.2V, VCC = VDRV = 5.0V                             | -5    | 1    | +5    | %     |

| Accuracy                                  | A <sub>CC_ALL</sub>           | I <sub>OUT</sub> = 30A (Note 1)                                                      | -5    |      |       |       |

|                                           |                               | I <sub>OUT</sub> = 40A (Note 1)                                                      | -7    |      | +7    | %     |

| Gain                                      | G <sub>cs</sub>               | T <sub>J</sub> = 90°C, 20A load, REFIN = 1.2V,<br>VCC = VDRV = 5.0V(Note 1)          | 4.75  | 5    | 5.25  | mV/A  |

| IMON Active Pull Down<br>Resistance       | R <sub>PULLLDN_IMON</sub>     | VCC < UVLO                                                                           |       | 170  |       | Ω     |

| IMON Sink Current                         | CSAS                          | VCC > UVLO                                                                           |       | 0.3  |       | mA    |

| Current Monitor Reference Input Voltage   | V <sub>REFIN</sub>            | Externally supplied reference voltage                                                | 1.1   | 1.2  | 1.8   | V     |

| Phase-Fault Detection                     |                               |                                                                                      |       |      |       |       |

| HS Control MOSFET Short<br>Threshold      | V <sub>PHASFLT_TH</sub>       | V(SW) - V(PGND)(Note 1)                                                              |       | 400  |       | mV    |

| Propagation Delay for TOUT Low to Active  | T <sub>PD_TOUT</sub>          |                                                                                      |       |      | 300   | ns    |

### **Electrical Characteristics**

| Parameter                                    | Symbol                       | Test Conditions                                                                                                | Min | Тур  | Max | Units |  |  |

|----------------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|--|--|

| Over Temperature Protection                  |                              |                                                                                                                |     |      |     |       |  |  |

| Over Temp Rising Threshold                   | T <sub>OTPR</sub>            | TOUT/FLT pulled up high,<br>guaranteed by design<br>(Driver IC temperature) (Note 1)                           | 120 | 130  | 1   | °C    |  |  |

| Over Temp Falling Threshold                  | $T_{OTPF}$                   | TOUT/FLT released,<br>guaranteed by design<br>(Driver IC temperature) (Note 1)                                 | 1   | 115  | 1   | °C    |  |  |

| Preliminary Over Voltage Prote               | ction                        |                                                                                                                |     |      |     |       |  |  |

| SW Threshold                                 | V <sub>PREOVP</sub>          |                                                                                                                |     | 2.7  |     | V     |  |  |

| Programmable Cycle-by-Cycle                  | Over Curren                  | t                                                                                                              |     |      |     |       |  |  |

| Programmable Over Current<br>Threshold Range | CC_OCP                       | Program through R <sub>OCSET</sub> (Note 1)                                                                    | 20  |      | 80  | А     |  |  |

| Over Current Threshold<br>Programmable Gain  | CC_OCP_GAIN                  | R <sub>OCSET</sub> *I <sub>CC_OCP</sub>                                                                        |     | 3000 |     | kΩ*A  |  |  |

| Constant Over Current Threshold              | V <sub>OCP_CST</sub>         | T <sub>J</sub> = 90°C, OCSET open or connects to VCC (equivalent to 80A, measure IMON to REFIN)                | 370 | 400  | 430 | mV    |  |  |

|                                              |                              | $T_J = 90^{\circ}\text{C}$ , OCSET open or connects to 50k $\Omega$ (equivalent to 60A, measure IMON to REFIN) | 280 | 300  | 320 | mV    |  |  |

| OCP Detect Blanking Delay                    | T <sub>BLANK_OCP-FAULT</sub> | PWM high-low cycles to TOUT / FLT high                                                                         |     | 9    |     | cycle |  |  |

Note 1. Guaranteed by design but not tested in production.

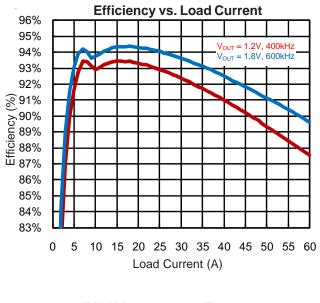

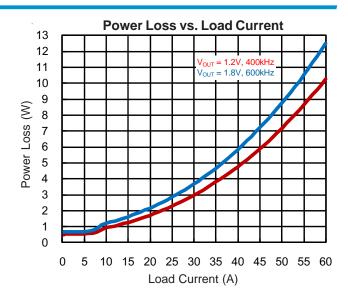

### **Typical Operation Characteristics**

# **Typical Operation Characteristics**

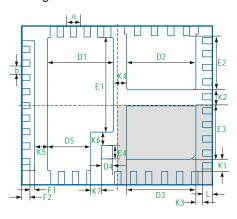

### **Package Information**

#### VQFN6X5 - 39L Package

Bottom View - Exposed Pad

| SYMBOLS  | Dimension (mm) |         | SYMBOLS | Dimension (mm) |                  |              | SYMBOLS | Dimension (mm) |           |           |     |  |

|----------|----------------|---------|---------|----------------|------------------|--------------|---------|----------------|-----------|-----------|-----|--|

| STIMBULS | MIN            | NOM     | MAX     | STIVIDULS      | MIN              | NOM          | MAX     | STIVIBULS      | MIN       | NOM       | MAX |  |

| Α        | 0.800          | 0.900   | 1.000   | D5             | 1.300            | 1.400        | 1.500   | F2             | 0.275 BSC |           | С   |  |

| A1       | 0.000          | 0.020   | 0.050   | Е              | 5                | .000 BS      | С       | K1             | 0         | 0.350 BSC |     |  |

| А3       | 0              | .200 RE | F       | E1             | 3.022            | 3.122        | 3.230   | K2             | 0         | 0.400 BSC |     |  |

| b        | 0.200          | 0.250   | 0.300   | E2             | 1.718            | 1.818        | 1.925   | K3             | 0         | 0.350 BSC |     |  |

| D        | 6              | .000 BS | С       | E3             | 1.650            | 1.750        | 1.850   | K4             | 0.400 BSC |           | С   |  |

| D1       | 2.000          | 2.100   | 2.200   | E4             | 0                | 0.450 BSC K5 |         | 0              | .400 BS   | С         |     |  |

| D2       | 1.850          | 1.950   | 2.050   | Ф              | 0.450 BSC K6 0.4 |              | .400 BS | O              |           |           |     |  |

| D3       | 1.850          | 1.950   | 2.050   | Ш              | 0.300            | 0.400        | 0.500   | K7             | 0.400 BSC |           |     |  |

| D4       | 0              | .300 BS | С       | F1             | 0.125 BSC        |              |         |                | <u>'</u>  |           |     |  |

#### Note

1. Package Outline Unit Description:

BSC: Basic. Represents theoretical exact dimension or dimension target

MIN: Minimum dimension specified.

MAX: Maximum dimension specified.

REF: Reference. Represents dimension for reference use only. This value is not a device specification.

NOM: Nominal. Provided as a general value. This value is not a device specification.

- 2. Dimensions in Millimeters.

- 3. Drawing not to scale.

- 4. These dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm.

- 5. There are tie bars exposed on package side wall and the exposed position are inconsistent depending on different vendors.

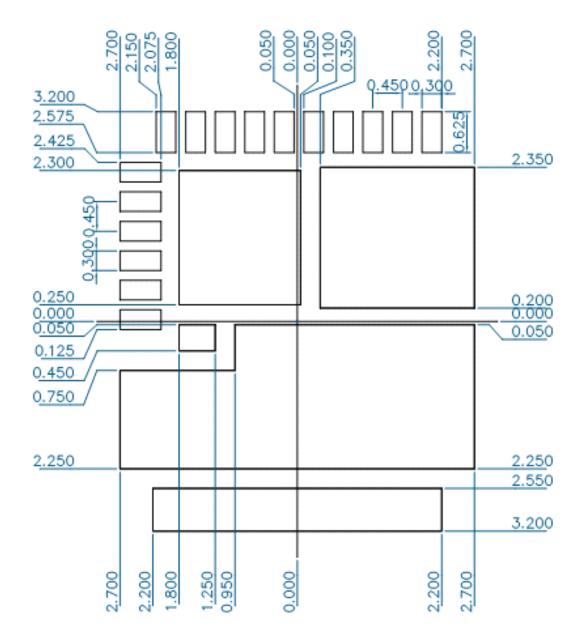

### **Package Information**

#### **Recommended PCB Land Pattern**

#### Note

- 1. Dimensions in Millimeters.

- 2. Drawing not to scale.

# **Legal Notice**

The contents of this document are provided in connection with uPI Semiconductor Corp. ("uPI") products. uPI makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice.

No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights, is granted by this publication. Except as provided in uPl's terms and conditions of sale for such products, uPl assumes no liability whatsoever, and uPl disclaims any express or implied warranty relating to sale and/or use of uPl products, including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. uPl products are not designed, intended, authorized or warranted for use as components in systems intended for medical, life-saving, or life sustaining applications. uPl reserves the right to discontinue or make changes to its products at any time without notice.

Copyright 2020 ©, uPI Semiconductor Corp. All rights reserved. uPI, uPI design logo, and combinations thereof, are registered trademarks of uPI Semiconductor Corp.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

#### uPI Semiconductor Corp.

9F.,No.5, Taiyuan 1st St. Zhubei City, Hsinchu, Taiwan, R.O.C. TEL: 886.3.560.1666 FAX: 886.3.560.1888 sales@upi-semi.com