# RELIMINARY PRODUCT INFORMATION

# MOS INTEGRATED CIRCUIT $\mu$ PD161802

# 240 OUTPUTS TFT-LCD SOURCE DRIVER WITH RAM

#### **DESCRIPTION**

The  $\mu$  PD161802 is a TFT-LCD source driver that includes display RAM

This driver has 240 outputs, a display RAM capacity of 172.8 K bytes (240 pixels x 18 bits x 320 lines) and can provide a 262,144-color display.

## **FEATURES**

- TFT-LCD driver with on-chip display RAM

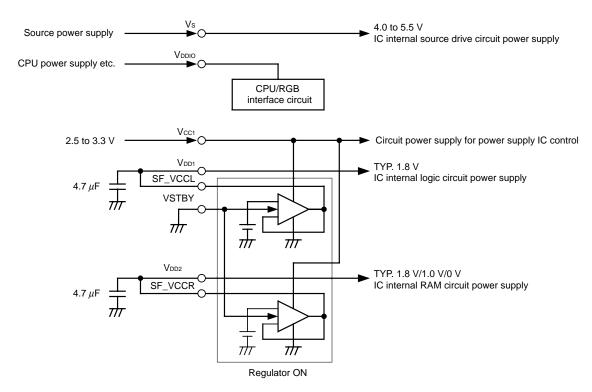

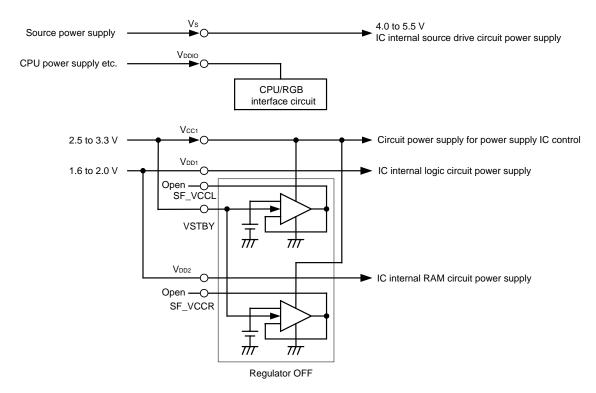

- Logic power supply voltage: 1.6 to 2.0 V (Can also be generated within chip from power IC interface's power supply)

- CPU/RGB interface voltage: 1.8 to VDD

- Power supply IC interface power supply voltage: 2.5 to 3.3 V

- Driver power supply voltage: 4.0 to 5.5 V

- Display RAM: 240 x 18 x 320 bits

- Driver outputs: 240 outputs

- CPU interface: Three types of interfaces selectable

- · 6-bit/16-bit/18-bit RGB interface (through mode, capture mode)

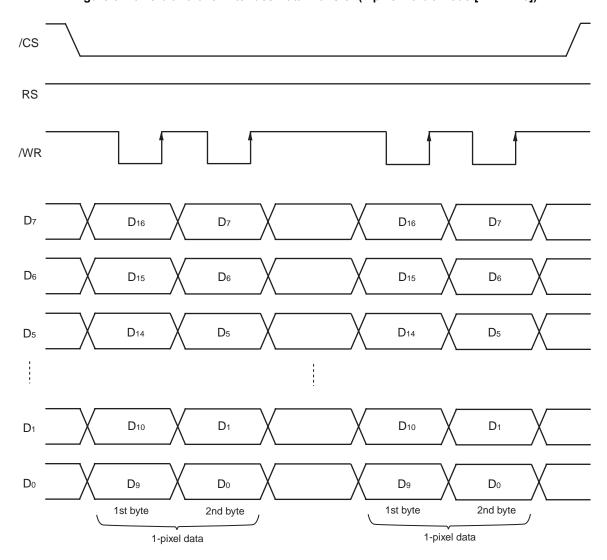

- · i80/M68 parallel interface (selectable from 8/16/18-bit)

- · 8-bit serial interface

- Colors: 262,144 colors/pixel

- On-chip timing generator

- On-chip oscillator

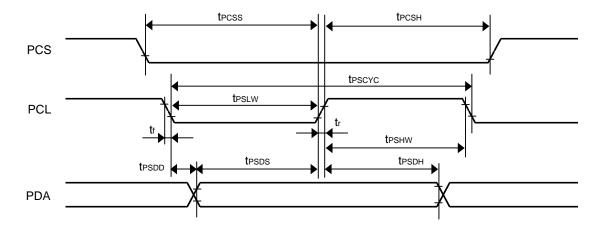

- E<sup>2</sup>PROM interface (Micro Wire)

## ORDERING INFORMATION

| Part Number | Package |

|-------------|---------|

| μ PD161802P | Chip    |

**Remark** Purchasing the above chip entails the exchange of documents such as a separate memorandum on product quality, so please contact one of our sales representatives.

The information contained in this document is being issued in advance of the production cycle for the product. The parameters for the product may change before final production or NEC Electronics Corporation, at its own discretion, may withdraw the product prior to its production. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

# **CONTENTS**

| 1. | BLOCK     | CDIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5  |

|----|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2. | PIN CO    | NFIGURATION (Pad Layout)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6  |

| 3. | PIN FUN   | ICTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13 |

| ;  | 3.1 Powe  | er Supply System Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13 |

| ;  | 3.2 Logic | : System Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16 |

| ;  | 3.3 Gate  | Driver Control Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18 |

| ;  | 3.4 RGB   | Multi-plectra Switch Control Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20 |

| ;  | 3.5 Exter | nal IC ( $\mu$ PD161862, etc.) Control Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20 |

| ;  | 3.6 Drive | r Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20 |

| ;  | 3.7 Test  | or Other Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21 |

| 4. | PIN I/O   | CIRCUITS AND RECOMMENDED CONNECTION OF UNUSED PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22 |

| 5. | DESCRI    | PTION OF FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24 |

| į  | 5.1 CPU   | Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24 |

|    | 5.1.1     | Selection of interface type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24 |

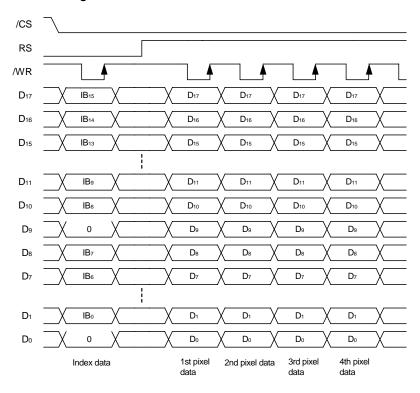

|    | 5.1.2     | Selection of data transfer mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25 |

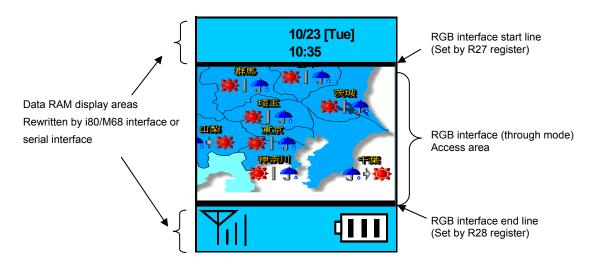

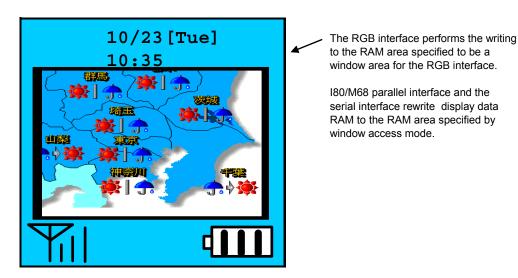

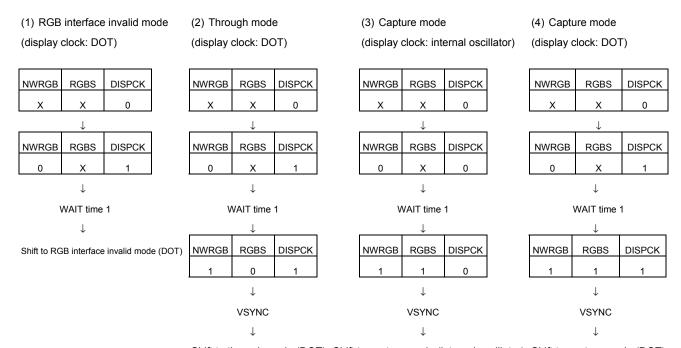

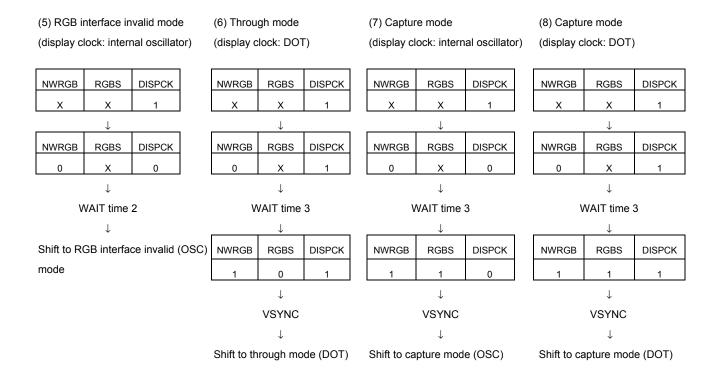

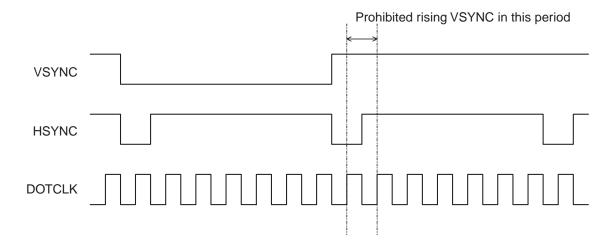

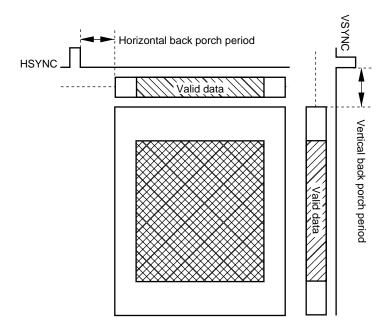

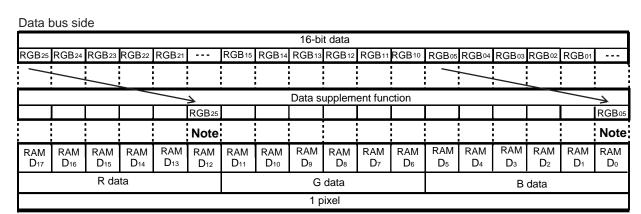

|    | 5.1.3     | RGB interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33 |

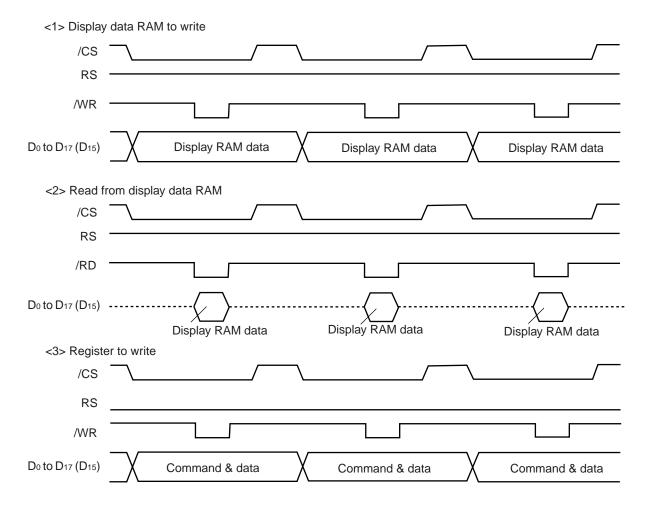

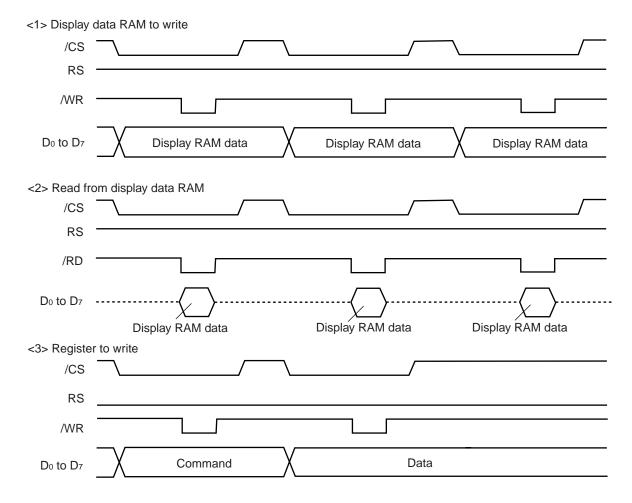

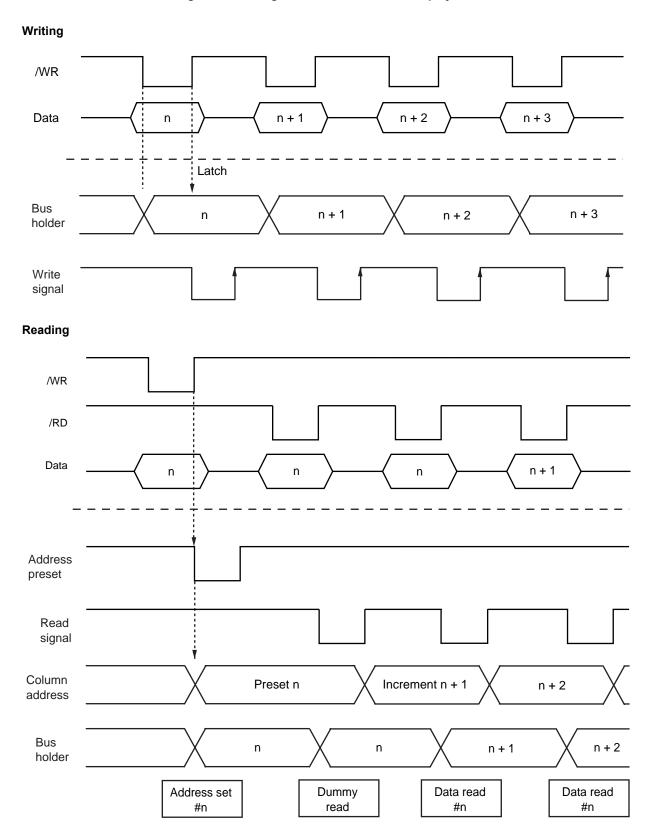

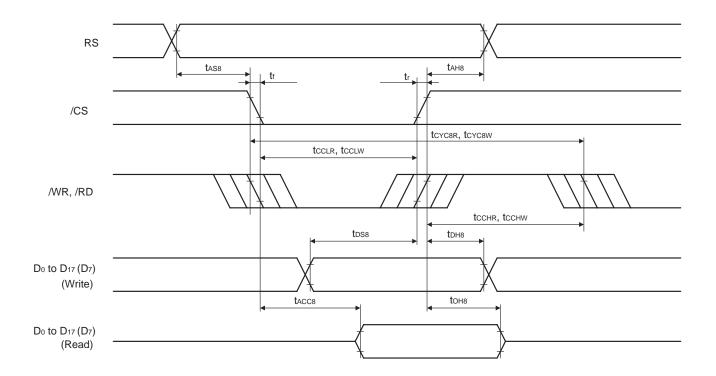

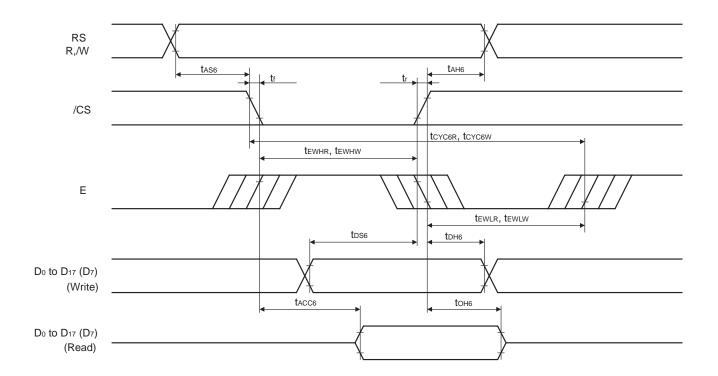

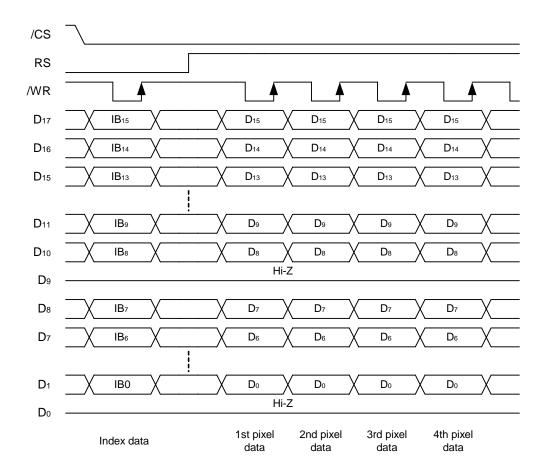

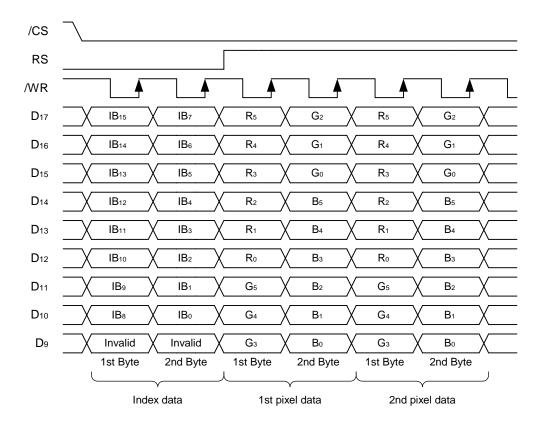

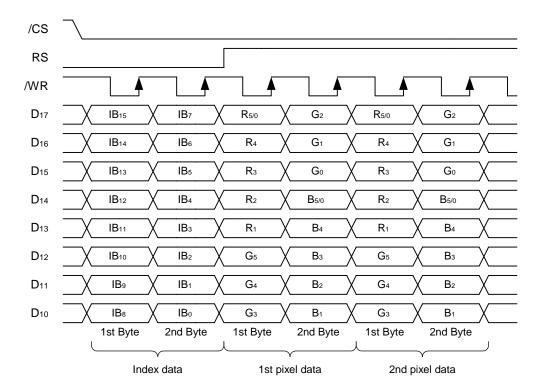

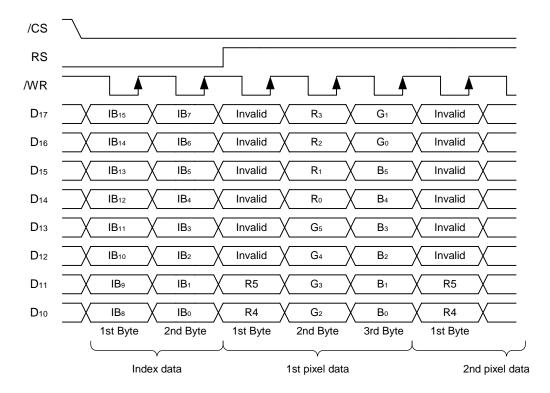

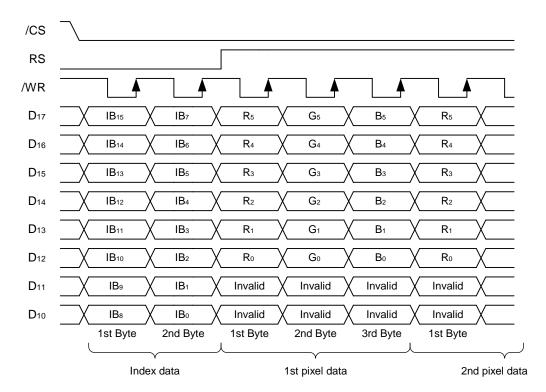

|    | 5.1.4     | i80/M68 Parallel interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 39 |

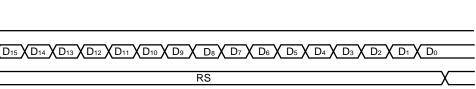

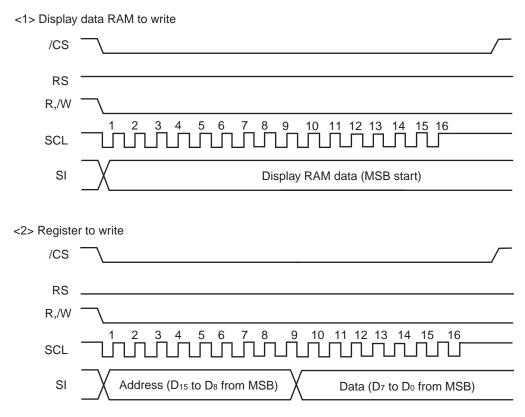

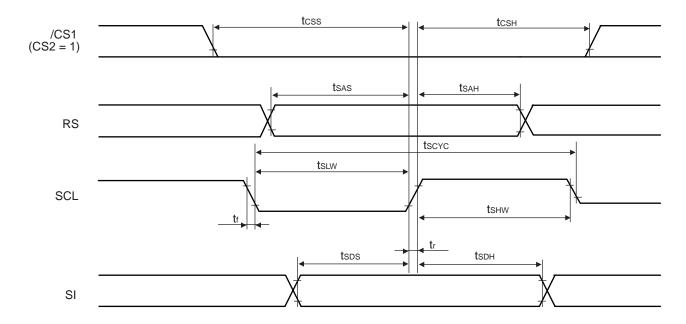

|    | 5.1.5     | Serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 41 |

|    | 5.1.6     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|    | 5.1.7     | Access to display data RAM and internal registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 42 |

|    | 5.1.8     | and the second by the second s |    |

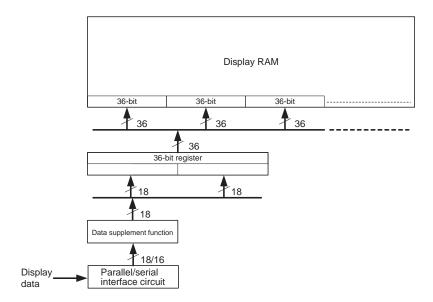

| ,  | 5.2 Displ | ay Data RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

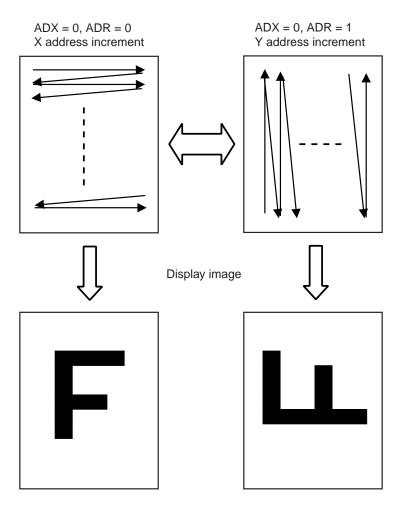

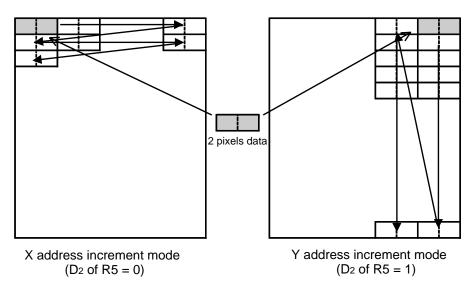

|    | 5.2.1     | X address circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 49 |

|    | 5.2.2     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

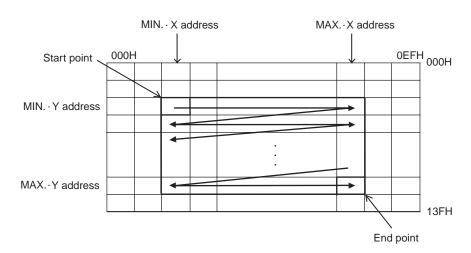

|    | 5.2.3     | Arbitrary address area access (window access mode (WAS))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 52 |

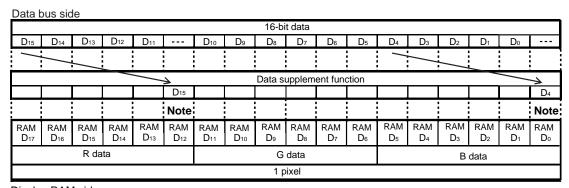

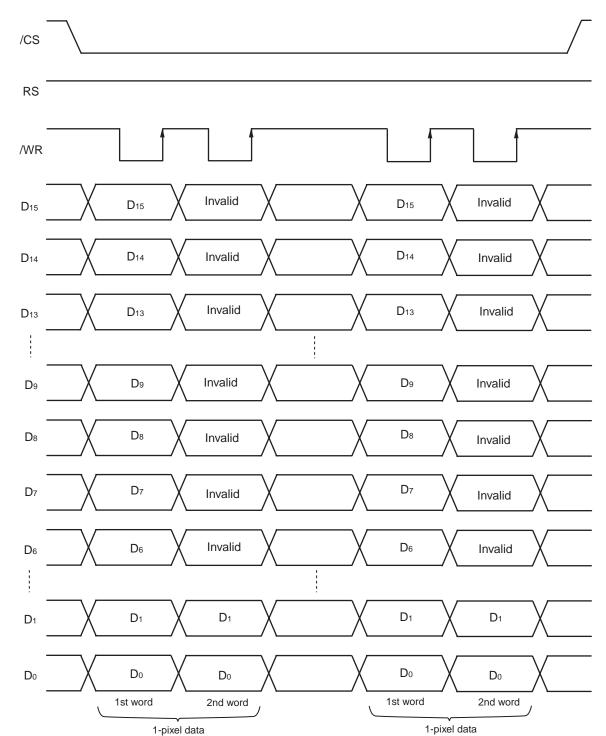

|    | 5.2.4     | High-speed RAM write mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 54 |

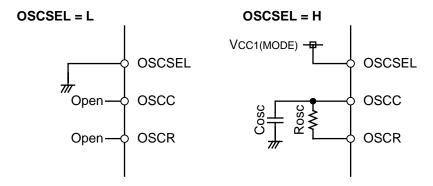

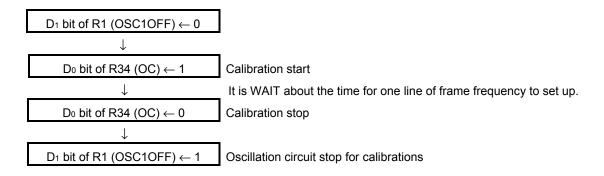

|    |           | lator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

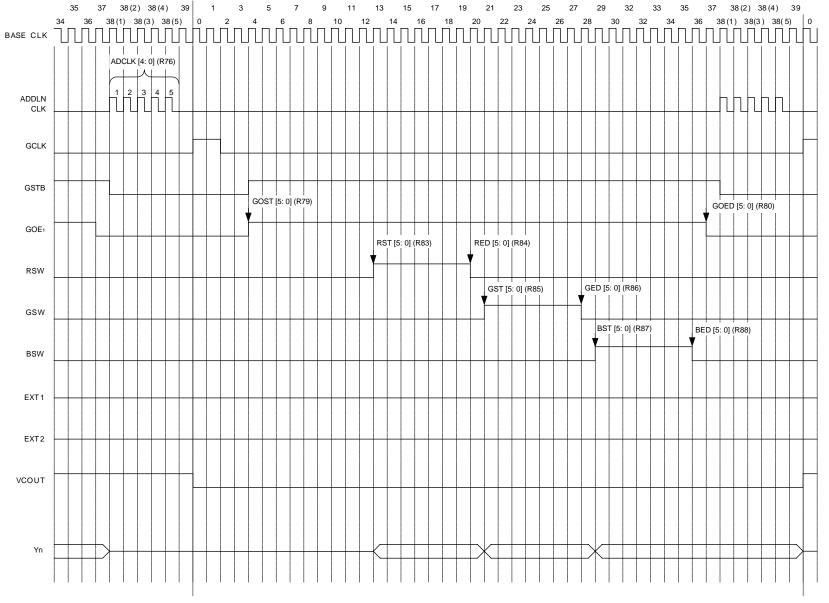

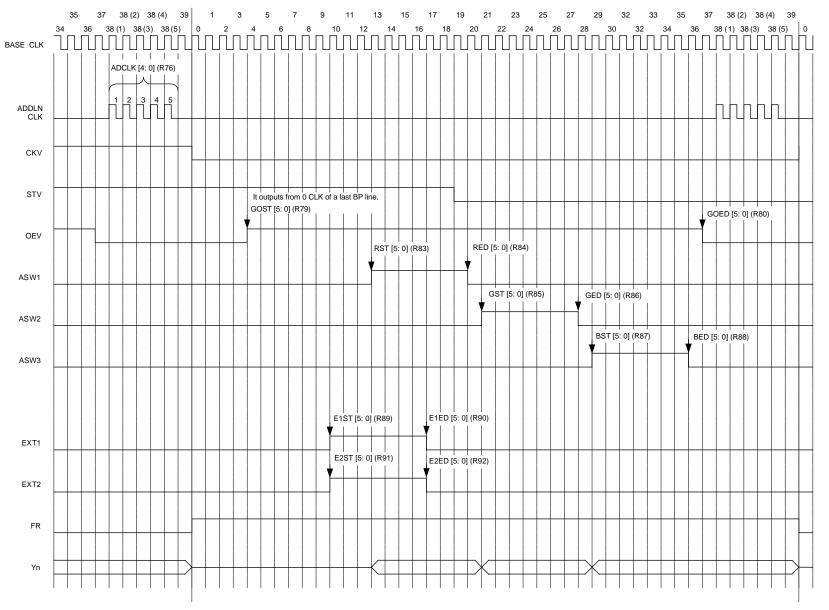

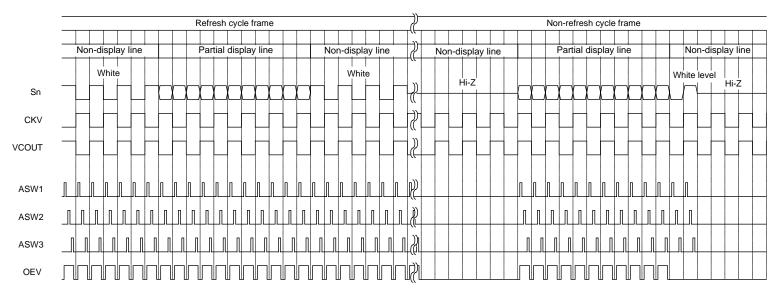

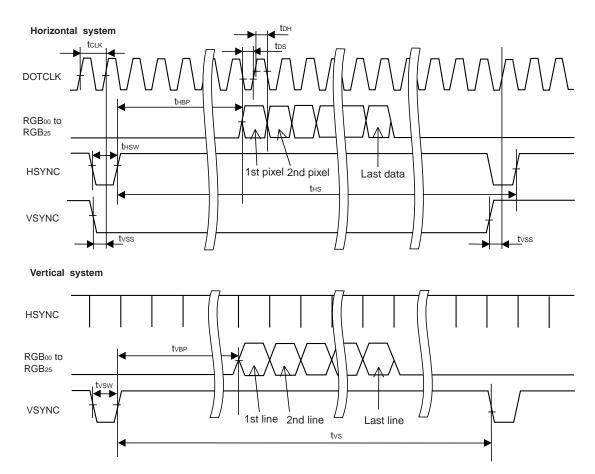

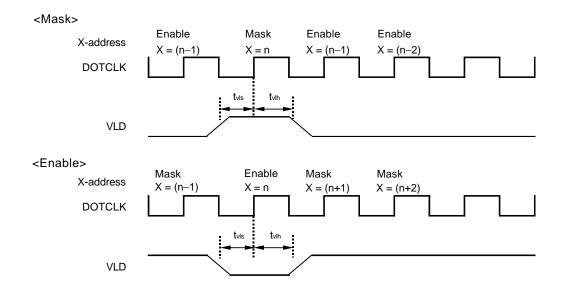

|    | 5.4 Displ | ay Timing Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 58 |

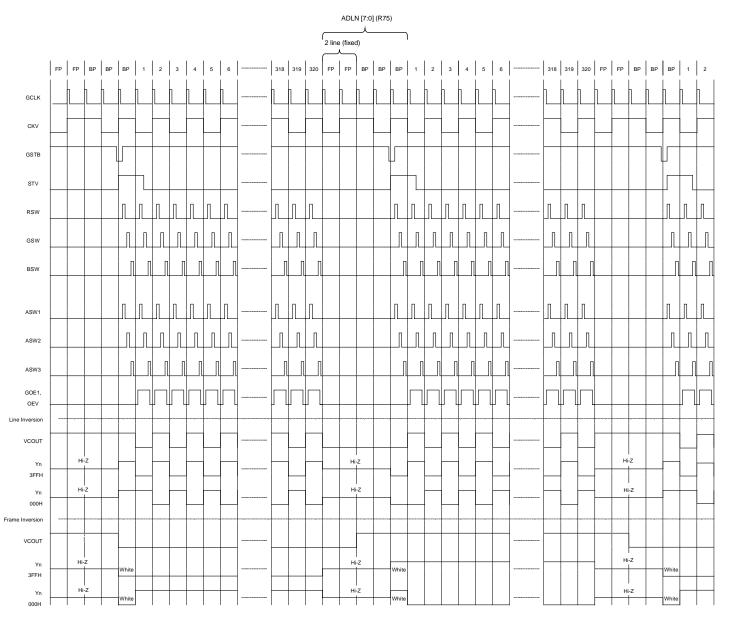

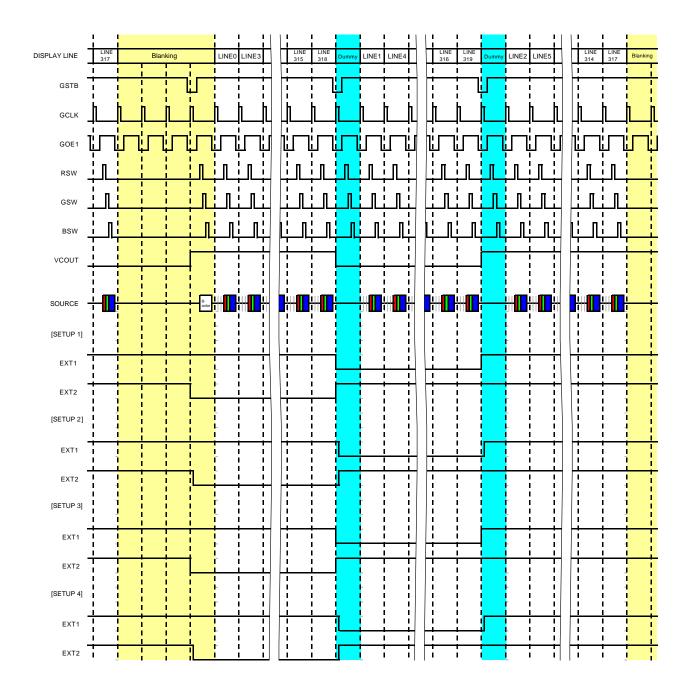

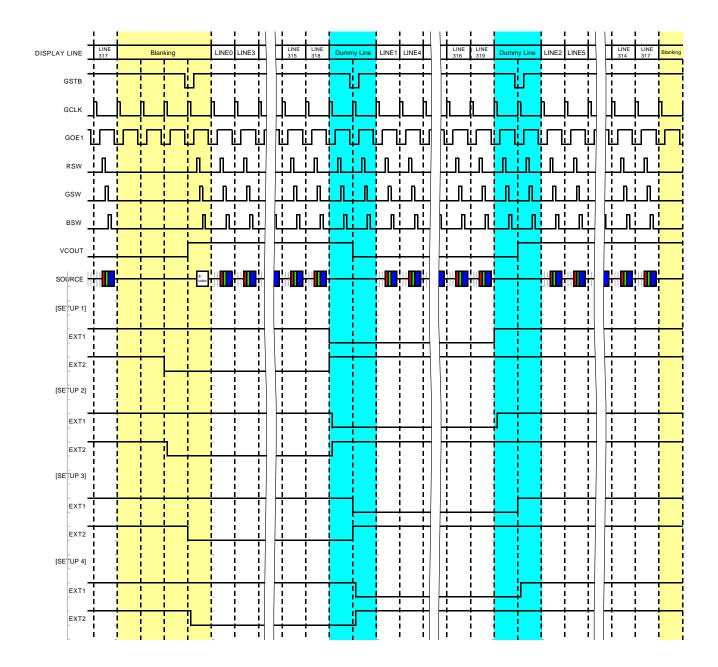

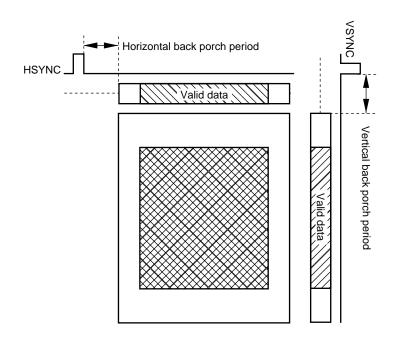

|    | 5.4.1     | 1-line period timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58 |

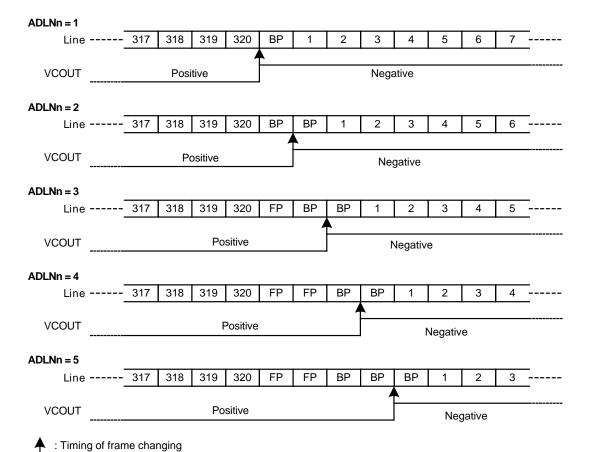

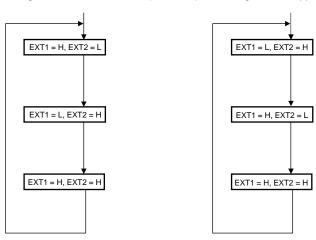

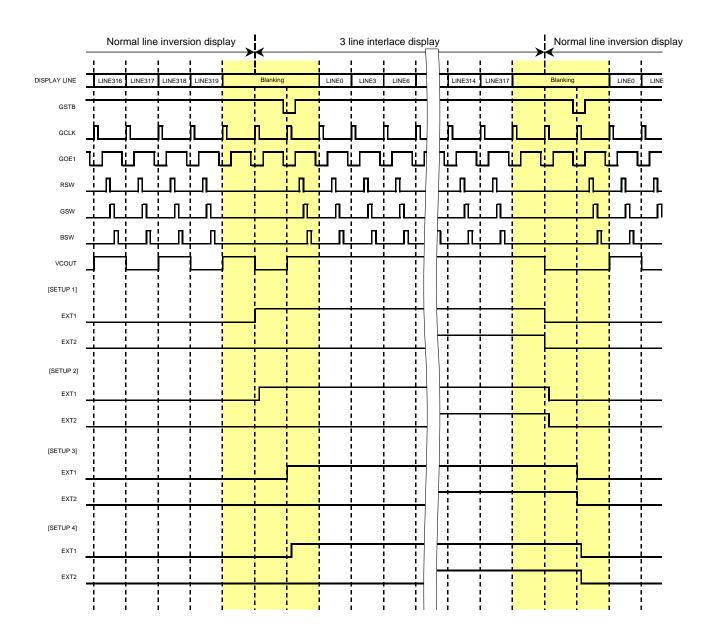

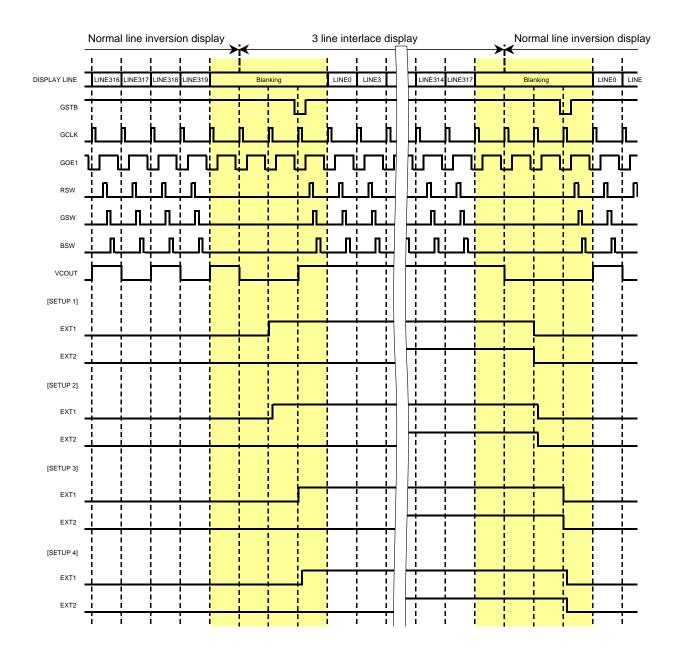

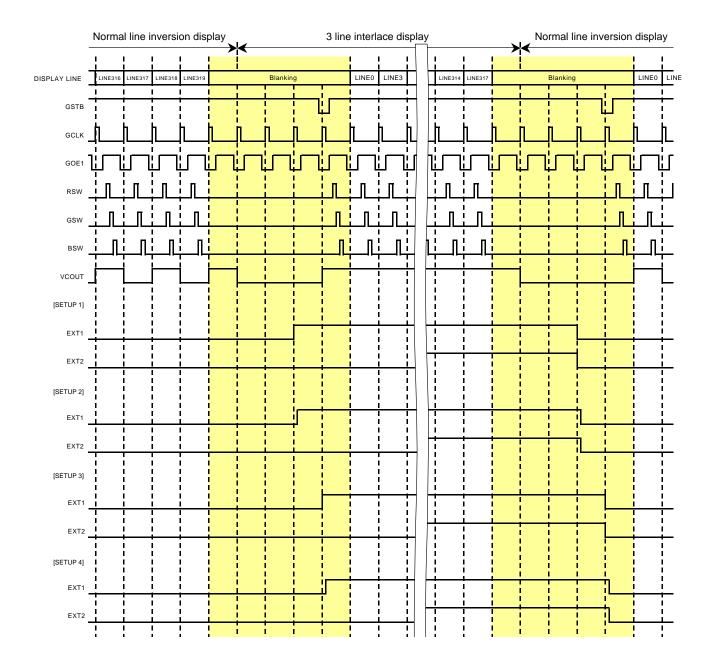

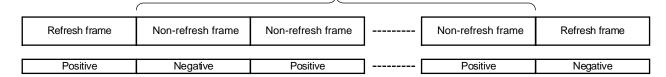

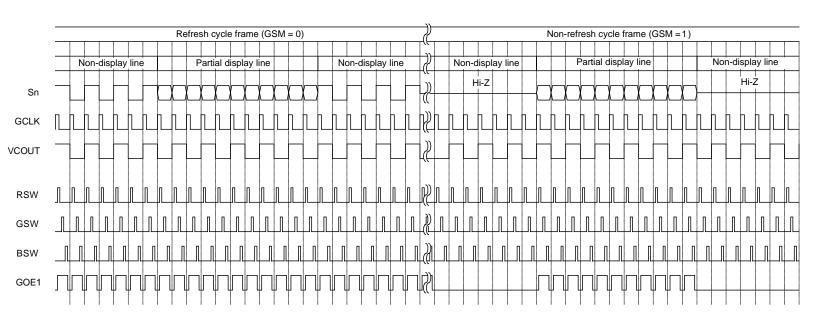

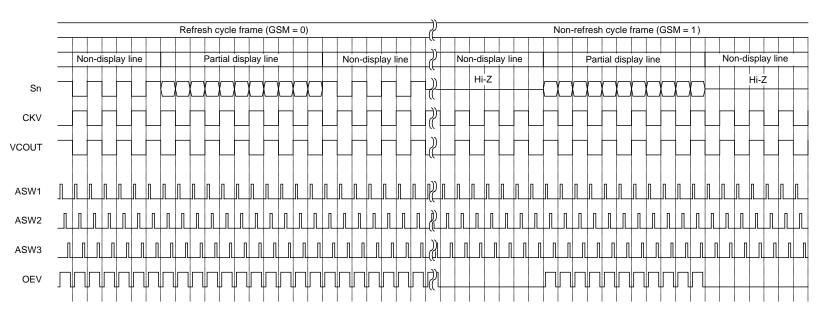

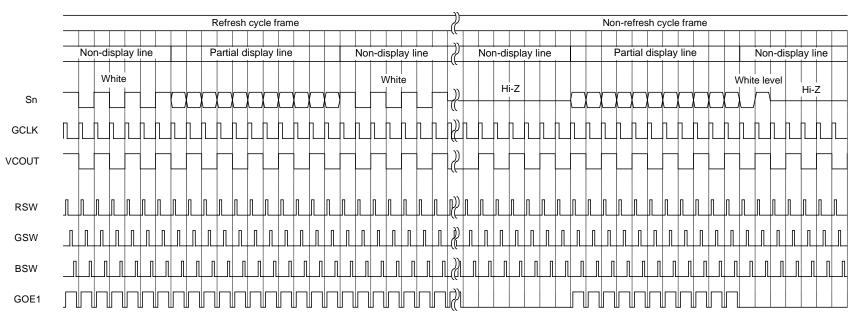

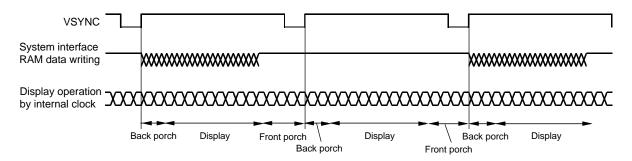

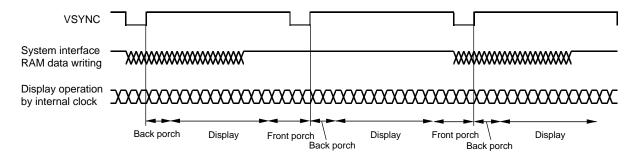

|    | 5.4.2     | 1-frame period timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|    | 5.4.3     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

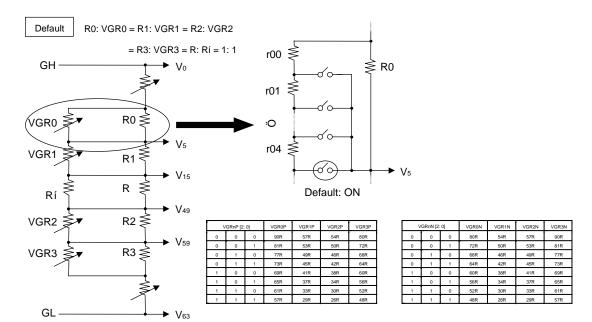

|    | 5.5 γ-Cu  | rve Correction Power Supply Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

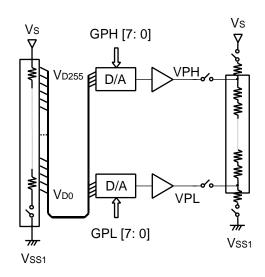

|    | 5.5.1     | Amplitude adjustment with internal amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

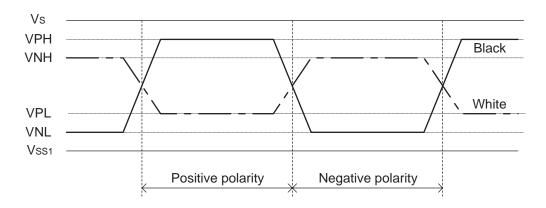

|    | 5.5.2     | Amplitude adjustment by bulit-in resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 77 |

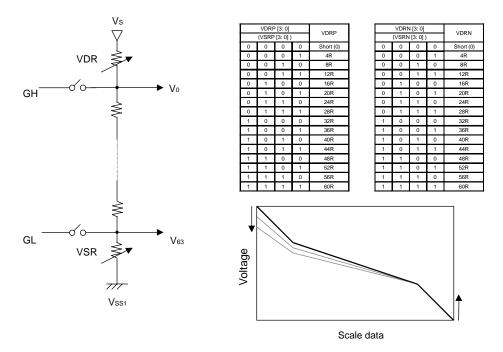

|    | 5.5.3     | Inclination adjustment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 77 |

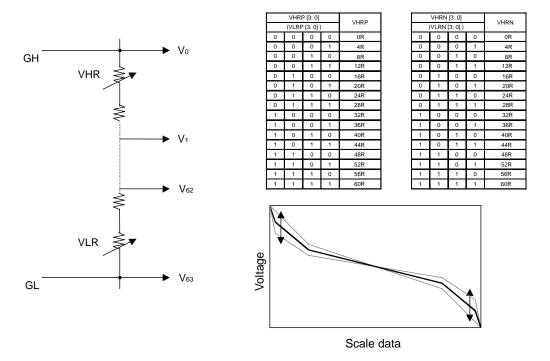

|              |        | 5.5.4       | Fine tuning adjustment                                        | 78    |

|--------------|--------|-------------|---------------------------------------------------------------|-------|

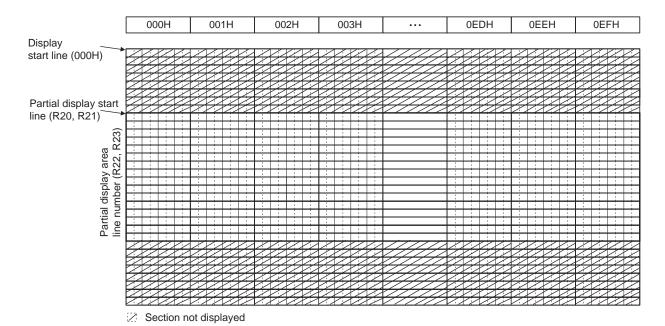

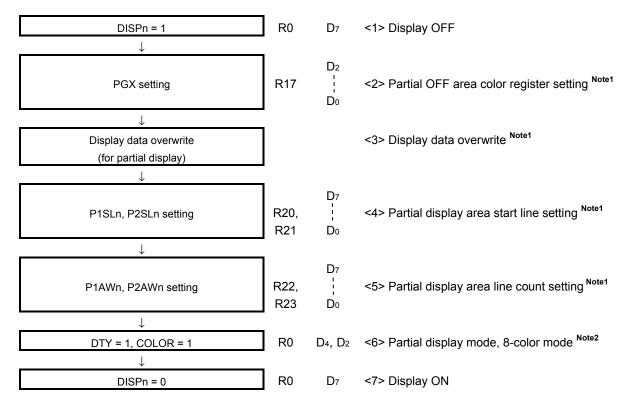

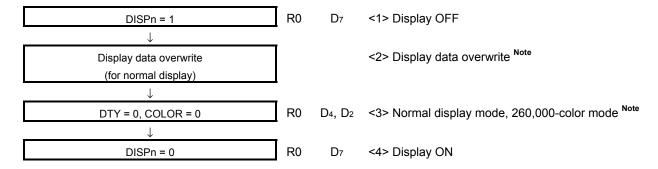

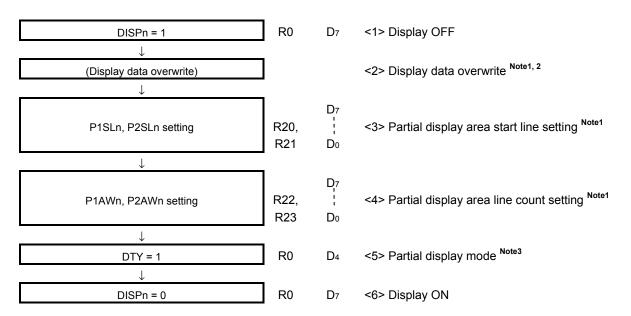

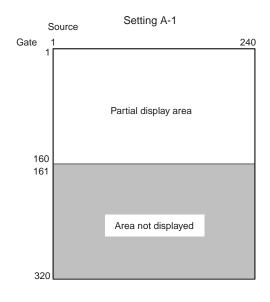

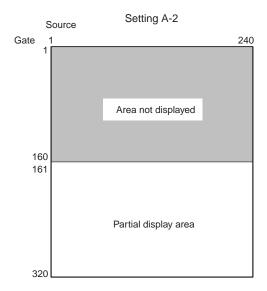

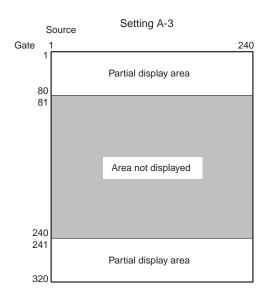

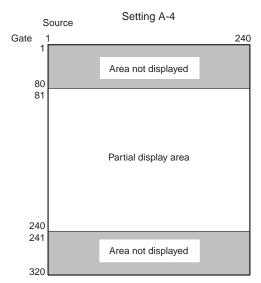

| 5            | .6     | Partial     | Display Mode                                                  | 79    |

|              |        | 5.6.1       | Partial display, non-display area driving                     | 80    |

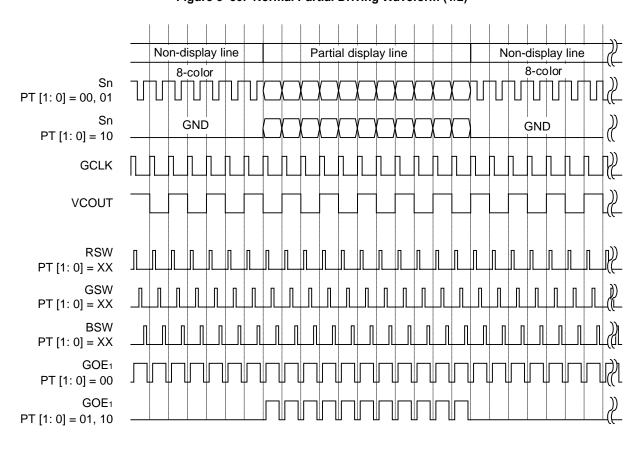

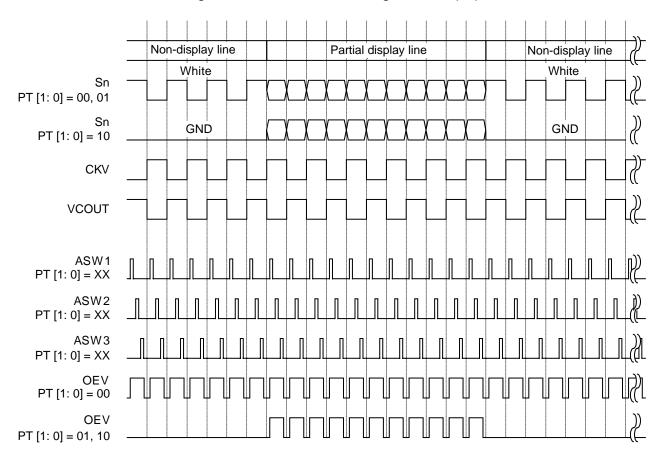

|              |        | 5.6.2       | Partial display, non-display area, and normal partial driving | 81    |

|              |        | 5.6.3       | Partial display, non-display area, and non-refrech driving    | 83    |

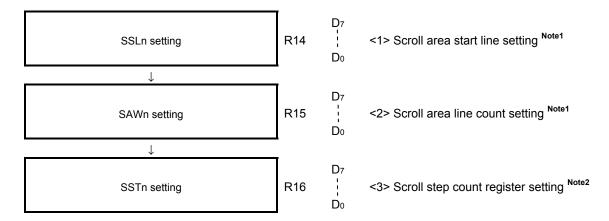

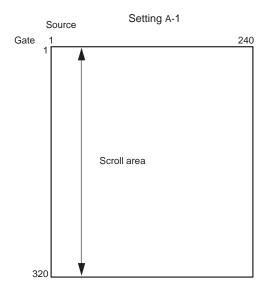

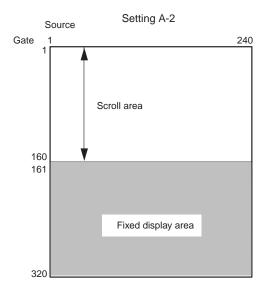

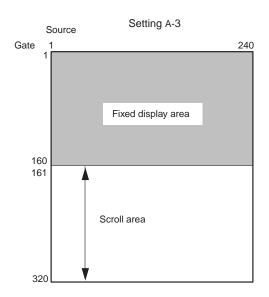

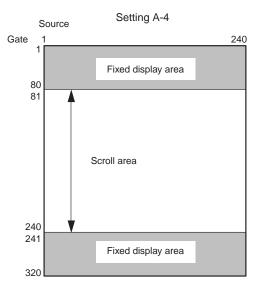

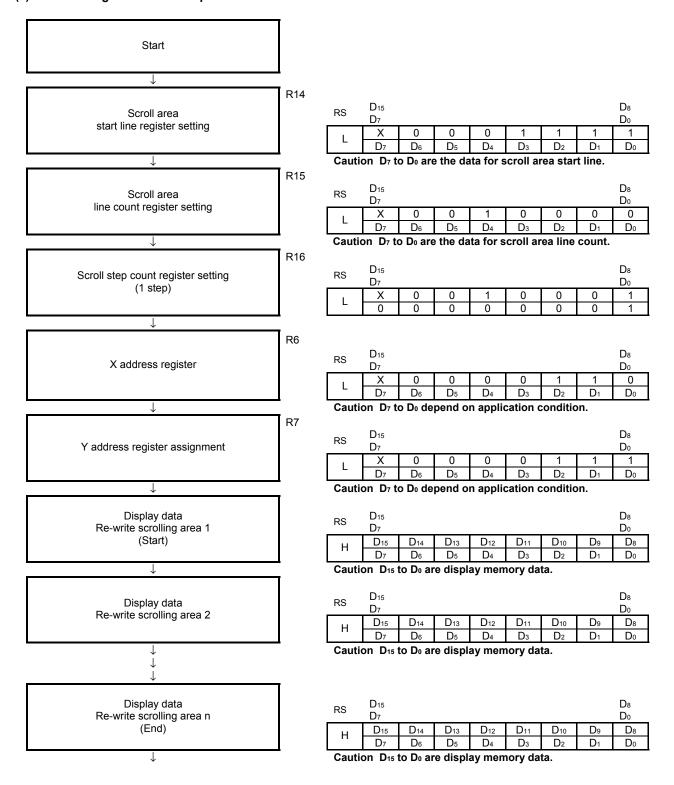

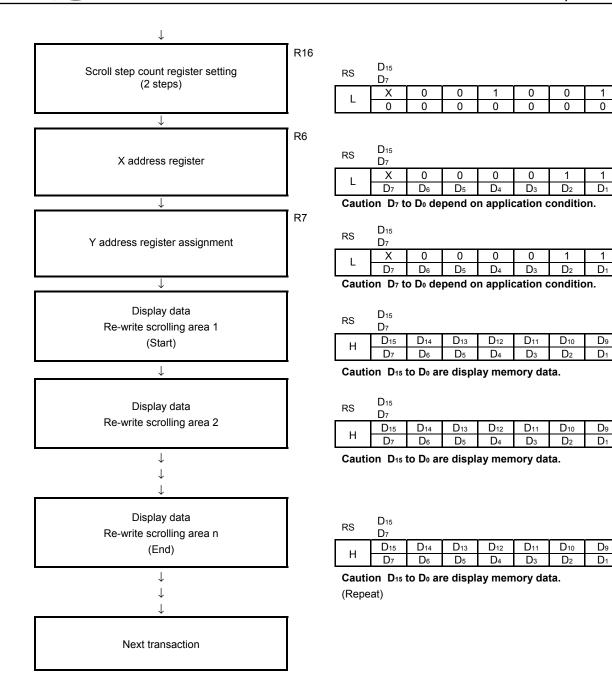

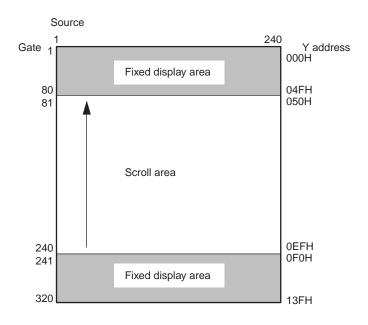

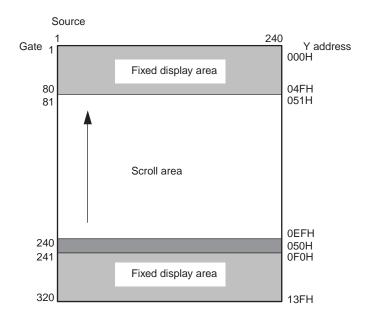

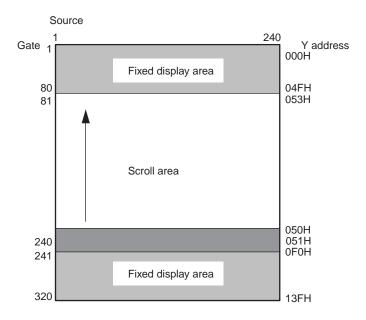

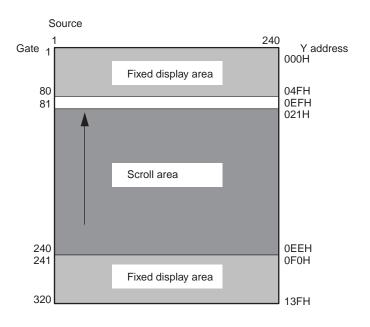

| 5            | 5.7    | Panel       | Scroll                                                        | 92    |

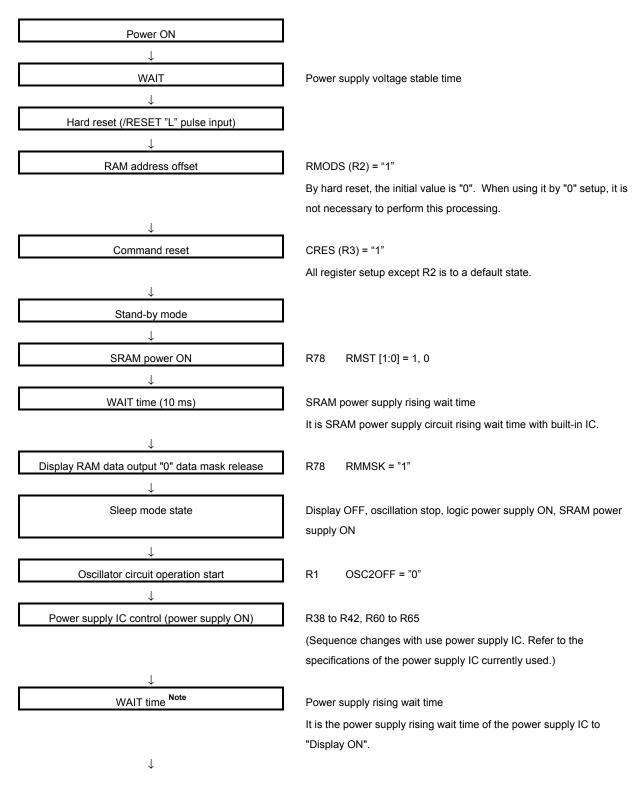

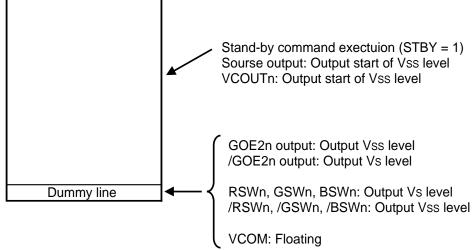

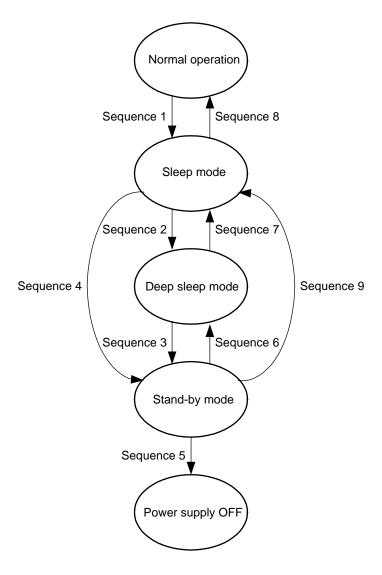

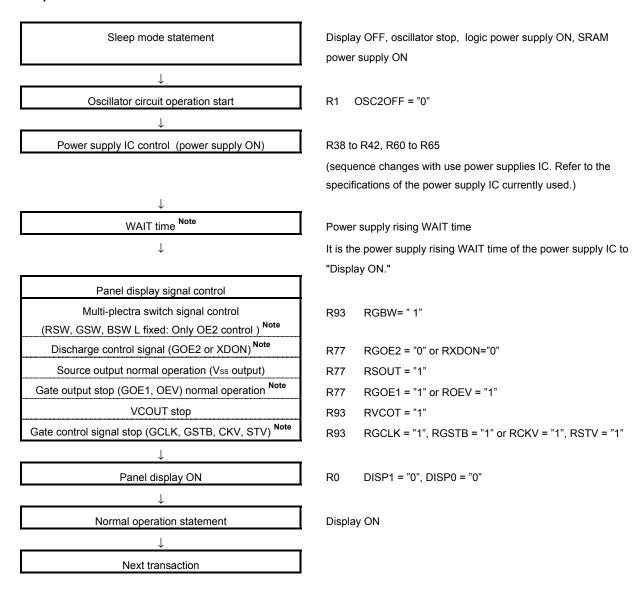

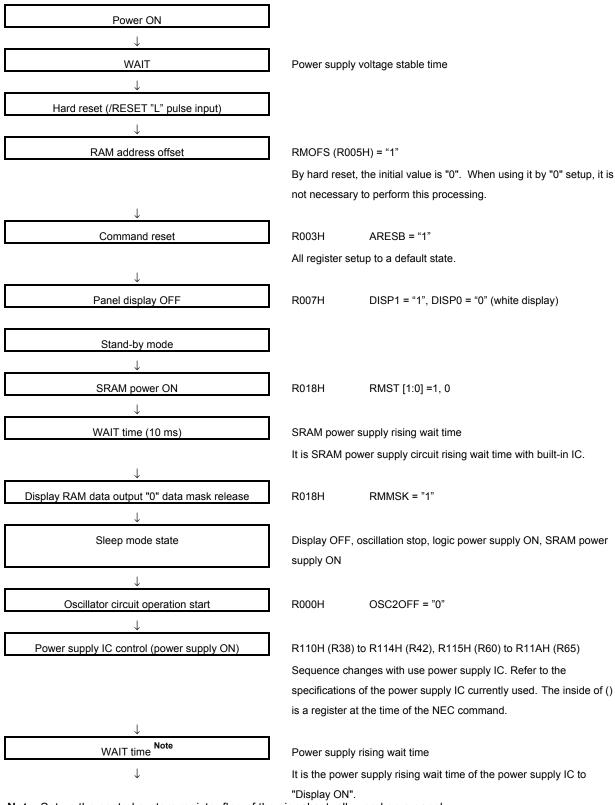

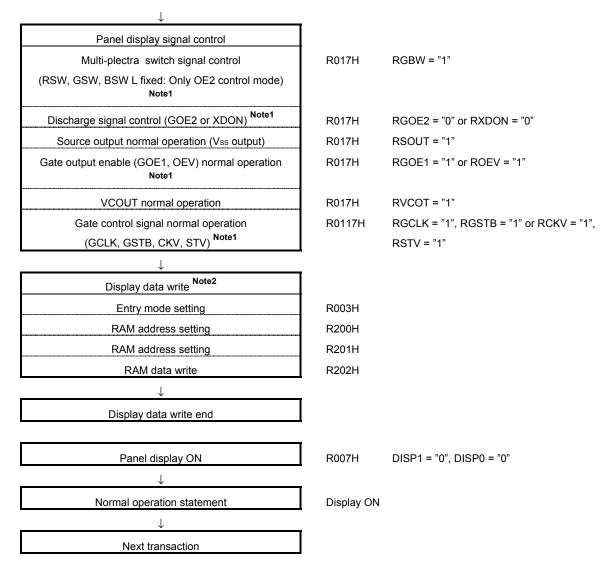

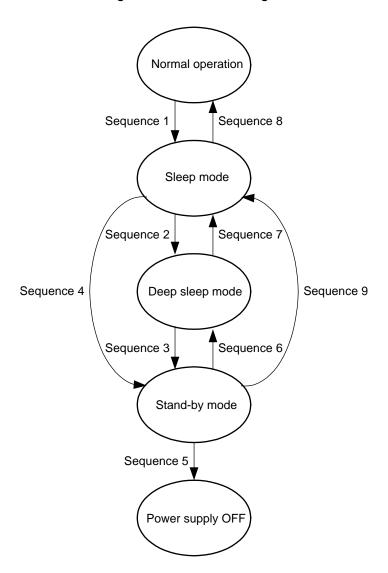

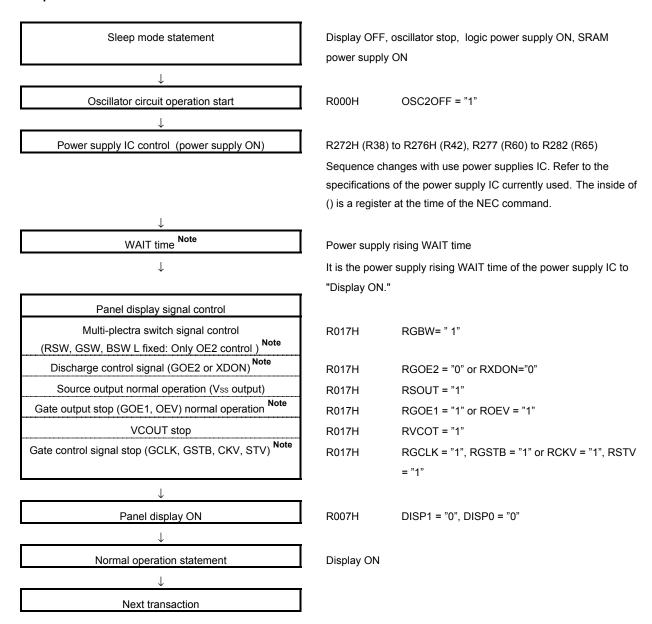

| 5            | .8     | Power       | Supply Sequence                                               | . 100 |

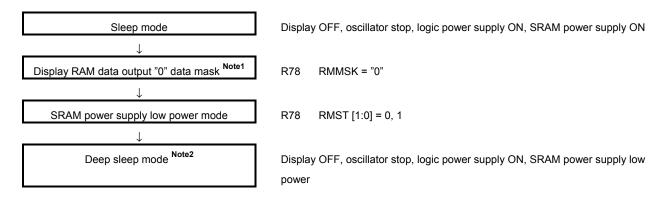

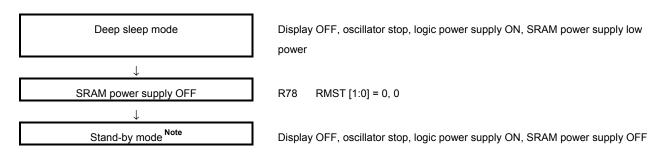

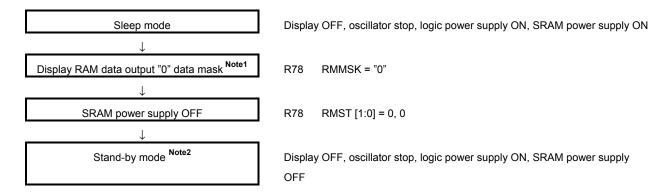

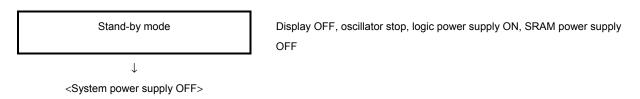

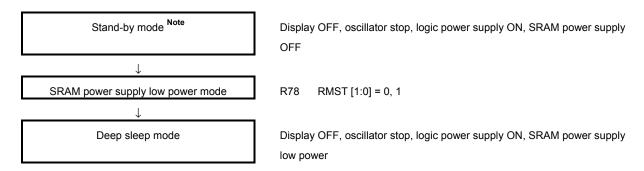

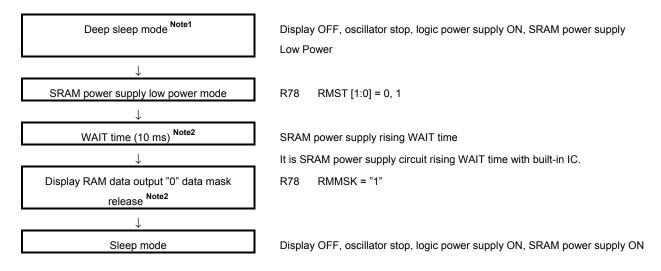

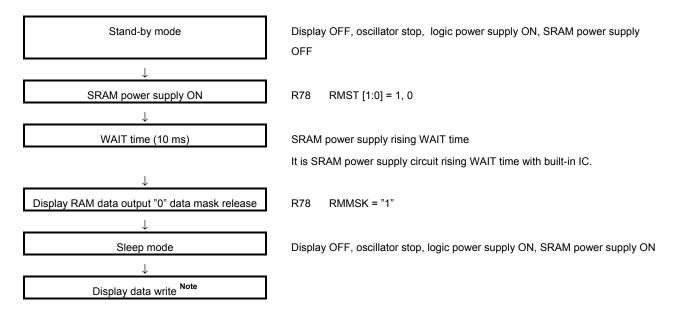

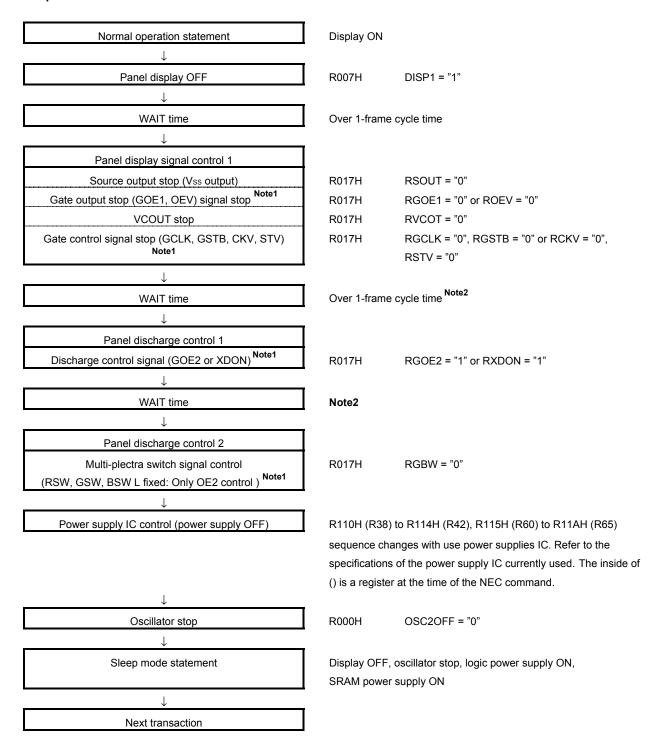

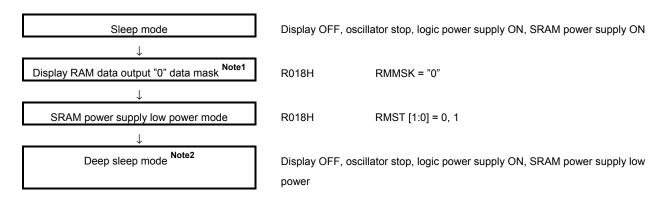

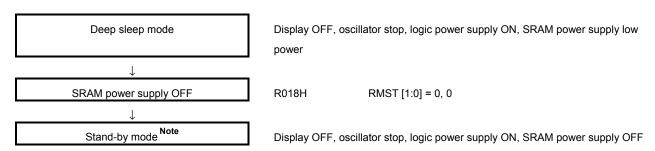

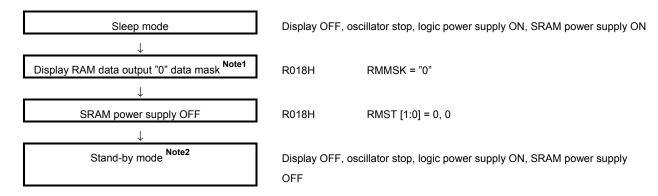

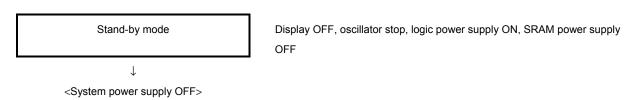

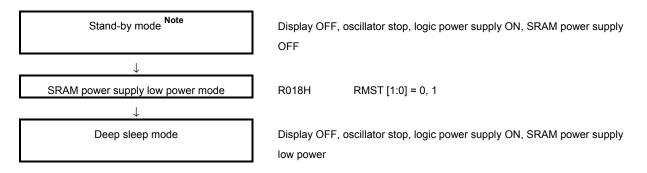

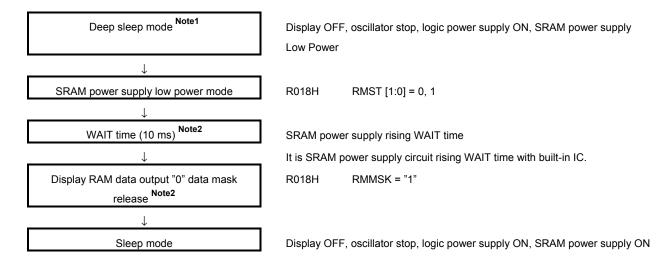

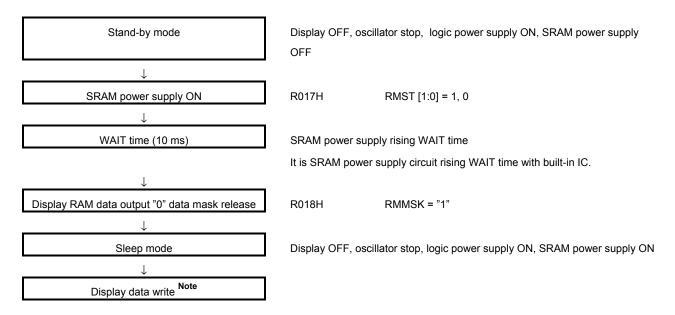

| 5            | .9     | Stand-      | by Power Supply OFF Sequence                                  | . 102 |

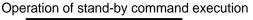

|              |        | 5.9.1       | Stand-by controlled by STBY flag                              | . 102 |

|              |        | 5.9.2       | Stand-by by command input control                             | . 105 |

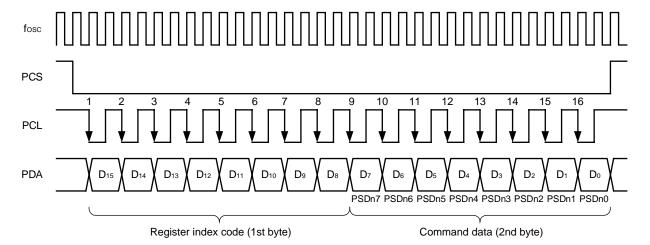

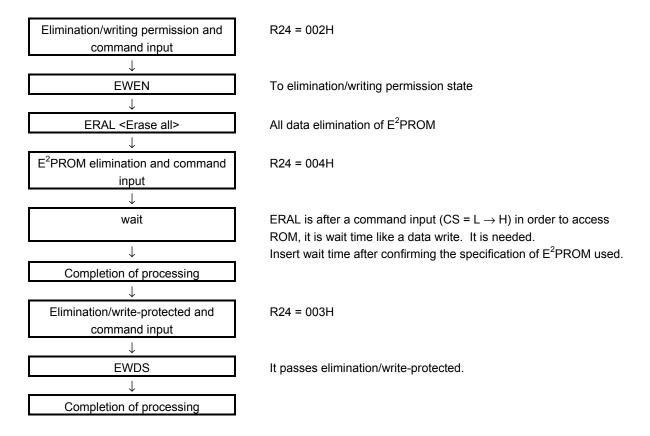

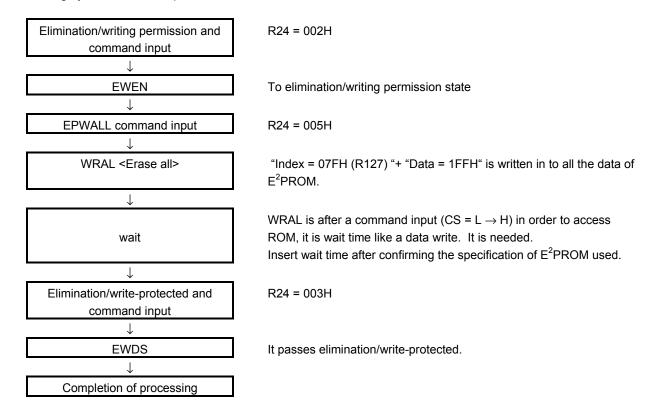

| <b>6</b> .   | $E^2P$ | ROM         | INTERFACE                                                     | .113  |

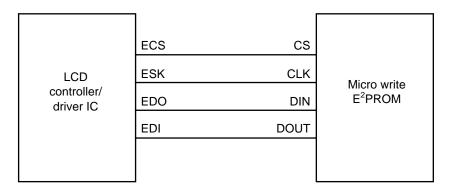

| 6            | i.1 ·  | The $\mu$ F | PD161802 and E <sup>2</sup> PROM Connection                   | . 113 |

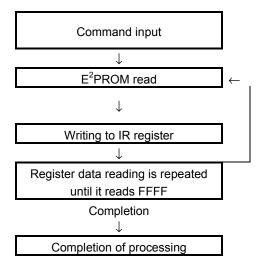

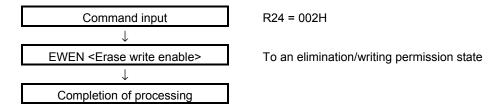

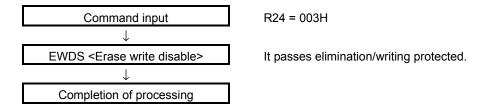

| 6            | i.2    | Each (      | Operation                                                     | . 114 |

| <b>7</b> . I | RES    | SET         |                                                               | .119  |

| 8. (         | COI    | MMA         | ND                                                            | .122  |

| 8            | 3.1    | Comm        | and List                                                      | . 122 |

| 8            | 3.2    | Comm        | and Explanation                                               | . 128 |

| <b>9</b> . I | ELE    | ECTRI       | CAL SPECIFICATIONS                                            | .144  |

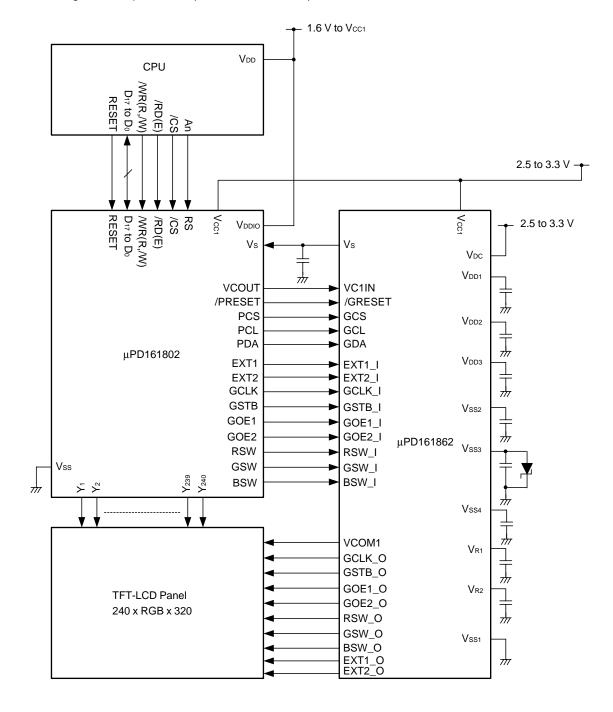

| 10.          | TH     | IE μP       | D161802 AND THE μPD161862 CONNECTION                          | .155  |

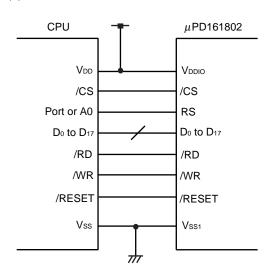

| 11.          | EX     | AMP         | LE OF THE μPD161802 AND CPU CONNECTION                        | .156  |

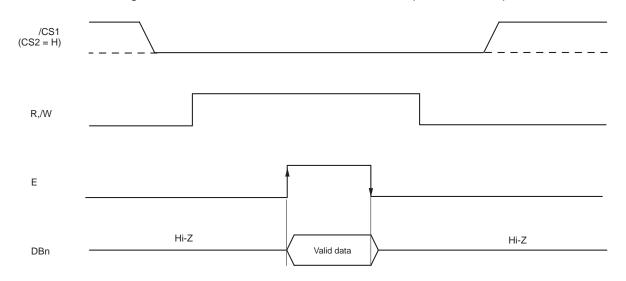

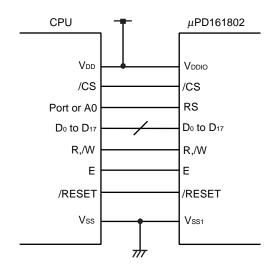

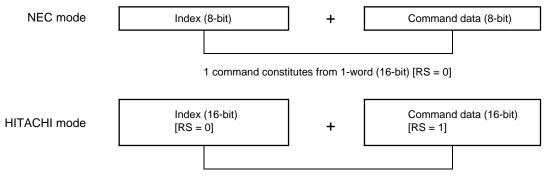

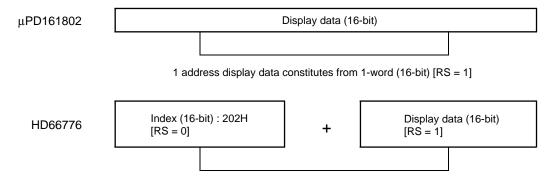

# HITACHI MODE

| 5. | DE  | SCRIF  | PTION OF FUNCTIONS                | 157 |

|----|-----|--------|-----------------------------------|-----|

|    | 5.1 | CPU II | nterface                          | 157 |

|    |     |        | Selection of interface type       |     |

|    |     | 5.1.2  | Selection of data transfer mode   | 159 |

|    |     | 5.1.3  | RGB interface                     | 166 |

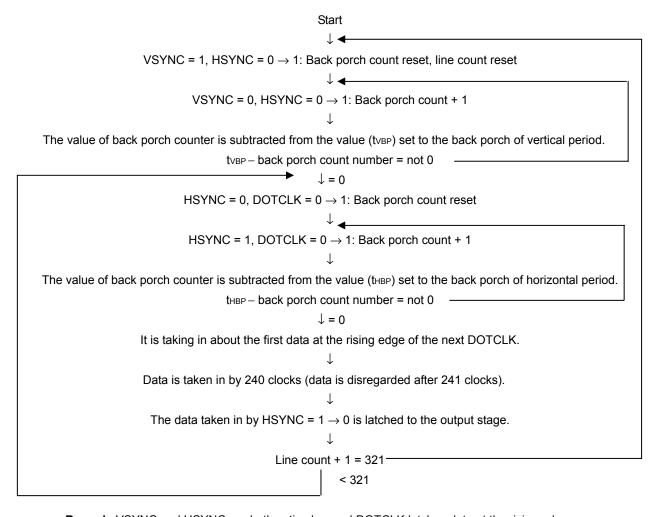

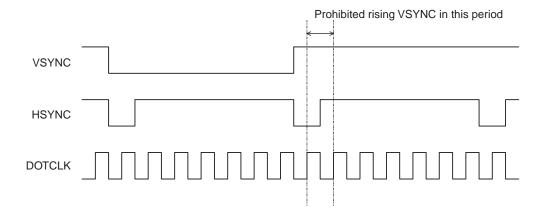

|    |     |        | VSYNC interface                   |     |

|    | 5.8 | Power  | Supply Sequence                   | 170 |

|    | 5.9 | Stand  | by Power Supply OFF Sequence      | 172 |

|    |     | 5.9.1  | Stand-by by command input control | 172 |

| 7. | RE  | SET    |                                   | 180 |

|    |     |        | ND                                |     |

|    | 8.1 | Comm   | and List                          | 183 |

|    | 8.2 | Comm   | and Explanation                   | 188 |

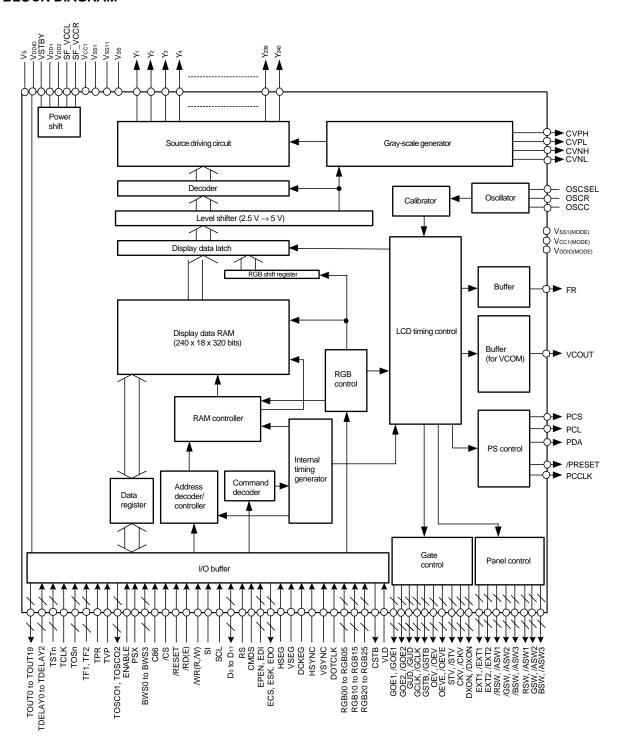

## 1. BLOCK DIAGRAM

Remark /xxx indicates active low signal.

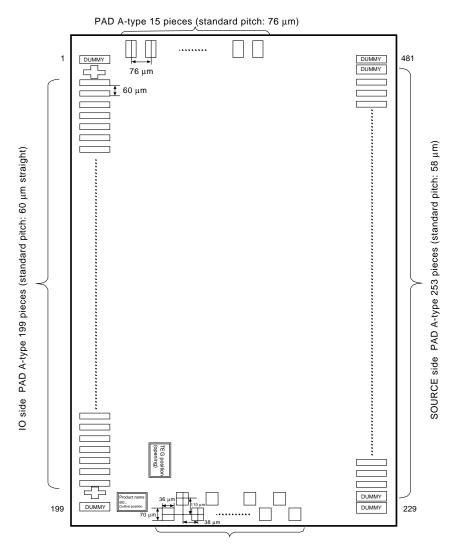

# 2. PIN CONFIGURATION (Pad Layout)

Chip size: 2.60 x 15.06 mm<sup>2</sup> (Target value)

Bump size:

PAD A-type: 30 x 100  $\mu$ m<sup>2</sup> PAD B-type: 36 x 70  $\mu$ m<sup>2</sup>

PAD B-type 29 pieces (standard pitch: 38  $\mu m$  hounds-tooth check)

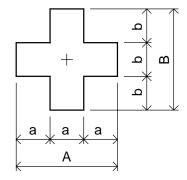

# <Alignment Mark>

Alignment shape of mark (unit:  $\mu$ m)

| Α  | а  | В  | b  |

|----|----|----|----|

| 90 | 30 | 90 | 30 |

Table 2-1. Pad Coordinate (1/5)

| No.      | Pin Name               | I/O      | Power          | Pad coordina         | te [μm]            |

|----------|------------------------|----------|----------------|----------------------|--------------------|

|          |                        | 1/0      | 1 OWC1         | X                    | Υ                  |

| 1        | DUMMY                  | _        | -              | -1152.00             | 7310.00            |

| 2        | /PRESET                | OUT      | VCC1           | -1152.00             | 7110.00            |

| 3        | ASW3,BSW               | OUT      | VCC1           | -1152.00             | 7050.00            |

| 4        | /ASW3,/BSW             | OUT      | VCC1           | -1152.00             | 6990.00            |

| 5        | ASW2,GSW               | OUT      | VCC1           | -1152.00             | 6930.00            |

| 6        | /ASW2,/GSW             | OUT      | VCC1           | -1152.00             | 6870.00            |

| 7        | ASW1,RSW               | OUT      | VCC1           | -1152.00             | 6810.00            |