### DATA SHEET

# MOS INTEGRATED CIRCUIT $\mu$ PD16652

### 200/192-OUTPUT TFT-LCD GATE DRIVER

The  $\mu$ PD16652 is a TFT-LCD gate driver. Because this gate driver has a level shift circuit for logic input, it can output a high gate scanning voltage in response to a CMOS-level input.

Moreover, it can also drive both the VGA/XGA/SXGA panel (192 output mode) and SVGA panel (200 output mode) by changing the number of outputs over between 200 and 192.

#### FEATURES

- High breakdown voltage output (ON/OFF range: VDD-VEE = 31 V MAX.)

- 3.3 V CMOS level input

- Number of output select function (200/192 outputs)

#### **ORDERING INFORMATION**

| Parts Number  | Package           |

|---------------|-------------------|

| μPD16652N-××× | TCP (TAB package) |

Because the TCP is a custom model, consult NEC for details.

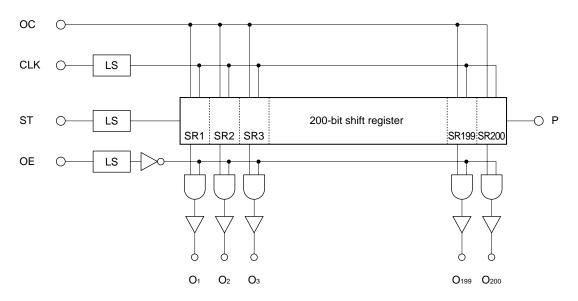

### 1. BLOCK DIAGRAM

LS (level shift): Interfaces between 3.3-V CMOS level and  $\mathsf{V}_{\mathsf{DD}}\text{-}\mathsf{V}_{\mathsf{EE}}$  level.

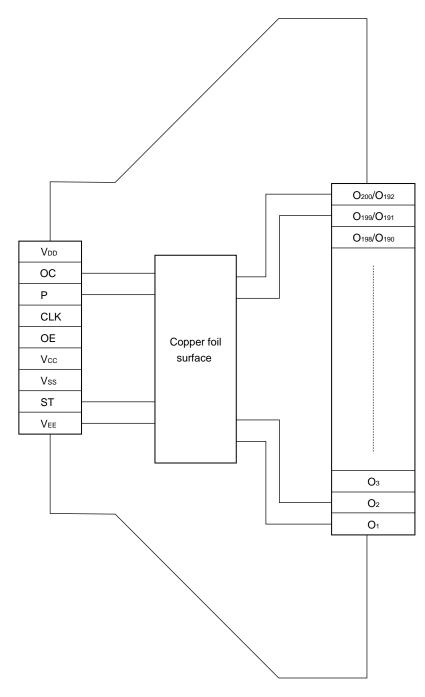

2. PIN CONFIGURATION (µPD16652n-xxx)

Caution This figure does not specify the TCP package. It is recommended to connect OC to VDD or VEE on the TCP.

### 3. PIN DESCRIPTION

| Symbol     | Pin Name                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| O1 to O200 | Driver output pins                | Scan signal output pins that drive the gate electrode of a TFT-LCD. The output level of each output pin changes in synchronization with the rising edge of shift clock CLK. The output voltage of the driver is $V_{DD}$ to $V_{EE}$ and the shift direction is only from O <sub>1</sub> to O <sub>200</sub> .                                                                                                                                                      |

| ST         | Start pulse input pin             | Input pin of the internal shift register. The input data is read at the rising edge of shift clock CLK, and a scan signal is output from the driver pin. The input level is 3.3 V CMOS level.                                                                                                                                                                                                                                                                       |

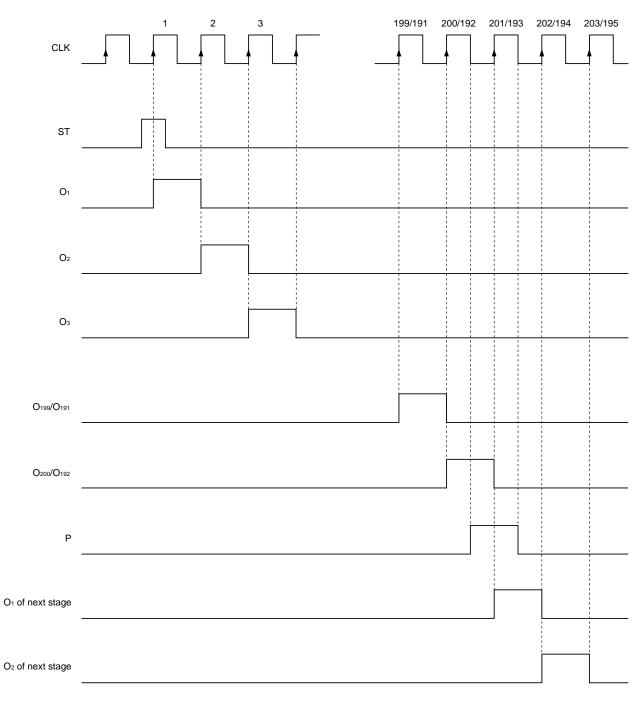

| Ρ          | Cascade output pin                | This pin works as output terminal of the start pulse to the next stage when two or more $\mu$ PD16652's are connected in cascade.<br>The output pulse is output at the falling edge of the 199th clock CLK when OC = L, and cleared at the falling edge of the 200th clock. When OC = H, the pulse is output at the falling edge if the 191st clock and cleared at the falling edge of the 192nd clock. The output level is V <sub>DD</sub> -V <sub>EE</sub> level. |

| CLK        | Shift clock input                 | Shift clock input to the internal shift register. The internal shift register shifts its contents at the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                        |

| OE         | Enable input                      | This pin fixes the driver output to the L level when it is high. However, the shift register is not cleared. Because the OE operation is not synchronous with the clock, the internal logic operates even when $OE = H$ .                                                                                                                                                                                                                                           |

| oc         | Input to select number of outputs | Selects the number of outputs.<br>OC = L: 200 outputs (SVGA)<br>OC = H: 192 outputs (VGA, XGA, SXGA)<br>When OC = H (192 outputs), O <sub>97</sub> through O <sub>104</sub> outputs of the register are<br>fixed to the V <sub>EE</sub> level. Fix this terminal to V <sub>DD</sub> or V <sub>EE</sub> on TCP.                                                                                                                                                      |

| Vdd        | Positive power supply for driver  | Shared with internal logic and driver.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Vcc        | Reference power supply            | 3.3 V $\pm$ 0.3 V. Reference power supply for level shifter: LS                                                                                                                                                                                                                                                                                                                                                                                                     |

| Vss        | Ground                            | Connect this pin to the system ground.                                                                                                                                                                                                                                                                                                                                                                                                                              |

### 4. NOTES ON CORRECT USE

### (1) Power ON/OFF sequence

To prevent the  $\mu$ PD16652 from damage due to latchup, turn on power in the order V<sub>CC</sub>  $\rightarrow$  V<sub>EE</sub> and V<sub>DD</sub>  $\rightarrow$  logic input. Turn off power in the reverse order. Observe these power sequences even during transition period.

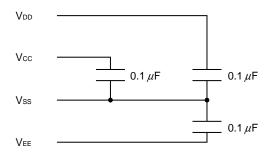

#### (2) Inserting bypass capacitor

Because the internal logic operates at a high voltage (V<sub>DD</sub>-V<sub>EE</sub>), insert a bypass capacitor of about 0.1  $\mu$ F between the respective power pins as shown below to secure the noise margin of V<sub>IH</sub> and V<sub>IL</sub>.

#### (3) Processing of OC pin

Do not input a switching signal to the OC pin that selects the number of outputs. Connect this pin to VDD or VEE.

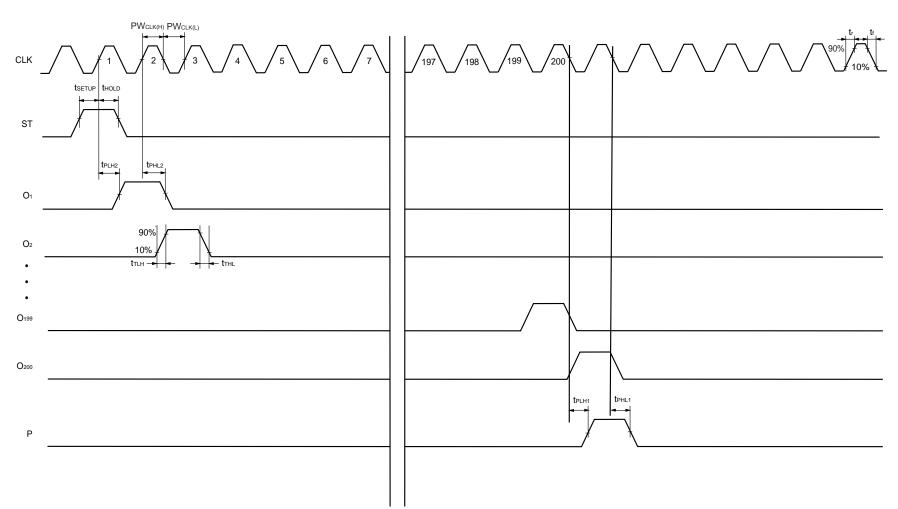

### 5. TIMING CHART (200/192 OUTPUTS)

$O_{97}$  through  $O_{104}$  are fixed to L (VEE) level for 192-output.

### 6. ELECTRIC SPECIFICATION

### Absolute Maximum Ratings (T<sub>A</sub> = 25°C, Vss = 0 V)

| Parameter                     | Symbol  | Ratings                | Unit |

|-------------------------------|---------|------------------------|------|

| Supply voltage                | Vdd     | -0.5 to +28            | V    |

| Supply voltage                | Vcc     | -0.5 to +7.0           | V    |

| Supply voltage                | Vdd-Vee | -0.5 to +33            | V    |

| Supply voltage                | Vee     | -23 to +0.5            | V    |

| Input voltage                 | Vı      | VEE - 0.5 to VDD + 0.5 | V    |

| Input current                 | h       | ±10                    | mA   |

| Output current                | lo      | ±10                    | mA   |

| Operating ambient temperature | TA      | -20 to +85             | °C   |

| Storage temperature           | Tstg.   | -55 to +125            | °C   |

#### Recommended Operating Range ( $T_A = -20$ to $70^{\circ}C$ , $V_{SS} = 0$ V)

| Parameter      | Symbol  | MIN. | TYP. | MAX. | Unit |

|----------------|---------|------|------|------|------|

| Supply voltage | Vdd     | 10   |      | 25   | V    |

| Supply voltage | Vee     | -21  |      | -5   | V    |

| Supply voltage | Vdd-Vee | 15   |      | 31   | V    |

| Supply voltage | Vcc     | 3.0  | 3.3  | 3.6  | V    |

Electrical Specifications (T<sub>A</sub> = -20 to +70°C, V<sub>DD</sub> = 22 V, V<sub>EE</sub> = -9 V, V<sub>CC</sub> = 3.3 V  $\pm$  0.3 V, V<sub>SS</sub> = 0 V)

| Parameter                   | Symbol | Condition                                                 | MIN.                | TYP. | MAX.                                | Unit |

|-----------------------------|--------|-----------------------------------------------------------|---------------------|------|-------------------------------------|------|

| Input voltage, high         | Vін    | CLK, ST                                                   | 0.7 Vcc             |      | Vcc                                 | V    |

| Input voltage, low          | VIL    | CLK, ST                                                   | Vee                 |      | 0.3 Vcc                             | V    |

| Output voltage, high        | Vон    | Р, Іон = –40 µА                                           | $V_{DD}-0.4^{Note}$ |      | VDD <sup>Note</sup>                 | V    |

| Output voltage, low         | Vol    | Р, Іон = 40 μА                                            | VEE <sup>Note</sup> |      | $V_{\text{EE}} + 0.4^{\text{Note}}$ | V    |

| Output current, high        | InOH   | $O_n$ , $V_n = V_{DD} - 1.0 V$                            |                     |      | -1.0                                | mA   |

| Output current, low         | InOL   | $O_n, V_n = V_{EE} + 1.0 V$                               | 1.0                 |      |                                     | mA   |

| Output ON resistance        | Ron    | $V_n = V_{EE} + 1.0 \text{ V or } V_{DD} - 1.0 \text{ V}$ |                     |      | 1.0                                 | kΩ   |

| Input leakage current       | ١L     | VI = 0 V or 3.3 V                                         |                     |      | ±1.0                                | μA   |

| Dynamic current consumption | ldd    | Vdd, fclk = 60 kHz                                        |                     | 500  | 1000                                | μA   |

|                             | IEE    | VEE, fclk = 60 kHz                                        | -1000               | -500 |                                     | μA   |

|                             | lcc    | Vcc, fclк = 60 kHz                                        |                     | 13   | 50                                  | μA   |

**Note** The cascade output is at the driver level (VDD-VEE).

### Switching Characteristics (T<sub>A</sub> = -20 to +70°C, V<sub>DD</sub> = 22 V, V<sub>EE</sub> = -9 V, V<sub>CC</sub> = 3.3 V $\pm$ 0.3 V, V<sub>SS</sub> = 0 V)

| Parameter                | Symbol            | Condition                 | MIN. | TYP. | MAX. | Unit |

|--------------------------|-------------------|---------------------------|------|------|------|------|

| STVL output delay time   | tPHL1             | CL = 20 pF                |      |      | 600  | ns   |

|                          | tPLH1             | $CLK \to P$               |      |      | 600  | ns   |

| Driver output delay time | tPHL2             | C∟ = 220 pF               |      |      | 700  | ns   |

|                          | tPLH2             | $CLK \to O_n$             |      |      | 700  | ns   |

| Output rise time         | tт∟н              | C∟ = 220 pF               |      |      | 400  | ns   |

| Output fall time         | t⊤н∟              | CL = 220 pF               |      |      | 400  | ns   |

| Input capacitance        | С                 | T <sub>A</sub> = 25°C     |      |      | 15   | pF   |

| Maximum clock frequency  | f <sub>max.</sub> | When connected in cascade | 300  |      |      | kHz  |

#### Timing Requirement (T<sub>A</sub> = -20 to +70°C, V<sub>DD</sub> = 22 V, V<sub>EE</sub> = -9 V, V<sub>CC</sub> = 3.3 V $\pm$ 0.3 V, V<sub>SS</sub> = 0 V)

| Parameter               | Symbol    | Condition                        | MIN. | TYP. | MAX. | Unit |

|-------------------------|-----------|----------------------------------|------|------|------|------|

| Clock pulse high period | PWclk (H) |                                  | 500  |      |      | ns   |

| Clock pulse low period  | PWclk (L) |                                  | 500  |      |      | ns   |

| Data setup time         | tsetup    | $ST \uparrow \to CLK \uparrow$   | 200  |      |      | ns   |

| Data hold time          | thold     | $CLK \uparrow \to ST \downarrow$ | 200  |      |      | ns   |

The rise and fall times of logic input must be  $t_r = t_f = 20$  ns (10% to 90%).

<u>μ</u>PD16652

7. SWITCHING CHARACTERISTICS WAVE

NEC

**Phase-out/Discontinued**

### 8. RECOMMENDED MOUNTING CONDITIONS

When mounting this product, please make sure that the following recommended conditions are satisfied.

For packaging methods and conditions other than those recommended below, please contact NEC sales personnel.

| Mounting Condition | Mounting Method                      | Condition                                                                                                                                                                                                                                                              |

|--------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Thermocompression  | Soldering                            | Heating tool 300 to 350°C, heating for 2 to 3 sec; pressure 100 g (per solder)                                                                                                                                                                                         |

|                    | ACF<br>(Adhesive<br>Conductive Film) | Temporary bonding 70 to 100°C; pressure 3 to 8 kg/cm <sup>2</sup> ; time 3 to 5 sec.<br>Real bonding 165 to 180°C; pressure 25 to 45 kg/cm <sup>2</sup> , time 30 to 40 secs.<br>(When using the anisotropy conductive film SUMIZAC1003 of Sumitomo<br>Bakelite, Ltd.) |

Caution To find out the detailed conditions for packaging the ACF part, please contact the ACF manufacturing company. Be sure to avoid using two or more packaging methods at a time.

#### Reference

NEC Semiconductor Device Reliability/Quality Control System (C10983E) Quality Grades to NEC's Semiconductor Devices (C11531E)

[MEMO]

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.