## uS5651P ADC Prefilter with Analog Multiplexer

### **General Description**

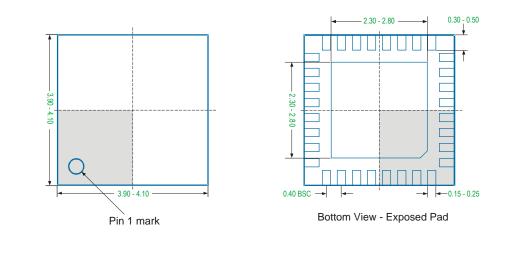

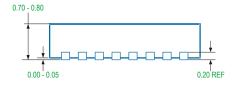

The uS5651P is an ADC prefilter with analog multiplexer, which output is used mainly by the analog to digital converter (ADC) of GPU/ASIC for voltage and current monitoring. This device has four input channels, and each channel has an independent voltage and current monitoring input. This part senses the voltage across the shunt resistor for current monitoring. The voltage and current information of each channel is processed and scaled then sent to a differential output via a multiplexer. The multiplexer selects which channel to be the signal source in a switching manner. The operating mode, switching sequence, scaling factor and other parameters are set by the I<sup>2</sup>C register. The device operates with 3.3V VCC supply voltage, and it is available in a WQFN4x4-32L package.

### **Features**

- 4 Channel Bus Voltage Monitoring Inputs, Up to 30V

- 4 Channel Shunt Current Monitoring Inputs with 5V to 30V Operating Voltage

- □ 2.8V to 3.8V VCC Supply Voltage

- Differential Output via Analog Multiplexer with Single Bit MUX Select

- □ Selectable I<sup>2</sup>C Device Address by Resistor Strap

- Adjustable Scaling Factors and Operating Parameters by I<sup>2</sup>C Registers

- Active Channel

- Alternating Mode

- Offset Voltage

- Common Mode Voltage

- Voltage Gain (Bus Gain)

- Current Gain (Shunt Gain)

- Open-Drain Bus OK Indicator

- Device Enable Control

- Two IMON Analog Inputs

- Reference GND Input

- □ Stand-Alone and Dual Device Operation Mode

- Low Profile WQFN4x4-32L Package

- RoHS Compliant and Halogen Free

### **Ordering Information**

| Order Number | Package Type | Top Marking |

|--------------|--------------|-------------|

| uS5651PQKI   | WQFN4x4-32L  | uS5651P     |

Note:

(1) Please check the sample/production availability with uPl representatives.

(2) uPI products are compatible with the current IPC/JEDEC J-STD-020 requirement. They are halogen-free, RoHS compliant and 100% matte tin (Sn) plating that are suitable for use in SnPb or Pb-free soldering processes.

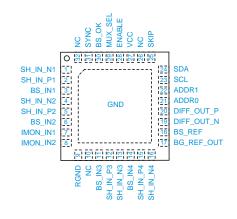

### **Pin Configuration**

### **Applications**

- Computers

- Power Management

- Battery Chargers

- Power Supplies

- Test Equipments

#### uS5651P-DS-F0000, Sep. 2023

1

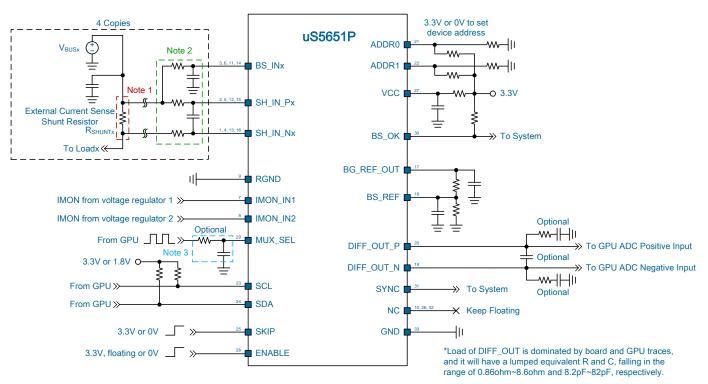

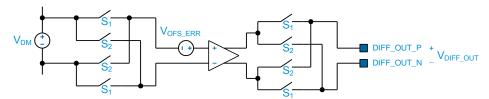

### **Typical Application Circuit**

#### 4-Channel Stand-Alone Mode

Note 1: Use Kelvin connection for external current sense shunt resistor.

Note 2: Local RC filter at BS\_Inx input, and local RCR filter at SH\_IN\_Px and SH\_IN\_Nx input are required for noise filtering.

Note 3: Recommend to reserve RC circuit at MUX\_SEL and DIFF\_OUT pins for noise filtering when necessary.

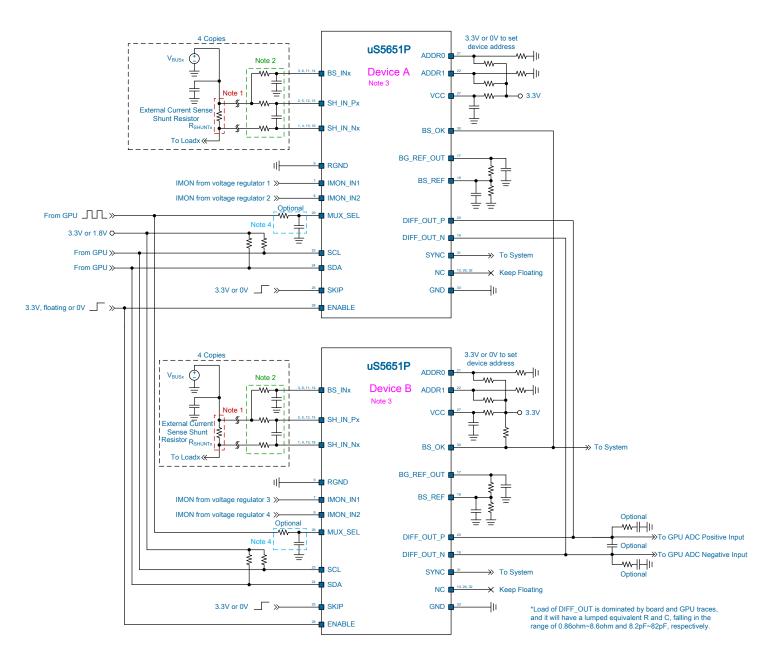

### **Typical Application Circuit**

#### 8-Channel Dual Device Mode

Note 1: Use Kelvin connection for external current sense shunt resistor.

Note 2: Local RC filter at BS\_INx input, and local RCR filter at SH\_IN\_Px and SH\_IN\_Nx input are required for noise filtering.

Note 3: Register 0x05h of each device need to be programmed to activate dual device mode operation.

Note 4: Recommend to reserve RC circuit at MUX\_SEL and DIFF\_OUT pins for noise filtering when necessary.

### **Functional Pin Description**

| Pin No.    | Pin Name | I/O | Pin Function                                                                                                                                                                                                                          |

|------------|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | SH_IN_N1 | AI  | <b>Negative Node of Current Monitoring Input for Channel 1.</b> Connect to the external current sense shunt resistor with Kelvin connection for current sense. If not used, see related section for pin connection of unused channel. |

| 2          | SH_IN_P1 | AI  | <b>Positive Node of Current Monitoring Input for Channel 1.</b> Connect to the external current sense shunt resistor with Kelvin connection for current sense. If not used, see related section for pin connection of unused channel. |

| 3          | BS_IN1   | AI  | <b>Bus Voltage Sense Input for Channel 1.</b> Connect to the same point as SH_IN_P1. If not used, see related section for pin connection of unused channel.                                                                           |

| 4          | SH_IN_N2 | AI  | <b>Negative Node of Current Monitoring Input for Channel 2.</b> Connect to the external current sense shunt resistor with Kelvin connection for current sense. If not used, see related section for pin connection of unused channel. |

| 5          | SH_IN_P2 | AI  | <b>Positive Node of Current Monitoring Input for Channel 2.</b> Connect to the external current sense shunt resistor with Kelvin connection for current sense. If not used, see related section for pin connection of unused channel. |

| 6          | BS_IN2   | AI  | <b>Bus Voltage Sense Input for Channel 2.</b> Connect to the same point as SH_IN_P2. If not used, see related section for pin connection of unused channel.                                                                           |

| 7          | IMON_IN1 | AI  | <b>Voltage Regulator IMON Input 1.</b> Connect to the total output current signal of voltage regulator 1.                                                                                                                             |

| 8          | IMON_IN2 | AI  | <b>Voltage Regulator IMON Input 2.</b> Connect to the total output current signal of voltage regulator 2.                                                                                                                             |

| 9          | RGND     | AI  | <b>Ground Reference Channel Input.</b> Connect to the ground near this device. The device will use this as an input and mux it through signal channel.                                                                                |

| 10, 26, 32 | NC       |     | Do not connect to any circuit. These pins must be left floating.                                                                                                                                                                      |

| 11         | BS_IN3   | AI  | <b>Bus Voltage Sense Input for Channel 3.</b> Connect to the same point as SH_IN_P3. If not used, see related section for pin connection of unused channel.                                                                           |

| 12         | SH_IN_P3 | AI  | <b>Positive Node of Current Monitoring Input for Channel 3.</b> Connect to the external current sense shunt resistor with Kelvin connection for current sense. If not used, see related section for pin connection of unused channel. |

### **Functional Pin Description**

| Pin No. | Pin Name   | I/O   | Pin Function                                                                                                                                                                                                                                   |

|---------|------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13      | SH_IN_N3   | AI    | <b>Negative Node of Current Monitoring Input for Channel 3.</b> Connect to the external current sense shunt resistor with Kelvin connection for current sense. If not used, see related section for pin connection of unused channel.          |

| 14      | BS_IN4     | AI    | <b>Bus Voltage Sense Input for Channel 4.</b> Connect to the same point as SH_IN_P4. If not used, see related section for pin connection of unused channel.                                                                                    |

| 15      | SH_IN_P4   | AI    | <b>Positive Node of Current Monitoring Input for Channel 4.</b> Connect to the external current sense shunt resistor with Kelvin connection for current sense. If not used, see related section for pin connection of unused channel.          |

| 16      | SH_IN_N4   | AI    | <b>Negative Node of Current Monitoring Input for Channel 4.</b> Connect to the external current sense shunt resistor with Kelvin connection for current sense. If not used, see related section for pin connection of unused channel.          |

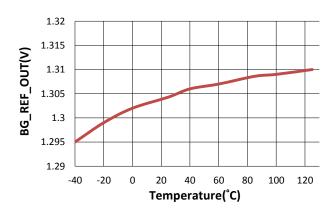

| 17      | BG_REF_OUT | AO    | <b>Bandgap Reference Voltage Output.</b> Connect a MLCC to this pin for noise decoupling. BG_REF_OUT is the voltage source for resistor voltage divider for BS_REF input. It is recommended to use MLCC of 100nF minimum for noise decoupling. |

| 18      | BS_REF     | AI    | <b>Reference Input for the BS_OK Comparator.</b> Connect a resistor voltage divider from BG_REF_OUT to this pin to set the reference voltage for bus-ready comparator (for BS_OK). Recommend to add a MLCC to this pin for noise decoupling.   |

| 19      | DIFF_OUT_N | AO    | <b>Negative Output Node of Differential Amplifier.</b> Connect this pin to the GPU ADC negative input pin. It is recommended to reserve RC circuit for noise decoupling when necessary.                                                        |

| 20      | DIFF_OUT_P | AO    | <b>Positive Output Node of Differential Amplifier.</b> Connect this pin to the GPU ADC positive input pin. It is recommended to reserve RC circuit for noise decoupling when necessary.                                                        |

| 21      | ADDR0      | DI    | <b>Device Address Setting 0.</b> Logic state of this pin determines the $I^2C$ address of this device. See $I^2C$ Device Bus Address Setting table for detail.                                                                                 |

| 22      | ADDR1      | DI    | <b>Device Address Setting 1.</b> Logic state of this pin determines the $I^2C$ address of this device. See $I^2C$ Device Bus Address Setting table for detail.                                                                                 |

| 23      | SCL        | DI    | <b>I<sup>2</sup>C Clock Input.</b> This pin receives serial bus clock signal input (3.3V or 1.8V logic).                                                                                                                                       |

| 24      | SDA        | DI/DO | <b>I<sup>2</sup>C Data Input.</b> This pin is input or output of serial bus data signal (3.3V or 1.8V logic).                                                                                                                                  |

### **Functional Pin Description**

| Pin No. | Pin Name   | I/O | Pin Function                                                                  |  |  |  |

|---------|------------|-----|-------------------------------------------------------------------------------|--|--|--|

| 25      | 25 SKIP DI |     | Mask for BS_OK. See table of logic state of ENABLE, SKIP, BS_INx and          |  |  |  |

| 25      | ORI        |     | BS_OK for detail.                                                             |  |  |  |

| 27      | VCC        | AI  | Supply Input for the Device. Connect this pin to a 3.3V voltage source        |  |  |  |

| 21      | VCC        | AI  | with a MLCC of 1uF minimum.                                                   |  |  |  |

|         |            |     | Enable Control (Active Low). Logic state of this pin enable/disable the       |  |  |  |

| 28      | ENABLE     | DI  | device. Note that this pin is active low, which means logic state low to this |  |  |  |

|         |            |     | pin enables this device to full function state.                               |  |  |  |

|         |            |     | Multiplexer Selection Input. The multiplexer selects which channel to be      |  |  |  |

| 29      |            |     | the signal source per MUX_SEL clock input. It is recommended to reserve       |  |  |  |

| 29      | MUX_SEL    | DI  | RC circuit for noise filtering. It is recommended to reserve RC filter at     |  |  |  |

|         |            |     | MUX_SEL input for noise filtering.                                            |  |  |  |

| 30      | BS_OK      | DO  | Bus OK Indication. This pin is an open-drain output. Connect this pin to a    |  |  |  |

| 30      | BS_OK      | DO  | voltage source with a pull-up resistor.                                       |  |  |  |

| 31      | SYNC       | DO  | Synchronous Output. This pin outputs a pulse for the first MUX_SEL            |  |  |  |

| 31      | 31 3116 00 |     | period in every MUX_SEL sequence.                                             |  |  |  |

| Evo     | osed Pad   |     | Ground. The exposed pad is the ground of the device, and it must be           |  |  |  |

| Expo    | JOCU FOU   |     | soldered to a large PCB and connected to GND.                                 |  |  |  |

Note: AI=Analog Input; AO=Analog Output; DI=Digital Input; DO=Digital Output

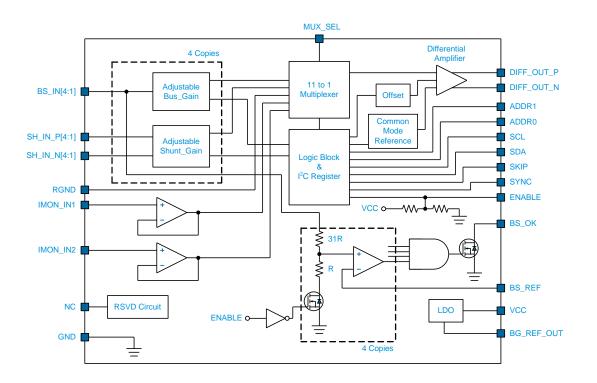

### **Functional Block Diagram**

### **Functional Description**

#### Device Enable Control

Input logic state of ENABLE pin controls the disable/enable of this device. Note that the ENABLE function is **active low**, which is different from the pin name convention. There are three logic levels for ENABLE function as shown in the table below.

| Input Logic State of ENABLE | Description                                                      |  |

|-----------------------------|------------------------------------------------------------------|--|

| Low                         | Enabled and fully functional.                                    |  |

|                             | Enabled but with limited function. Only BG_REF_OUT and           |  |

|                             | BS_OK comparators are functional. All other functions are        |  |

| Tri-state                   | disabled to reduce power consumption. The differential           |  |

|                             | amplifier output (DIFF_OUT_P/N) is in high impedance state,      |  |

|                             | and MUX_SEL logic input is ignored.                              |  |

| Llich                       | <b>Disabled.</b> The device is disabled and in standby mode. All |  |

| High                        | functions are turned off to minimize power consumption.          |  |

#### Table 1. Logic Input State of ENABLE and Operation Mode

### I<sup>2</sup>C Device Address Setting

The uS5651P has I<sup>2</sup>C interface for function setting. Logic state of ADDR0 and ADDR1 determines the I<sup>2</sup>C address of this device. It is recommended to use VCC or ground for address setting logic input. See Table 2 for device address setting.

200

| Table 2. I <sup>2</sup> C Device Address Setting |             |                                             |  |  |  |

|--------------------------------------------------|-------------|---------------------------------------------|--|--|--|

| ADDR1 Input                                      | ADDR0 Input | I <sup>2</sup> C Device Address<br>Bit[7:1] |  |  |  |

| GND                                              | GND         | 0110100 (68h)                               |  |  |  |

| GND                                              | VCC         | 0110101 (6Ah)                               |  |  |  |

| VCC                                              | GND         | 0110110 (6Ch)                               |  |  |  |

| VCC                                              | VCC         | 0110111 (6Eh)                               |  |  |  |

####

Figure 1. I<sup>2</sup>C Bus Timing Diagram

## **Functional Description**

| Read Data:  | S    | Slave Address        | W | A                                                               | Reg. Address                                                      | A          |            |   |   |

|-------------|------|----------------------|---|-----------------------------------------------------------------|-------------------------------------------------------------------|------------|------------|---|---|

|             | S/RS | Slave Address        | R | А                                                               | 8 Data Bit                                                        | A/NA       | Р          |   |   |

|             |      | From Master to Slave |   |                                                                 | Slave address: 7 bit F<br>W: 1'b0, R:1'b1                         | •          | ess: 8 bit |   |   |

|             |      | From Slave to Master |   |                                                                 | S: Start, P: Stop, RS:<br>A: ACK (SDA low)<br>NA: Not ACK (SDA hi |            |            |   |   |

|             |      |                      |   |                                                                 |                                                                   |            |            |   |   |

| Write Data: | S    | Slave Address        | w | А                                                               | Reg. Address                                                      | А          | 8 Data Bit | A | Р |

|             |      | From Master to Slave |   |                                                                 | Slave address: 7 bit F<br>W: 1'b0, R:1'b1<br>S: Start, P: Stop    | Reg. addre | ess: 8 bit |   |   |

|             |      | From Slave to Master |   | S: Start, P: Stop<br>A: ACK (SDA low)<br>NA: Not ACK (SDA high) |                                                                   |            |            |   |   |

Figure 2. I<sup>2</sup>C Read/Write Protocol Format

| Parameter                                      | Symbol              | Min  | Мах | Unit |

|------------------------------------------------|---------------------|------|-----|------|

| SCL Clock Frequency                            | f <sub>I2C</sub>    |      | 400 | kHz  |

| Repeated Hold Time START Condition             | t <sub>HD_STA</sub> | 0.26 |     | us   |

| Data Hold Time                                 | t <sub>HD_DAT</sub> | 0    |     | us   |

| LOW Period of SCL Clock                        | t <sub>LOW</sub>    | 0.5  |     | us   |

| HIGH Period of SCL Clock                       | t <sub>HIGH</sub>   | 0.26 |     | us   |

| Setup Time for Repeated START Condition        | t <sub>SU_STA</sub> | 0.26 |     | us   |

| Data Setup Time                                | t <sub>SU_DAT</sub> | 50   |     | ns   |

| Setup Time for STOP Condition                  | t <sub>s∪_sto</sub> | 0.26 |     | us   |

| Bus Free Time between STOP and START Condition | t <sub>BUF</sub>    | 0.5  |     | us   |

| Rise Time for Both SDA and SCL Signals         | t <sub>r</sub>      |      | 120 | ns   |

| Fall Time for Both SDA and SCL Signals         | t <sub>f</sub>      |      | 120 | ns   |

| Table 3  | Timina  | Requirements | of $I^2C$ Interf | 200 |

|----------|---------|--------------|------------------|-----|

| Table 5. | rinning | Requirements |                  | ace |

### **Functional Description**

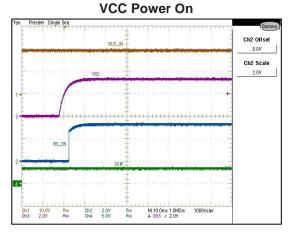

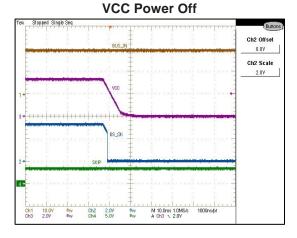

#### **Power up Sequence**

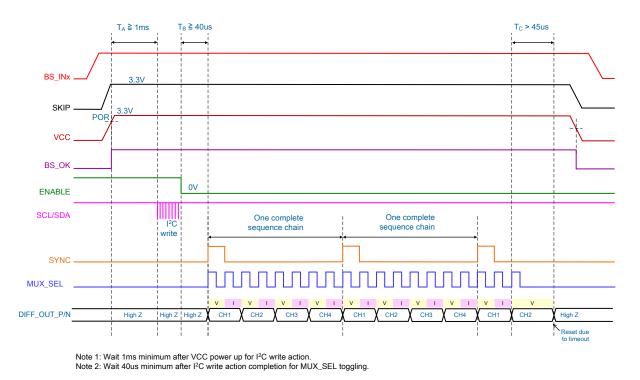

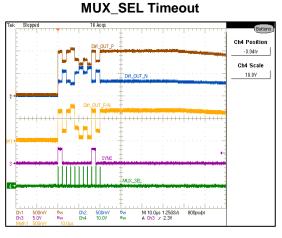

Once the device is enabled and its VCC rises above the POR threshold, it starts to operate. The timing relation between VCC, BS\_IN, BS\_OK and MUX\_SEL is shown in the Figure 3. For I<sup>2</sup>C writing timing, a delay time of 1ms (T<sub>A</sub>) minimum is required after VCC POR. It is required to wait for at least 1ms after VCC POR to write data into registers. This is to ensure all the internal circuits are ready to receive I<sup>2</sup>C command. As for MUX\_SEL timing, a delay time of 40us (T<sub>B</sub>) minimum is required after ENABLE go low (device enabled) to MUX\_SEL toggling. It is required to wait for at least 40us after ENABLE go low to toggle MUX\_SEL. This delay time is to ensure all the circuits are ready for operation mode transition. Note that the MUX\_SEL has a timeout of 45us (T<sub>C</sub>) maximum, therefore the device will go back to the initial state of output sequence if MUX\_SEL stays high or low longer than timeout.

Figure 3. Timing Relation between VCC, BS\_IN, BS\_OK and MUX\_SEL.

#### **Shunt Current Monitoring**

The input for shunt current monitoring function comes in a pin pair (SH\_IN\_P and SH\_IN\_N). An external current sense shunt resistor is required to convert current signal to voltage signal for channel current sensing. In each channel, a differential amplifier senses the voltage across the external shunt resistor, amplifying the sensed voltage with a ratio Shunt\_Gain. The amplified signal is fed to a multiplexer then sent to the single to differential amplifier and outputs (DIFF\_OUT\_P and DIFF\_OUT\_N) to GPU. The ADC of the GPU then receives the shunt current information. For shunt current monitoring, the output of differential amplifier is as follows.

$V_{DIFF\_OUT} = I \times R_{SENSE} \times Shunt\_Gain$

### **Functional Description**

I is the shunt current, R<sub>SENSE</sub> is the resistance of current sense shunt resistor, and Shunt\_Gain is the amplification ratio. The Shunt\_Gain value is adjustable in register 0x20h~0x23h. Table 4 lists the Shunt\_Gain register content.

Note that the PCB trace routing between the external current sense shunt resistor and SH\_IN\_P/N pins should be Kelvin connection. Also, the BS\_IN pin should be tied to the same point as SH\_IN\_P.

|          | Shunt_Gain Register (0x20h, 0x21h, 0x22h, 0x23h) Content, |            |          |                                    |            |  |  |  |

|----------|-----------------------------------------------------------|------------|----------|------------------------------------|------------|--|--|--|

|          | bit[7:6] and bit0 are fixed=0                             |            |          |                                    |            |  |  |  |

| Bit[5:1] | Hex<br>(include bit7, bit6 & bit0)                        | Shunt_Gain | Bit[5:1] | Hex<br>(include bit7, bit6 & bit0) | Shunt_Gain |  |  |  |

| 00000    | 00(default)                                               | 2.000      | 10000    | 20                                 | 7.212      |  |  |  |

| 00001    | 02                                                        | 2.167      | 10001    | 22                                 | 7.813      |  |  |  |

| 00010    | 04                                                        | 2.348      | 10010    | 24                                 | 8.465      |  |  |  |

| 00011    | 06                                                        | 2.544      | 10011    | 26                                 | 9.172      |  |  |  |

| 00100    | 08                                                        | 2.756      | 10100    | 28                                 | 9.937      |  |  |  |

| 00101    | 0A                                                        | 2.986      | 10101    | 2A                                 | 10.767     |  |  |  |

| 00110    | 0C                                                        | 3.235      | 10110    | 2C                                 | 11.665     |  |  |  |

| 00111    | 0E                                                        | 3.505      | 10111    | 2E                                 | 12.639     |  |  |  |

| 01000    | 10                                                        | 3.798      | 11000    | 30                                 | 13.694     |  |  |  |

| 01001    | 12                                                        | 4.115      | 11001    | 32                                 | 14.837     |  |  |  |

| 01010    | 14                                                        | 4.458      | 11010    | 34                                 | 16.075     |  |  |  |

| 01011    | 16                                                        | 4.830      | 11011    | 36                                 | 17.417     |  |  |  |

| 01100    | 18                                                        | 5.233      | 11100    | 38                                 | 18.870     |  |  |  |

| 01101    | 1A                                                        | 5.670      | 11101    | 3A                                 | 20.445     |  |  |  |

| 01110    | 1C                                                        | 6.143      | 11110    | 3C                                 | 22.151     |  |  |  |

| 01111    | 1E                                                        | 6.656      | 11111    | 3E                                 | 24.000     |  |  |  |

|          | <b>.</b> | <u> </u> |          | -       |

|----------|----------|----------|----------|---------|

| Table 4. | Shunt    | Gain     | Register | Content |

#### Bus Voltage Monitoring and BS\_OK

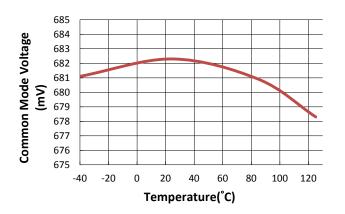

The bus voltage monitoring function has a single input pin (BS\_IN). The BS\_IN is internally connected to a resistor voltage divider with adjustable dividing ratio of 1/Bus\_Gain. The Bus\_Gain is adjustable in register 0x10h~0x13h. Table 5 lists the Bus\_Gain register content. The BS\_IN input is scaled down and fed to a multiplexer then sent to a single to differential amplifier and outputs (DIFF\_OUT\_P and DIFF\_OUT\_N) to GPU. The common mode voltage of the differential amplifier is determined by register 0x08h with 675mV as default setting. The analog to digital converter (ADC) of the GPU then receives the bus voltage information.

For bus voltage monitoring, the output of differential amplifier is  $V_{DIFF_OUT} = V_{BS_IN} / Bus_Gain$ , where Bus\_Gain is the denominator, meaning it is an attenuation factor.

### **Functional Description**

|          | Table 5. Bus_Gain (Attenuation Factor) Register Content                                                    |                                     |          |                                    |                                     |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------|-------------------------------------|----------|------------------------------------|-------------------------------------|--|--|--|

| Bus_G    | Bus_Gain (Attenuation Factor) Register (0x10h, 0x11h, 0x12h, 0x13h) Content, bit[7:6] and bit0 are fixed=0 |                                     |          |                                    |                                     |  |  |  |

| Bit[5:1] | Hex<br>(include bit7, bit6 & bit0)                                                                         | Bus_Gain<br>(Attenuation<br>Factor) | Bit[5:1] | Hex<br>(include bit7, bit6 & bit0) | Bus_Gain<br>(Attenuation<br>Factor) |  |  |  |

| 00000    | 00(default)                                                                                                | 64.000                              | 10000    | 20                                 | 15.300                              |  |  |  |

| 00001    | 02                                                                                                         | 58.524                              | 10001    | 22                                 | 13.991                              |  |  |  |

| 00010    | 04                                                                                                         | 53.517                              | 10010    | 24                                 | 12.794                              |  |  |  |

| 00011    | 06                                                                                                         | 48.939                              | 10011    | 26                                 | 11.700                              |  |  |  |

| 00100    | 08                                                                                                         | 44.752                              | 10100    | 28                                 | 10.699                              |  |  |  |

| 00101    | 0A                                                                                                         | 40.923                              | 10101    | 2A                                 | 9.783                               |  |  |  |

| 00110    | 0C                                                                                                         | 37.422                              | 10110    | 2C                                 | 8.946                               |  |  |  |

| 00111    | 0E                                                                                                         | 34.220                              | 10111    | 2E                                 | 8.181                               |  |  |  |

| 01000    | 10                                                                                                         | 31.292                              | 11000    | 30                                 | 7.481                               |  |  |  |

| 01001    | 12                                                                                                         | 28.615                              | 11001    | 32                                 | 6.841                               |  |  |  |

| 01010    | 14                                                                                                         | 26.167                              | 11010    | 34                                 | 6.256                               |  |  |  |

| 01011    | 16                                                                                                         | 23.928                              | 11011    | 36                                 | 5.720                               |  |  |  |

| 01100    | 18                                                                                                         | 21.881                              | 11100    | 38                                 | 5.231                               |  |  |  |

| 01101    | 1A                                                                                                         | 20.009                              | 11101    | ЗA                                 | 4.783                               |  |  |  |

| 01110    | 1C                                                                                                         | 18.297                              | 11110    | 3C                                 | 4.374                               |  |  |  |

| 01111    | 1E                                                                                                         | 16.732                              | 11111    | 3E                                 | 4.000                               |  |  |  |

Operating independently from the multiplexer, the uS5651P have comparators for each bus inputs and VCC. The BS\_IN input is internally connected to another voltage divider (fixed as 1/32). In each channel, a comparator compares (1/32) downscaled bus voltage with BS\_REF (divided from BG\_REF\_OUT) to indicate whether the bus voltage is good for operation. When the (1/32) downscaled bus voltage of all active channels are higher than BS\_REF, VCC is higher than a threshold (for BS\_OK) and the SKIP pin is logic High, the BS\_OK (open-drain) is set to high impedance state (BS\_OK=High) to indicate bus voltage is good. Note that the Bus\_Gain setting in I<sup>2</sup>C registers does not affect the BS\_OK function since they are operated independently.

### **Functional Description**

#### ENABLE, SKIP and BS\_INx

The BS\_OK function provides an indication that all the effective bus voltage inputs are above the user-defined level. BS\_OK keeps low if any of the active bus voltage inputs fall below the user-defined level. In addition, the SKIP pin provides a flexibility to modify the logic of ENABLE, BS\_IN and BS\_OK. The complete logic table of ENABLE, BS\_IN, BS\_OK and SKIP is as Table 6. The SKIP pin is used to provide power to hold BS\_OK=Low in the absence of VCC.

|     |        | Table  | 0. LUGI |                             | E, SKIP, DS_INX and DS_OK                      |

|-----|--------|--------|---------|-----------------------------|------------------------------------------------|

| VCC | ENABLE | BS_INx | SKIP    | BS_OK                       | Note                                           |

| L   | L      | Х      | L       | H (open drain)              | No power is provided to the device.            |

| L   | L      | Х      | Н       | L                           | Enabled. SKIP pin provides power to hold BS_OK |

| Н   | Н      | Х      | L       | H (open drain)              | Disable state (standby mode).                  |

| Н   | н      | Х      | Н       | L                           | Disable state (standby mode).                  |

| н   | L      |        | н       | L                           | Fully functional.                              |

|     | High Z | L      | п       | L                           | Enabled but with limited function.             |

| н   | L      | Н      | Н       | H (apap drain)              | Fully functional.                              |

|     | High Z |        | п       | H (open drain)              | Enabled but with limited function.             |

| н   | L      | х      |         | H (apap drain)              | Fully functional.                              |

|     | High Z | ^      | L       | H (open drain)              | Enabled but with limited function.             |

|     |        | L=Low  | , H=Hig | High Z=High impedance state |                                                |

|     |        |        |         |                             |                                                |

Table 6. Logic State of ENABLE, SKIP, BS INx and BS OK

#### Voltage Regulator IMON Monitoring

The uS5651P provides two analog input channels for voltage regulator IMON signal monitoring. IMON\_IN1 and IMON\_IN2 are connected to the total output current signal of voltage regulators. The input of IMON\_IN1 and IMON\_IN2 are fed to the multiplexer through a unity gain voltage buffer. The ADC of the GPU then receives the voltage regulator total output current information.

### **Reference Ground (RGND) Monitoring**

The RGND pin is treated as a reference ground input (RGND) of device. The uS5651P uses RGND as an input and mux it through signal chain, and the corresponding output at DIFF\_OUT\_P/N denotes the offset error of the differential amplifier. The GPU is then able to get the information of differential amplifier offset error, which can be used for offset cancellation when needed.

### **Functional Description**

### I<sup>2</sup>C Register and Function Setting

Most of the functions of the device are controlled by registers. Table 7 shows the register map. Operation of each main function is described in the following sections.

| Register<br>Address | Register Name          | Bit                                                                                                                           | Туре | Description                                                                 | Default Valu            | e   | New Value<br>Takes Effect |

|---------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------|-------------------------|-----|---------------------------|

| 0x00h               | Vendor ID              | 7:0                                                                                                                           | R    | Vendor specific ID                                                          | 4E                      |     |                           |

| 0x01h               | Device ID              | 7:0                                                                                                                           | R    |                                                                             | 2E                      |     |                           |

|                     |                        | 7                                                                                                                             | R/W  | Ground Reference                                                            | 0(disable)              |     | At next timeout           |

|                     |                        | 6                                                                                                                             |      | Don't care                                                                  | 0                       |     |                           |

|                     |                        | 5                                                                                                                             | R/W  | IMON Channel 2                                                              | 0(disable)              |     | At next timeout           |

| 0.04                |                        | 4                                                                                                                             | R/W  | IMON Channel 1                                                              | 0(disable)              | 0.5 | At next timeout           |

| 0x04h               | Active Channel         | 3                                                                                                                             | R/W  | Channel 4 Voltage & Current                                                 | 1(enable)               | 0F  | At next timeout           |

|                     |                        | 2                                                                                                                             | R/W  | Channel 3 Voltage & Current                                                 | 1(enable)               |     | At next timeout           |

|                     |                        | 1                                                                                                                             | R/W  | Channel 2 Voltage & Current                                                 | 1(enable)               |     | At next timeout           |

|                     |                        | 0                                                                                                                             | R/W  | Channel 1 Voltage & Current                                                 | 1(enable)               |     | At next timeout           |

|                     |                        | 7:4                                                                                                                           | R/W  | Pulses to skip at start of cycle (operated as Device B in dual device mode) | 0 (no pulse to<br>skip) |     | At next timeout           |

| 0x05h               | MUL_SEL Skip           | 3:0                                                                                                                           | R/W  | Pulses to skip at start of cycle (operated as Device A in dual device mode) | 0 (no pulse to<br>skip) | 00  | At next timeout           |

| 0x06h               | Alternating            | 7                                                                                                                             | R/W  | Bit7=1: Enable alternating mode<br>Bit7=0: No alternating                   | 0 (No<br>alternating)   | 00  | At next timeout           |

|                     | Mode                   | 6:0                                                                                                                           |      | Don't care                                                                  | 0                       |     |                           |

|                     |                        | 7:4                                                                                                                           |      | Don't care                                                                  | 0                       |     |                           |

| 0x07h               | Offset Voltage         | 3:0                                                                                                                           | R/W  | 1111= -375mV<br><br>0001= -25mV<br>0000= 0mV                                | 0(0mV)                  | 00  | At next timeout           |

|                     |                        | 7:4                                                                                                                           |      | Don't care                                                                  | 0                       |     |                           |

| 0x08                | Common Mode<br>Voltage | 3:0                                                                                                                           | R/W  | 1111= 875mV<br><br>0001= 525mV<br>0000= 500mV                               | 7 (675mV)               | 07  | At next timeout           |

| 0x0F                | Timeout                | Timeout         7         R/W         Bit7=1: Disable timeout           Bit7=0: Enable timeout         Bit7=0: Enable timeout |      |                                                                             | 0 (Enable<br>timeout)   | 00  |                           |

|                     |                        | 6:0                                                                                                                           |      | Don't care                                                                  | 0                       |     |                           |

Table 7. Register Map

### **Functional Description**

| Register<br>Address | Register Name | Bit | Туре | Description                                                                                         |    | Default Value            | New Value<br>Takes Effect |

|---------------------|---------------|-----|------|-----------------------------------------------------------------------------------------------------|----|--------------------------|---------------------------|

| 0x10                | Bus_Gain 1    | 5:1 | R/W  |                                                                                                     |    | 00(64)                   | At next timeout           |

| 0x11                | Bus_Gain 2    | 5:1 | R/W  | See Table 5 <sup>(2)</sup>                                                                          |    | 00(64)                   | At next timeout           |

| 0x12                | Bus_Gain 3    | 5:1 | R/W  | See Table 5                                                                                         |    | 00(64)                   | At next timeout           |

| 0x13                | Bus_Gain 4    | 5:1 | R/W  |                                                                                                     |    | 00(64)                   | At next timeout           |

| 0x20                | Shunt_Gain 1  | 5:1 | R/W  |                                                                                                     |    | 00(2)                    | At next timeout           |

| 0x21                | Shunt_Gain 2  | 5:1 | R/W  | See Table 4 <sup>(2)</sup>                                                                          |    | 00(2)                    | At next timeout           |

| 0x22                | Shunt_Gain 3  | 5:1 | R/W  | See Table 4                                                                                         |    | 00(2)                    | At next timeout           |

| 0x23                | Shunt_Gain 4  | 5:1 | R/W  |                                                                                                     |    | 00(2)                    | At next timeout           |

|                     |               | 7:2 |      | Don't care                                                                                          |    | 0                        |                           |

|                     |               | 1   | R/W  | Bit1=1: Lock interface write action<br>Bit1=0: Allow interface write action                         |    | 0 (allow write)          | Immediately               |

| 0x24                | Lock          | 0   | R/W  | Bit1=1: Lock interface read and<br>write action<br>Bit1=0: Allow interface read and<br>write action | 00 | 0 (allow read and write) | Immediately               |

Table 7. Register Map (cont.)

Note 1: R=Read, R/W=Read and Write

Note 2: For Bus\_Gain and Shunt\_Gain registers, bit [7:6] and bit 0 are always 0.

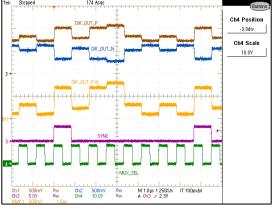

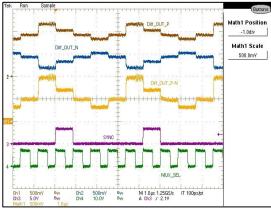

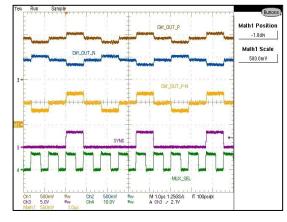

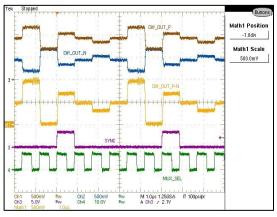

#### MUX\_SEL and Multiplexer Output Sequence

A differential amplifier outputs a scaled bus voltage and shunt current (in the form of voltage) for active channels. These voltage and current information are sent to DIFF\_OUT\_P and DIFF\_OUT\_N via a multiplexer.

The multiplexer selection is done through a single bit digital input clock MUX\_SEL. The device monitors the input and cycle the output in a fixed sequence. The sequence starts with the bus voltage of first enumerated and active channel before changing to its shunt. It then cycles likewise through the bus/shunt pairs in order of enumeration repeating itself after the shunt of the last active channel has been passed through the multiplexer. The multiplexer repeats the cycle indefinitely until either a timeout condition is detected or device is disabled. The multiplexer default output sequence is shown in Table 8.

|                                                                                                                                         | 1      |       |         |       |         |       |         |       |         |       | 1       |       | 1       |       |         | 1     | 1       |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------|-------|---------|-------|---------|-------|---------|-------|---------|-------|---------|-------|---------|-------|---------|-------|---------|

| MUX_SEL                                                                                                                                 | 0      | 1     | 2       | 3     | 4       | 5     | 6       | 7     | 8       | 9     | 10      | 11    | 12      | 13    | 14      | 15    | 16      |

| clock cycle                                                                                                                             | ů      |       | -       | Ŭ     | ·       | °,    | Ŭ       | ·     | Ŭ       | Ũ     |         |       |         |       |         |       |         |

| Differential                                                                                                                            | High Z | Ch1   | Ch1     | Ch2   | Ch2     | Ch3   | Ch3     | Ch4   | Ch4     | Ch1   | Ch1     | Ch2   | Ch2     | Ch3   | Ch3     | Ch4   | Ch4     |

| Output                                                                                                                                  | High Z | Bus V | Shunt I |

| Register setting: 0x04h=0F(default, IMON1, IMON2, RGND are off), 0x05h=00(default, no pulse to skip), 0x06h=00(default, no alternating) |        |       |         |       |         |       |         |       |         |       |         |       |         |       |         |       |         |

|          |                |            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3        | Bit 2        | Bit 1        | Bit 0        |

|----------|----------------|------------|-------|-------|-------|-------|--------------|--------------|--------------|--------------|

| register | value<br>(hex) | value(bin) | RGND  | RSVD  | IMON2 | IMON1 | CH4<br>(V&I) | CH3<br>(V&I) | CH2<br>(V&I) | CH1<br>(V&I) |

| 0x04h    | 0F             | 00001111   | OFF   | Х     | OFF   | OFF   | ON           | ON           | ON           | ON           |

### **Functional Description**

#### Active Channel Configuration (0x04h)

The device can be configured to work with a reduced channel. Register 0x04h determines which channel is active and to be monitored. The default setting of 0x04h is 0F, which means only CH1~CH4 are active and its voltage and current signals are the output.

Table 9 and Table 10 are examples of the multiplexer output sequence with reduced channel.

Table 9. An Example of Multiplexer Output Sequence with Reduced Channel

| MUX_SEL<br>clock cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0      | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11      | 12  | 13  | 14  | 15  | 16  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---------|-----|-----|-----|-----|-----|

| Differential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Link 7 | Ch1 | Ch1 | Ch3 | Ch3 | Ch1 | Ch1 | Ch3 | Ch3 | Ch1 | Ch1 | Ch3     | Ch3 | Ch1 | Ch1 | Ch3 | Ch3 |

| Output         High Z         Bus V         Shunt I         Shunt I |        |     |     |     |     |     |     |     |     |     |     | Shunt I |     |     |     |     |     |

| Register setting: 0x04h=05(Ch2, Ch4, IMON1, IMON2, RGND are off), 0x05h=00(default, no pulse to skip), 0x06h=00(default, no alternating)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |     |     |     |     |     |     |     |     |     |     |         |     |     |     |     |     |

|          |       |             | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|-------|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| register | value | value(bin)  | RGND  | RSVD  | IMON2 | IMON1 | CH4   | CH3   | CH2   | CH1   |

| rogiotoi | (hex) | raido(biii) |       |       |       |       | (V&I) | (V&I) | (V&I) | (V&I) |

| 0x04     | 05    | 00000101    | OFF   | Х     | OFF   | OFF   | OFF   | ON    | OFF   | ON    |

Table 10. Another Example of Multiplexer Output Sequence with Reduced Channel

| MUX_SEL<br>clock cycle | 0                                                                                                                | 1     | 2       | 3     | 4       | 5     | 6       | 7     | 8       | 9       | 10   | 11    | 12      | 13    | 14      | 15    | 16      | 17    | 18      | 19     | 20    |

|------------------------|------------------------------------------------------------------------------------------------------------------|-------|---------|-------|---------|-------|---------|-------|---------|---------|------|-------|---------|-------|---------|-------|---------|-------|---------|--------|-------|

| Differential           | High Z                                                                                                           | Ch1   | Ch1     | Ch2   | Ch2     | Ch3   | Ch3     | Ch4   | Ch4     | IMON2   | POND | Ch1   | Ch1     | Ch2   | Ch2     | Ch3   | Ch3     | Ch4   | Ch4     | IMON2  | RGND  |

| Output                 |                                                                                                                  | Bus V | Shunt I | INICINZ | RGND | Bus V | Shunt I | INIONZ | RGIND |

| Register setti         | Register setting: 0x04h=AF(IMON1 is off), 0x05h=00(default, no pulse to skip), 0x06h=00(default, no alternating) |       |         |       |         |       |         |       |         |         |      |       |         |       |         |       |         |       |         |        |       |

|          |                |            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3        | Bit 2        | Bit 1        | Bit 0        |

|----------|----------------|------------|-------|-------|-------|-------|--------------|--------------|--------------|--------------|

| register | value<br>(hex) | value(bin) | RGND  | RSVD  | IMON2 | IMON1 | CH4<br>(V&I) | CH3<br>(V&I) | CH2<br>(V&I) | CH1<br>(V&I) |

| 0x04     | AF             | 10101111   | ON    | Х     | ON    | OFF   | ON           | ON           | ON           | ON           |

### Dual Device (MUX\_SEL Skips) Mode (0x05h)

The uS5651P can be configured to work in one of three modes of operation: stand-alone, as device-A, or as device-B per register 0x05h (MUX\_SEL Skips) setting. The default setting of 0x05h is 00, which means stand-alone mode operation with no pulse to skip. In stand-alone mode, the device cycles through channels based on active channel configuration in register 0x04h. There is no skip pulse in either start or end of cycles. As device-A mode, the device respond to the first set of clock cycle and then go into high impedance, waiting specified amount of cycles programmed in 0x05h bit [3:0].

While device-B skips the start of cycles programmed in 0x05 bit [7:4], then responds to the subsequent clocks. With the capability of specifying different skip cycles for two devices, asymmetric channel configuration is achieved. Table 11 shows an example of multiplexer output sequence of dual device mode with asymmetric channel configuration. When in dual device mode, one device is configured as device-A, and the other is configured as device-B, both share the MUX\_SEL and DIFF\_OUT lines on the PCB as shown in the typical application circuit section.

### **Functional Description**

#### Table 11. An Example of Multiplexer Output Sequence of Dual Device Mode

| MUX_SEL<br>clock cycle                                                                                                      | 0      | 1            | 2              | 3            | 4              | 5            | 6              | 7      | 8      | 9      | 10           | 11             | 12           | 13             | 14     | 15           | 16             |

|-----------------------------------------------------------------------------------------------------------------------------|--------|--------------|----------------|--------------|----------------|--------------|----------------|--------|--------|--------|--------------|----------------|--------------|----------------|--------|--------------|----------------|

| Device- A<br>Differential<br>Output                                                                                         | High Z | Ch1<br>Bus V | Ch1<br>Shunt I | Ch2<br>Bus V | Ch2<br>Shunt I | Ch3<br>Bus V | Ch3<br>Shunt I | IMON1  | IMON2  | RGND   | High Z       | High Z         | High Z       | High Z         | High Z | Ch1<br>Bus V | Ch1<br>Shunt I |

| Device- B<br>Differential<br>Output                                                                                         | High Z | High Z       | High Z         | High Z       | High Z         | High Z       | High Z         | High Z | High Z | High Z | Ch1<br>Bus V | Ch1<br>Shunt I | Ch3<br>Bus V | Ch3<br>Shunt I | RGND   | High Z       | High Z         |

| Device-A register setting: 0x04h=B7(CH4 is off), 0x05h=05(as device-A, 5 pulses to skip), 0x06h=00(default, no alternating) |        |              |                |              |                |              |                |        |        |        |              |                |              |                |        |              |                |

Device-B register setting: 0x04h=85(CH2, CH4, IMON1, IMON2 are off), 0x05h=90(as device-B, 9 pulses to skip), 0x06h=00(default, no alternating)

|          |       |             | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|-------|-------------|-------|-------|---------|---------|-------|-------|-------|-------|

| register | value | value(bin)  | RGND  | RSVD  | IMON2   | IMON1   | CH4   | CH3   | CH2   | CH1   |

| register | (hex) | value(bill) | RGND  | ROVD  | INICINZ | INICIAL | (V&I) | (V&I) | (V&I) | (V&I) |

| 0x04     | B7    | 10110111    | ON    | Х     | ON      | ON      | OFF   | ON    | ON    | ON    |

| 0x04     | 85    | 10000101    | ON    | Х     | OFF     | OFF     | OFF   | ON    | OFF   | ON    |

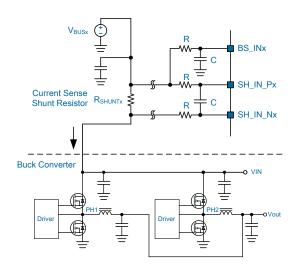

#### Alternating Mode (0x06h)

The device can be configured to work in alternating differential polarity mode (alternating mode), which is set by register 0x06h. In alternating mode, the polarity of the input signal to the differential amplifier and its output is reversed. The polarity reversal technique is often used to cancel potential offset error of the differential amplifier.

Figure 4 shows the simplified input and output diagram of the differential amplifier.  $V_{DM}$  is the differential input signal,  $V_{OFS\_ERR}$  is the offset error of the differential amplifier,  $V_{DIFF\_OUT}$  is the output, S1 and S2 are switches used to reverse the polarity. The result of first measurement with S1 turned on is

$$V_{DIFF_OUT}(S_1) = V_{DIFF_OUT_P} - V_{DIFF_OUT_N} = V_{DM} + (V_{OFS_ERR})$$

(Eq. 1)

The result of second measurement with S2 turned on (reversed input and output polarity) is

$V_{DIFF_OUT}(S_2) = V_{DIFF_OUT_P} - V_{DIFF_OUT_N} = V_{DM} + (-V_{OFS_ERR})$  (Eq. 2)

Add Eq. 2 and Eq. 1 yields the final result,

$V_{DIFF_OUT}(S_1+S_2)=2*V_{DM}$  (Eq. 3)

The polarity reversal technique effectively removes the offset error. When the device works in alternating mode, the polarity changes in an alternating way as described above. With the alternating mode, the GPU is able to get more accurate voltage/current reporting from the device.

Figure 4. Polarity Reversal in Alternating Mode

When alternating mode is enabled, the N channel device will first output N pairs of differential signal, then each channel signal become reversed differential output. If the reference ground channel is enabled, the reference ground channel is also reversed in alternating mode. Table 12 is an example of multiplexer output sequence of stand-alone application with alternating mode enabled. Table 13 is an example of multiplexer output sequence of dual device application with alternating mode enabled.

### **Functional Description**

Table 12. An Example of Multiplexer Output Sequence of Stand-Alone Mode with Alternating Mode Enabled

| MUX_SEL<br>clock cycle | 0                                                                                                                        | 1            | 2              | 3            | 4              | 5            | 6              | 7            | 8              | 9     | 10 | 11                       | 12                         | 13                       | 14                         | 15                       | 16                         | 17                       | 18                         | 19                | 20 | 21           | 22             |

|------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------|----------------|--------------|----------------|--------------|----------------|--------------|----------------|-------|----|--------------------------|----------------------------|--------------------------|----------------------------|--------------------------|----------------------------|--------------------------|----------------------------|-------------------|----|--------------|----------------|

| Differential<br>Output | High Z                                                                                                                   | Ch1<br>Bus V | Ch1<br>Shunt I | Ch2<br>Bus V | Ch2<br>Shunt I | Ch3<br>Bus V | Ch3<br>Shunt I | Ch4<br>Bus V | Ch4<br>Shunt I | IMON2 |    | Ch1<br>Bus V<br>Reversed | Ch1<br>Shunt I<br>Reversed | Ch2<br>Bus V<br>Reversed | Ch2<br>Shunt I<br>Reversed | Ch3<br>Bus V<br>Reversed | Ch3<br>Shunt I<br>Reversed | Ch4<br>Bus V<br>Reversed | Ch4<br>Shunt I<br>Reversed | IMON2<br>Reversed |    | Ch1<br>Bus V | Ch1<br>Shunt I |

| Register sett          | tegister setting: 0x04h=AF(IMON1 is off), 0x05h=00(default, no pulse to skip), 0x06h=80(bit7=1, enable alternating mode) |              |                |              |                |              |                |              |                |       |    |                          |                            |                          |                            |                          |                            |                          |                            |                   |    |              |                |

|          |                |            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3        | Bit 2        | Bit 1        | Bit 0        |

|----------|----------------|------------|-------|-------|-------|-------|--------------|--------------|--------------|--------------|

| register | value<br>(hex) | value(bin) | RGND  | RSVD  | IMON2 | IMON1 | CH4<br>(V&I) | CH3<br>(V&I) | CH2<br>(V&I) | CH1<br>(V&I) |

| 0x04     | AF             | 10101111   | ON    | Х     | ON    | OFF   | ON           | ON           | ON           | ON           |

#### Table 13. An Example of Multiplexer Output Sequence of Dual Device Mode with Alternating Mode Enabled

| MUX_SEL<br>clock cycle              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1            | 2              | 3            | 4              | 5            | 6              | 7      | 8      | 9            | 10             | 11           | 12             | 13     | 14                       | 15                         | 16                       | 17                         | 18     | 19                         | 20                | 21               | 22                       | 23                         | 24     | 25                         | 26     | 27           | 28             |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|--------------|----------------|--------------|----------------|--------|--------|--------------|----------------|--------------|----------------|--------|--------------------------|----------------------------|--------------------------|----------------------------|--------|----------------------------|-------------------|------------------|--------------------------|----------------------------|--------|----------------------------|--------|--------------|----------------|

| Device- A<br>Differential<br>Output | High Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Ch1<br>Bus V | Ch1<br>Shunt I | Ch2<br>Bus V | Ch2<br>Shunt I | Ch3<br>Bus V | Ch3<br>Shunt I | IMON2  | RGND   | High Z       | High Z         | High Z       | High Z         | High Z | Ch1<br>Bus V<br>Reversed | Ch1<br>Shunt I<br>Reversed | Ch2<br>Bus V<br>Reversed | Ch2<br>Shunt I<br>Reversed |        | Ch3<br>Shunt I<br>Reversed | IMON2<br>Reversed | RGND<br>Reversed | High Z                   | High Z                     | High Z | High Z                     | High Z | Ch1<br>Bus V | Ch1<br>Shunt I |

| Device- B<br>Differential<br>Output | High Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | High Z       | High Z         | High Z       | High Z         | High Z       | High Z         | High Z | High Z | Ch1<br>Bus V | Ch1<br>Shunt I | Ch3<br>Bus V | Ch3<br>Shunt I | RGND   | High Z                   | High Z                     | High Z                   | High Z                     | High Z | High Z                     | High Z            | High Z           | Ch1<br>Bus V<br>Reversed | Ch1<br>Shunt I<br>Reversed |        | Ch3<br>Shunt I<br>Reversed |        | High Z       | High Z         |

|                                     | wice-A register setting: 0x40H=A7(IMON1, CH4 are off), 0x05H=05(as device-A, 5 pulses to skip), 0x05H=05(as device-A, 5 |              |                |              |                |              |                |        |        |              |                |              |                |        |                          |                            |                          |                            |        |                            |                   |                  |                          |                            |        |                            |        |              |                |

|          |       |             | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|-------|-------------|-------|-------|---------|---------|-------|-------|-------|-------|

| register | value | value(bin)  | RGND  | RSVD  | IMON2   | IMON1   | CH4   | CH3   | CH2   | CH1   |

| register | (hex) | value(DIII) | RGND  | ROVD  | IIVIONZ | INICIAL | (V&I) | (V&I) | (V&I) | (V&I) |

| 0x04     | A7    | 10100111    | ON    | Х     | ON      | OFF     | OFF   | ON    | ON    | ON    |

| 0x04     | 85    | 10000101    | ON    | Х     | OFF     | OFF     | OFF   | ON    | OFF   | ON    |

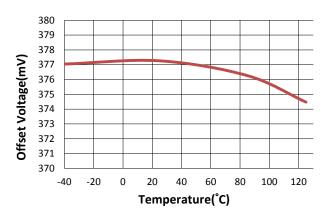

#### Offset Voltage for Differential Output (0x07h)