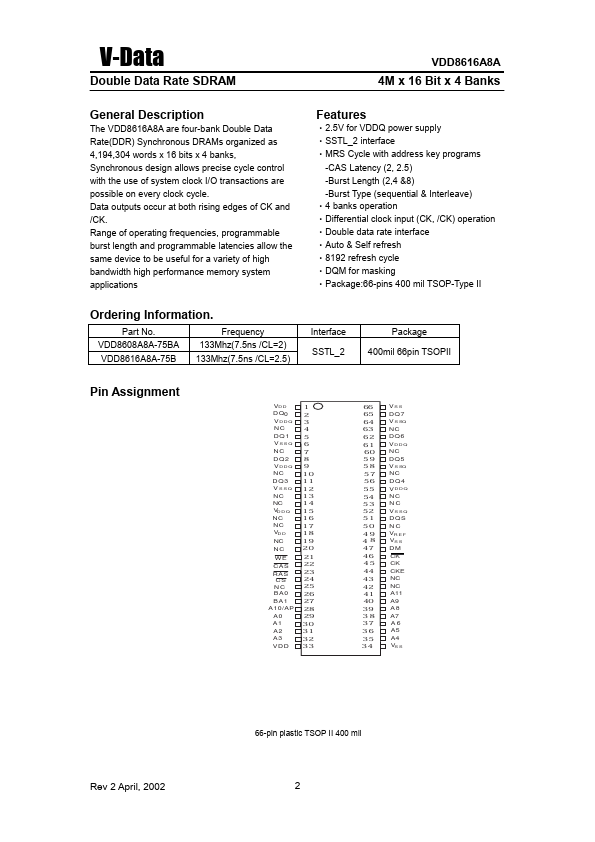

VDD8616A8A Description

The VDD8616A8A are four-bank Double Data Rate(DDR) Synchronous DRAMs organized as 4,194,304 words x 16 bits x 4 banks, Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle. Data outputs occur at both rising edges of CK and /CK. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be...