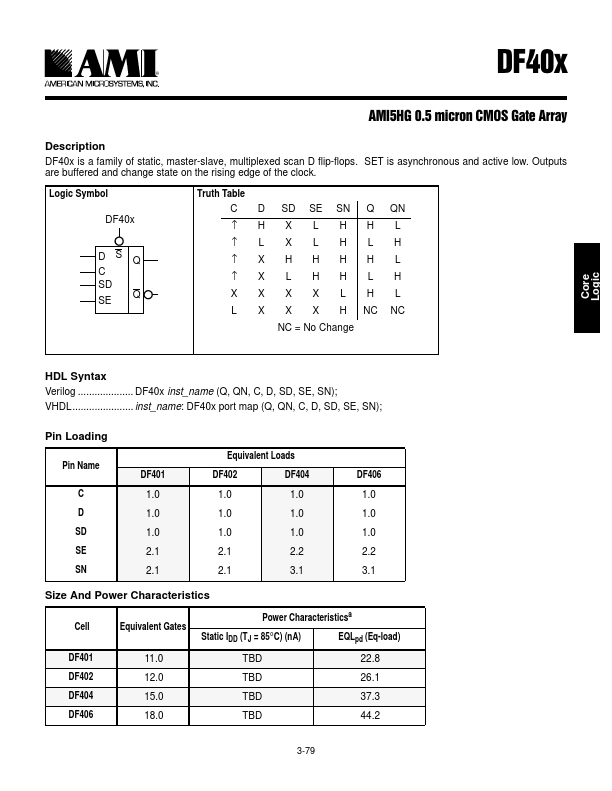

- Part: DF401

- Description: CMOS Gate Array

- Manufacturer: AMI

- Size: 46.03 KB

Datasheets by Manufacturer

| Part Number | Manufacturer | Description |

|---|---|---|

| DF40SC3L | Shindengen | Schottky Barrier Diode |

| CD-DF406SL | Bourns | Surface Mount Bridge Rectifier Diode |

| DF40AA160 | SanRex Corporation | DIODE |

| DF40BA80 | SanRex Corporation | Power Diode |

| CD-DF408S | Bourns | Surface Mount Bridge Rectifier Diode |

| CD-DF406S | Bourns | Surface Mount Bridge Rectifier Diode |

| DF40SC4 | Shindengen | Schottky Barrier Diodes |