ODTSXN12 Description

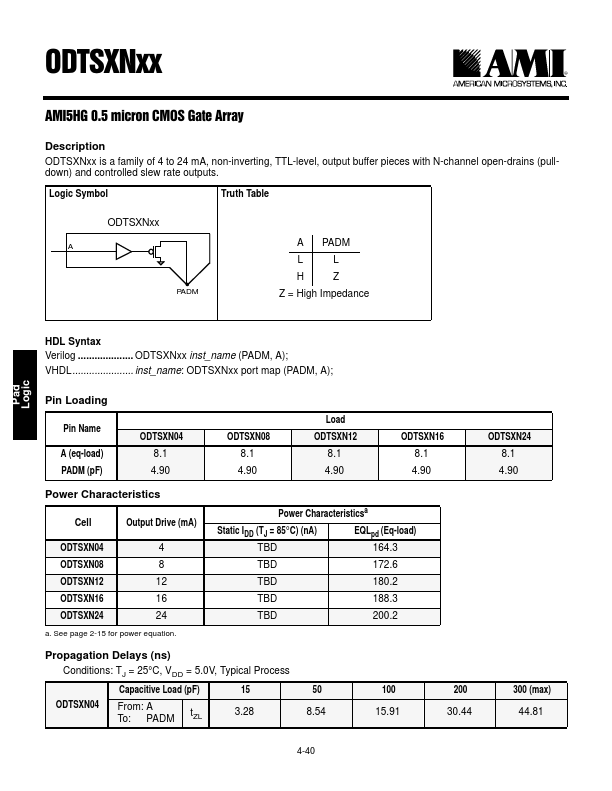

ODTSXNxx is a family of 4 to 24 mA, non-inverting, TTL-level, output buffer pieces with N-channel open-drains (pulldown) and controlled slew rate outputs. Logic Symbol Truth Table ODTSXNxx A PADM A PADM LL HZ Z = High Impedance Pad Logic HDL Syntax Verilog .................... ODTSXNxx inst_name (PADM, A);.