AMIS-710651-A4

Key Features

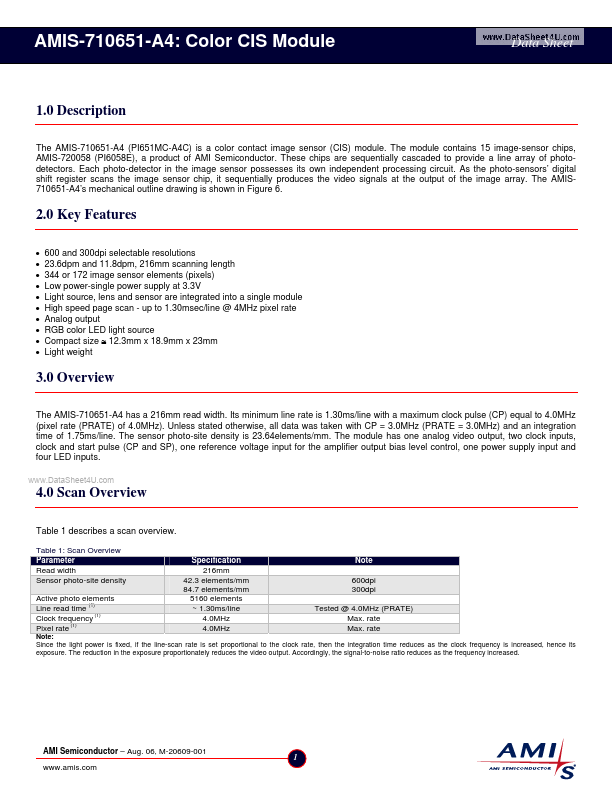

- Its minimum line rate is 1.30ms/line with a maximum clock pulse (CP) equal to 4.0MHz (pixel rate (PRATE) of 4.0MHz)

- Unless stated otherwise, all data was taken with CP = 3.0MHz (PRATE = 3.0MHz) and an integration time of 1.75ms/line

- The sensor photo-site density is 23.64elements/mm

- 4.0 Scan Overview Table 1 describes a scan overview

- The reduction in the exposure proportionately reduces the video output

- Accordingly, the signal-to-noise ratio reduces as the frequency increased

- AMI Semiconductor - Aug

- 06, M-20609-001 .amis

- 1 AMIS-710651-A4: Color CIS Module 5.0 Physical Overview Table 2 describes a physical overview

- This signal pixel level should be operated at less than