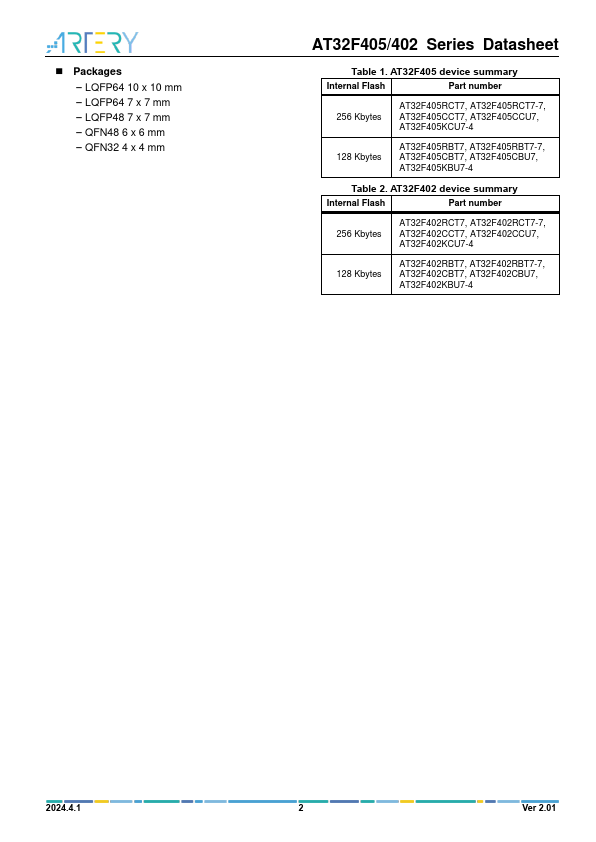

AT32F402 Overview

AT32F405/402 Series Datasheet ARM®-based 32-bit Cortex®-M4 MCU with FPU, 128 to 256 KB Flash, sLib, 14 timers, 1 ADC, 19 munication interfaces (CAN, OTGHS, OTGFS).

AT32F402 Key Features

- Core: ARM® 32-bit Cortex®-M4 CPU with FPU

- 216 MHz maximum frequency, with a memory protection unit (MPU), single-cycle multiplication and hardware division

- Floating point unit (FPU)

- DSP instructions

- Memories

- 128 to 256 Kbytes of Flash memory

- 20 Kbytes of boot memory used as a Bootloader or as a general instruction/data memory (one-time programmable)

- sLib: configurable part of main Flash as a library area with code executable but secured, non-readable

- 70 to 102 Kbytes of SRAM (the first 48 KB with parity check)

- QSPI interface for interfacing external SPI memory or SPI RAM extension, supporting address mapping mode