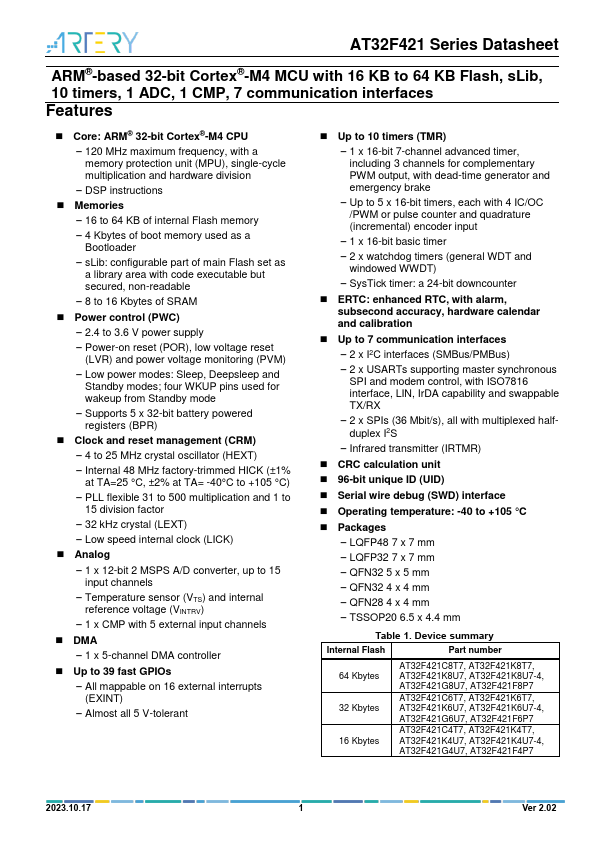

AT32F421

Features

- Core: ARM® 32-bit Cortex®-M4 CPU

- 120 MHz maximum frequency, with a memory protection unit (MPU), single-cycle multiplication and hardware division

- DSP instructions

- Memories

- 16 to 64 KB of internal Flash memory

- 4 Kbytes of boot memory used as a

Bootloader

- s Lib: configurable part of main Flash set as a library area with code executable but secured, non-readable

- 8 to 16 Kbytes of SRAM

- Power control (PWC)

- 2.4 to 3.6 V power supply

- Power-on reset (POR), low voltage reset

(LVR) and power voltage monitoring (PVM)

- Low power modes: Sleep, Deepsleep and Standby modes; four WKUP pins used for wakeup from Standby mode

- Supports 5 x 32-bit battery powered registers (BPR)

- Clock and reset management (CRM)

- 4 to 25 MHz crystal oscillator (HEXT)

- Internal 48 MHz factory-trimmed HICK (±1% at TA=25 °C, ±2% at TA= -40°C to +105 °C)

- PLL flexible 31 to 500 multiplication and 1 to 15 division factor

- 32 k Hz crystal (LEXT)

- Low speed internal clock (LICK)

- Analog

-...