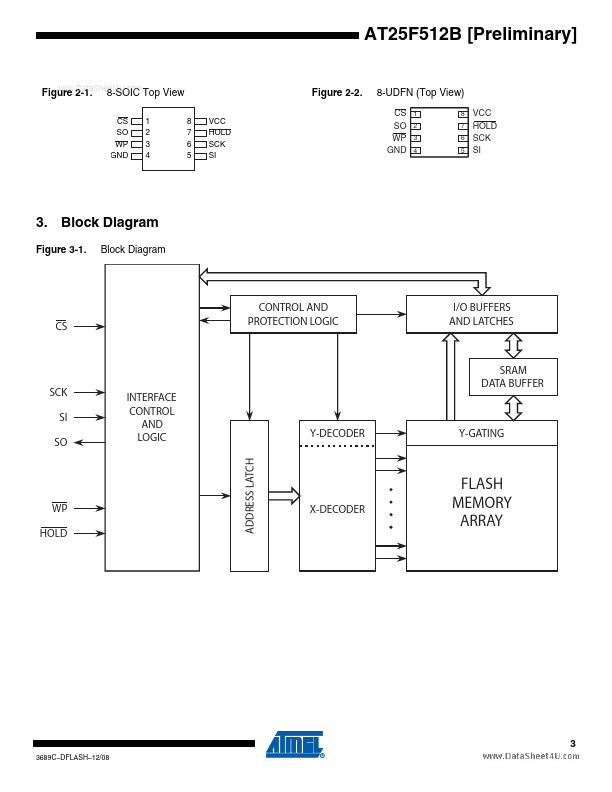

AT25F512B Description

The AT25F512B is a serial interface Flash memory device designed for use in a wide variety of high-volume consumer based applications in which program code is shadowed from Flash memory into embedded or external RAM for execution. The flexible erase architecture of the AT25F512B, with its erase granularity as small as 4 Kbytes, makes it ideal for data storage as well, eliminating the need for additional data storage...

AT25F512B Key Features

- Single 2.7V

- 3.6V Supply

- Serial Peripheral Interface (SPI) patible

- Supports SPI Modes 0 and 3

- 70 MHz Maximum Operating Frequency

- Clock-to-Output (tV) of 6 ns Maximum

- Flexible, Optimized Erase Architecture for Code + Data Storage