Key Specifications

Pins: 256

| Part | TSC695F |

|---|---|

| Description | Rad-Hard 32-bit SPARC Embedded Processor |

| Manufacturer | Atmel |

| Size | 2.50 MB |

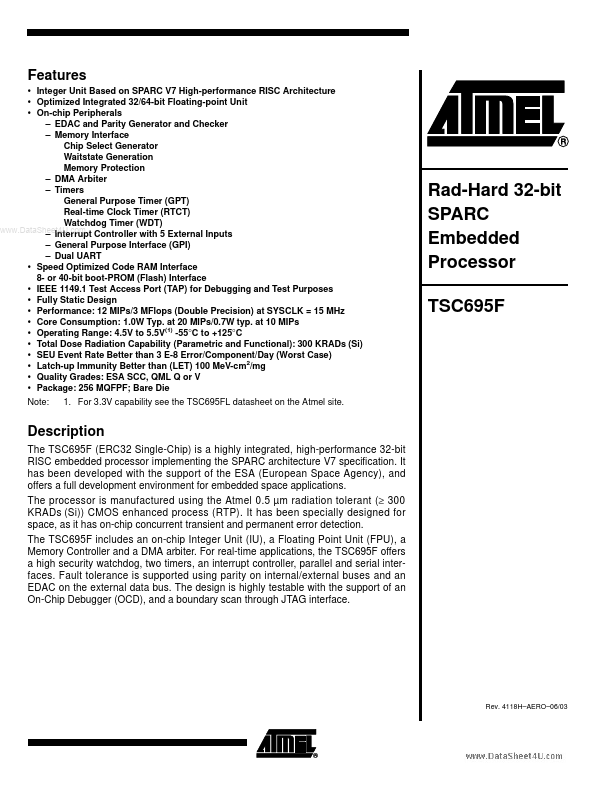

Rad-Hard 32-bit SPARC Embedded Processor

The TSC695F (ERC32 Single-Chip) is a highly integrated, high-performance 32-bit RISC embedded processor implementing the SPARC architecture V7 specification. It has been developed with the support of the ESA (European Space Agency), and offers a full development environment for embedded space applications.

Integer Unit Based on SPARC V7 High-performance RISC Architecture

Optimized Integrated 32/64-bit Floating-point Unit

Speed Optimized Code RAM Interface 8- or 40-bit boot-PROM (Flash) Interface

IEEE 1149.1 Test Access Port (TAP) for Debugging and Test Purposes

Fully Static Design

Price & Availability

| Seller | Price Breaks | Buy | |

|---|---|---|---|

| No distributor offers were returned for this part. | |||