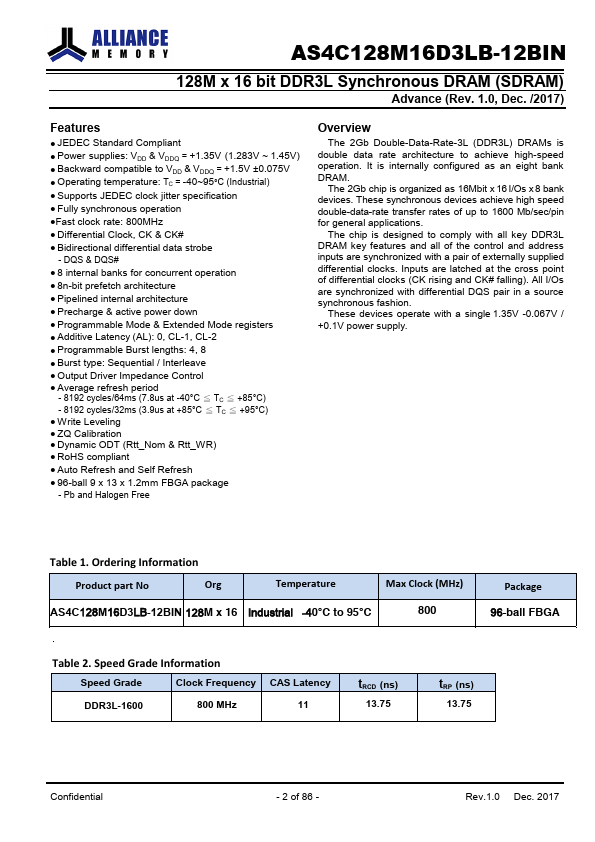

AS4C128M16D3LB-12BIN Description

2017 Alliance Memory Inc. 511 Taylor Way, San Carlos, CA 94070 TEL: (650) 620-9211 Alliance Memory Inc.

AS4C128M16D3LB-12BIN Key Features

- JEDEC Standard pliant

- Power supplies: VDD & VDDQ = +1.35V (1.283V ~ 1.45V)

- Backward patible to VDD & VDDQ = +1.5V ±0.075V

- Operating temperature: TC = -40~95°C (Industrial)

- Supports JEDEC clock jitter specification

- Fully synchronous operation

- Fast clock rate: 800MHz

- Differential Clock, CK & CK#

- Bidirectional differential data strobe

- DQS & DQS#