Datasheet Summary

AS4C128M16D3LC-12BIN AS4C128M16D3LC-12BCN

Revision History 2Gb AS4C128M16D3LC 96 ball FBGA PACKAGE

Revision Details Rev 1.0 Initial Release

Date Feb.2020

Alliance Memory Inc. 12815 NE 124th St. STE#D,Kirkland WA 98034 TEL: (425) 898-44356 FAX: (425) 868-8628 Alliance Memory Inc. reserves the right to change products or specification without notice

Confidential

- 1 of 87

- Rev.1.0 FEB. 2020

AS4C128M16D3LC-12BIN AS4C128M16D3LC-12BCN

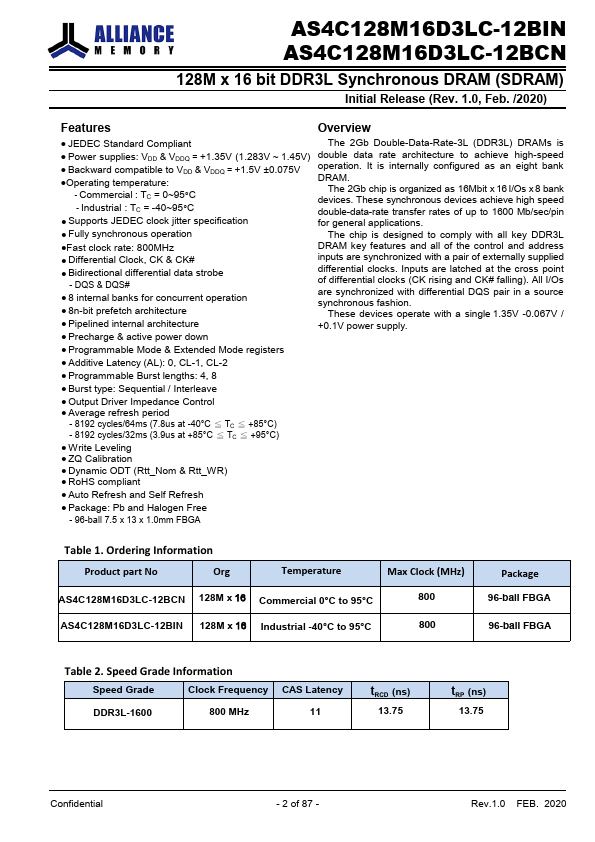

128M x 16 bit DDR3L Synchronous DRAM (SDRAM)

Initial Release (Rev. 1.0, Feb. /2020)

Features

Overview

- JEDEC Standard pliant

The 2Gb Double-Data-Rate-3L (DDR3L) DRAMs is

- Power supplies: VDD & VDDQ = +1.35V (1.283V ~ 1.45V) double data rate...