AS6C62256A Overview

Key Specifications

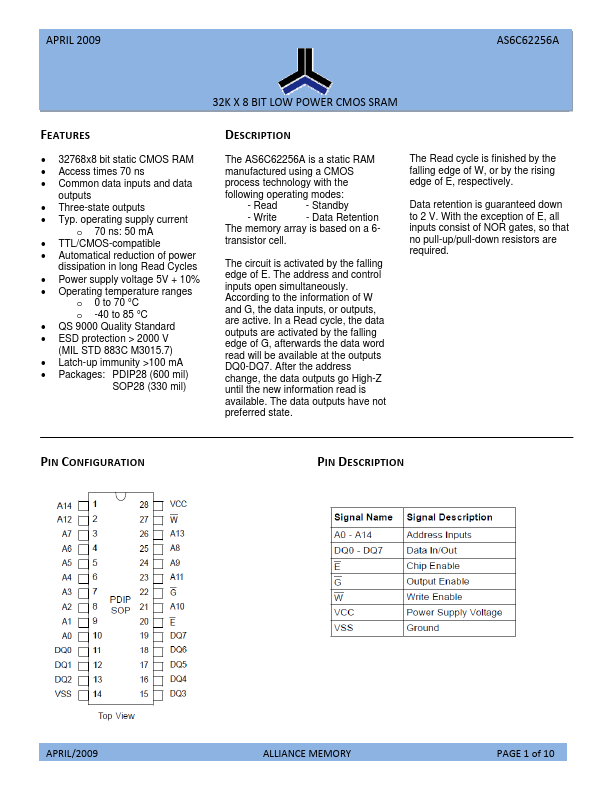

Package: SOP

Pins: 28

Operating Voltage: 5 V

Max Voltage (typical range): 5.5 V

Description

The AS6C62256A is a static RAM manufactured using a CMOS process technology with the following operating modes: - Read - Standby - Write - Data Retention The memory array is based on a 6- transistor cell. The circuit is activated by the falling edge of E.

Key Features

- 32768x8 bit static CMOS RAM

- Access times 70 ns

- Common data inputs and data outputs

- Three-state outputs

- Typ. operating supply current o 70 ns: 50 mA

- TTL/CMOS-compatible

- Automatical reduction of power dissipation in long Read Cycles

- Power supply voltage 5V + 10%

- Operating temperature ranges o 0 to 70 °C o -40 to 85 °C

- QS 9000 Quality Standard