AS7C3256 Description

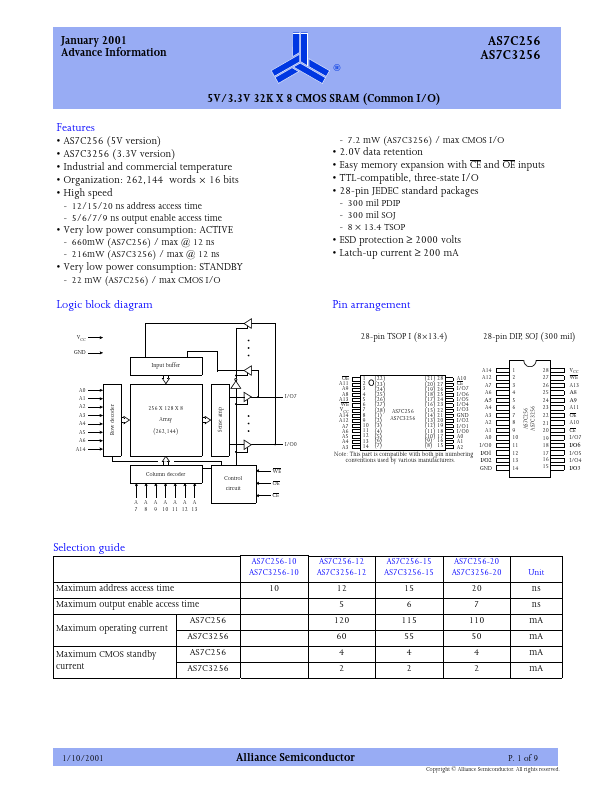

January 2001 Advance Information AS7C256 AS7C3256 ® 5V/3.3V 32K X 8 CMOS SRAM (mon.

AS7C3256 Key Features

- AS7C256 (5V version)

- AS7C3256 (3.3V version)

- Industrial and mercial temperature

- Organization: 262,144 words × 16 bits

- High speed

- 12/15/20 ns address access time

- 5/6/7/9 ns output enable access time

- Very low power consumption: ACTIVE

- 660mW (AS7C256) / max @ 12 ns

- 216mW (AS7C3256) / max @ 12 ns